# EEPROM PROGRAMMABLE CLOCK GENERATOR

# IDT5V49EE702

### **Description**

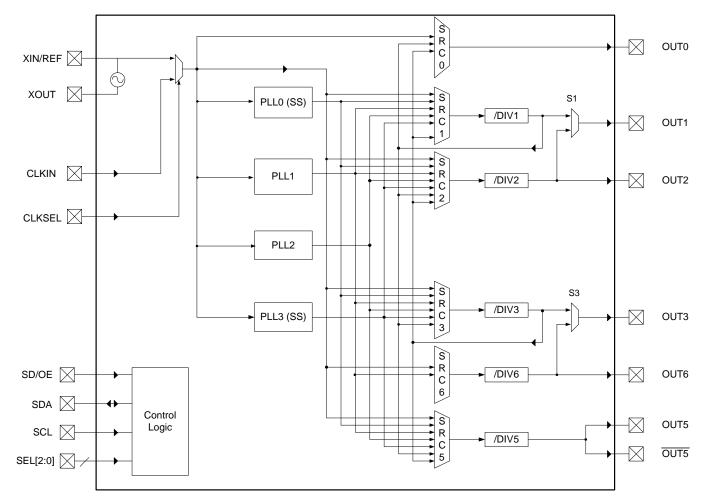

The IDT5V49EE702 is a programmable clock generator intended for high performance data-communications, telecommunications, consumer, and networking applications. There are four internal PLLs, each individually programmable, allowing for four unique non-integer-related frequencies. The frequencies are generated from a single reference clock. The reference clock can come from one of the two redundant clock inputs. Automatic or manual switchover function allows any one of the redundant clocks to be selected during normal operation.

The IDT5V49EE702 is in-system, programmable and can be programmed through the use of  $I^2C$  interface. An internal EEPROM allows the user to save and restore the configuration of the device without having to reprogram it on power-up.

Each of the four PLLs has an 7-bit reference divider and a 12-bit feedback divider. This allows the user to generate four unique non-integer-related frequencies. The PLL loop bandwidth is programmable to allow the user to tailor the PLL response to the application. For instance, the user can tune the PLL parameters to minimize jitter generation or to maximize jitter attenuation. Spread spectrum generation and/or fractional divides are allowed on two of the PLLs.

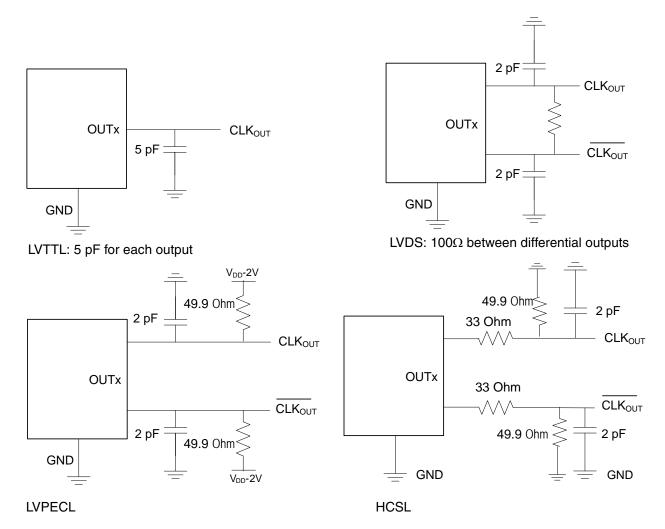

There are a total of five 8-bit output dividers. Each output bank can be configured to support LVTTL, LVPECL, LVDS or HCSL logic levels. Out0 (Output 0) supports LVTTL standard only. The outputs are connected to the PLLs via a switch matrix. The switch matrix allows the user to route the PLL outputs to any output bank. This feature can be used to simplify and optimize the board layout. In addition, each output's slew rate and enable/disable function is programmable.

### **Features**

- Four internal PLLs

- Internal non-volatile EEPROM

- Fast (400kHz) mode I<sup>2</sup>C serial interface

- Input frequency range: 1 MHz to 200 MHz

- Output frequency range: 4.9 kHz to 500 MHz

- Reference crystal input with programmable linear load capacitance

- Crystal frequency range: 8 MHz to 50 MHz

- Three independently controlled VDDO (1.8V 3.3V)

- Each PLL has a 7-bit reference divider and a 12-bit feedback-divider

- 8-bit output-divider blocks

- Fractional division capability on one PLL

- Two of the PLLs support spread spectrum generation capability

- I/O Standards:

- Outputs 1.8 3.3 V LVTTL/ LVCMOS

- Outputs LVPECL, LVDS and HCSL

- Inputs 3.3 V LVTTL/ LVCMOS

- Programmable slew rate control

- Programmable loop bandwidth

- · Programmable output inversion to reduce bimodal jitter

- Redundant clock inputs with auto and manual switchover options

- Individual output enable/disable

- Power-down mode

- 3.3V core V<sub>DD</sub>

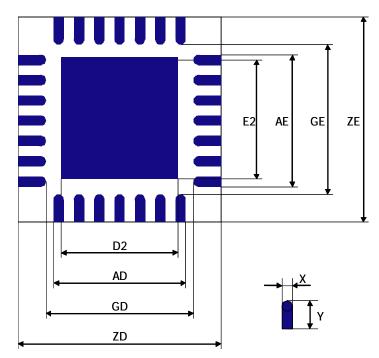

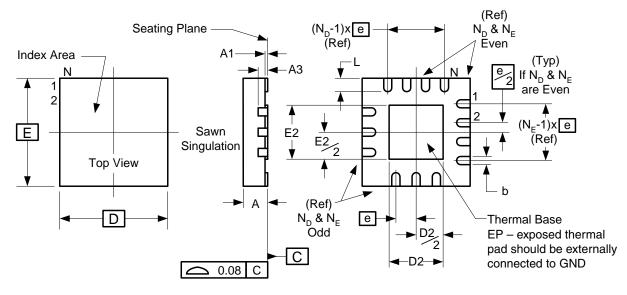

- Available in VFQFPN package

- -40 to +85 C Industrial Temp operation

# **Functional Block Diagram**

1. OUT1 & OUT2, OUT3 & OUT6, and OUT5 & OUT5 pairs can be configured to be LVDS, LVPECL or HCSL, or two single-ended LVTTL outputs. 2. CLKIN, CLKSEL, SD/OE and SEL[2:0] have pull down resistors.

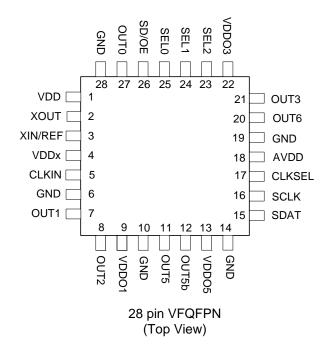

### **Pin Configuration**

### **Pin Descriptions**

| Pin# | Pin Name  | I/O | Pin Type                  | Pin Description                                                                                                             |  |

|------|-----------|-----|---------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| 1    | VDD       |     | Power                     | Device power supply. Connect to 3.3V.                                                                                       |  |

| 2    | XOUT      | 0   | LVTTL                     | CRYSTAL_OUT Reference crystal feedback.                                                                                     |  |

| 3    | XIN / REF | I   | LVTTL                     | CRYSTAL_IN Reference crystal input or external reference clock input.                                                       |  |

| 4    | VDDx      |     | Power                     | Crystal oscillator power supply. Connect to 3.3V through $5\Omega$ resistor. Use filtered analog power supply if available. |  |

| 5    | CLKIN     | I   | LVTTL                     | Input clock. Weak internal pull down resistor.                                                                              |  |

| 6    | GND       |     | Power                     | Connect to Ground.                                                                                                          |  |

| 7    | OUT1      | 0   | Adjustable <sup>1</sup>   | Configurable clock output 1. Single-ended or differential when combined with OUT2.                                          |  |

| 8    | OUT2      | 0   | Adjustable <sup>1</sup>   | Configurable clock output 2. Single-ended or differenti when combined with OUT1.                                            |  |

| 9    | VDDO1     |     | Power                     | Device power supply. Connect to 1.8 to 3.3V. Sets output voltage levels for OUT1 and OUT2.                                  |  |

| 10   | GND       |     | Power                     | Connect to Ground.                                                                                                          |  |

| 11   | OUT5      | 0   | Adjustable <sup>1,2</sup> | Configurable clock output 5. Single-ended or differential when combined with OUT5b.                                         |  |

| 12   | OUT5b     | 0   | Adjustable <sup>1,2</sup> | Configurable clock output 5b. Single-ended or differential when combined with OUT5.                                         |  |

| Pin# | Pin Name | I/O | Pin Type                | Pin Description                                                                                                                                                                                                  |

|------|----------|-----|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13   | VDDO5    |     | Power                   | Device power supply. Connect to 1.8 to 3.3V. Sets output voltage levels for OUT5 and OUT5b.                                                                                                                      |

| 14   | GND      |     | Power                   | Connect to Ground.                                                                                                                                                                                               |

| 15   | SDAT     | I/O | Open Drain              | Bidirectional I <sup>2</sup> C data. An external pull-up resistor is required. See I <sup>2</sup> C specification for pull-up value recommendation.                                                              |

| 16   | SCLK     | I   | LVTTL                   | I <sup>2</sup> C clock. An external pull-up resistor is required. See I <sup>2</sup> C specification for pull-up value recommendation.                                                                           |

| 17   | CLKSEL   | I   | LVTTL                   | Input clock selector. Weak internal pull down resistor.                                                                                                                                                          |

| 18   | AVDD     |     | Power                   | Device analog power supply. Connect to 3.3V. Use filtered analog power supply if available.                                                                                                                      |

| 19   | GND      |     | Power                   | Connect to Ground.                                                                                                                                                                                               |

| 20   | OUT6     | 0   | Adjustable <sup>1</sup> | Configurable clock output 6. Single-ended or differential when combined with OUT3.                                                                                                                               |

| 21   | OUT3     | 0   | Adjustable <sup>1</sup> | Configurable clock output 3. Single-ended or differential when combined with OUT6.                                                                                                                               |

| 22   | VDDO3    |     | Power                   | Device power supply. Connect to 1.8 to 3.3V. Sets output voltage levels for OUT3 and OUT6.                                                                                                                       |

| 23   | SEL2     | I   | LVTTL                   | Configuration select pin. Weak internal pull down resistor.                                                                                                                                                      |

| 24   | SEL1     | I   | LVTTL                   | Configuration select pin. Weak internal pull down resistor.                                                                                                                                                      |

| 25   | SEL0     | I   | LVTTL                   | Configuration select pin. Weak internal pull down resistor.                                                                                                                                                      |

| 26   | SD/OE    | I   | LVTTL                   | Enables/disables the outputs or powers down the chip.<br>The SP bit (0x02) controls the polarity of the signal to be<br>either active HIGH or LOW. (Default is active LOW.)<br>Weak internal pull down resistor. |

| 27   | OUT0     | 0   | LVTTL                   | Configurable clock output 0.                                                                                                                                                                                     |

| 28   | GND      |     | Power                   | Connect to Ground.                                                                                                                                                                                               |

1.Outputs are user programmable to drive single-ended 3.3-V LVTTL, or differential LVDS, LVPECL or HCSL interface levels

2. When only an individual single-ended clock output is required, tie OUT# and OUT#b together.

3. Analog power plane should be isolated from a 3.3V power plane through a ferrite bead.

4. Each power pin should have a dedicated 0.01µF de-coupling capacitor. Digital VDDs may be tied together.

5. Unused clock inputs (REFIN or CLKIN) must be pulled high or low - they cannot be left floating. If the crystal oscillator is not used, XOUT must be left floating.

### **PLL Features and Descriptions**

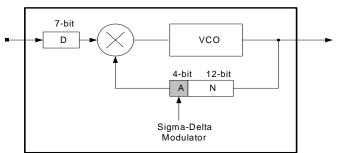

#### **PLL0 Block Diagram**

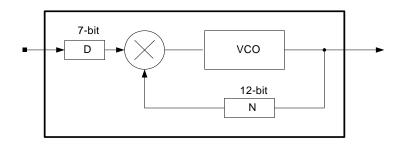

#### PLL1, PLL2 and PLL3 Block Diagram

|      | Pre-Divider<br>(D) <sup>1</sup> Values | Multiplier<br>(M) <sup>2</sup> Values | Programmable<br>Loop Bandwidth | Spread Spectrum<br>Generation Capability |

|------|----------------------------------------|---------------------------------------|--------------------------------|------------------------------------------|

| PLL0 | 1 - 127                                | 10 - 8206                             | Yes                            | Yes                                      |

| PLL1 | 1 - 127                                | 1 - 4095                              | Yes                            | No                                       |

| PLL2 | 1 - 127                                | 1 - 4095                              | Yes                            | No                                       |

| PLL3 | 3 - 127                                | 12 - 4095                             | Yes                            | Yes                                      |

1.For PLL0, PLL1 and PLL2, D=0 means PLL power down. For PLL3, 0, 1, and 2 are DNU (do not use) 2.For PLL0,  $M = 2^*N + A + 1$  (for A > 0);  $M = 2^*N$  (for A = 0);  $A \le N-1$ . For PLL1, PLL2 and PLL3, M=N.

# **Reference Clock Input Pins and Selection**

The IDT5V49EE702 supports up to two clock inputs. One of the clock inputs (XIN/ REF) can be driven by either an external crystal or a reference clock. The second clock input (CLKIN) can only be driven from an external reference clock. The CLKSEL pin selects the input clock from either XTAL/REF or CLKIN.

Either clock input can be set as the primary clock. The primary clock designation is to establish which is the main reference clock to the PLLs. The non-primary clock is designated as the secondary clock in case the primary clock goes absent and a backup is needed. The PRIMSRC bit (0xBE through 0xC3) determines which clock input will be selected as primary clock. When PRIMSRC bit is "0", XIN/REF is selected as the primary clock, and when "1", CLKIN as the primary clock.

The two external reference clocks can be manually selected using the CLKSEL pin. The SM bits (0xBE through 0xC3) must be set to "0x" for manual switchover which is detailed in SWITCHOVER MODES section.

### **Crystal Input (XIN/REF)**

The crystal used should be a fundamental mode quartz crystal; overtone crystals should not be used.

When the XIN/REF pin is driven by a crystal, it is important to set the internal inverter oscillator drive strength and tuning/load capacitor values correctly to achieve the best clock performance. These values are programmable through I<sup>2</sup>C interface to allow for maximum compatibility with crystals from various manufacturers, processes, performances, and gualities. The internal load capacitors are true parallel-plate capacitors for ultra-linear performance. Parallel-plate capacitors were chosen to reduce the frequency shift that occurs when non-linear load capacitance interacts with load, bias, supply, and temperature changes. External non-linear crystal load capacitors should not be used for applications that are sensitive to absolute frequency requirements. The value of the internal load capacitors are determined by XTAL[4:0] bits. The load capacitance can be set with a resolution of 0.125 pF for a total crystal load ranging from 3.5 pF to 7.5 pF. Check with the crystal vendor's load capacitance specification for the exact setting to tune the internal load capacitor. The following equation governs how the total

internal load capacitance is set.

XTAL load cap = 3.5 pF + XTAL[4:0] \* 0.125 pF (Eq. 1)

| Parameter | Bits | Step (pF) | Min (pF) | Max (pF) |

|-----------|------|-----------|----------|----------|

| XTAL      | 8    | 0.125     | 0        | 4        |

When using an external reference clock instead of a crystal on the XTAL/REF pin, the input load capacitors may be completely bypassed. This allows for the input frequency to be up to 200 MHz. When using an external reference clock, the XOUT pin must be left floating, XTAL must be programmed to the default value of "00h", and the crystal drive strength bit, XDRV (0x06), must be set to the default value of "11h".

### **Switchover Modes**

The IDT5V49EE702 features redundant clock inputs which supports both Automatic and Manual switchover mode. These two modes are determined by the configuration bits, SM (0xBE through 0xC3). The primary clock source can be programmed, via the PRIMSRC bit, to be either XIN/REF or CLKIN. The other clock input will be considered as the secondary source. Note that the switchover modes are asynchronous. If the reference clocks are directly routed to OUTx with no phase relationship, short pulses can be generated during switchover. The automatic switchover mode will work only when the primary clock source is XIN/REF. Switchover modes are not supported for crystal input configurations.

#### **Manual Switchover Mode**

When SM[1:0] is "0x", the redundant inputs are in manual switchover mode. In this mode, CLKSEL pin is used to switch between the primary and secondary clock sources. As previously mentioned, the primary and secondary clock source setting is determined by the PRIMSRC bit. During the switchover, no glitches will occur at the output of the device, although there may be frequency and phase drift, depending on the exact phase and frequency relationship between the primary and secondary clocks.

#### Automatic Switchover Mode

The redundant inputs are in automatic switchover mode. Automatic switchover mode has revertive functionality. The input clock selection will switch to the secondary clock source when there are no transitions on the primary clock source for two secondary clock cycles. If both reference clocks are at different frequencies, the device will always remain on the primary clock unless it is absent for two secondary clock cycles. The secondary clock must always run at a frequency less than or equal to the primary clock frequency.

#### Reference Divider, Feedback Divider, and Output Divider

Each PLL incorporates a 7-bit reference divider (D[6:0]) and a 12-bit feedback divider (N[11:0]) that allows the user to generate four unique non-integer-related frequencies. Each output divide supports 8-bit output-divider (PM and Q[7:0]). The following equation governs how the output frequency is calculated.

$$F_{OUT} = \frac{F_{IN} * \left(\frac{M}{D}\right)}{ODIV}$$

(Eq. 1)

Where FIN is the reference frequency, M is the total feedback-divider value, D is the reference divider value, ODIV is the total output-divider value, and FOUT is the resulting output frequency.

For PLL0,

M = 2 \* N + A + 1 (for A>0)

M = 2 \* N (for A = 0)

For PLL1, PLL2 and PLL3,

M = N

PM and Q[6:0] are the bits used to program the 8-bit output-dividers for outputs OUT1-6. OUT0 does not have any output divide along its path. The 8-bit output-dividers will bypass or divide down the output banks' frequency with even integer values ranging from 2 to 256.

There is the option to choose between disabling the output-divider, utilizing a div/1, a div/2, or the 7-bit Q-divider by using the PM bit. If the output is disabled, it will be driven High, Low or High Impedance, depending on OEM[1:0]. Each bank, except for OUT0, has a PM bit. When disabled, no clocks will appear at the output of the divider, but will remain powered on. The output divides selection table is shown below.

| Q[6:0]    | РМ | Output Divider      |

|-----------|----|---------------------|

| 111 1111  | 0  | Disabled            |

|           | 1  | /1                  |

| <111 1111 | 0  | /2                  |

|           | 1  | /((Q[6:0] + 2) * 2) |

Note that the actual 7-bit Q-divider value has a 2 added to the integer value Q and the outputs are routed through another div/2 block. The output divider should never be disabled unless the output bank will never be used during normal operation. The output frequency range for LVTTL outputs are from 4.9KHz to 200MHz. The output frequency for LVPECL/LVDS/HCSL outputs range from 4.9KHz to 500MHz.

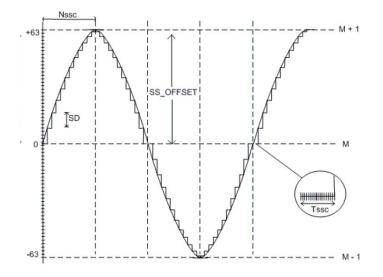

### **Spread Spectrum Generation (PLL0)**

PLL0 supports spread spectrum generation capability, which users have the option of turning on or off. Spread spectrum profile, frequency, and spread amplitude are fully programmable. The programmable spread spectrum generation parameters are TSSC[3:0], NSSC[2:0], SS\_OFFSET[5:0], SD[3:0], DITH, and X2 bits. These bits are in the memory address from 0xAC to 0xBD for PLL0. The spread spectrum generation on PLL0 can be enabled/disabled using the TSSC[3:0] bits. To enable spread spectrum, set TSSC > '0' and set NSSC[2:0], SS\_OFFSET[5:0], SD[3:0], and the A[3:0] (in the total M value) accordingly. To disable spread spectrum generation, set TSSC = '0'.

### TSSC[3:0]

These bits are used to determine the number of phase/frequency detector cycles per spread spectrum cycle (ssc) steps. The modulation frequency can be calculated with the TSSC bits in conjunction with the NSSC bits. Valid TSSC integer values for the modulation frequency range from 5 to 14. Values of 0 - 4 and 15 should not be used.

### NSSC[2:0]

These bits are used to determine the number of delta-encoded samples used for a single quadrant of the spread spectrum waveform. All four quadrants of the spread spectrum waveform are mirror images of each other. The modulation frequency is also calculated based on the NSSC bits in conjunction with the TSSC bits. Valid NSSC integer values range from 1 to 6. Values of 0 and 7 should not be used.

#### SS\_OFFSET[5:0]

These bits are used to program the fractional offset with respect to the nominal M integer value. For center spread, the SS\_OFFSET is set to '0' so that the spread spectrum waveform is centered about the nominal M (Mnom) value. For down spread, the SS\_OFFSET > '0' such the spread spectrum waveform is centered about the (Mideal -1 +SS\_Offset) value. The downspread percentage can be thought of in terms of center spread. For example, a downspread of -1% can also be considered as a center spread of  $\pm 0.5\%$  but with Mnom shifted down by one and offset. The SS\_OFFSET has integer values ranging from 0 to 63.

#### SD[3:0]

These bits are used to shape the profile of the spread spectrum waveform. These are delta-encoded samples of the waveform. There are twelve sets of SD samples. The NSSC bits determine how many of these samples are used for the waveform. The sum of these delta-encoded samples (sigma delta- encoded samples) determine the amount of spread and should not exceed (63 - SS\_OFFSET). The maximum spread is inversely proportional to the nominal M integer value.

#### DITH

This bit is used for dithering the sigma-delta-encoded samples. This will randomize the least-significant bit of the input to the spread spectrum modulator. Set the bit to '1' to enable dithering.

#### X2

This bit will double the total value of the sigma-delta-encoded-samples which will increase the amplitude of the spread spectrum waveform by a factor of two. When X2 is '0', the amplitude remains nominal but if set to '1', the amplitude is increased by x2. The following equations govern how the spread spectrum is set:

Tssc = TSSC[3:0] + 2 (Eq. 2)

Nssc = NSSC[2:0] \* 2 (Eq. 3)

$SD[3:0]\kappa = S_{J+1}(unencoded) - S_J(unencoded)$  (Eq. 4)

where  $S_J$  is the unencoded sample out of a possible 12 and  $SD_K$  is the delta-encoded sample out of a possible 12.

Amplitude = ((2\*N[11:0] + A[3:0] + 1) \* Spread% / 100) /2 (Eq. 5) if 1 < Amplitude < 2, then set X2 bit to '1'.

#### Modulation frequency:

FPFD = FIN / D (Eq. 6)

FVCO = FPFD \* MNOM (Eq. 7)

Fssc = FPFD / (4 \* Nssc \* Tssc) (Eq. 8)

#### Spread:

$\Sigma \Delta = SD_0 + SD_1 + SD_2 + ..+ SD_{11}$

the number of samples used depends on the Nssc value

$\Sigma\Delta \leq 63 - SS_OFFSET$

$\pm$ Spread% = ( $\Sigma\Delta * 100$ )/(64 \* (2\*N[11:0] + A[3:0] + 1) (Eq. 9)

±Max Spread% / 100 = 1 / MNOM or 2 / MNOM (X2=1)

### **Profile:**

Waveform starts with SS\_OFFSET, SS\_OFFSET + SD<sub>J</sub>, SS\_OFFSET + SD<sub>J+1</sub>, etc.

#### Spread Spectrum Using Sinusoidal Profile

### Example

$F_{IN} = 25MHz$ ,  $F_{OUT} = 100MHz$ ,  $F_{SSC} = 33KHz$  with center spread of ±2%. Find the necessary spread spectrum register settings.

Since the spread is center, the SS\_OFFSET can be set to '0'. Solve for the nominal M value; keep in mind that the nominal M should be chosen to maximize

the VCO. Start with D = 1, using Eq.6 and Eq.7.

MNOM = 1200MHz / 25MHz = 48

Using Eq.4, we arbitrarily choose N = 22, A = 3. Now that we have the nominal M value, we can determine TSSC and NSSC by using Eq.8.

Nssc \* Tssc = 25MHz / (33KHz \* 4) = 190

However, using Eq. 2 and Eq.3, we find that the closest value is when TSSC = 14 and NSSC = 6. Keep in mind to maximize the number of samples used

to enhance the profile of the spread spectrum waveform.

$$Tssc = 14 + 2 = 16$$

$Nssc = 6 * 2 = 12$

$Nssc * Tssc = 192$

Use Eq.10 to determine the value of the sigma-delta-encoded samples.

$\pm 2\% = (\Sigma \Delta * 100)/(64 * 48)$

$$\Sigma \Delta = 61.4$$

Either round up or down to the nearest integer value. Therefore, we end up with 61 or 62 for sigma-delta-encoded samples. Since the sigma-delta-encoded samples must not exceed 63 with SS\_OFFSET set to '0', 61 or 62 is well within the limits. It is the discretion of the user to define the shape of the profile that is better suited for the intended application.

Using Eq. 9 again, the actual spread for the sigma-delta-encoded samples of 56 and 57 are  $\pm 1.99\%$  and  $\pm 2.02\%$ , respectively.

Use Eq.10 to determine if the X2 bit needs to be set;

Amplitude = 48 \* (1.99 or 2.02) / 100/2 = 0.48 < 1

Therefore, the X2 = 0'. The dither bit is left to the discretion of the user.

The example above was of a center spread using spread spectrum. For down spread, the nominal M value can be set one integer value lower to 47.

Note that the IDT5V49EE702 should not be programmed with TSSC > '0', SS\_OFFSET = '0', and SD = '0' in order to prevent an unstable state in the modulator.

The PLL loop bandwidth must be at least 10x the modulation frequency along with higher damping (larger  $\omega uz$ ) to prevent the spread spectrum from being filtered and reduce extraneous noise. Refer to the LOOP FILTER section for more detail on  $\omega uz$ . The A[3:0] must be used for spread spectrum, even if the total multiplier value is an even integer.

### Spread Spectrum Generation (PLL3)

PLL3 support spread spectrum generation capability, which users have the option of turning on and off. Spread spectrum profile, frequency, and spread are fully programmable (within limits). The technique is different from that used in PLL0. The programmable spread spectrum generation parameters are SS\_D3[7:0], SSVCO[15:0], SSENB, IP3[4:0] and RZ3[3:0] bits. These bits are in the memory address range of 0x4C to 0x85 for PLL3. The spread spectrum generation on PLL3 can be enabled/disabled using the SSENB bit. To enable spread spectrum, set SSENB = '1'.

### For Spread Enabled:

Spread spectrum is configured using SS\_D3(spread spectrum reference divide)

$$SS_D3 = \frac{F_{IN}}{4 * F_{MOD}}$$

(Eq. 10)

and SSVCO (spread spectrum loop feedback counter).

SSVCO =

$$[0.5 * \frac{F_{VCO}}{F_{MOD}} * (1 + SS/400) + 5]$$

(Eq. 11)

SS is the total Spread Spectrum amount (I.e. center spread  $\pm 0.5\%$  has a total spread of 1.0% and down spread -0.5% has a total spread of 0.5%.)

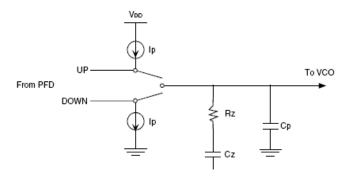

### **Loop Filter**

The loop filter for each PLL can be programmed to optimize the jitter performance. The low-pass frequency response of the PLL is the mechanism that dictates the jitter transfer characteristics. The loop bandwidth can be extracted from the jitter transfer. A narrow loop bandwidth is good for jitter attenuation while a wide loop bandwidth is best for low-jitter frequency generation. The specific loop filter components that can be programmed are the resistor via the RZ[3:0] bits, zero capacitor via the CZ bit (for PLL0, PLL1 and PLL2), and the charge pump current via the IP[2:0] bits (for PLL0, PLL1 and PLL2) or IP[3:0] (for PLL3).

The following equations govern how the loop filter is set for PLL0 - PLL2:

Resistor (Rz) = (RZ[0] + 2\* RZ[1]+4\* RZ[2] + 8\* RZ[3])\* 4.0 kOhm

Zero capacitor (Cz) = 196 pF + CZ\* 217 pF

Pole capacitor (Cp) = 15 pF

Charge pump (Ip) = 6 \* (IP[0] + 2\*IP[1]+4\*IP[2]) uA

VCO gain (Kvco) = 900 MHz/V \*  $2\pi$

The following equations govern how the loop filter is set for PLL3:

For Non-Spread Spectrum Operation:

$$Resistor(Rz) = {(12.5 + 12.5^{\circ}(RZ_1] + 2^{\circ}RZ_2] + 4^{\circ}RZ_3])) * RZ_0] + 6^{\circ}(1 - RZ_0])$$

kOhms (Eq. 12)

For Spread Spectrum Operation:

$Resistor(Rz) = {}^{(62.5 + 12.5^{\circ}(RZ[1] + 2^{\circ}RZ[2] + 4^{\circ}RZ[3]))}_{* RZ[0] + 6^{\circ}(1 - RZ[0])}$ kOhms (Eq. 13)

Zero capacitor (Cz) = 250 pF

Pole capacitor (Cp) = 15 pF

For Non-Spread Spectrum Operation:

$$\begin{array}{l} \text{Charge} \\ \text{pump (lp)} \end{array} = \frac{24^{*} \left(1 + \left(2^{*} \, \text{IP[0]}\right) + \left(4^{*} \, \text{IP[1]}\right) + \left(8^{*} \, \text{IP[2]}\right)\right)}{3 + \left(5^{*} \, \text{IP[3]}\right) + \left(11^{*} \, \text{IP[4]}\right)} \quad \text{A} \quad (\text{Eq. 14}) \end{array}$$

For Spread Spectrum Operation:

$$\frac{\text{Charge}}{\text{pump}(lp)} = \frac{12^{*}(1 + (2^{*} \text{IP}[0]) + (4^{*} \text{IP}[1]) + (8^{*} \text{IP}[2]))}{27 + (5^{*} \text{IP}[3]) + (11^{*} \text{IP}[4])} \text{ A (Eq. 14)}$$

VCO gain (Kvco) = 900 MHz/V \*  $2\pi$

#### PLL Loop Bandwidth:

Charge pump gain  $(K\phi)$  = lp /  $2\pi$

VCO gain (Kvco) = 900 MHz/V \*  $2\pi$

M = Total multiplier value (See the Reference Divider, Feedback Divider and Output Divider section for more detail)

$\omega c = (Rz * K\phi * Kvco * Cz)/(M * (Cz + Cp))$

$Fc = \omega c / 2\pi$

Note, the phase/frequency detector frequency (FPFD) is typically seven times the PLL closed-loop bandwidth (Fc) but too high of a ratio will reduce the phase margin thus compromising loop stability.

To determine if the loop is stable, the phase margin ( $\phi$ m) needs to be calculated as follows.

#### **Phase Margin:**

$\omega z = 1 / (Rz * Cz)$

$\omega p = (Cz + Cp)/(Rz * Cz * Cp)$

$\phi m = (360 / 2\pi) * [tan_{-1}(\omega c / \omega z) - tan_{-1}(\omega c / \omega p)]$

To ensure stability in the loop, the phase margin is recommended to be >  $60^{\circ}$  but too high will result in the lock time being excessively long. Certain loop filter parameters would need to be compromised to not only meet a required loop bandwidth but to also maintain loop stability.

# SEL[2:0] Function

The IDT5V49EE702 can support up to six unique configurations. Users may pre-programmed all these configurations, and select the configurations using SEL[2:0] pins. Alternatively, users may use I<sup>2</sup>C interface to configure these registers on-the-fly.

| SEL2 | SEL1 | SEL0 | <b>Configuration Selections</b> |

|------|------|------|---------------------------------|

| 0    | 0    | 0    | Select CONFIG0                  |

| 0    | 0    | 1    | Select CONFIG1                  |

| 0    | 1    | 0    | Select CONFIG2                  |

| 0    | 1    | 1    | Select CONFIG3                  |

| 1    | 0    | 0    | Select CONFIG4                  |

| 1    | 0    | 1    | Select CONFIG5                  |

| 1    | 1    | 0    | Reserved (Do not use)           |

| 1    | 1    | 1    | Reserved (Do not use)           |

### **Crystal/Clock Selection**

XTCLKSEL bit is used to bypass a crystal oscillator circuit when external clock source is used.

PRIMSRC bit is used to select a primary clock from XIN/REF and CLKIN.

| PRIMSRC bit | Primary | Secondary |

|-------------|---------|-----------|

| 0           | XIN/REF | CLKIN     |

| 1           | CLKIN   | XIN/REF   |

| CLKSEL input | Clock Source           |

|--------------|------------------------|

| 0            | Primary Clock Source   |

| 1            | Secondary Clock Source |

| CLKSEL | PRIMSRC | Reference Clock |

|--------|---------|-----------------|

| 0      | 0       | XIN/REF         |

| 0      | 1       | CLKIN           |

| 1      | 0       | CLKIN           |

| 1      | 1       | XIN/REF         |

| SMx[1:0] | Swithcing Mode | Primary to<br>Secondary | Secondary to<br>Primary |

|----------|----------------|-------------------------|-------------------------|

| 0x       | Manual         | No                      | No                      |

| 10       | Auto           | Yes                     | No                      |

| 11       | Auto-Revertive | Yes                     | Yes                     |

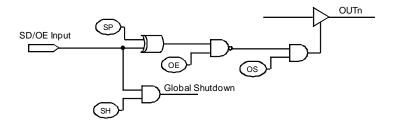

### **SD/OE** Pin Function

The polarity of the SD/OE signal pin can be programmed to be either active HIGH or LOW with the SP bit (0x02). When SP is "0" (default), the pin becomes active LOW and when SP is "1", the pin becomes active HIGH. The SD/OE pin can be configured as either to shutdown the PLLs or to enable/disable the outputs.

#### **Truth Table**

| SH bit | SP bit | OSn bit | OEn bit | SD/OE | OUTn                   |

|--------|--------|---------|---------|-------|------------------------|

| 0      | 0      | 0       | х       | х     | High-Z <sup>2</sup>    |

| 0      | 0      | 1       | 0       | х     | Enabled                |

| 0      | 0      | 1       | 1       | 0     | Enabled                |

| 0      | 0      | 1       | 1       | 1     | Suspended              |

| 0      | 1      | 0       | х       | х     | High-Z <sup>2</sup>    |

| 0      | 1      | 1       | 0       | х     | Enabled                |

| 0      | 1      | 1       | 1       | 0     | Suspended              |

| 0      | 1      | 1       | 1       | 1     | Enabled                |

| 1      | 0      | 0       | х       | 0     | High-Z <sup>2</sup>    |

| 1      | 0      | 1       | 0       | 0     | Enabled                |

| 1      | 0      | 1       | 1       | 0     | Enabled                |

| 1      | 1      | 0       | х       | 0     | High-Z <sup>2</sup>    |

| 1      | 1      | 1       | 0       | 0     | Enabled                |

| 1      | 1      | 1       | 1       | 0     | Suspended              |

| 1      | х      | х       | х       | 1     | Suspended <sup>1</sup> |

Note 1 : Global Shutdown

Note 2 : Hi-Z regardless of OEM bits

### **Configuration OUTx IO Standard**

Users can configure the individual output IO standard from a specified 1.8V to 3.3V power supplies. Each output can support 1.8V to 3.3V LVTTL. Each output pair can support LVDS, LVPECL or HCSL from the specified 3.3V power supply. OUT0 can only be 3.3V single-ended output.

### **Programming the Device**

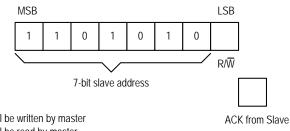

I<sup>2</sup>C may be used to program the IDT5V49EE702.

- Device (slave) address = 7'b1101010

### I<sup>2</sup>C Programming

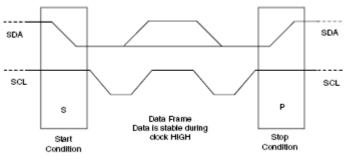

The IDT5V49EE702 is programmed through an  $I^2$ C-Bus serial interface, and is an  $I^2$ C slave device. The read and write transfer formats are supported. The first byte of data after a write frame to the correct slave address is interpreted as the register address; this address auto-increments after each byte written or read.

R/W

0 – Slave will be written by master1 – Slave will be read by master

The first byte transmitted by the Master is the Slave Address followed by the  $R/\overline{W}$  bit. The Slave acknowledges by sending a "1" bit.

#### First Byte Transmitted on I<sup>2</sup>C Bus

### External I<sup>2</sup>C Interface Condition

From Master to Slave

From Master to Slave, but can be omitted if followed by the correct sequence Normally, data transfer is terminated by a STOP condition generated by the Master. However, if the Master still wishes to communicate on the bus, it can generate a separate START condition, and address another Slave address without first generating a STOP condition.

From Slave to Master

#### SYMBOLS:

ACK - Acknowledge (SDAT LOW) NACK – Not Acknowledge (SDAT HIGH) SR – Repeated Start Condition S – START Condition P – STOP Condition

#### Progwrite

| S | Address | R/W | ACK   | Command Code      | ACK   | Register | ACK   | Data   | ACK   | Р |

|---|---------|-----|-------|-------------------|-------|----------|-------|--------|-------|---|

|   | 7-bits  | 0   | 1-bit | 8-bits: xxxx xx00 | 1-bit | 8-bits   | 1-bit | 8-bits | 1-bit |   |

#### **Progwrite Command Frame**

Writes can continue as long as a Stop condition is not sent and each byte will increment the register address.

IDT® EEPROM PROGRAMMABLE CLOCK GENERATOR

The frame formats are shown in the following illustration.

Framing

#### Progread

Note: If the expected read command is not from the next higher register to the previous read or write command, then set a known "read" register address prior to a read operation by issuing the following command:

| S | Address | R/W | ACK   | Command Code      | ACK   | Register | ACK   | Р |

|---|---------|-----|-------|-------------------|-------|----------|-------|---|

|   | 7-bits  | 0   | 1-bit | 8-bits: xxxx xx00 | 1-bit | 8-bits   | 1-bit |   |

Prior to Progread Command Set Register Address

The user can ignore the STOP condition above and use a repeated START condition instead, straight after the slave acknowledgement bit (i.e., followed by the Progread command):

| S | Address | R/W | ACK   | ID Byte | ACK   | Data_1 | ACK   | Data_2 | ACK   | Data_last | NACK  | Р |

|---|---------|-----|-------|---------|-------|--------|-------|--------|-------|-----------|-------|---|

|   | 7-bits  | 1   | 1-bit | 8-bits  | 1-bit | 8-bits | 1-bit | 8-bits | 1-bit | 8-bits    | 1-bit |   |

#### **Progread Command Frame**

#### Progsave

| S | Address | R/W | ACK   | Command Code      | ACK   | Ρ |

|---|---------|-----|-------|-------------------|-------|---|

|   | 7-bits  | 0   | 1-bit | 8-bits: xxxx xx01 | 1-bit |   |

Note:

PROGWRITE is for writing to the IDT5V49EE702 registers.

PROGREAD is for reading the IDT5V49EE702 registers.

PROGSAVE is for saving all the contents of the IDT5V49EE702 registers to the EEPROM.

PROGRESTORE is for loading the entire EEPROM contents to the IDT5V49EE702 registers.

#### Progrestore

| S | Address | R/W | ACK   | Command Code      | ACK   | Р |

|---|---------|-----|-------|-------------------|-------|---|

|   | 7-bits  | 0   | 1-bit | 8-bits: xxxx xx10 | 1-bit |   |

#### **EEPROM Interface**

The IDT5V49EE702 can also store its configuration in an internal EEPROM. The contents of the device's internal programming registers can be saved to the EEPROM by issuing a save instruction (ProgSave) and can be loaded back to the internal programming registers by issuing a restore instruction (ProgRestore).

To initiate a save or restore using I<sup>2</sup>C, only two bytes are transferred. The Device Address is issued with the read/write bit set to "0", followed by the appropriate command code. The save or restore instruction executes after the STOP condition is issued by the Master, during which time the IDT5V49EE702 will not generate Acknowledge bits. The IDT5V49EE702 will acknowledge the instructions after it has completed execution of them. During that time, the I<sup>2</sup>C bus should be interpreted as busy by all other users of the bus.

On power-up of the IDT5V49EE702, an automatic restore is performed to load the EEPROM contents into the internal programming registers. The IDT5V49EE702 will be ready to accept a programming instruction once it acknowledges its 7-bit I<sup>2</sup>C address.

# I<sup>2</sup>C Bus DC Characteristics

| Symbol           | Parameter             | Conditions             | Min                  | Тур | Max                 | Unit |

|------------------|-----------------------|------------------------|----------------------|-----|---------------------|------|

| V <sub>IH</sub>  | Input HIGH Level      |                        | 0.7xV <sub>DD</sub>  |     |                     | V    |

| V <sub>IL</sub>  | Input LOW Level       |                        |                      |     | 0.3xV <sub>DD</sub> | V    |

| V <sub>HYS</sub> | Hysteresis of Inputs  |                        | 0.05xV <sub>DD</sub> |     |                     | V    |

| I <sub>IN</sub>  | Input Leakage Current |                        |                      |     | ±1.0                | μA   |

| V <sub>OL</sub>  | Output LOW Voltage    | I <sub>OL</sub> = 3 mA |                      |     | 0.4                 | V    |

# I<sup>2</sup>C Bus AC Characteristics for Standard Mode

| Symbol                | Parameter                                | Min | Тур | Max  | Unit |

|-----------------------|------------------------------------------|-----|-----|------|------|

| F <sub>SCLK</sub>     | Serial Clock Frequency (SCL)             | 0   |     | 100  | kHz  |

| t <sub>BUF</sub>      | Bus free time between STOP and START     | 4.7 |     |      | μs   |

| t <sub>SU:START</sub> | Setup Time, START                        | 4.7 |     |      | μs   |

| t <sub>HD:START</sub> | Hold Time, START                         | 4   |     |      | μs   |

| t <sub>SU:DATA</sub>  | Setup Time, data input (SDA)             | 250 |     |      | ns   |

| t <sub>HD:DATA</sub>  | Hold Time, data input (SDA) <sup>1</sup> | 0   |     |      | μs   |

| t <sub>OVD</sub>      | Output data valid from clock             |     |     | 3.45 | μs   |

| CB                    | Capacitive Load for Each Bus Line        |     |     | 400  | pF   |

| t <sub>R</sub>        | Rise Time, data and clock (SDAT, SCLK)   |     |     | 1000 | ns   |

| t <sub>F</sub>        | Fall Time, data and clock (SDAT, SCLK)   |     |     | 300  | ns   |

| t <sub>HIGH</sub>     | HIGH Time, clock (SCLK)                  | 4   |     |      | μs   |

| t <sub>LOW</sub>      | LOW Time, clock (SCLK)                   | 4.7 |     |      | μs   |

| t <sub>SU:STOP</sub>  | Setup Time, STOP                         | 4   |     |      | μs   |

Note 1: A device must internally provide a hold time of at least 300 ns for the SDAT signal (referred to the  $V_{IH}(MIN)$  of the SCLK signal) to bridge the undefined region of the falling edge of SCLK.

# I<sup>2</sup>C Bus AC Characteristics for Fast Mode

| Symbol                | Parameter                                | Min                     | Тур | Max | Unit |

|-----------------------|------------------------------------------|-------------------------|-----|-----|------|

| F <sub>SCLK</sub>     | Serial Clock Frequency (SCL)             | 0                       |     | 400 | kHz  |

| t <sub>BUF</sub>      | Bus free time between STOP and START     | 1.3                     |     |     | μs   |

| t <sub>SU:START</sub> | Setup Time, START                        | 0.6                     |     |     | μs   |

| t <sub>HD:START</sub> | Hold Time, START                         | 0.6                     |     |     | μs   |

| t <sub>SU:DATA</sub>  | Setup Time, data input (SDA)             | 100                     |     |     | ns   |

| t <sub>HD:DATA</sub>  | Hold Time, data input (SDA) <sup>1</sup> | 0                       |     |     | μs   |

| t <sub>OVD</sub>      | Output data valid from clock             |                         |     | 0.9 | μs   |

| CB                    | Capacitive Load for Each Bus Line        |                         |     | 400 | pF   |

| t <sub>R</sub>        | Rise Time, data and clock (SDA, SCL)     | 20 + 0.1xC <sub>B</sub> |     | 300 | ns   |

| t <sub>F</sub>        | Fall Time, data and clock (SDA, SCL)     | 20 + 0.1xC <sub>B</sub> |     | 300 | ns   |

| t <sub>HIGH</sub>     | HIGH Time, clock (SCL)                   | 0.6                     |     |     | μs   |

| t <sub>LOW</sub>      | LOW Time, clock (SCL)                    | 1.3                     |     |     | μs   |

| t <sub>SU:STOP</sub>  | Setup Time, STOP                         | 0.6                     |     |     | μs   |

Note 1: A device must internally provide a hold time of at least 300 ns for the SDA signal (referred to the  $V_{IH}(MIN)$  of the SCL signal) to bridge the undefined region of the falling edge of SCL.

# Absolute Maximum Ratings

Stresses above the ratings listed below can cause permanent damage to the IDT5V49EE702. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Symbol           | Description                                       | Min  | Мах                  | Unit |

|------------------|---------------------------------------------------|------|----------------------|------|

| V <sub>DD</sub>  | Internal Power Supply Voltage                     | -0.5 | +4.6                 | V    |

| VI               | Input Voltage <sup>1</sup>                        | -0.5 | +4.6                 | V    |

| Vo               | Output Voltage (not to exceed 4.6 V) <sup>1</sup> | -0.5 | V <sub>DD</sub> +0.5 | V    |

| Т <sub>Ј</sub>   | Junction Temperature                              |      | 150                  | °C   |

| T <sub>STG</sub> | Storage Temperature                               | -65  | 150                  | °C   |

1.Input negative and output voltage ratings may be exceeded if the input and output current ratings are observed.

# **Recommended Operation Conditions**

| Symbol                | Parameter                                                                                                        | Min   | Тур | Max   | Unit |

|-----------------------|------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| V <sub>DD</sub>       | Power supply voltage for $V_{\mbox{\scriptsize DD}}$ pins supporting core and outputs                            | 3.135 | 3.3 | 3.465 | V    |

| V <sub>DDX</sub>      | Power supply voltage for crystal oscillator. Use filtered analog power supply if available.                      | 3.135 | 3.3 | 3.465 | V    |

| AV <sub>DD</sub>      | Analog power supply voltage. Use filtered analog power supply if available.                                      | 3.135 | 3.3 | 3.465 | V    |

| V <sub>DDOX</sub>     | 3.3V VDDO Range                                                                                                  | 3.0   | 3.3 | 3.6   | V    |

|                       | 2.5V VDDO Range for 2.5V LVTTL                                                                                   | 2.25  | 2.5 | 2.75  | V    |

|                       | 1.8V VDDO Range for 1.8V LVTTL                                                                                   | 1.7   | 1.8 | 1.9   | V    |

|                       | Power supply voltage for V <sub>DD</sub> pins supporting LVDS/LVPECL/HCSL outputs                                | 3.135 | 3.3 | 3.465 | V    |

| Τ <sub>Α</sub>        | Operating temperature, ambient                                                                                   | -40   |     | +85   | °C   |

| C <sub>LOAD_OUT</sub> | Maximum load capacitance (3.3V LVTTL only)                                                                       |       |     | 15    | pF   |

|                       | Maximum load capacitance (1.8V/2.5V LVTTL only)                                                                  |       |     | 8     | pF   |

| F <sub>IN</sub>       | External reference crystal                                                                                       | 8     |     | 50    | MHz  |

|                       | External reference clock CLKIN                                                                                   | 1     |     | 200   | 1    |

| t <sub>PU</sub>       | Power up time for all $V_{\text{DD}}\text{s}$ to reach minimum specified voltage (power ramps must be monotonic) | 0.05  |     | 5     | ms   |

# **Capacitance** (T<sub>A</sub> = +25 °C)

| Symbol                | Parameter                                                    | Min | Тур | Max  | Unit |

|-----------------------|--------------------------------------------------------------|-----|-----|------|------|

| C <sub>IN</sub>       | Input Capacitance (CLKIN, CLKSEL, SD/OE, SDA, SCL, SEL[2:0]) |     | 3   | 7    | pF   |

| Pull-down<br>Resistor | CLKIN, CLKSEL, SD/OE, SEL[2:0]                               |     | 180 |      | kΩ   |

| Crystal Specif        | ications                                                     |     |     |      | 1    |

| XTAL_FREQ             | Crystal frequency                                            | 8   |     | 50   | MHz  |

| XTAL_MIN              | Minimum crystal load capacitance                             | 3.5 |     |      | pF   |

| XTAL_MAX              | Maximum crystal load capacitance                             |     |     | 35.5 | pF   |

| XTAL_V <sub>PP</sub>  | Voltage swing (peak-to-peak, nominal)                        | 1.5 | 2.3 | 3.2  | V    |

# DC Electrical Characteristics for 3.3-V LVTTL<sup>1</sup>

| Symbol            | Parameter              | Test Conditions                                            | Min | Тур | Max             | Unit |

|-------------------|------------------------|------------------------------------------------------------|-----|-----|-----------------|------|

| V <sub>OH</sub>   | Output HIGH Voltage    |                                                            | 2.4 |     | V <sub>DD</sub> | V    |

| V <sub>OL</sub>   | Output LOW Voltage     |                                                            |     |     | 0.4             | V    |

| V <sub>IH</sub>   | Input HIGH Voltage     |                                                            | 2   |     |                 | V    |

| V <sub>IL</sub>   | Input LOW Voltage      |                                                            |     |     | 0.8             | V    |

| I <sub>OZDD</sub> | Output Leakage Current | 3-state outputs. $V_O = V_{DD}$ or GND,<br>$V_{DD} = 3.6V$ |     |     | 10              | μA   |

Note 1: See "Recommended Operating Conditions" table.

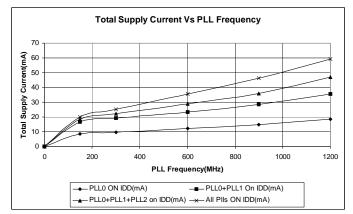

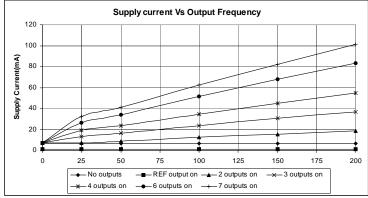

# Power Supply Characteristics for PLLs and LVTTL Outputs

IDT® EEPROM PROGRAMMABLE CLOCK GENERATOR

# **DC Electrical Characteristics for LVDS**

| Symbol              | Parameter                                                                | Min   | Тур | Max   | Unit |

|---------------------|--------------------------------------------------------------------------|-------|-----|-------|------|

| V <sub>OT</sub> (+) | Differential Output Voltage for the TRUE binary state                    | 247   |     | 454   | mV   |

| V <sub>OT</sub> (-) | Differential Output Voltage for the FALSE binary state                   | -247  |     | -454  | mV   |

| $\triangle V_{OT}$  | Change in V <sub>OT</sub> between Complimentary Output States            |       |     | 50    | mV   |

| V <sub>OS</sub>     | Output Common Mode Voltage (Offset Voltage)                              | 1.125 | 1.2 | 1.375 | V    |

| $\triangle V_{OS}$  | Change in V <sub>OS</sub> between Complimentary Output States            |       |     | 50    | mV   |

| I <sub>OS</sub>     | Outputs Short Circuit Current, $V_{OUT}$ + or $V_{OUT}$ = 0V or $V_{DD}$ |       | 9   | 24    | mA   |

| I <sub>OSD</sub>    | Differential Outputs Short Circuit Current, $V_{OUT}$ + = $V_{OUT}$ -    |       | 6   | 12    | mA   |

# Power Supply Characteristics for LVDS Outputs<sup>1</sup>

| Symbol           | Parameter                                                  | Test Conditions <sup>2</sup>                                  | Тур | Max | Unit   |

|------------------|------------------------------------------------------------|---------------------------------------------------------------|-----|-----|--------|

| I <sub>DDQ</sub> | Quiescent V <sub>DD</sub> Power<br>Supply Current          | REF = LOW<br>Outputs enabled, all outputs unloaded            | 68  | 90  | mA     |

| I <sub>DDD</sub> | Dynamic V <sub>DD</sub> Power Supply<br>Current per Output | $V_{DD} = Max., C_L = 0pF$                                    | 30  | 45  | µA/MHz |

| I <sub>TOT</sub> | Total Power V <sub>DD</sub> Supply                         | $F_{REFERENCE CLOCK} = 100 \text{ MHz}, C_{L} = 2 \text{ pF}$ | 86  | 130 | mA     |

|                  | Current                                                    | $F_{REFERENCE CLOCK} = 200 \text{ MHz}, C_{L} = 2 \text{ pF}$ | 100 | 150 |        |

|                  |                                                            | $F_{REFERENCE CLOCK} = 400 \text{ MHz}, C_{L} = 2 \text{ pF}$ | 122 | 190 |        |

Note 1: Output bank 5 is toggling. Other output banks are powered down.

Note 2: The termination resistors are excluded from these measurements.

# **DC Electrical Characteristics for LVPECL**

| Symbol             | Parameter                                                            | Min                   | Тур | Max                   | Unit |

|--------------------|----------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| V <sub>OH</sub>    | Output Voltage HIGH, terminated through 50 $\Omega$ tied to V_DD-2 V | V <sub>DD</sub> -1.2  |     | V <sub>DD</sub> -0.9  | V    |

| V <sub>OL</sub>    | Output Voltage LOW, terminated through 50 $\Omega$ tied to V_DD-2 V  | V <sub>DD</sub> -1.95 |     | V <sub>DD</sub> -1.61 | V    |

| V <sub>SWING</sub> | Peak-to-Peak Output Voltage Swing                                    | 0.55                  |     | 0.93                  | V    |

# Power Supply Characteristics for LVPECL Outputs<sup>1</sup>

| Symbol           | Parameter                                                  | Тур                                                | Max | Unit |        |

|------------------|------------------------------------------------------------|----------------------------------------------------|-----|------|--------|

| I <sub>DDQ</sub> | Quiescent V <sub>DD</sub> Power<br>Supply Current          | REF = LOW<br>Outputs enabled, all outputs unloaded | 86  | 110  | mA     |

| I <sub>DDD</sub> | Dynamic V <sub>DD</sub> Power Supply<br>Current per Output | $V_{DD} = Max., C_L = 0pF$                         | 35  | 50   | µA/MHz |

| Symbol           | Parameter                          | Test Conditions <sup>2</sup>                                                | Тур | Max | Unit |

|------------------|------------------------------------|-----------------------------------------------------------------------------|-----|-----|------|

| I <sub>TOT</sub> | Total Power V <sub>DD</sub> Supply | F <sub>REFERENCE CLOCK</sub> = 100 MHz, C <sub>L</sub> = 2 pF               | 120 | 180 | mA   |

|                  | Current                            | $F_{REFERENCE CLOCK} = 200 \text{ MHz}, C_{L} = 2 \text{ pF}$               | 130 | 190 |      |

|                  |                                    | $F_{\text{REFERENCE CLOCK}} = 400 \text{ MHz}, C_{\text{L}} = 2 \text{ pF}$ | 140 | 210 |      |

Note 1: Output bank 5 is toggling. Other output banks are powered down.

Note 2: The termination resistors are excluded from these measurements.

### **DC Electrical Characteristics for HCSL**

| Symbol                       | Parameter           | Min  | Тур | Max | Unit |

|------------------------------|---------------------|------|-----|-----|------|

| V <sub>OH</sub>              | Output Voltage HIGH | 660  | 700 | 850 | mV   |

| V <sub>OL</sub>              | Output Voltage LOW  | -150 | 0   | 27  | mV   |

| Crossing<br>Point<br>Voltage | Absolute            | 250  | 350 | 550 | mV   |

# Power Supply Characteristics for HCSL Outputs<sup>1</sup>

| Symbol           | Parameter                                                  | Test Conditions <sup>2</sup>                                  | Тур | Max | Unit   |

|------------------|------------------------------------------------------------|---------------------------------------------------------------|-----|-----|--------|

| I <sub>DDQ</sub> | Quiescent V <sub>DD</sub> Power<br>Supply Current          | REF = LOW<br>Outputs enabled, all outputs unloaded            | 68  | 90  | mA     |

| I <sub>DDD</sub> | Dynamic V <sub>DD</sub> Power Supply<br>Current per Output | $V_{DD} = Max., C_L = 0pF$                                    | 30  | 45  | µA/MHz |

| I <sub>TOT</sub> | Total Power V <sub>DD</sub> Supply                         | $F_{REFERENCE CLOCK} = 100 \text{ MHz}, C_{L} = 2 \text{ pF}$ | 86  | 130 | mA     |

|                  | Current                                                    | $F_{REFERENCE CLOCK} = 200 \text{ MHz}, C_{L} = 2 \text{ pF}$ | 100 | 150 |        |

|                  |                                                            | $F_{REFERENCE CLOCK} = 400 \text{ MHz}, C_{L} = 2 \text{ pF}$ | 122 | 190 |        |

Note 1: Output bank 5 is toggling. Other output banks are powered down.

Note 2: The termination resistors are excluded from these measurements.

# **AC Timing Electrical Characteristics**

(Spread Spectrum Generation = OFF)

| Symbol            | Parameter                 | Test Conditions                                                                                             | Min.             | Тур. | Max. | Units |

|-------------------|---------------------------|-------------------------------------------------------------------------------------------------------------|------------------|------|------|-------|

| f <sub>IN</sub> 1 | Input Frequency           | Input frequency limit (CLKIN)                                                                               | 1                |      | 200  | MHz   |

|                   |                           | Input frequency limit (XIN/REF)                                                                             | 8                |      | 100  | MHz   |

| 1 / t1            | Output Frequency          | Single ended clock output limit (LVTTL)                                                                     | 0.001            |      | 200  | MHz   |

|                   |                           | Differential clock output limit (LVPECL/<br>LVDS/HCSL)                                                      | 0.001            |      | 500  |       |

| f <sub>VCO</sub>  | VCO Frequency             | VCO operating frequency range                                                                               | 100              |      | 1200 | MHz   |

| f <sub>PFD</sub>  | PFD Frequency             | PFD operating frequency range                                                                               | 0.5 <sup>1</sup> |      | 100  | MHz   |

| f <sub>BW</sub>   | Loop Bandwidth            | Based on loop filter resistor and capacitor values                                                          | 0.01             |      | 10   | MHz   |

| t2                | Input Duty Cycle          | Duty Cycle for input                                                                                        | 40               |      | 60   | %     |

| t3                | Output Duty Cycle         | Measured at V <sub>DD</sub> /2, all outputs except Reference output                                         | 45               |      | 55   | %     |

|                   |                           | Measured at V <sub>DD</sub> /2, Reference output                                                            | 40               |      | 60   | %     |

| t4 <sup>2</sup>   | Slew Rate, SLEW[1:0] = 00 | Single-ended 3.3V LVCMOS output clock rise<br>and fall time, 20% to 80% of $V_{DD}$<br>(Output Load = 5 pF) |                  | 3.5  |      | V/ns  |

|                   | Slew Rate, SLEW[1:0] = 01 | Single-ended 3.3V LVCMOS output clock rise<br>and fall time, 20% to 80% of $V_{DD}$<br>(Output Load = 5 pF) |                  | 2.75 |      |       |

|                   | Slew Rate, SLEW[1:0] = 10 | Single-ended 3.3V LVCMOS output clock rise<br>and fall time, 20% to 80% of $V_{DD}$<br>(Output Load = 5 pF) |                  | 2    |      | -     |

|                   | Slew Rate, SLEW[1:0] = 11 | Single-ended 3.3V LVCMOS output clock rise<br>and fall time, 20% to 80% of $V_{DD}$<br>(Output Load = 5 pF) |                  | 1.25 |      | -     |

| t5                | Rise Times                | LVDS, 20% to 80%                                                                                            |                  | 600  |      | ps    |

|                   | Fall Times                | LVDS, 80% to 20%                                                                                            |                  | 600  |      |       |

|                   | Rise Times                | LVPECL, 20% to 80%                                                                                          |                  | 600  |      | ps    |

|                   | Fall Times                | LVPECL, 80% to 20%                                                                                          |                  | 600  |      |       |

|                   | Rise Times                | HCSL, From 0.175 V to 0.525 V                                                                               | 175              | 400  | 700  | ps    |

|                   | Fall Times                | HCSL, From 0.525 V to 0.175 V                                                                               | 175              | 400  | 700  |       |

| Symbol           | Parameter                 | Test Conditions                                                                                             | Min. | Тур. | Max. | Units |

|------------------|---------------------------|-------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t7               | Clock Jitter <sup>6</sup> | Peak-to-peak period jitter, 1PLL, multiple output frequencies switching, LVTTL outputs                      |      | 80   | 100  | ps    |

|                  |                           | Peak-to-peak period jitter, all 4 PLLs on, LVTTL outputs <sup>3</sup>                                       |      | 200  | 270  | ps    |

|                  |                           | Peak-to-peak period jitter, 1PLL, multiple<br>output frequencies switching, LVPECL, LVDS<br>or HCSL outputs |      | 60   | 80   | ps    |

|                  |                           | Peak-to-peak period jitter, all 4 PLLs on, LVPECL, LVDS or HCSL outputs                                     |      | 120  | 160  | ps    |

| t8               | Output Skew               | Skew between output to output on the same bank                                                              |      |      | 75   | ps    |

| t9 <sup>4</sup>  | Lock Time                 | PLL lock time from power-up                                                                                 |      | 10   | 20   | ms    |

| t10 <sup>5</sup> | Lock Time                 | PLL lock time from shutdown mode                                                                            |      |      | 2    | ms    |

1. Practical lower frequency is determined by loop filter settings.

2.A slew rate of 2.75V/ns or greater should be selected for output frequencies of 100MHz or higher. 3.Jitter measured with clock outputs of 27 MHz, 48 MHz, 24.576 MHz, 74.25 MHz and 25 MHz. 4.Includes loading the configuration bits from EEPROM to PLL registers. It does not include EEPROM programming/write time.

S.Actual PLL lock time depends on the loop configuration.

Not guaranteed until customer specific configuration is approved by IDT.

### **Spread Spectrum Generation Specifications**

| Symbol                           | Parameter       | Description                                           | Min   | Тур | Max  | Unit              |

|----------------------------------|-----------------|-------------------------------------------------------|-------|-----|------|-------------------|

| f <sub>IN</sub> 1                | Input Frequency | Input Frequency Limit                                 | 1     |     | 400  | MHz               |

| f <sub>MOD</sub>                 | Mod Frequency   | Modulation Frequency                                  |       | 33  | 120  | kHz               |

| f <sub>SPREAD</sub> <sup>2</sup> | Spread Value    | Amount of Spread Value (programmable) - Down Spread   | -0.5  |     | -4.0 | %f <sub>OUT</sub> |

|                                  |                 | Amount of Spread Value (programmable) - Center Spread | ±0.25 |     | ±2.0 |                   |

1. Practical lower frequency is determined by loop filter settings.

2. Not guaranteed until customer specific configuration is approved by IDT.

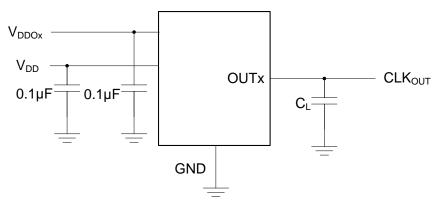

### **Test Circuits and Conditions**

**Test Circuits for DC Outputs**

# Other Termination Scheme (Block Diagram)

# Programming Registers Table

|              | Default                  |                      |                           |               | E        | Bit #       |       |           |       |                                                                                                                                                                                                             |

|--------------|--------------------------|----------------------|---------------------------|---------------|----------|-------------|-------|-----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Addr         | Register<br>Hex<br>Value | 7                    | 6                         | 5             | 4        | 3           | 2     | 1         | 0     | Description                                                                                                                                                                                                 |

| 0x00         | 00                       |                      |                           |               | Reserved |             |       |           | HW/SW | Hardware/Software Mode control<br>HW/SW - 0=HW, 1=SW                                                                                                                                                        |

| 0x01         | 00                       |                      |                           | Reserved      |          |             |       | SEL[2:0]  |       | SEL[2:0] - selects configuration in SW mode                                                                                                                                                                 |

| 0x02         | 02                       | SP                   | OE6                       | OE5           | OE4      | OE3         | OE2   | OE1       | OE0   | OEx=Output Power Suspend<br>function for OUTx ('1'=OUTx will<br>be suspended on SD/OE pin.<br>Disable mode is defined by<br>OEMx bits), '0'=outputs enabled<br>and no association with OE pin<br>(default). |

| 0x03         | 02                       | Reserved             |                           |               | -1       | OS*[6:0]    |       | +         |       | OS*[6:0] - output suspend, active<br>low. Overwrites OE setting.                                                                                                                                            |

| 0x04         | 0F                       | SH                   |                           | Reserved      |          |             | PL    | LS*[3:0]  |       | PLLS*[3:0] - PLL Suspend, active<br>low<br>SH - shutdown/OE configuration                                                                                                                                   |

| 0x05         | 04                       |                      | Reserved                  |               | XTCLKSEL |             | Re    | eserved   |       | XTCLKSEL - crystal/clock select.<br>0=Crytal, 1=ICLK                                                                                                                                                        |

| 0x06         | 00                       | Reserved             |                           |               |          |             |       |           |       |                                                                                                                                                                                                             |

| 0x07         | 00                       |                      | Reserved XTAL[4:0] XTAL[4 |               |          |             |       |           |       | XTAL[4:0] - crystal cap                                                                                                                                                                                     |

| 0x08         | 00                       |                      |                           |               | Re       | served      |       |           |       |                                                                                                                                                                                                             |

| 0x09         | 00                       |                      |                           |               | Re       | served      |       |           |       |                                                                                                                                                                                                             |

| 0x0A         | 10                       | CZ0_CFG4             |                           | IP0[2:0]_CFG4 |          |             |       | 3:0]_CFG4 |       | PLL0 loop parameter                                                                                                                                                                                         |

| 0x0B         | 10                       | CZ0_CFG5             |                           | IP0[2:0]_CFG5 |          |             | RZ0[3 |           |       |                                                                                                                                                                                                             |

| 0x0C         | 10                       | CZ0_CFG0             |                           | IP0[2:0]_CFG0 |          |             |       | 3:0]_CFG0 |       |                                                                                                                                                                                                             |

| 0x0D         | 10                       | CZ0_CFG1             |                           | IP0[2:0]_CFG1 |          |             | -     | 3:0]_CFG1 |       | _                                                                                                                                                                                                           |

| 0x0E         | 10                       | CZ0_CFG2             |                           | IP0[2:0]_CFG2 |          |             | -     | 3:0]_CFG2 |       |                                                                                                                                                                                                             |

| 0x0F         | 10                       | CZ0_CFG3             | IP0[2:0]_CFG3             |               |          | D0/0.01.050 | -     | 3:0]_CFG3 |       |                                                                                                                                                                                                             |

| 0x10         | 00                       | Reserved             |                           |               |          | D0[6:0]_CFG |       |           |       | PLL0 input divider and input sel<br>D0[6:0] - 127 step Ref Div                                                                                                                                              |

| 0x11<br>0x12 | 00                       | Reserved<br>Reserved |                           |               |          | D0[6:0]_CFG |       |           |       | D0 = 0 means power down.                                                                                                                                                                                    |

| 0x12<br>0x13 | 00                       | Reserved             |                           |               |          | D0[6:0]_CFG |       |           |       | _                                                                                                                                                                                                           |

| 0x13         | 00                       | Reserved             |                           |               |          | D0[6:0]_CFG |       |           |       |                                                                                                                                                                                                             |

| 0x14         | 00                       | Reserved             |                           |               |          | D0[6:0]_CFG |       |           |       | _                                                                                                                                                                                                           |

| 0x10         | 00                       | Hobervou             |                           |               | N0[7·    | 0] CFG4     | •     |           |       | N - Feedback Divider                                                                                                                                                                                        |

| 0x10         | 01                       |                      |                           |               |          | 0]_CFG5     |       |           |       | 2 - 4095 (values of "0" and "1" are                                                                                                                                                                         |

| 0x18         | 01                       |                      |                           |               | -        | 0] CFG0     |       |           |       | <ul> <li>not allowed) Total feedback with<br/>A, using provided calculation</li> </ul>                                                                                                                      |

| 0x19         | 01                       |                      |                           |               |          | 0]_CFG1     |       |           |       |                                                                                                                                                                                                             |

| 0x1A         | 01                       |                      |                           |               | -        | :0]_CFG2    |       |           |       | -                                                                                                                                                                                                           |

| 0x1B         | 01                       |                      |                           |               | N0[7:    | 0]_CFG3     |       |           |       |                                                                                                                                                                                                             |

| 0x1C         | 00                       |                      | A0[3:0]                   | _CFG0         |          |             | N0[11 | 1:8]_CFG0 |       |                                                                                                                                                                                                             |

| 0x1D         | 00                       |                      | A0[3:0]                   | _CFG1         |          |             | N0[11 | 1:8]_CFG1 |       |                                                                                                                                                                                                             |

| 0x1E         | 00                       |                      | A0[3:0]_                  | _CFG2         |          |             | N0[11 | 7         |       |                                                                                                                                                                                                             |

| 0x1F         | 00                       |                      | A0[3:0]                   | _CFG3         |          |             | N0[11 | 1:8]_CFG3 |       | 7                                                                                                                                                                                                           |