# **RENESAS** Low Skew 1 to 10 Clock Buffer

# 74FCT3807S

#### DATASHEET

#### Description

The 74FCT3807S is a low skew, single input to ten output, clock buffer. The 74FCT3807S has best in class additive phase Jitter of sub 50 fsec.

IDT makes many non-PLL and PLL based low skew output devices as well as Zero Delay Buffers to synchronize clocks. Contact us for all of your clocking needs.

#### **Features**

- · Low additive phase jitter RMS: 50fs

- Low skew outputs (50ps)

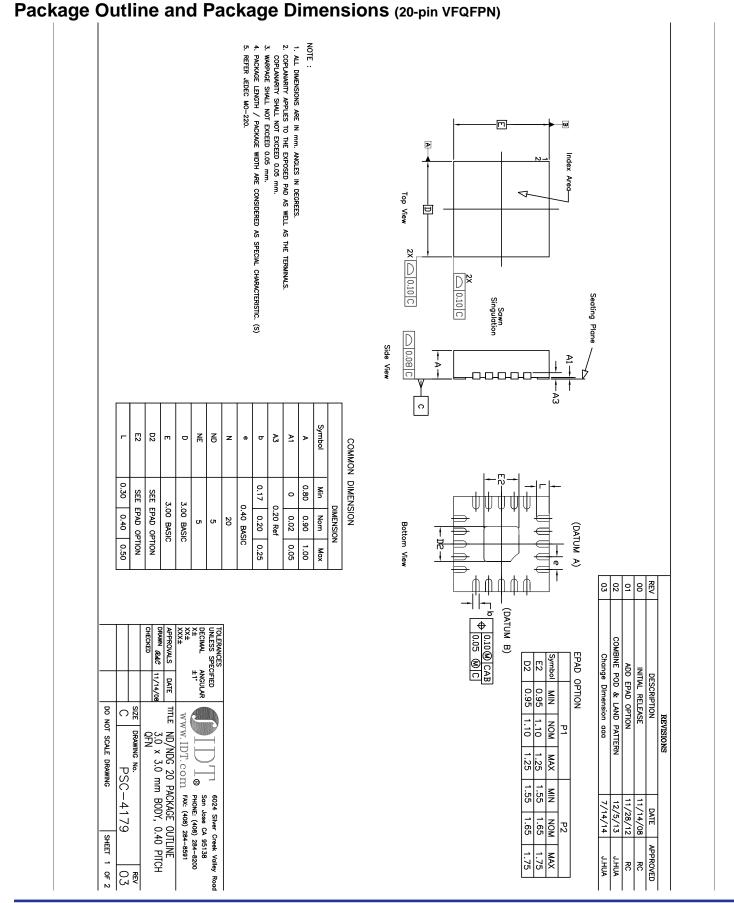

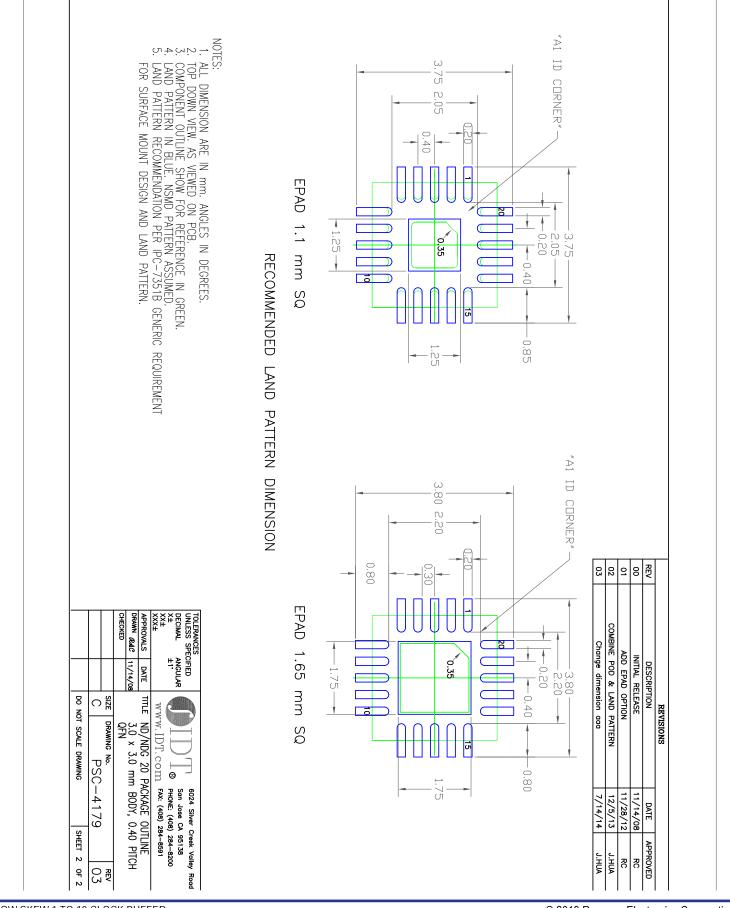

- Packaged in 20-pin TSSOP, SSOP, QSOP and VFQFPN packages, Pb (lead) free

- Operating voltages of 1.8V to 3.3V

- Input/Output clock frequency up to 200 MHz

- Advanced, low power CMOS process

- Extended temperature range (-40°C to +105°C)

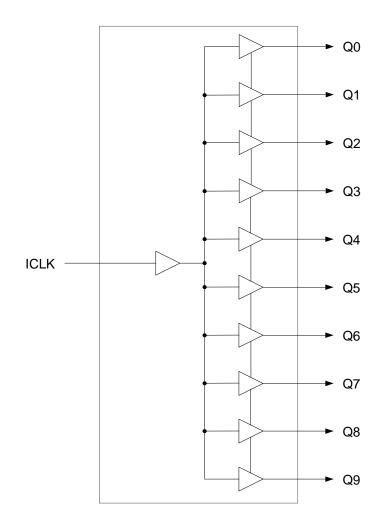

#### **Block Diagram**

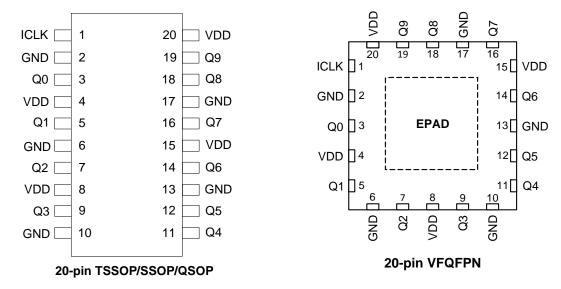

#### **Pin Assignments**

#### **Pin Descriptions**

| Pin<br>Number | Pin<br>Name | Pin<br>Type | Pin Description                      |

|---------------|-------------|-------------|--------------------------------------|

| 1             | ICLK        | Input       | Clock input.                         |

| 2             | GND         | Power       | Connect to ground.                   |

| 3             | Q0          | Output      | Clock output 0.                      |

| 4             | VDD         | Power       | Connect to +1.8V, +2.5 V, or +3.3 V. |

| 5             | Q1          | Output      | Clock output 1.                      |

| 6             | GND         | Power       | Connect to ground.                   |

| 7             | Q2          | Output      | Clock Output 2.                      |

| 8             | VDD         | Power       | Connect to +1.8V, +2.5 V, or +3.3 V. |

| 9             | Q3          | Output      | Clock Output 3.                      |

| 10            | GND         | Power       | Connect to ground.                   |

| 11            | Q4          | Output      | Clock Output 4.                      |

| 12            | Q5          | Output      | Clock Output 5.                      |

| 13            | GND         | Power       | Connect to ground.                   |

| 14            | Q6          | Output      | Clock Output 6.                      |

| 15            | VDD         | Power       | Connect to +1.8V, +2.5 V, or +3.3 V. |

| 16            | Q7          | Output      | Clock Output 7.                      |

| 17            | GND         | Power       | Connect to ground.                   |

| 18            | Q8          | Output      | Clock Output 8.                      |

| 19            | Q9          | Output      | Clock Output 9.                      |

| 20            | VDD         | Power       | Connect to +1.8V, +2.5 V, or +3.3 V. |

### **External Components**

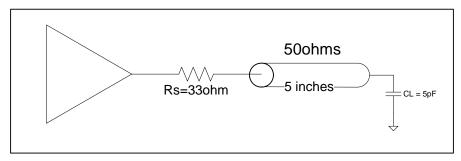

A minimum number of external components are required for proper operation. A decoupling capacitor of  $0.01\mu$ F should be connected between VDD pins and GND pins, as close to the device as possible. A  $33\Omega$  series terminating resistor may be used on each clock output if the trace is longer than 1 inch.

To achieve the low output skew that the 74FCT3807S is capable of, careful attention must be paid to board layout. Essentially, all ten outputs must have identical terminations, identical loads and identical trace geometries. If they do not, the output skew will be degraded. For example, using a  $30\Omega$  series termination on one output (with  $33\Omega$  on the others) will cause at least 15 ps of skew.

#### **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the 74FCT3807S. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Item                                     | Rating              |

|------------------------------------------|---------------------|

| Supply Voltage, VDD                      | 3.465V              |

| Outputs                                  | -0.5 V to VDD+0.5 V |

| ICLK                                     | 3.465V              |

| Ambient Operating Temperature (extended) | -40° to +105°C      |

| Storage Temperature                      | -65° to +150°C      |

| Junction Temperature                     | 125°C               |

| Soldering Temperature                    | 260°C               |

#### **Recommended Operation Conditions**

| Parameter                                         | Min.  | Тур. | Max.   | Units |

|---------------------------------------------------|-------|------|--------|-------|

| Ambient Operating Temperature (extended)          | -40   |      | +105   | °C    |

| Power Supply Voltage (measured in respect to GND) | +1.71 |      | +3.465 | V     |

#### **DC Electrical Characteristics**

(VDD = 1.8V, 2.5V, 3.3V)

| Parameter                | Symbol          | Conditions               | Min.    | Тур. | Max.    | Units |

|--------------------------|-----------------|--------------------------|---------|------|---------|-------|

| Operating Voltage        | VDD             |                          | 1.71    |      | 1.89    | V     |

| Input High Voltage, ICLK | V <sub>IH</sub> | Note 1                   | 0.7xVDD |      | VDD     | V     |

| Input Low Voltage, ICLK  | V <sub>IL</sub> | Note 1                   |         |      | 0.3xVDD | V     |

| Output High Voltage      | V <sub>OH</sub> | I <sub>OH</sub> = -10 mA | 1.3     |      |         | V     |

| Output Low Voltage       | V <sub>OL</sub> | I <sub>OL</sub> = 10 mA  |         |      | 0.35    | V     |

| Operating Supply Current | IDD             | No load, 135 MHz         |         | 35   |         | mA    |

| Nominal Output Impedance | Z <sub>O</sub>  |                          |         | 17   |         | Ω     |

| Input Capacitance        | C <sub>IN</sub> | ICLK                     |         | 5    |         | pF    |

VDD=1.8V ±5%, Ambient temperature -40° to +105°C, unless stated otherwise

Notes: 1. Nominal switching threshold is VDD/2

#### VDD=2.5 V ±5%, Ambient temperature -40° to +105°C, unless stated otherwise

| Parameter                | Symbol          | Conditions               | Min.    | Тур. | Max.    | Units |

|--------------------------|-----------------|--------------------------|---------|------|---------|-------|

| Operating Voltage        | VDD             |                          | 2.375   |      | 2.625   | V     |

| Input High Voltage, ICLK | V <sub>IH</sub> | Note 1                   | 0.7xVDD |      | VDD     | V     |

| Input Low Voltage, ICLK  | V <sub>IL</sub> | Note 1                   |         |      | 0.3xVDD | V     |

| Output High Voltage      | V <sub>OH</sub> | I <sub>OH</sub> = -16 mA | 1.8     |      |         | V     |

| Output Low Voltage       | V <sub>OL</sub> | I <sub>OL</sub> = 16 mA  |         |      | 0.5     | V     |

| Operating Supply Current | IDD             | No load, 135 MHz         |         | 45   |         | mA    |

| Nominal Output Impedance | Z <sub>O</sub>  |                          |         | 17   |         | Ω     |

| Input Capacitance        | C <sub>IN</sub> | ICLK                     |         | 5    |         | pF    |

#### VDD=3.3 V $\pm$ 5% , Ambient temperature -40° to +105°C, unless stated otherwise

| Parameter                | Symbol          | Conditions               | Min.    | Тур. | Max.    | Units |

|--------------------------|-----------------|--------------------------|---------|------|---------|-------|

| Operating Voltage        | VDD             |                          | 3.15    |      | 3.45    | V     |

| Input High Voltage, ICLK | V <sub>IH</sub> | Note 1                   | 0.7xVDD |      | VDD     | V     |

| Input Low Voltage, ICLK  | V <sub>IL</sub> | Note 1                   |         |      | 0.3xVDD | V     |

| Output High Voltage      | V <sub>OH</sub> | I <sub>OH</sub> = -25 mA | 2.2     |      |         | V     |

| Output Low Voltage       | V <sub>OL</sub> | I <sub>OL</sub> = 25 mA  |         |      | 0.7     | V     |

| Operating Supply Current | IDD             | No load, 135 MHz         |         | 55   |         | mA    |

| Nominal Output Impedance | Z <sub>O</sub>  |                          |         | 17   |         | Ω     |

| Input Capacitance        | C <sub>IN</sub> | ICLK                     |         | 5    |         | pF    |

#### **AC Electrical Characteristics**

(VDD = 1.8V, 2.5V, 3.3V)

| Parameter                         | Symbol                | Conditions                                             | Min. | Тур. | Max. | Units |

|-----------------------------------|-----------------------|--------------------------------------------------------|------|------|------|-------|

| Input Frequency                   |                       |                                                        | 0    |      | 200  | MHz   |

| Output Rise Time                  | t <sub>OR</sub>       | 0.36 to 1.44 V, C <sub>L</sub> =5 pF                   |      | 1.4  | 1.9  | ns    |

| Output Fall Time                  | t <sub>OF</sub>       | 1.44 to 0.36 V, C <sub>L</sub> =5 pF                   |      | 1.4  | 1.9  | ns    |

| Propagation Delay                 |                       | Note 1                                                 | 1.5  | 2.5  | 4    | ns    |

| Buffer Additive Phase Jitter, RMS |                       | 125MHz, Integration Range: 12kHz-20MHz                 |      |      | 0.05 | ps    |

| Output to Output Skew             |                       | Rising edges at VDD/2, Note 2                          |      | 50   | 65   | ps    |

| Device to Device Skew             |                       | Rising edges at VDD/2                                  |      |      | 200  | ps    |

| Start-up Time                     | t <sub>START-UP</sub> | Part start-up time for valid outputs after VDD ramp-up |      |      | 2    | ms    |

#### VDD = 1.8V ±5%, Ambient Temperature -40° to +105°C, unless stated otherwise

| VDD = 2.5 V ±5%, Ambien | Temperature -40° to +105°C | unless stated otherwise |

|-------------------------|----------------------------|-------------------------|

|-------------------------|----------------------------|-------------------------|

| Parameter                         | Symbol                | Conditions                                             | Min. | Тур. | Max. | Units |

|-----------------------------------|-----------------------|--------------------------------------------------------|------|------|------|-------|

| Input Frequency                   |                       |                                                        | 0    |      | 200  | MHz   |

| Output Rise Time                  | t <sub>OR</sub>       | 0.5 to 2.0 V, C <sub>L</sub> =5 pF                     |      | 1.0  | 1.5  | ns    |

| Output Fall Time                  | t <sub>OF</sub>       | 2.0 to 0.5 V, C <sub>L</sub> =5 pF                     |      | 1.0  | 1.5  | ns    |

| Propagation Delay                 |                       | Note 1                                                 | 1.8  | 2.5  | 4.5  | ns    |

| Buffer Additive Phase Jitter, RMS |                       | 125MHz, Integration Range: 12kHz-20MHz                 |      |      | 0.05 | ps    |

| Output to Output Skew             |                       | Rising edges at VDD/2, Note 2                          |      | 50   | 65   | ps    |

| Device to Device Skew             |                       | Rising edges at VDD/2                                  |      |      | 200  | ps    |

| Start-up Time                     | t <sub>START-UP</sub> | Part start-up time for valid outputs after VDD ramp-up |      |      | 2    | ms    |

#### VDD = 3.3 V ±5%, Ambient Temperature -40° to +105°C, unless stated otherwise

| Parameter                         | Symbol                | Conditions                                             | Min. | Тур. | Max. | Units |

|-----------------------------------|-----------------------|--------------------------------------------------------|------|------|------|-------|

| Input Frequency                   |                       |                                                        | 0    |      | 200  | MHz   |

| Output Rise Time                  | t <sub>OR</sub>       | 0.66 to 2.64 V, C <sub>L</sub> =5 pF                   |      | 0.6  | 1.0  | ns    |

| Output Fall Time                  | t <sub>OF</sub>       | 2.64 to 0.66 V, C <sub>L</sub> =5 pF                   |      | 0.6  | 1.0  | ns    |

| Propagation Delay                 |                       | Note 1                                                 | 1.5  | 2.5  | 4    | ns    |

| Buffer Additive Phase Jitter, RMS |                       | 125MHz, Integration Range: 12kHz-20MHz                 |      |      | 0.05 | ps    |

| Output to Output Skew             |                       | Rising edges at VDD/2, Note 2                          |      | 50   | 65   | ps    |

| Device to Device Skew             |                       | Rising edges at VDD/2                                  |      |      | 200  | ps    |

| Start-up Time                     | t <sub>START-UP</sub> | Part start-up time for valid outputs after VDD ramp-up |      |      | 2    | ms    |

Notes:

1. With rail to rail input clock

Between any 2 outputs with equal loading.

Duty cycle on outputs will match incoming clock duty cycle. Consult IDT for tight duty cycle clock generators.

#### **Test Load and Circuit**

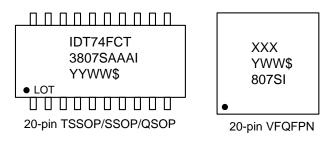

#### **Marking Diagrams**

Notes:

- 1. "LOT" denotes the lot number.

- 2. "XXX" denotes the lot number.

- 3. "YYWW" or "YWW" are the last digits of the year and week that the part was assembled.

- 4. "\$" denotes mark code.

- 5. "I" denotes extended temperature range device.

- 6. "AAA" denotes package code.

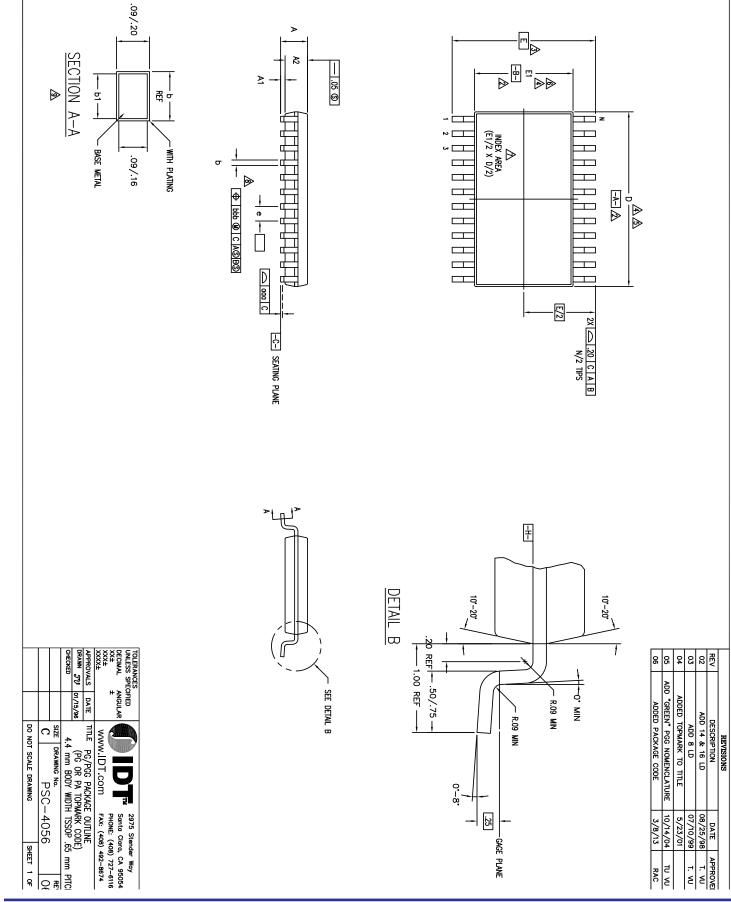

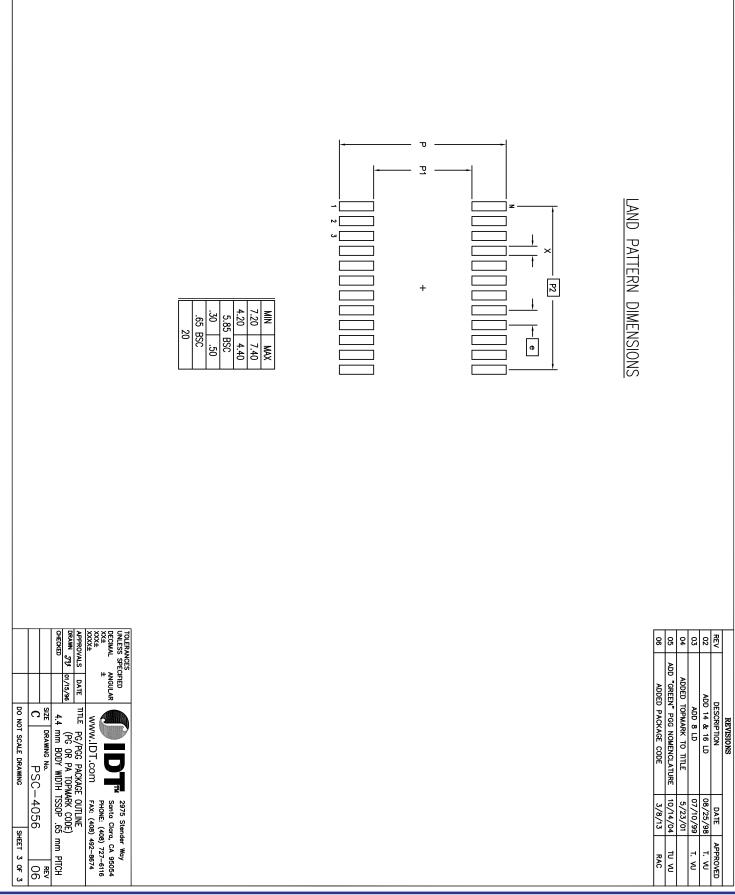

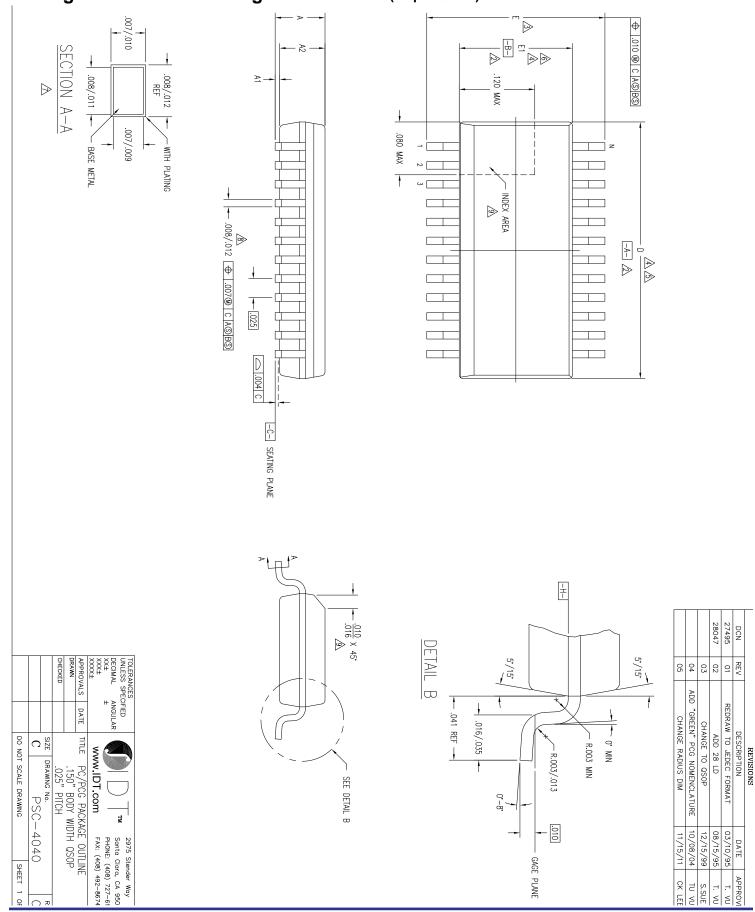

### Package Outline and Package Dimensions (20-pin TSSOP)

REVISION A 03/18/15

© 2019 Renesas Electronics Corporation

# Package Outline and Package Dimensions, cont. (20-pin TSSOP)

|   | =                                                                                                      | 10                                                                                                                                      | A                                                                                               |                                                                                                                                                                                                                                       | $\mathbb{A}$                                                                            | ß                                                                                                                                | A                                                                                                                                             | $\mathbb{A}$                                                | A                                                 |                                                  | -                                                            |        |  |

|---|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------|--------|--|

|   | THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95 REGISTRATION MO-153, VARIATION AA, AB-1, AB, AC, AD & AE | ALL DIMENSIONS ARE IN MILLIMETERS                                                                                                       | THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN .10 AND .25 mm FROM THE LEAD TIP | LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION, ALLOWABLE<br>DAMBAR PROTRUSION IS .08 mm IN EXCESS OF THE LEAD WIDTH DIMENSION<br>AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER<br>RADIUS OR THE FOOT | detail of Pin 1 identifier is optional but must be located within<br>The zone indicated | DIMENSION E1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD<br>FLASH OR PROTRUSIONS SHALL NOT EXCEED .25 mm PER SIDE | DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.<br>MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED .15 mm PER SIDE | DIMENSIONS D AND E1 ARE TO BE DETERMINED AT DATUM PLANE -H- | DIMENSION E TO BE DETERMINED AT SEATING PLANE -C- | DATUMSA_ ANDB_ TO BE DETERMINED AT DATUM PLANEH_ | ALL DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5M-1994 | NOTES: |  |

| - |                                                                                                        | APPROVALS DATE IIILE PG/PGG PACKAGE OUTLINE<br>DRAWN 272 07/5/96 (PG OR PA TOPMARK CODE)<br>GHEOKED 4.4 mm RODY WIDTH TSSOP 65 mm PITCH | ANGULAR<br>+<br>WW                                                                              | TOLERANCES<br>UNLESS SPECIFIED                                                                                                                                                                                                        |                                                                                         |                                                                                                                                  |                                                                                                                                               |                                                             |                                                   |                                                  |                                                              |        |  |

|  | -  | T   | .19 | .19 |     | 4.30    | -    | 6.40     | .80  | .05  | -   | MIN  |     | JEDEC |             |          |  |

|--|----|-----|-----|-----|-----|---------|------|----------|------|------|-----|------|-----|-------|-------------|----------|--|

|  | 20 | I   | I   | .22 | I   | .65 BSC | 4.40 | 6.40 BSC | 6.50 | 1.00 | I   | I    | NOM | AC    | C VARIATION | PG/PGG20 |  |

|  |    | .10 | .10 | .25 | .30 |         | 4.50 |          | 6.60 | 1.05 | .15 | 1.20 | MAX |       | ION         | 3G20     |  |

|  |    |     |     |     |     |         | 4,6  | ы        | 4,5  |      |     |      | m   |       | z           |          |  |

| 6                  | <b>0</b> 5                   | 04                     | 03       | 02             | REV         |           |

|--------------------|------------------------------|------------------------|----------|----------------|-------------|-----------|

| ADDED PACKAGE CODE | ADD "GREEN" PGG NOMENCLATURE | ADDED TOPMARK TO TITLE | ADD 8 LD | ADD 14 & 16 LD | DESCRIPTION | REVISIONS |

| 3/8/13             | 10/14/04                     | 5/23/01                | 07/10/99 | 08/25/98       | DATE        |           |

| RAC                | TU VU                        |                        | T. VU    | T. VU          | APPROVED    |           |

### Package Outline and Package Dimensions, cont. (20-pin TSSOP)

REVISION A 03/18/15

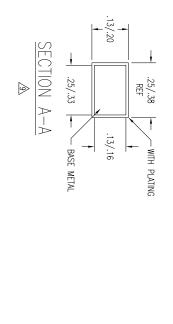

## Package Outline and Package Dimensions (20-pin QSOP)

LOW SKEW 1 TO 10 CLOCK BUFFER

© 2019 Renesas Electronics Corporation

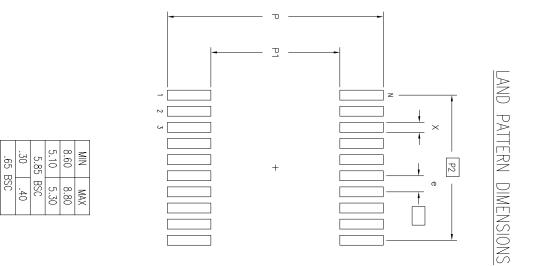

## Package Outline and Package Dimensions, cont. (20-pin QSOP)

| acnaye                                                                                                                                                                                                                                | 10                                                                           |                                                                                                                                        |                                                                                                                                                                                                                                     |                                                                                            | nayt<br>D                                                                                                                      |                                                                                                                                              |                                                         |                                                   |                                                  | ı <b>3</b> ,<br>_`                                           | cont.           | (20-pin QSOP)                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95 REGISTRATION MO-137,<br>VARIATION AB, AD, AE & AF. EXCEPTIONS: JEDEC DIMENSION A2 MAX IS .059                                                                                           | ALL DIMENSIONS ARE IN INCHES                                                 | THE CHAMFER ON THE PACKAGE BODY IS OPTIONAL. IF IT IS NOT PRESENT,<br>A VISUAL INDEX FEATURE MUST BE LOCATED WITHIN THE ZONE INDICATED | LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE<br>DAMBAR PROTRUSION IS .004 IN EXCESS OF THE LEAD WIDTH DIMENSION<br>AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER<br>RADIUS OR THE FOOT | THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN .005 AND .010 FROM LEAD TIP | DIMENSION E1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD<br>FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 PER SIDE | DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.<br>MOLD FLASH, PROTRUSIONS AND GATE BURRS SHALL NOT EXCEED .006 PER SIDE | DIMENSIONS D AND E1 ARE TO BE DETERMINED AT DATUM PLANE | DIMENSION E TO BE DETERMINED AT SEATING PLANE -C- | DATUMSA_ ANDB_ TO BE DETERMINED AT DATUM PLANEH_ | ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5M-1982 | NOTES:          | JEDEC         VARIATION         N           AD         T         T           MIN         NOM         MAX         E           .061         .064         .068         .0010           .055         .058         .061         11           .337         .342         .344         4,5           .230         .236         .244         3           .150         .155         .157         4,6           20         20 |

| APPROVALS     DATE     TITLE     PC/PCC     PC/CC     PC/CC       DRAWNQ     .150"     BODY     WIDTH     QSOP       OHEORED     SIZE     DRAWNQ NO.     .150"     PSC-4040       DO NOT SCALE DRAWNQ     DO NOT SCALE DRAWNQ     SHE | XX± ± WWW.IDT.com FAX: (408) 127-61<br>XXXX± WWW.IDT.com FAX: (408) 492-8674 | 위입                                                                                                                                     | 20                                                                                                                                                                                                                                  | .142 .150<br>.225 BSC<br>010 018                                                           | MIN MAX<br>.274 .282                                                                                                           |                                                                                                                                              |                                                         |                                                   |                                                  |                                                              | - P<br>- P<br>+ | AND PATTERN DIMENSIONS                                                                                                                                                                                                                                                                                                                                                                                             |

DATE 08/15/95 12/15/99 10/08/04 11/15/11

T. VU S.SUE TU VU CK LEE APPROVED

DCN 28047

> REVISIONS DESCRIPTION

02 02 02 02 05

ADD 28 LD CHANGE TO GSOP ADD "GREEN" PCG NOMENCLATURE CHANGE RADIUS DIM

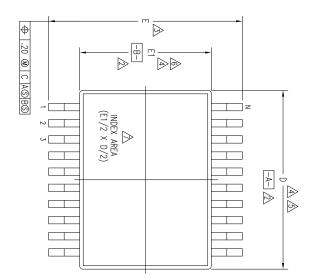

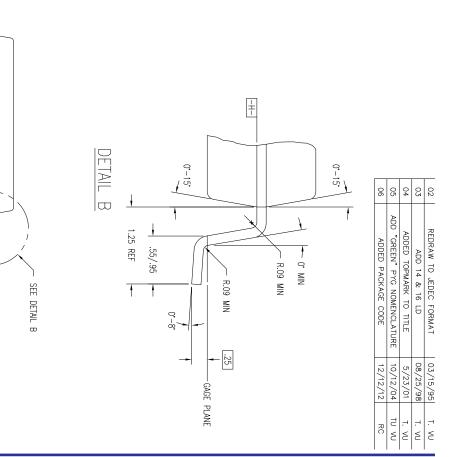

## Package Outline and Package Dimensions (20-pin SSOP)

>L\_I

## Package Outline and Package Dimensions, cont. (20-pin SSOP)

|             | NOTES:                                                                                                                                                                                                                                |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>→</b>    | ALL DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5M-1994                                                                                                                                                                          |

|             | DATUMS -A- AND -B- TO BE DETERMINED AT DATUM PLANE -H-                                                                                                                                                                                |

| 3           | DIMENSION E TO BE DETERMINED AT SEATING PLANE -C-                                                                                                                                                                                     |

| A           | DIMENSIONS D AND E1 ARE TO BE DETERMINED AT DATUM PLANE                                                                                                                                                                               |

| B           | DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.<br>MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED .20 mm PER SIDE                                                                                         |

|             | DIMENSION E1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED .20 mm PER SIDE                                                                                                         |

| $\geqslant$ | DETAIL OF PIN 1 IDENTIFIER IS OPTIONAL BUT MUST BE LOCATED WITHIN THE ZONE INDICATED                                                                                                                                                  |

|             | LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE<br>DAMBAR PROTRUSION IS .13 mm IN EXCESS OF THE LEAD WIDTH DIMENSION<br>AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER<br>RADIUS OR THE FOOT |

|             | THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN .10 AND .25 mm FROM THE LEAD TIP                                                                                                                                       |

| 10          | ALL DIMENSIONS ARE IN MILLIMETERS                                                                                                                                                                                                     |

| 11          | THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95 REGISTRATION MO-150, VARIATION AB, AC, AE, AG & AH                                                                                                                                      |

|    | 5.20 | 7.65 | 7.07 | 1.68 | .05 | 1.73 | MIN |    | JEDEC     |          |

|----|------|------|------|------|-----|------|-----|----|-----------|----------|

| 20 | 5.30 | 7.80 | 7.20 | 1.73 | .13 | 1.86 | NON | AE | VARIATION | PY/PYG20 |

|    | 5.38 | 7.90 | 7.33 | 1.78 | .21 | 1.99 | MAX |    | ION       | G20      |

|    | 4,6  | Ы    | 4,5  |      |     |      | m   | -0 | z         |          |

| C       | SIZE        | CHECKED               | DRAWN                 | APPROVALS DATE TITLE         | XXX± W           | DECIMAL ANGULAR | UNLESS SPECIFIED |

|---------|-------------|-----------------------|-----------------------|------------------------------|------------------|-----------------|------------------|

| PSC-403 | DRAWING No. | 5.3 mm BODY WIDTH SSC | (PY OR PV TOPMARK COL | TITLE PY/PYG PACKAGE OUTLINE | www.IDT.com FAX: | PHON<br>PHON    |                  |

02

REDRAW TO JEDEC FORMAT

03/15

03

ADD 14 & 16 LD

08/25

04

ADDED TOPMARK TO TITLE

5/23

05

ADD "GREEN" PYG NOMENCLATURE

10/12

06

ADDED PACKAGE CODE

12/12

20

## Package Outline and Package Dimensions, cont. (20-pin SSOP)

LOW SKEW 1 TO 10 CLOCK BUFFER

| ADDED PACKAGE CODE | ADD "GREEN" PYG NOMENCLATURE | ADDED TOPMARK TO TITLE | ADD 14 & 16 LD | REDRAW TO JEDEC FORMAT | ADD 28 LD | INITIAL RELEASE | DESCRIPTION | A VALE I ANV A V A INV |

|--------------------|------------------------------|------------------------|----------------|------------------------|-----------|-----------------|-------------|------------------------|

| 12/12/12           | 10/12/04                     | 5/23/01                | 08/25/98       | 03/15/95               | 07/27/93  | 04/15/91        | DATE        |                        |

| RC                 | TU VU                        | T. VU                  | T. VU          | T. VU                  | T. VU     | T. VU           | APPROVED    |                        |

REV 00 01 02 02 03 05

## **Ordering Information**

| Part / Order Number | Marking    | Shipping Packaging | Package       | Temperature    |

|---------------------|------------|--------------------|---------------|----------------|

| 74FCT3807SNDGI      | see page 6 | Tubes              | 20-pin VFQFPN | -40° to +105°C |

| 74FCT3807SNDGI8     |            | Tape and Reel      | 20-pin VFQFPN | -40° to +105°C |

| 74FCT3807SPGGI      |            | Tubes              | 20-pin TSSOP  | -40° to +105°C |

| 74FCT3807SPGGI8     |            | Tape and Reel      | 20-pin TSSOP  | -40° to +105°C |

| 74FCT3807SQGI       |            | Tubes              | 20-pin QSOP   | -40° to +105°C |

| 74FCT3807SQGI8      |            | Tape and Reel      | 20-pin QSOP   | -40° to +105°C |

| 74FCT3807SPYGI      |            | Tubes              | 20-pin SSOP   | -40° to +105°C |

| 74FCT3807SPYGI8     |            | Tape and Reel      | 20-pin SSOP   | -40° to +105°C |

"G" after the two-letter package code denotes Pb-Free configuration, RoHS compliant.

## **Revision History**

| Rev. | Date     | Originator   | Description of Change |

|------|----------|--------------|-----------------------|

| А    | 03/18/15 | B. Chandhoke | Initial release.      |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.