# FAST CMOS BUFFER/CLOCK DRIVER

## IDT74FCT810BT/CT

### **FEATURES:**

- 0.5 MICRON CMOS Technology

- Guaranteed low skew < 600ps (max.)</li>

- Very low duty cycle distortion < 700ps (max.)</li>

- · Low CMOS levels

- · TTL compatible inputs and outputs

- · TTL level output voltage swings

- High drive: -32mA loh, +48mA lol

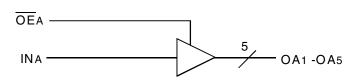

- · Two independent output banks with 3-state control:

- One 1:5 inverting bank

- One 1:5 non-inverting bank

- · Available in QSOP, SSOP, and SOIC packages

### **DESCRIPTION:**

The 74FCT810T is a dual bank inverting/ non-inverting clock driver built using advanced dual metal CMOS technology. It consists of two banks of drivers, one inverting and one non-inverting. Each bank drives five output buffers from a standard TTL-compatible input. The FCT810T has low output skew, pulse skew and package skew. Inputs are designed with hysteresis circuitry for improved noise immunity. The outputs are designed with TTL output levels and controlled edge rates to reduce signal noise. The part has multiple grounds, minimizing the effects of ground inductance.

## FUNCTIONAL BLOCK DIAGRAM

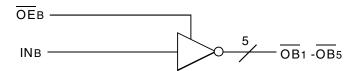

## **PIN CONFIGURATION**

QSOP/ SOIC/ SSOP TOP VIEW

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

# ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Description                          | Max         | Unit |

|--------|--------------------------------------|-------------|------|

| VTERM  | Terminal Voltage with Respect to GND | –0.5 to +7  | V    |

| Tstg   | Storage Temperature                  | -65 to +150 | °C   |

| lout   | DC Output Current                    | -60 to +120 | mA   |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

# **CAPACITANCE** (TA = $+25^{\circ}$ C, f = 1.0MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Тур. | Max. | Unit |

|--------|--------------------------|------------|------|------|------|

| CIN    | Input Capacitance        | VIN = 0V   | 4.5  | 6    | pF   |

| Соит   | Output Capacitance       | Vout = 0V  | 5.5  | 8    | pF   |

#### NOTE:

1. This parameter is measured at characterization but not tested.

## **PIN DESCRIPTION**

| Pin Names | Description                               |

|-----------|-------------------------------------------|

| OEA, OEB  | 3-State Output-Enable Inputs (Active LOW) |

| INA, INB  | Clock Inputs                              |

| ОАх, ОВХ  | Clock Outputs                             |

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified: Commercial:  $Ta = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $Vcc = 5V \pm 5\%$

| Symbol               | Parameter                       | Test Conditions <sup>(1)</sup> |                                     | Min.     | Typ. <sup>(2)</sup> | Max. | Unit |

|----------------------|---------------------------------|--------------------------------|-------------------------------------|----------|---------------------|------|------|

| VIH                  | Input HIGH Level (Input pins)   | Guaranteed Logic HIGH          | Guaranteed Logic HIGH Level         |          | _                   | _    | V    |

| VIL                  | Input LOW Level                 | Guaranteed Logic LOW           | Level                               | <u> </u> | _                   | 0.8  | V    |

| Іін                  | Input HIGH Current (Input pins) | Vcc = Max.                     | VI = 2.7V                           | _        | _                   | ±1   | μΑ   |

| liL                  | Input LOW Current (Input pins)  | Vcc = Max.                     | VI = 0.5V                           | <u> </u> | _                   | ±1   | μΑ   |

| lozh                 | High Impedance Output Current   | Vcc = Max.                     | Vo = 2.7V                           | _        | _                   | ±1   | μΑ   |

| lozL                 | (3-State Output pins)           |                                | Vo = 0.5V                           | T -      | _                   | ±1   |      |

| lı                   | Input HIGH Current              | Vcc = Max., VI = Vcc (Max.)    |                                     | _        | _                   | ±1   | μΑ   |

| Vik                  | Clamp Diode Voltage             | VCC = Min., IIN = -18mA        |                                     | _        | -0.7                | -1.2 | V    |

| los                  | Short Circuit Current           | Vcc = Max., Vo = GNE           | Vcc = Max., Vo = GND <sup>(3)</sup> |          | -120                | -225 | mA   |

| Vон                  | Output HIGH Voltage             | Vcc = Min.                     | Iон = -15mA                         | 2.4      | 3.3                 | _    | V    |

|                      |                                 | VIN = VIH or VIL               | $IOH = -32mA^{(4)}$                 | 2        | 3                   | _    |      |

| Vol                  | Output LOW Voltage              | Vcc = Min.                     | IoL = 48mA                          | <u> </u> | 0.3                 | 0.55 | V    |

|                      |                                 | VIN = VIH or VIL               |                                     |          |                     |      |      |

| loff                 | Input/Output Power Off Leakage  | Vcc = 0V, Vin or Vo≤           | Vcc = 0V, Vin or Vo ≤4.5V           |          | _                   | ±1   | μΑ   |

| Vн                   | Input Hysteresis for all inputs | _                              |                                     | _        | 150                 | _    | mV   |

| ICCL<br>ICCH<br>ICCZ | Quiescent Power Supply Current  | Vcc = Max., Vin = GNE          | O or Vcc                            | _        | 5                   | 500  | μА   |

#### NOTES

- 1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. Typical values are at Vcc = 5V, +25°C ambient.

- 3. Not more than one output should be shorted at one time. Duration of the test should not exceed one second.

- 4. Duration of the condition should not exceed one second.

# **POWER SUPPLY CHARACTERISTICS**

| Symbol | Parameter                                   | Test Conditions <sup>(1)</sup> |            | Min. | Typ. <sup>(2)</sup> | Max.                | Unit   |

|--------|---------------------------------------------|--------------------------------|------------|------|---------------------|---------------------|--------|

| Δlcc   | Quiescent Power Supply Current              | Vcc = Max.                     |            |      | 0.5                 | 2                   | mA     |

|        | TTL Inputs HIGH                             | $VIN = 3.4V^{(3)}$             | _          |      |                     |                     |        |

| ICCD   | Dynamic Power Supply Current <sup>(4)</sup> | Vcc = Max.                     | VIN = VCC  | _    | 60                  | 100                 | μA/MHz |

|        |                                             | Outputs Open                   | VIN = GND  |      |                     |                     |        |

|        |                                             | OEA = OEB = GND                |            |      |                     |                     |        |

|        |                                             | 50% Duty Cycle                 |            |      |                     |                     |        |

| Ic     | Total Power Supply Current <sup>(6)</sup>   | Vcc = Max.                     | VIN = VCC  | _    | 7.5                 | 13                  | mA     |

|        |                                             | Outputs Open                   | VIN = GND  |      |                     |                     |        |

|        |                                             | fo = 25MHz                     |            |      |                     |                     |        |

|        |                                             | 50% Duty Cycle                 | VIN = 3.4V | _    | 7.8                 | 14                  |        |

|        |                                             | OEA = GND, OEB = VCC           | VIN = GND  |      |                     |                     |        |

|        |                                             | Vcc = Max.                     | VIN = VCC  | _    | 30                  | 50.5 <sup>(5)</sup> |        |

|        |                                             | Outputs Open                   | VIN = GND  |      |                     |                     |        |

|        |                                             | fo = 50MHz                     |            |      |                     |                     |        |

|        |                                             | 50% Duty Cycle                 | VIN = 3.4V | _    | 30.5                | 52.5 <sup>(5)</sup> |        |

|        |                                             | OEA = OEB = GND                | VIN = GND  |      |                     |                     |        |

#### NOTES:

- 1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. Typical values are at Vcc = 5V, +25°C ambient.

- 3. Per TTL driven input (VIN = 3.4V); all other inputs at Vcc or GND.

- 4. This parameter is not directly testable, but is derived for use in Total Power Supply calculations.

- 5. Values for these conditions are examples of the Ic formula. These limits are guaranteed but not tested.

- 6. IC = IQUIESCENT + INPUTS + IDYNAMIC

- $IC = ICC + \Delta ICC DHNT + ICCD (foNo)$

- Icc = Quiescent Current (IccL, IccH and Iccz)

- $\Delta Icc$  = Power Supply Current for a TTL High Input (VIN = 3.4V)

- DH = Duty Cycle for TTL Inputs High

- NT = Number of TTL Inputs at DH

- ICCD = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

- fo = Output Frequency

- No = Number of Outputs at fo

- All currents are in milliamps and all frequencies are in megahertz.

# **SWITCHING CHARACTERISTICS OVER OPERATING RANGE**(3,4)

|         |                                                  |                           | FCT810BT            |      | FCT810CT            |      |      |

|---------|--------------------------------------------------|---------------------------|---------------------|------|---------------------|------|------|

| Symbol  | Parameter                                        | Conditions <sup>(1)</sup> | Min. <sup>(2)</sup> | Max. | Min. <sup>(2)</sup> | Max. | Unit |

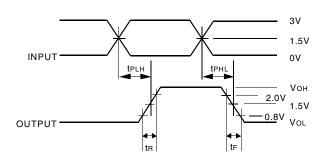

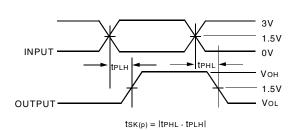

| tPLH    | Propagation Delay                                | CL = 50pF                 | 1.5                 | 4.5  | 1.5                 | 4.3  | ns   |

| tphl    | INA to OAx, INA to OBX                           | $RL = 500\Omega$          |                     |      |                     |      |      |

| ₽       | Output Rise Time                                 |                           | _                   | 1.5  | _                   | 1.5  | ns   |

| tF      | Output Fall Time                                 |                           | _                   | 1.5  | _                   | 1.5  | ns   |

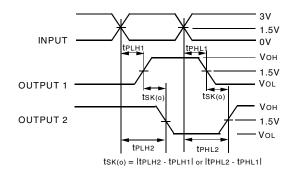

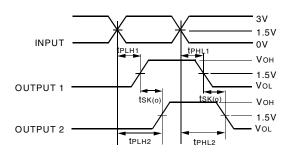

| tsk1(0) | Output skew (same bank): skew between outputs of |                           | _                   | 0.5  | _                   | 0.3  | ns   |

|         | same bank and same package (same transition)     |                           |                     |      |                     |      |      |

| tsk2(0) | Output skew (all banks): skew between outputs of |                           | _                   | 0.7  | _                   | 0.6  | ns   |

|         | all banks of same package (inputs tied together) |                           |                     |      |                     |      |      |

| tsk(p)  | Pulse skew: skew between opposite transitions    |                           | _                   | 0.7  | _                   | 0.7  | ns   |

|         | of same output ( tphl tplh )                     |                           |                     |      |                     |      |      |

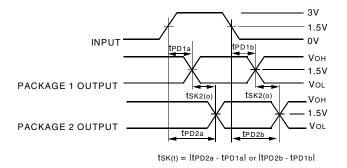

| tsk(T)  | Package skew: skew between outputs of different  |                           | _                   | 1.2  | _                   | 1    | ns   |

|         | packages at same power supply voltage,           |                           |                     |      |                     |      |      |

|         | temperature, package type and speed grade        |                           |                     |      |                     |      |      |

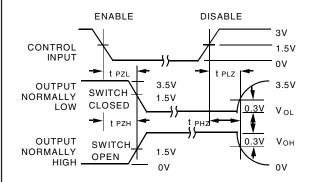

| tPZL    | Output Enable Time                               |                           | 1.5                 | 6    | 1.5                 | 5    | ns   |

| tpzh    | OEA to OAx, OEB to OBX                           |                           |                     |      |                     |      |      |

| tPLZ    | Output Disable Time                              |                           | 1.5                 | 6    | 1.5                 | 5    | ns   |

| tphz    | OEA to OAx, OEB to OBX                           |                           |                     |      |                     |      |      |

#### NOTES:

- 1. See test circuits and waveforms.

- 2. Minimum limits are guaranteed but not tested on Propagation Delays.

- 3. tplh, tphl, tsk(t) are production tested. All other parameters guaranteed but not production tested.

4. Propagation delay range indicated by Min. and Max. limit is due to Vcc, operating temperature and process parameters. These propagation delay limits do not imply skew.

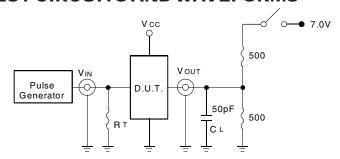

# **TEST CIRCUITS AND WAVEFORMS**

Test Circuit for All Outputs

Package Delay

Output Skew (All Banks) - tSK2(0)

Package Skew - tsk(T)

### NOTES:

- 1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH

- 2. Pulse Generator for All Pulses: Rate ≤1.0MHz; tF ≤2.5ns; tR ≤2.5ns

# **SWITCH POSITION**

| Test                        | Switch |

|-----------------------------|--------|

| Disable LOW<br>Enable LOW   | Closed |

| Disable HIGH<br>Enable HIGH | GND    |

#### **DEFINITIONS:**

- CL = Load capacitance: includes jig and probe capacitance.

- RT = Termination resistance: should be equal to ZouT of the Pulse Generator.

tsk(o) = |tplh2 - tplh1| or |tphl2 - tphl1|

Output Skew (Same Bank) - tsk1(0)

Pulse Skew - tsk(P)

Enable and Disable Times

#### NOTE:

1. Package 1 and Package 2 are same device type and speed grade.

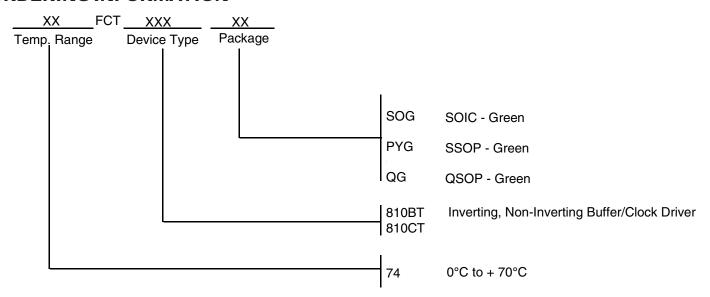

# **ORDERING INFORMATION**

### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.