# 1:1 AND 1:2 REGISTERED BUFFER WITH 1.8V SSTL I/O

## IDT74SSTU32864/ A/C/D/G

#### **FEATURES:**

- · 1:1 and 1:2 registered buffer

- 1.8V Operation

- SSTL\_18 style clock and data inputs

- · Differential CLK input

- · Control inputs compatible with LVCMOS levels

- · Flow-through architecture for optimum PCB design

- Latch-up performance exceeds 100mA

- ESD >2000V per MIL-STD-883, Method 3015; >200V using machine model (C = 200pF, R = 0)

- Maximum operating frequency: 340MHz

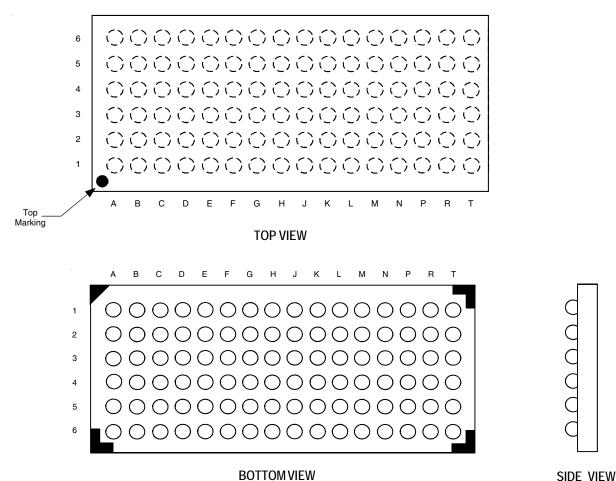

- Available in 96-pin LFBGA package

#### **APPLICATIONS:**

- Ideally suited for DDR2-400/533 (PC2 3200/ 4200) registered DIMM applications

- Along with CSPU877/A/D, zero delay PLL clock buffer, provides complete solution for DDR2-400/533 DIMMs

- SSTU32864 is optimized for DDR2 Raw cards B and C

- SSTU32864A is optimized for DDR2 Raw card A

- SSTU32864C/D/G are optimized for DDR2 Raw cards A, B, and C

- SSTU32864G has control pins for output slew rate control

#### **DESCRIPTION:**

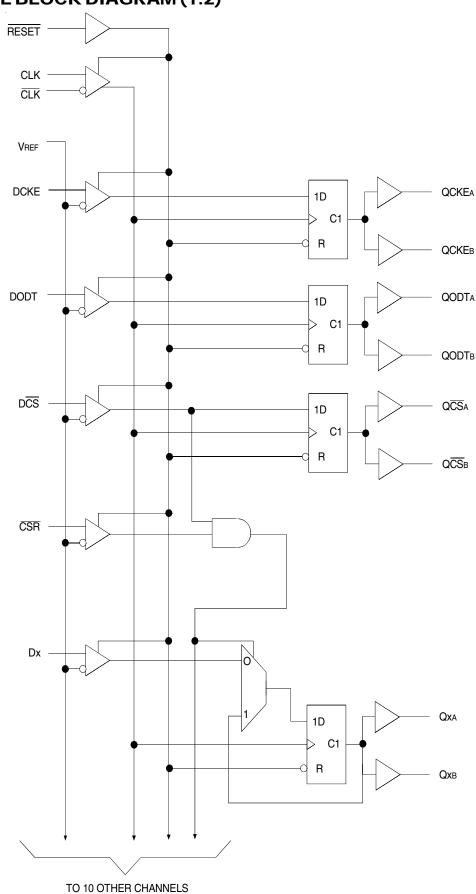

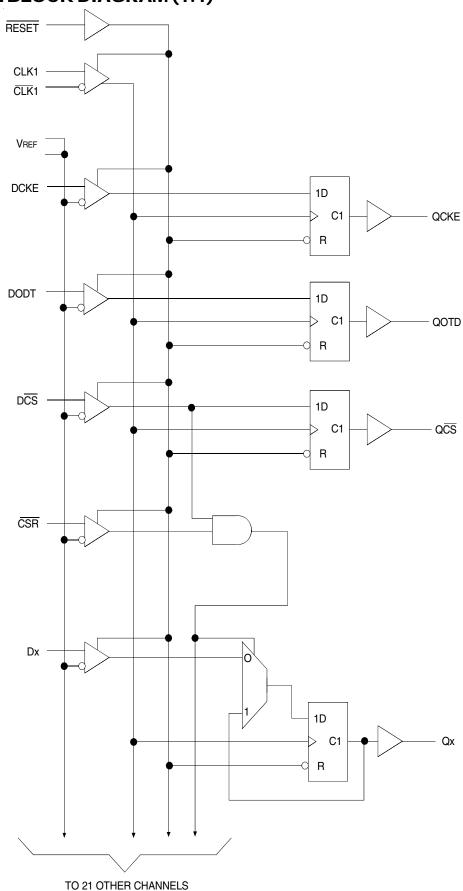

The SSTU32864 is a 25-bit 1:1/14-bit 1:2 configurable registered buffer designed for 1.7V to 1.9V VDD operation. All clock and data inputs are compatible with the JEDEC standard for SSTL\_18. The control inputs are LVCMOS. All outputs are 1.8V CMOS drivers that have been optimized to drive the DDR2 DIMM load.

The SSTU32864 operates from a differential clock (CLK and  $\overline{\text{CLK}}$ ). Data are registered at the crossing of CLK going high and  $\overline{\text{CLK}}$  going low.

The C0 input controls the pinout configuration of the 1:2 pinout from the A configuration (when low) to B configuration (when high). The C1 input controls the configuration from the 25-bit 1:1 (when low) to 14-bit 1:2 (when high).

This device supports low-power standby operation. When the reset input  $(\overline{\text{RESET}})$  is low, the differential input receivers are disabled, and undriven (floating) data, clock, and reference voltage (VREF) inputs are allowed. In addition, when  $\overline{\text{RESET}}$  is low all registers are reset, and all outputs are forced low. The LVCMOS  $\overline{\text{RESET}}$  and Cx inputs must always be held at a valid logic high or low level.

To ensure defined outputs from the register before a stable clock has been supplied, RESET must be held in the low state during power up.

In the DDR2 DIMM application,  $\overline{\text{RESET}}$  is specified to be completely asynchronous with respect to CLK and  $\overline{\text{CLK}}$ . Therefore, no timing relationship can be guaranteed between the two. When entering reset, the register will be cleared and the outputs will be driven low quickly, relative to the time to disable the differential input receivers. However, when coming out of a reset, the register will become active quickly, relative to the time to enable the differential input receivers. As long as the data inputs are low, and the clock is stable during the time from the low-to-high transition of  $\overline{\text{RESET}}$  until the input receivers are fully enabled, the design of the SSTU32864 must ensure that the outputs will remain low, thus ensuring no glitches on the outputs.

The device monitors both  $\overline{DCS}$  and  $\overline{CSR}$  inputs and will gate the outputs from changing states when both  $\overline{DCS}$  and  $\overline{CSR}$  inputs are high. If either  $\overline{DCS}$  or  $\overline{CSR}$  input is low, the device will function normally. The  $\overline{RESET}$  input has priority over the  $\overline{DCS}$  control and will force the inputs low. If the  $\overline{DCS}$  control functionality is not desired, then the  $\overline{CSR}$  input can be hardwired to ground, in which case the set-up time requirement for  $\overline{DCS}$  would be the same as for the other D data inputs.

The SSTU32864G has two slew control pins (ZoH and ZoL) used to optimize the signal integrity on the DIMM.

## **FUNCTIONAL BLOCK DIAGRAM (1:2)**

## **PIN CONFIGURATION (TYPE A)**

| 6 | QCKEB | Q2B | Q3B | QODTB | Q5B | Q6B | C0    | QCSB | Zol | Q8B | Q9B | Q10B | Q11B | Q12B | Q13B | Q14B |

|---|-------|-----|-----|-------|-----|-----|-------|------|-----|-----|-----|------|------|------|------|------|

| 5 | QCKEA | Q2A | Q3A | QODTA | Q5A | Q6A | C1    | QCSA | Zон | Q8A | Q9A | Q10A | Q11A | Q12A | Q13A | Q14A |

| 4 | VDD   | GND | VDD | GND   | VDD | GND | VDD   | GND  | VDD | GND | VDD | GND  | VDD  | GND  | VDD  | VDD  |

| 3 | VREF  | GND | VDD | GND   | VDD | GND | VDD   | GND  | VDD | GND | VDD | GND  | VDD  | GND  | VDD  | VREF |

| 2 | NC    | NC  | NC  | NC    | NC  | NC  | RESET | DCS  | CSR | NC  | NC  | NC   | NC   | NC   | NC   | NC   |

| 1 | DCKE  | D2  | D3  | DODT  | D5  | D6  | NC    | CLK  | CLK | D8  | D9  | D10  | D11  | D12  | D13  | D14  |

|   | A     | В   | С   | D     | Е   | F   | G     | Н    | J   | K   | L   | М    | N    | Р    | R    | Т    |

96-PIN LFBGA 1:2 REGISTER (TYPE A, FRONTSIDE) TOP VIEW

## **PIN CONFIGURATION (TYPE B)**

| 6 | Q1B  | Q2B | Q3B | Q4B | Q5B | Q6B | C0    | QCSB | ZOL | Q8B | Q9B | Q10B | QODTB | Q12B | Q13B | QCKEB |

|---|------|-----|-----|-----|-----|-----|-------|------|-----|-----|-----|------|-------|------|------|-------|

| 5 | Q1A  | Q2A | Q3A | Q4A | Q5A | Q6A | C1    | QCSA | Zон | Q8A | Q9A | Q10A | QODTA | Q12A | Q13A | QCKEA |

| 4 | VDD  | GND | VDD | GND | VDD | GND | VDD   | GND  | VDD | GND | VDD | GND  | VDD   | GND  | VDD  | VDD   |

| 3 | VREF | GND | VDD | GND | VDD | GND | VDD   | GND  | VDD | GND | VDD | GND  | VDD   | GND  | VDD  | VREF  |

| 2 | NC   | NC  | NC  | NC  | NC  | NC  | RESET | DCS  | CSR | NC  | NC  | NC   | NC    | NC   | NC   | NC    |

| 1 | D1   | D2  | D3  | D4  | D5  | D6  | NC    | CLK  | CLK | D8  | D9  | D10  | DODT  | D12  | D13  | DCKE  |

|   | A    | В   | С   | D   | Е   | F   | G     | Н    | J   | K   | L   | М    | N     | Р    | R    | Т     |

96-PIN LFBGA 1:2 REGISTER (TYPE B, BACKSIDE) TOP VIEW

## **FUNCTIONAL BLOCK DIAGRAM (1:1)**

#### **PIN CONFIGURATION**

| 6 | NC   | Q15 | Q16 | NC   | Q17 | Q18 | CO    | NC  | Zol | Q19 | Q20 | Q21 | Q22 | Q23 | Q24 | Q25  |

|---|------|-----|-----|------|-----|-----|-------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| 5 | QCKE | Q2  | Q3  | QODT | Q5  | Q6  | C1    | QCS | Zон | Q8  | Q9  | Q10 | Q11 | Q12 | Q13 | Q14  |

| 4 | VDD  | GND | VDD | GND  | VDD | GND | VDD   | GND | VDD | GND | VDD | GND | VDD | GND | VDD | VDD  |

| 3 | VREF | GND | VDD | GND  | VDD | GND | VDD   | GND | VDD | GND | VDD | GND | VDD | GND | VDD | VREF |

| 2 | NC   | D15 | D16 | NC   | D17 | D18 | RESET | DCS | CSR | D19 | D20 | D21 | D22 | D23 | D24 | D25  |

| 1 | DCKE | D2  | D3  | DODT | D5  | D6  | NC    | CLK | CLK | D8  | D9  | D10 | D11 | D12 | D13 | D14  |

|   | Α    | В   | С   | D    | E   | F   | G     | Н   | J   | K   | L   | М   | N   | Р   | R   |      |

<sup>\*</sup>Rows 3 and 4 are reserved for VDD and GND.

96-PIN LFBGA 1:1 REGISTER **TOP VIEW**

## 96 BALL LFBGA PACKAGE ATTRIBUTES

## FUNCTION TABLE (EACH FLIP-FLOP) (1)

|       |               |               | Inputs        |               |                | Qx                            | Q <b>CS</b> x                 | QODTx, QCKEx                  |

|-------|---------------|---------------|---------------|---------------|----------------|-------------------------------|-------------------------------|-------------------------------|

| RESET | D <b>CS</b>   | CSR           | CLK           | CLK           | Dx, DODT, DCKE | Outputs                       | Output                        | Outputs                       |

| Н     | L             | L             | <b>↑</b>      | $\downarrow$  | L              | L                             | L                             | L                             |

| Н     | L             | L             | <b>↑</b>      | <b>↓</b>      | Н              | Н                             | L                             | Н                             |

| Н     | L             | L             | L or H        | L or H        | Х              | Q <sub>0</sub> <sup>(2)</sup> | O <sub>0</sub> <sup>(2)</sup> | O <sub>0</sub> <sup>(2)</sup> |

| Н     | L             | Н             | 1             | $\downarrow$  | L              | L                             | L                             | L                             |

| Н     | L             | Н             | <b>↑</b>      | $\downarrow$  | Н              | Н                             | L                             | Н                             |

| Н     | L             | Н             | L or H        | L or H        | Х              | Q <sub>0</sub> <sup>(2)</sup> | O <sub>0</sub> <sup>(2)</sup> | O <sub>0</sub> <sup>(2)</sup> |

| Н     | Н             | L             | 1             | $\downarrow$  | L              | L                             | Н                             | L                             |

| Н     | Н             | L             | 1             | $\downarrow$  | Н              | Н                             | Н                             | Н                             |

| Н     | Н             | L             | L or H        | L or H        | Χ              | Q <sub>0</sub> <sup>(2)</sup> | O <sub>0</sub> <sup>(2)</sup> | O <sub>0</sub> <sup>(2)</sup> |

| Н     | Н             | Н             | <b>↑</b>      | <b>↓</b>      | L              | O <sub>0</sub> <sup>(2)</sup> | Н                             | L                             |

| Н     | Н             | Н             | <b>↑</b>      | $\downarrow$  | Н              | O <sub>0</sub> <sup>(2)</sup> | Н                             | Н                             |

| Н     | Н             | Н             | L or H        | L or H        | Х              | Q <sub>0</sub> <sup>(2)</sup> | Q <sub>0</sub> <sup>(2)</sup> | O <sub>0</sub> <sup>(2)</sup> |

| L     | X or Floating  | L                             | L                             | L                             |

#### NOTES:

1. H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

↑ = LOW to HIGH

$\downarrow$  = HIGH to LOW

2. Output level before the indicated steady-state conditions were established.

#### **MODE SELECT**

| C <sub>0</sub> | C1 | Device Mode                         |

|----------------|----|-------------------------------------|

| 0              | 0  | 1:125-bit to 25-bit                 |

| 0              | 1  | 1:214-bit to 28-bit, Front (Type A) |

| 1              | 0  | Reserved                            |

| 1              | 1  | 1:2 14-bit to 28-bit, Back (Type B) |

## **OUTPUT CONTROL (SSTU32864G)**

| <b>Z</b> oh | Zol | Output Slew Rate |

|-------------|-----|------------------|

| 0           | 0   | Standard         |

| 0           | 1   | Highest          |

| 1           | 0   | Low              |

| 1           | 1   | High             |

## **ABSOLUTE MAXIMUM RATINGS (1)**

| Symbol              | Description             |                             | Max.             | Unit |

|---------------------|-------------------------|-----------------------------|------------------|------|

| Vdd                 | Supply Voltage Range    |                             | -0.5 to 2.5      | V    |

| VI <sup>(2,3)</sup> | Input Voltage Range     | -0.5 to 2.5                 | V                |      |

| Vo <sup>(2,3)</sup> | Output Voltage Range    |                             | -0.5 to VDD +0.5 | V    |

| lık                 | Input Clamp Current     | VI < 0                      | ±50              | mA   |

|                     |                         | VI > VDD                    |                  |      |

| Іок                 | Output Clamp Current    | Output Clamp Current Vo < 0 |                  | mA   |

|                     |                         | Vo > VDD                    |                  |      |

| lo                  | Continuous Output Cur   | rent,                       | ±50              | mA   |

|                     | Vo = 0 to VDD           |                             |                  |      |

| VDD                 | Continuous Current thro | ougheach                    | ±100             | mA   |

|                     | VDD or GND              |                             |                  |      |

| Tstg                | Storage Temperature R   | ange                        | -65 to +150      | °C   |

#### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. The input and output negative voltage ratings may be exceeded if the ratings of the I/P and O/P clamp current are observed.

- 3. This value is limited to 2.5V maximum.

**TERMINAL FUNCTIONS (ALL PINS)**

| Name<br>GND                                       | Characteristics Ground Input | Description                                                                                                                  |

|---------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------|

|                                                   | Ground Input                 | Constant                                                                                                                     |

|                                                   |                              | Ground                                                                                                                       |

| Vdd                                               | 1.8V nominal                 | Power Supply Voltage                                                                                                         |

| Vref                                              | 0.9V nominal                 | Input Reference Voltage                                                                                                      |

| ZoH <sup>(1)</sup>                                | LVCMOS                       | Output Slew Rate Control                                                                                                     |

| ZoL <sup>(1)</sup>                                | LVCMOS                       | Output Slew Rate Control                                                                                                     |

| CLK                                               | DifferentialInput            | Positive Master Clock Input                                                                                                  |

| CLK                                               | Differential Input           | Negative Master Clock Input                                                                                                  |

| Сх                                                | LVCMOS Input                 | Configuration Control Inputs                                                                                                 |

| RESET                                             | LVCMOS Input                 | Asynchronous Reset Input. Resets registers and disables VREF data and clock differential-input receivers.                    |

| $\overline{\text{CSR}}$ , $\overline{\text{DCS}}$ | SSTL_18Input                 | Chip Select Inputs. Disables outputs Dx switching when both inputs are HIGH.                                                 |

| Dx                                                | SSTL_18Input                 | Data Input. Clocked in on the crossing of the rising edge of CLK and the falling edge of CLK.                                |

| DODT                                              | SSTL_18Input                 | The outputs of this register bit will not be suspended by the D $\overline{\text{CSR}}$ and $\overline{\text{CSR}}$ controls |

| DCKE                                              | SSTL_18Input                 | The outputs of this register bit will not be suspended by the D $\overline{\text{CS}}$ and $\overline{\text{CSR}}$ controls  |

| Qx                                                | 1.8V CMOS                    | Data Outputs that are suspended by the DCS and CSR controls                                                                  |

| Q <del>C</del> Sx                                 | 1.8V CMOS                    | Data Output that will not be suspended by the D $\overline{\text{CS}}$ and $\overline{\text{CSR}}$ controls                  |

| QODTx                                             | 1.8V CMOS                    | Data Output that will not be suspended by the DCS and CSR controls                                                           |

| QCKEx                                             | 1.8V CMOS                    | Data Output that will not be suspended by the DCS and CSR controls                                                           |

#### NOTE

1. The signals will be left unconnected for the SSTU32864/A/C/D.

## OPERATING CHARACTERISTICS, TA = 25°C (1,2)

| Symbol | Parameter                      |             | Min.        | Тур.       | Max.       | Unit |

|--------|--------------------------------|-------------|-------------|------------|------------|------|

| Vdd    | Supply Voltage                 |             | 1.7         | _          | 1.9        | V    |

| Vref   | Reference Voltage              | 0.49 * VDD  | 0.5 * Vdd   | 0.51 * Vdd | V          |      |

| VTT    | Termination Voltage            | VREF- 40mV  | Vref        | VREF+ 40mV | V          |      |

| Vı     | Input Voltage                  |             | 0           | _          | Vdd        | V    |

| VIH    | AC High-Level Input Voltage    | Data Inputs | VREF+ 250mV | _          | _          | V    |

| VIL    | AC Low-Level Input Voltage     | Data Inputs | _           | _          | VREF-250mV | V    |

| VIH    | DC High-Level Input Voltage    | Data Inputs | VREF+ 125mV | _          | _          | V    |

| VIL    | DC Low-Level Input Voltage     | Data Inputs | _           | _          | VREF-125mV | V    |

| VIH    | High-Level Input Voltage       | RESET, Cx   | 0.65 * VDD  |            |            | V    |

| VIL    | Low-Level Input Voltage        | RESET, Cx   | _           | _          | 0.35 * Vdd | V    |

| Vicr   | Common Mode Input Voltage      | CLK, CLK    | 0.675       | _          | 1.125      | V    |

| VID    | Differential Input Voltage     | CLK, CLK    | 600         | _          | _          | mV   |

| Іон    | High-Level Output Current      |             | _           | _          | -8         | mA   |

| loL    | Low-Level Output Current       | _           | _           | 8          |            |      |

| TA     | Operating Free-Air Temperature |             | 0           | _          | 70         | °C   |

#### NOTES:

- 1. The RESET and Cx inputs of the device must be held at valid levels (not floating) to ensure proper device operation.

- 2. The differential inputs must not be floating unless RESET is LOW.

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified: Operating Condition:  $TA = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $VDD = 1.8V \pm 0.1V$

| Symbol | Parameter             | Test Conditions                                                          |           | Min. | Тур. | Max. | Unit     |

|--------|-----------------------|--------------------------------------------------------------------------|-----------|------|------|------|----------|

| Vон    |                       | VDD = 1.7V to 1.9V, IOH = -6mA                                           | 1.2       | _    | _    | V    |          |

| Vol    |                       | VDD = 1.7V to 1.9V, IOL = 6mA                                            | _         | _    | 0.5  | V    |          |

| lı     | All Inputs            | VI = VDD or GND                                                          | -5        | _    | 5    | μΑ   |          |

| IDD    | Static Standby        | Io = 0, VDD = 1.9V, RESET = GND                                          |           | _    | _    | 100  | μA       |

|        | Static Operating      | Io = 0, $VDD = 1.9V$ , $\overline{RESET} = VDD$ , $VI = VIH$ (AC) or $V$ | /IL (AC)  | _    | _    | 40   | mA       |

| IDDD   | Dynamic Operating     | IO = 0, VDD = 1.8V, RESET = VDD, VI = VIH (AC) or \                      | /IL (AC), | _    | _    | _    | μA/Clock |

|        | (Clock Only)          | CLK and CLK Switching 50% Duty Cycle.                                    |           |      |      |      | MHz      |

|        |                       | Io = 0, Vdd = 1.8V, RESET = Vdd,                                         | 1:1 Mode  | _    | _    | _    |          |

|        | Dynamic Operating     | $VI = VIH (AC)$ or $VIL (AC)$ , $CLK$ and $\overline{CLK}$ Switching at  |           |      |      |      | μA/Clock |

|        | (Per Each Data Input) | 50% Duty Cycle. One Data Input Switching at                              | 1:2 Mode  | _    | _    | _    | MHz/Data |

|        |                       | Half Clock Frequency, 50% Duty Cycle.                                    |           |      |      |      | Input    |

|        | Data Inputs           | VI = VREF ± 250mV                                                        |           | 2.5  | _    | 3.5  |          |

| Сі     | CLK and CLK           | VICR = 0.9V, VID = 600mV                                                 | _         | 2    | _    | 3    | pF       |

|        | RESET                 | VI = VDD or GND                                                          |           | 2    | _    | 4    |          |

# TIMING REQUIREMENTS OVER RECOMMENDED OPERATING FREE-AIR TEMPERATURE RANGE

|                       |                   |                                                 | VDD = 1.8 | V ± 0.1V |      |

|-----------------------|-------------------|-------------------------------------------------|-----------|----------|------|

| Symbol                | Parameter         |                                                 | Min.      | Max.     | Unit |

| fclock <sup>(1)</sup> | Clock Frequence   | су                                              | _         | 340      | MHz  |

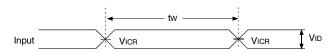

| tw                    | Pulse Duration    | , CLK, CLK HIGH or LOW                          | 1         |          | ns   |

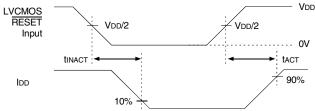

| tact <sup>(2)</sup>   | Differential Inpu | ts Active Time                                  |           | 10       | ns   |

| tinact <sup>(3)</sup> | Differential Inpu |                                                 |           | 15       | ns   |

|                       |                   | DCS before CLK↑, CLK↓, CSR HIGH                 | 0.7       | _        |      |

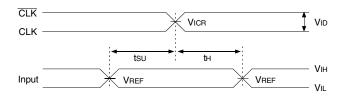

| tsu                   | SetupTime         | DCS before CLK↑, CLK↓, CSR LOW                  | 0.5       | _        | ns   |

|                       |                   | DODT, CSR, Data, and DCKE before CLK↑, CLK↓     | 0.5       | _        |      |

| t⊢                    | Hold Time         | Data, DCS, CSR, DCKE, and DODT after CLK↑, CLK↓ | 0.5       | _        | ns   |

#### NOTES:

- 1. 270MHz max clock frequency for parts assembled and tested prior to WW37.

- 2. Data and  $V_{REF}$  inputs must be low a minimum time of tact max, after  $\overline{RESET}$  is taken HIGH.

- 3. Data, VREF, and clock inputs must be held at valid levels (not floating) a minimum time of tINACT max, after RESET is taken LOW.

# SWITCHING CHARACTERISTICS OVER RECOMMENDED FREE-AIR OPERATING RANGE (UNLESS OTHERWISE NOTED) (1)

|                         |                                           | <b>V</b> DD = 1 | .8V ± 0.1V |      |

|-------------------------|-------------------------------------------|-----------------|------------|------|

| Symbol                  | Parameter                                 | Min             | Max.       | Unit |

| fMAX                    |                                           | 340             | _          | MHz  |

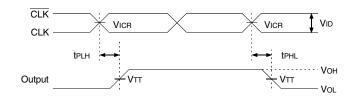

| tPDM <sup>(2)</sup>     | CLK and CLK to Q                          | 1.41            | 2.15       | ns   |

| tPDMSS <sup>(2,3)</sup> | CLK and CLK to Q (simultaneous switching) | _               | 2.35       | ns   |

| trphl                   | RESET to Q                                |                 | 3          | ns   |

| dV/dt_r                 | Output slew rate from 20% to 80%          | 1               | 4          | V/ns |

| dV/dt_f                 | Output slew rate from 20% to 80%          | 1               | 4          | V/ns |

| dV/dt $_{\Delta}^{(4)}$ | Output slew rate from 20% to 80%          | _               | 1          | V/ns |

#### NOTES:

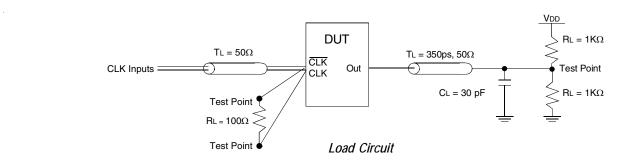

- 1. See TEST CIRCUITS AND WAVEFORMS.

- 2. Includes 350ps of test load transmission line delay.

- 3. This parameter is not production tested.

- 4. Difference between dV/dt\_r (rising edge rate) and dV/dt\_f (falling edge rate).

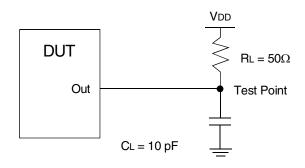

## TEST CIRCUITS AND WAVEFORMS (VDD = 1.8V ± 0.1V)

Voltage and Current Waveforms Inputs Active and Inactive Times

Voltage Waveforms - Pulse Duration

Voltage Waveforms - Setup and Hold Times

Voltage Waveforms - Propagation Delay Times

Voltage Waveforms - Propagation Delay Times

#### NOTES:

- 1. CL includes probe and jig capacitance.

- 2. IDD tested with clock and data inputs held at VDD or GND, and Io = 0mA

- 3. All input pulses are supplied by generators having the following characteristics: PRR ≤10MHz, Zo = 50Ω, input slew rate = 1 V/ns ±20% (unless otherwise specified).

- 4. The outputs are measured one at a time with one transition per measurement.

- 5. VTT = VREF = VDD/2

- 6. Vih = VREF + 250mV (AC voltage levels) for differential inputs. Vih = VDD for LVCMOS input.

- 7. VIL = VREF 250mV (AC voltage levels) for differential inputs. VIL = GND for LVCMOS input.

- 8. VID = 600mV.

- 9. tplh and tphL are the same as tppm.

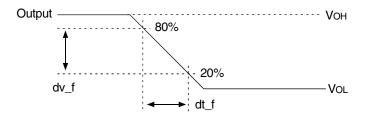

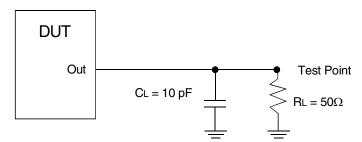

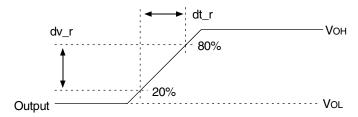

## **TEST CIRCUITS AND WAVEFORMS (VDD = 1.8V ± 0.1V)**

Load Circuit: High-to-Low Slew-Rate Adjustment

Voltage Waveforms: High-to-Low Slew-Rate Adjustment

Load Circuit: Low-to-High Slew-Rate Adjustment

Voltage Waveforms: Low-to-High Slew-Rate Adjustment

#### NOTES

- 1. CL includes probe and jig capacitance.

- 2. All input pulses are supplied by generators having the following characteristics: PRR ≤10MHz, Zo = 50Ω, input slew rate = 1 V/ns ±20% (unless otherwise specified).

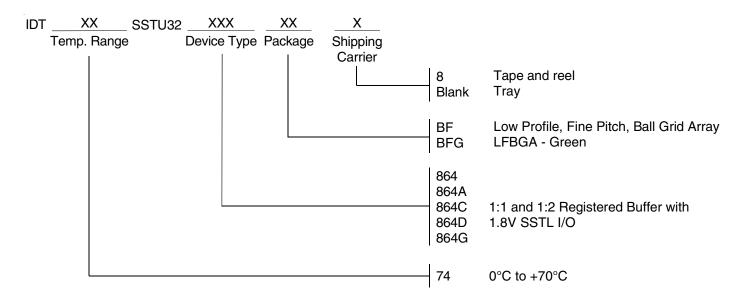

## **ORDERING INFORMATION**

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.