# **Eight Output Differential Buffer for PCI Express (50-200MHz)**

ICS9DB801C

## **Description**

The 9DB801C is a DB800 Version 2.0 Yellow Cover part with PCI Express support. It can be used in PC or embedded systems to provide outputs that have low cycle-to-cycle iitter (50ps), low output-to-output skew (100ps), and are PCI Express gen 1 compliant. The 9DB801C supports a 1 to 8 output configuration, taking a spread or non spread differential HCSL input from a CK410(B) main clock such as 954101 and 932S401, or any other differential HCSL pair. 9DB801C can generate HCSL or LVDS outputs from 50 to 200MHz in PLL mode or 0 to 400Mhz in bypass mode. There are two de-jittering modes available selectable through the HIGH\_BW# input pin, high bandwidth mode provides de-jittering for spread inputs and low bandwidth mode provides extra de-jittering for non-spread inputs. The SRC\_STOP#, PD#, and individual OE# real-time input pins provide completely programmable power management control.

## **Output Features**

- 8 0.7V current-mode differential output pairs

- Supports zero delay buffer mode and fanout mode

- Bandwidth programming available

#### Features/Benefits

- Spread spectrum modulation tolerant, 0 to -0.5% down spread and +/- 0.25% center spread.

- Supports undriven differential outputs in PD# and SRC\_STOP# modes for power management.

- Supports polarity inversion to the output enables, SRC\_STOP and PD.

## **Key Specifications**

- Outputs cycle-cycle jitter < 50ps</li>

- Outputs skew: 50ps

- 50 200MHz operation

- Extended frequency range in bypass mode to 400 MHz

- PCI Express Gen I compliant

- · Real time PLL lock detect output pin

- 48-pin SSOP/TSSOP package

- Available in RoHS compliant packaging

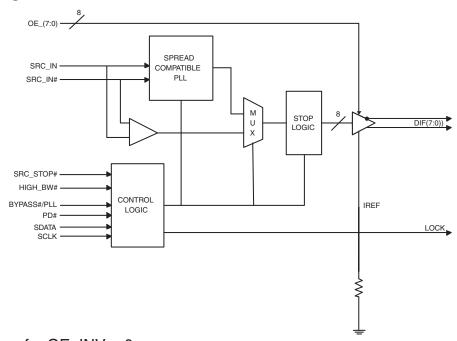

## **Funtional Block Diagram**

Note: Polarities shown for  $OE_INV = 0$ .

# **Pin Configuration**

| _             |                                  |                                  | -         | <u> </u>            |                            |    | _        |

|---------------|----------------------------------|----------------------------------|-----------|---------------------|----------------------------|----|----------|

| SRC_DIV# 1    | 1                                | 48                               | VDDA      | SRC_DIV#            | 1                          | 48 | VDDA     |

| VDD 2         | 2                                | 47                               | GNDA      | VDD 2               | 2                          | 47 | GNDA     |

| GND 3         | 3                                | 46                               | IREF      | GND                 |                            | 46 | IREF     |

| SRC_IN 4      | 4                                | 45                               | LOCK      | SRC_IN 4            | 4                          | 45 | LOCK     |

| SRC_IN# 5     |                                  | 44                               | OE_7      | SRC_IN#             |                            |    | OE7#     |

| OE_0 6        |                                  | 43                               | OE_4      | OE0#                |                            |    | OE4#     |

| OE_3 7        |                                  | <del>~</del> 42                  | DIF_7     | OE3#                |                            |    | DIF_7    |

| DIF_0         | 3                                | 8 41                             | DIF_7#    | DIF_0               |                            |    | DIF_7#   |

| DIF_0# 9      | 9                                | 41<br>40<br>39<br>38<br>37<br>36 | OE_INV    | DIF_0# 9            |                            |    | OE_INV   |

| GND 1         | 10                               | 39                               | VDD       | GND <sup>-</sup>    | 10                         |    | VDD      |

| VDD 1         | 11 👸                             | <b>5</b> 38                      | DIF_6     | VDD ·               | 11                         |    | DIF_6    |

| DIF_1 1       | 12                               | 37                               | DIF_6#    | DIF_1               | 12                         |    | DIF_6#   |

| DIF_1# 1      | 13 <b>5</b>                      |                                  | OE_6      | DIF_1#              | 10<br>11<br>12<br>13<br>14 | 36 | OE6#     |

| OE_1 1        | 10<br>11<br>12<br>13<br>14<br>15 | <b>se</b> 35                     | OE_5      | OE1#                | 14 <b>9</b>                |    | OE5#     |

| OE_2 1        | 15                               | <b>o</b> 34                      | DIF_5     | OE2#                |                            |    | DIF_5    |

| DIF_2 1       | 16                               | 34<br>33<br>32<br>31             | DIF_5#    | DIF_2               | 16                         | 33 | DIF_5#   |

| DIF_2# 1      | 17                               | <b>ශී</b> 32                     | GND       | DIF_2# <sup>-</sup> | 17                         | 32 | GND      |

| GND 1         | 18                               | 31                               | VDD       | GND <sup>-</sup>    |                            | 31 | VDD      |

| VDD 1         | 19                               | 30                               | DIF_4     | VDD <sup>-</sup>    |                            |    | DIF_4    |

| DIF_3 2       | 20                               | 29                               | DIF_4#    | DIF_3               | 20                         | 29 | DIF_4#   |

| DIF_3# 2      | 21                               | 28                               | HIGH_BW#  | DIF_3# 2            |                            | 28 | HIGH_BW# |

| BYPASS#/PLL 2 | 22                               | 27                               | SRC_STOP# | BYPASS#/PLL 2       | 22                         | 27 | SRC_STOP |

| SCLK 2        | 23                               | 26                               | PD#       | SCLK                |                            |    | PD       |

| SDATA 2       | 24                               | 25                               | GND       | SDATA 2             | 24                         | 25 | GND      |

| _             | OE_IN                            |                                  | 1         |                     | OE_INV =                   | 1  |          |

|               | _                                |                                  |           |                     |                            |    |          |

# **Polarity Inversion Pin List Table**

|      | OE_INV    |          |  |  |

|------|-----------|----------|--|--|

| Pins | 0         | 1        |  |  |

| 6    | OE_0      | OE0#     |  |  |

| 7    | OE_3      | OE3#     |  |  |

| 14   | OE_1      | OE1#     |  |  |

| 15   | OE_2      | OE2#     |  |  |

| 26   | PD#       | PD       |  |  |

| 27   | DIF_STOP# | DIF_STOP |  |  |

| 35   | OE_5      | OE5#     |  |  |

| 36   | OE_6      | OE6#     |  |  |

| 43   | OE_4      | OE4#     |  |  |

| 44   | OE_7      | OE7#     |  |  |

| PIN# | PIN NAME    | PIN TYPE | DESCRIPTION                                                                           |

|------|-------------|----------|---------------------------------------------------------------------------------------|

| 1    | SRC_DIV#    | INPUT    | Active low Input for determining SRC output frequency SRC or SRC/2. 0 = SRC/2, 1= SRC |

| 2    | VDD         | POWER    | Power supply, nominal 3.3V                                                            |

| 3    | GND         | POWER    | Ground pin.                                                                           |

| 4    | SRC_IN      | INPUT    | 0.7 V Differential SRC TRUE input                                                     |

| 5    | SRC_IN#     | INPUT    | 0.7 V Differential SRC COMPLEMENTARY input                                            |

| 6    | OE_0        | INPUT    | Active high input for enabling outputs.  0 = tri-state outputs, 1= enable outputs     |

| 7    | OE_3        | INPUT    | Active high input for enabling outputs.  0 = tri-state outputs, 1= enable outputs     |

| 8    | DIF_0       | OUTPUT   | 0.7V differential true clock outputs                                                  |

| 9    | DIF 0#      | OUTPUT   | 0.7V differential complement clock outputs                                            |

| 10   | GND         | POWER    | Ground pin.                                                                           |

| 11   | VDD         | POWER    | Power supply, nominal 3.3V                                                            |

| 12   | DIF_1       | OUTPUT   | 0.7V differential true clock outputs                                                  |

| 13   | DIF_1#      | OUTPUT   | 0.7V differential complement clock outputs                                            |

| 14   | OE_1        | INPUT    | Active high input for enabling outputs.  0 = tri-state outputs, 1= enable outputs     |

| 15   | OE_2        | INPUT    | Active high input for enabling outputs.  0 = tri-state outputs, 1= enable outputs     |

| 16   | DIF 2       | OUTPUT   | 0.7V differential true clock outputs                                                  |

| 17   | DIF_2#      | OUTPUT   | 0.7V differential complement clock outputs                                            |

| 18   | GND         | POWER    | Ground pin.                                                                           |

| 19   | VDD         | POWER    | Power supply, nominal 3.3V                                                            |

| 20   | DIF_3       | OUTPUT   | 0.7V differential true clock outputs                                                  |

| 21   | DIF_3#      | OUTPUT   | 0.7V differential complement clock outputs                                            |

| 22   | BYPASS#/PLL | INPUT    | Input to select Bypass(fan-out) or PLL (ZDB) mode  0 = Bypass mode, 1= PLL mode       |

| 23   | SCLK        | INPUT    | Clock pin of SMBus circuitry, 5V tolerant.                                            |

| 24   | SDATA       | I/O      | Data pin for SMBus circuitry, 5V tolerant.                                            |

| PIN# | PIN NAME  | PIN TYPE | DESCRIPTION                                                     |

|------|-----------|----------|-----------------------------------------------------------------|

| 25   | GND       | POWER    | Ground pin.                                                     |

|      |           |          | Asynchronous active low input pin, with 120Kohm internal pull-  |

| 26   | PD#       | INPUT    | up resistor, used to power down the device. The internal clocks |

|      |           |          | are disabled and the VCO and the crystal are stopped.           |

| 27   | SRC_STOP# | INPUT    | Active low input to stop SRC outputs.                           |

| 28   | HIGH_BW#  | INPUT    | 3.3V input for selecting PLL Band Width                         |

| 20   | пісп_ви#  | INFOT    | 0 = High, 1= Low                                                |

| 29   | DIF_4#    | OUTPUT   | 0.7V differential complement clock outputs                      |

| 30   | DIF_4     | OUTPUT   | 0.7V differential true clock outputs                            |

| 31   | VDD       | POWER    | Power supply, nominal 3.3V                                      |

| 32   | GND       | POWER    | Ground pin.                                                     |

| 33   | DIF_5#    | OUTPUT   | 0.7V differential complement clock outputs                      |

| 34   | DIF_5     | OUTPUT   | 0.7V differential true clock outputs                            |

| 35   | OE_5      | INPUT    | Active high input for enabling outputs.                         |

| 33   | OE_5      | INFOT    | 0 = tri-state outputs, 1= enable outputs                        |

| 36   | OE 6      | INPUT    | Active high input for enabling outputs.                         |

| 30   | OE_6      | INPUT    | 0 = tri-state outputs, 1= enable outputs                        |

| 37   | DIF_6#    | OUTPUT   | 0.7V differential complement clock outputs                      |

| 38   | DIF_6     | OUTPUT   | 0.7V differential true clock outputs                            |

| 39   | VDD       | POWER    | Power supply, nominal 3.3V                                      |

| 40   | OE_INV    | INPUT    | This latched input selects the polarity of the OE pins.         |

| 40   | OE_IIV    | INPUT    | 0 = OE pins active high, 1 = OE pins active low (OE#)           |

| 41   | DIF_7#    | OUTPUT   | 0.7V differential complement clock outputs                      |

| 42   | DIF_7     | OUTPUT   | 0.7V differential true clock outputs                            |

| 43   | OE_4      | INPUT    | Active high input for enabling outputs.                         |

| 40   | OL_4      | IIVI O I | 0 = tri-state outputs, 1= enable outputs                        |

| 44   | OE_7      | INPUT    | Active high input for enabling outputs.                         |

| 44   | OL_/      | INFOT    | 0 = tri-state outputs, 1= enable outputs                        |

| 45   | LOCK      | OUTPUT   | 3.3V output indicating PLL Lock Status. This pin goes high      |

| 40   | LOCK      | OUTFUT   | when lock is achieved.                                          |

|      |           |          | This pin establishes the reference current for the differential |

| 46   | IREF      | INPUT    | current-mode output pairs. This pin requires a fixed precision  |

| 40   | INCF      | IINFUI   | resistor tied to ground in order to establish the appropriate   |

|      |           |          | current. 475 ohms is the standard value.                        |

| 47   | GNDA      | POWER    | Ground pin for the PLL core.                                    |

| 48   | VDDA      | POWER    | 3.3V power for the PLL core.                                    |

| PIN# | PIN NAME    | PIN TYPE | DESCRIPTION                                                  |

|------|-------------|----------|--------------------------------------------------------------|

|      |             |          | Active low Input for determining SRC output frequency SRC or |

| 1    | SRC_DIV#    | INPUT    | SRC/2.                                                       |

|      |             |          | 0 = SRC/2, 1= SRC                                            |

| 2    | VDD         | POWER    | Power supply, nominal 3.3V                                   |

| 3    | GND         | POWER    | Ground pin.                                                  |

| 4    | SRC_IN      | INPUT    | 0.7 V Differential SRC TRUE input                            |

| 5    | SRC_IN#     | INPUT    | 0.7 V Differential SRC COMPLEMENTARY input                   |

| 6    | OE0#        | INPUT    | Active low input for enabling DIF pair 0.                    |

| 0    | OLO#        | INFO     | 1 = tri-state outputs, 0 = enable outputs                    |

| 7    | OE3#        | INPUT    | Active low input for enabling DIF pair 3.                    |

| /    | OL3#        | INFO     | 1 = tri-state outputs, 0 = enable outputs                    |

| 8    | DIF_0       | OUTPUT   | 0.7V differential true clock outputs                         |

| 9    | DIF_0#      | OUTPUT   | 0.7V differential complement clock outputs                   |

| 10   | GND         | POWER    | Ground pin.                                                  |

| 11   | VDD         | POWER    | Power supply, nominal 3.3V                                   |

| 12   | DIF_1       | OUTPUT   | 0.7V differential true clock outputs                         |

| 13   | DIF_1#      | OUTPUT   | 0.7V differential complement clock outputs                   |

| 14   | OE1#        | INPUT    | Active low input for enabling DIF pair 1.                    |

| 14   | OL1#        | INFO     | 1 = tri-state outputs, 0 = enable outputs                    |

| 15   | OE2#        | INPUT    | Active low input for enabling DIF pair 2.                    |

| 15   | OL2#        | INFO     | 1 = tri-state outputs, 0 = enable outputs                    |

| 16   | DIF_2       | OUTPUT   | 0.7V differential true clock outputs                         |

| 17   | DIF_2#      | OUTPUT   | 0.7V differential complement clock outputs                   |

| 18   | GND         | POWER    | Ground pin.                                                  |

| 19   | VDD         | POWER    | Power supply, nominal 3.3V                                   |

| 20   | DIF_3       | OUTPUT   | 0.7V differential true clock outputs                         |

| 21   | DIF_3#      | OUTPUT   | 0.7V differential complement clock outputs                   |

| 20   | BYPASS#/PLL | INPUT    | Input to select Bypass(fan-out) or PLL (ZDB) mode            |

| 22   | DIPASS#/PLL | INPUT    | 0 = Bypass mode, 1= PLL mode                                 |

| 23   | SCLK        | INPUT    | Clock pin of SMBus circuitry, 5V tolerant.                   |

| 24   | SDATA       | I/O      | Data pin for SMBus circuitry, 5V tolerant.                   |

| PIN# | PIN NAME | PIN TYPE | DESCRIPTION                                                                                                                                                                                                                           |

|------|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25   | GND      | PWR      | Ground pin.                                                                                                                                                                                                                           |

| 26   | PD       | IN       | Asynchronous active high input pin used to power down the device. The internal clocks are disabled and the VCO is stopped.                                                                                                            |

| 27   | SRC_STOP | IN       | Active high input to stop SRC outputs.                                                                                                                                                                                                |

| 28   | HIGH_BW# | IN       | 3.3V input for selecting PLL Band Width 0 = High, 1= Low                                                                                                                                                                              |

| 29   | DIF_4#   | OUT      | 0.7V differential complement clock outputs                                                                                                                                                                                            |

| 30   | DIF_4    | OUT      | 0.7V differential true clock outputs                                                                                                                                                                                                  |

| 31   | VDD      | PWR      | Power supply, nominal 3.3V                                                                                                                                                                                                            |

| 32   | GND      | PWR      | Ground pin.                                                                                                                                                                                                                           |

| 33   | DIF_5#   | OUT      | 0.7V differential complement clock outputs                                                                                                                                                                                            |

| 34   | DIF_5    | OUT      | 0.7V differential true clock outputs                                                                                                                                                                                                  |

| 35   | OE5#     | IN       | Active low input for enabling DIF pair 5.  1 = tri-state outputs, 0 = enable outputs                                                                                                                                                  |

| 36   | OE6#     | IN       | Active low input for enabling DIF pair 6.  1 = tri-state outputs, 0 = enable outputs                                                                                                                                                  |

| 37   | DIF_6#   | OUT      | 0.7V differential complement clock outputs                                                                                                                                                                                            |

| 38   | DIF_6    | OUT      | 0.7V differential true clock outputs                                                                                                                                                                                                  |

| 39   | VDD      | PWR      | Power supply, nominal 3.3V                                                                                                                                                                                                            |

| 40   | OE_INV   | IN       | This latched input selects the polarity of the OE pins.  0 = OE pins active high, 1 = OE pins active low (OE#)                                                                                                                        |

| 41   | DIF_7#   | OUT      | 0.7V differential complement clock outputs                                                                                                                                                                                            |

| 42   | DIF_7    | OUT      | 0.7V differential true clock outputs                                                                                                                                                                                                  |

| 43   | OE4#     | IN       | Active low input for enabling DIF pair 4 1 = tri-state outputs, 0 = enable outputs                                                                                                                                                    |

| 44   | OE7#     | IN       | Active low input for enabling DIF pair 7.  1 = tri-state outputs, 0 = enable outputs                                                                                                                                                  |

| 45   | LOCK     | OUT      | 3.3V output indicating PLL Lock Status. This pin goes high when lock is achieved.                                                                                                                                                     |

| 46   | IREF     | IN       | This pin establishes the reference current for the differential current-mode output pairs. This pin requires a fixed precision resistor tied to ground in order to establish the appropriate current. 475 ohms is the standard value. |

| 47   | GNDA     | PWR      | Ground pin for the PLL core.                                                                                                                                                                                                          |

| 48   | VDDA     | PWR      | 3.3V power for the PLL core.                                                                                                                                                                                                          |

## **Absolute Max**

| Symbol   | Parameter                 | Min     | Max                   | Units |

|----------|---------------------------|---------|-----------------------|-------|

| VDD_A    | 3.3V Core Supply Voltage  |         | 4.6                   | V     |

| VDD_In   | 3.3V Logic Supply Voltage |         | 4.6                   | V     |

| $V_{IL}$ | Input Low Voltage         | GND-0.5 |                       | V     |

| $V_{IH}$ | Input High Voltage        |         | V <sub>DD</sub> +0.5V | V     |

| Ts       | Storage Temperature       | -65     | 150                   | °C    |

| Tambient | Ambient Operating Temp    | 0       | 70                    | °C    |

| Tcase    | Case Temperature          |         | 115                   | °C    |

|          | Input ESD protection      |         |                       |       |

| ESD prot | human body model          | 2000    |                       | V     |

# Electrical Characteristics - Input/Supply/Common Output Parameters $T_A$ = 0 - 70°C; Supply Voltage $V_{DD}$ = 3.3 V +/-5%

| PARAMETER                        | SYMBOL                   | CONDITIONS                                                                                           | MIN       | TYP | MAX            | UNITS | NOTES |

|----------------------------------|--------------------------|------------------------------------------------------------------------------------------------------|-----------|-----|----------------|-------|-------|

| Input High Voltage               | $V_{IH}$                 | 3.3 V +/-5%                                                                                          | 2         |     | $V_{DD} + 0.3$ | V     |       |

| Input Low Voltage                | $V_{IL}$                 | 3.3 V +/-5%                                                                                          | GND - 0.3 |     | 0.8            | V     |       |

| Input High Current               | I <sub>IH</sub>          | $V_{IN} = V_{DD}$                                                                                    | -5        |     | 5              | uA    |       |

| land land Commit                 | I <sub>IL1</sub>         | V <sub>IN</sub> = 0 V; Inputs with no pull-<br>up resistors                                          | -5        |     |                | uA    |       |

| Input Low Current                | I <sub>IL2</sub>         | V <sub>IN</sub> = 0 V; Inputs with pull-up resistors                                                 | -200      |     |                | uA    |       |

| Operating Supply Current         | I <sub>DD3.3PLL</sub>    | Full Active, $C_L = Full load;$                                                                      |           | 175 | 200            | mA    |       |

| Operating Supply Surrent         | I <sub>DD3.3ByPass</sub> | <u>-</u>                                                                                             |           | 160 | 175            | mA    |       |

| Powerdown Current                | I <sub>DD3.3PD</sub>     | all diff pairs driven                                                                                |           | 50  | 70             | mA    |       |

|                                  |                          | all differential pairs tri-stated                                                                    |           | 1   | 4              | mA    |       |

| Input Frequency                  | F <sub>iPLL</sub>        | PLL Mode                                                                                             | 50        |     | 200            | MHz   |       |

| Input Frequency                  | F <sub>iBypass</sub>     | Bypass Mode (Revision<br>B/REV ID = 1H)                                                              | 0         |     | 333.33         | MHz   |       |

| Input Frequency                  | F <sub>iBypass</sub>     | Bypass Mode (Revision<br>C/REV ID = 2H)                                                              | 0         |     | 400            | MHz   |       |

| Pin Inductance <sup>1</sup>      | L <sub>pin</sub>         |                                                                                                      |           |     | 7              | nΗ    | 1     |

|                                  | C <sub>IN</sub>          | Logic Inputs                                                                                         | 1.5       |     | 4              | pF    | 1     |

| Input Capacitance <sup>1</sup>   | C <sub>OUT</sub>         | Output pin capacitance                                                                               |           |     | 4              | рF    | 1     |

| 5.1.5                            |                          | PLL Bandwidth when<br>PLL BW=0                                                                       | 2.4       | 3   | 3.4            | MHz   | 1     |

| PLL Bandwidth                    | BW                       | PLL Bandwidth when PLL_BW=1                                                                          | 0.7       | 1   | 1.4            | MHz   | 1     |

| Clk Stabilization <sup>1,2</sup> | T <sub>STAB</sub>        | From V <sub>DD</sub> Power-Up and after input clock stabilization or deassertion of PD# to 1st clock |           | 0.5 | 1              | ms    | 1,2   |

| Modulation Frequency             | fMOD                     | Triangular Modulation                                                                                | 30        |     | 33             | kHz   | 1     |

| Tdrive_SRC_STOP#                 |                          | DIF output enable after<br>SRC_Stop# de-assertion                                                    |           | 10  | 15             | ns    | 1,3   |

| Tdrive_PD#                       |                          | DIF output enable after PD# de-assertion                                                             |           |     | 300            | us    | 1,3   |

| Tfall                            |                          | Fall time of PD# and<br>SRC_STOP#                                                                    |           |     | 5              | ns    | 1     |

| Trise                            |                          | Rise time of PD# and SRC_STOP#                                                                       |           |     | 5              | ns    | 2     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup>See timing diagrams for timing requirements.

<sup>&</sup>lt;sup>3</sup>Time from deassertion until outputs are >200 mV

## **Electrical Characteristics - Clock Input Parameters**

$T_A = 0 - 70$ °C; Supply Voltage  $V_{DD} = 3.3 \text{ V +/-5}\%$

| PARAMETER                            | SYMBOL                | CONDITIONS                                     | MIN                   | MAX  | UNITS | NOTES |

|--------------------------------------|-----------------------|------------------------------------------------|-----------------------|------|-------|-------|

| Differential Input High Voltage      | V <sub>IHDIF</sub>    | Differential inputs (single-ended measurement) | 600                   | 1150 | mV    | 1     |

| Differential Input Low Voltage       | V <sub>ILDIF</sub>    | Differential inputs (single-ended measurement) | V <sub>SS</sub> - 300 | 300  | mV    | 1     |

| Input Slew Rate - DIF_IN             | dv/dt                 | Measured differentially                        | 0.4                   | 8    | V/ns  | 2     |

| Input Leakage Current                | I <sub>IN</sub>       | $V_{IN} = V_{DD}, V_{IN} = GND$                | -5                    | 5    | uA    | 1     |

| Input Duty Cycle                     | d <sub>tin</sub>      | Measurement from differential wavefrom         | 45                    | 55   | %     | 1     |

| Input SRC Jitter - Cycle to<br>Cycle | SRCJ <sub>C2CIn</sub> | Differential Measurement                       |                       | 125  | ps    | 1     |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

#### Electrical Characteristics - DIF 0.7V Current Mode Differential Pair

$T_{A} = 0 - 70^{\circ}\text{C}; \ V_{DD} = 3.3 \ V \ + / -5\%; \ C_{L} = 2pF, \ R_{S} = 33.2\Omega, \ R_{P} = 49.9\Omega, \ I_{REF} = 475\Omega$

| PARAMETER                          | SYMBOL                | CONDITIONS                                                        | MIN  | TYP | MAX  | UNITS | NOTES |

|------------------------------------|-----------------------|-------------------------------------------------------------------|------|-----|------|-------|-------|

| Current Source Output<br>Impedance | Zo <sup>1</sup>       | $V_O = V_x$                                                       | 3000 |     |      | Ω     | 1     |

| Voltage High                       | VHigh                 | Statistical measurement on single ended signal using oscilloscope | 660  |     | 850  | mV    | 1,3   |

| Voltage Low                        | VLow                  | math function.                                                    | -150 |     | 150  | 1110  | 1,3   |

| Max Voltage                        | Vovs                  | Measurement on single ended                                       |      |     | 1150 | mV    | 1     |

| Min Voltage                        | Vuds                  | signal using absolute value.                                      | -300 |     |      | IIIV  | 1     |

| Crossing Voltage (abs)             | Vcross(abs)           |                                                                   | 250  |     | 550  | mV    | 1     |

| Crossing Voltage (var)             | d-Vcross              | Variation of crossing over all edges                              |      |     | 140  | mV    | 1     |

| Long Accuracy                      | ppm                   | see Tperiod min-max values                                        |      |     | 0    | ppm   | 1,2   |

| Rise Time                          | t <sub>r</sub>        | $V_{OL} = 0.175V, V_{OH} = 0.525V$                                | 175  |     | 700  | ps    | 1     |

| Fall Time                          | t <sub>f</sub>        | $V_{OH} = 0.525 V V_{OL} = 0.175 V$                               | 175  |     | 700  | ps    | 1     |

| Rise Time Variation                | d-t <sub>r</sub>      |                                                                   |      |     | 125  | ps    | 1     |

| Fall Time Variation                | d-t <sub>f</sub>      |                                                                   |      |     | 125  | ps    | 1     |

| Duty Cycle                         | d <sub>t3</sub>       | Measurement from differential wavefrom                            | 45   |     | 55   | %     | 1     |

| Skew                               | t <sub>sk3</sub>      | V <sub>T</sub> = 50%                                              |      |     | 50   | ps    | 1     |

| Jitter, Cycle to cycle             | t <sub>jcyc-cyc</sub> | PLL mode, Measurement from differential wavefrom                  |      |     | 50   | ps    | 1     |

|                                    |                       | BYPASS mode as additive jitter                                    |      |     | 50   | ps    | 1     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup>Slew rate measured through Vswing centered around differential zero

<sup>&</sup>lt;sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that the input clock complies with CK409/CK410 accuracy requirements

$<sup>^{3}</sup>I_{REF} = V_{DD}/(3xR_{R})$ . For  $R_{R} = 475\Omega$  (1%),  $I_{REF} = 2.32$ mA.  $I_{OH} = 6$  x  $I_{REF}$  and  $V_{OH} = 0.7$ V @  $Z_{O} = 50\Omega$ .

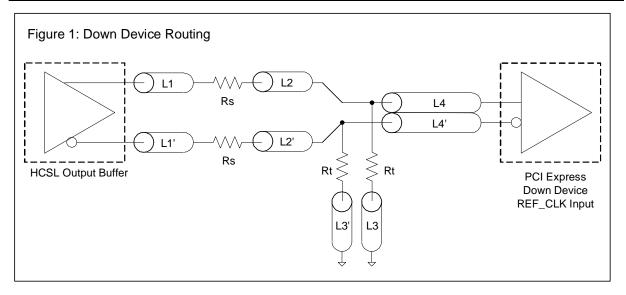

| SRC Reference Cloc                              | K                  |      |        |

|-------------------------------------------------|--------------------|------|--------|

| Common Recommendations for Differential Routing | Dimension or Value | Unit | Figure |

| L1 length, route as non-coupled 50ohm trace     | 0.5 max            | inch | 1      |

| L2 length, route as non-coupled 50ohm trace     | 0.2 max            | inch | 1      |

| L3 length, route as non-coupled 50ohm trace     | 0.2 max            | inch | 1      |

| Rs                                              | 33                 | ohm  | 1      |

| Rt                                              | 49.9               | ohm  | 1      |

| Down Device Differential Routing                                 |                     |      |   |

|------------------------------------------------------------------|---------------------|------|---|

| L4 length, route as coupled microstrip 100ohm differential trace | 2 min to 16 max     | inch | 1 |

| L4 length, route as coupled stripline 100ohm differential trace  | 1.8 min to 14.4 max | inch | 1 |

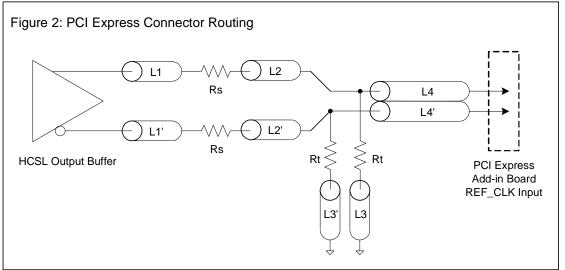

| Differential Routing to PCI Express Connector                    |                       |      |   |

|------------------------------------------------------------------|-----------------------|------|---|

| L4 length, route as coupled microstrip 100ohm differential trace | 0.25 to 14 max        | inch | 2 |

| L4 length, route as coupled stripline 100ohm differential trace  | 0.225 min to 12.6 max | inch | 2 |

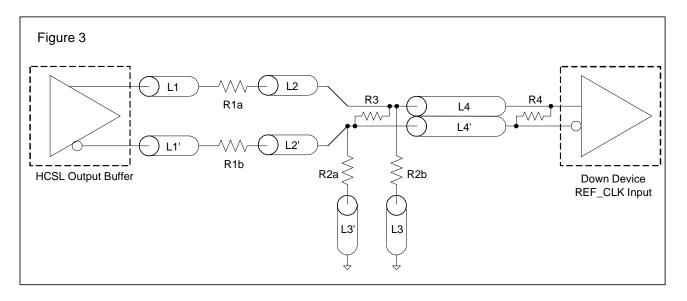

|       | Alternative Termination for LVDS and other Common Differential Signals (figure 3) |      |    |      |      |     |                                |  |  |  |

|-------|-----------------------------------------------------------------------------------|------|----|------|------|-----|--------------------------------|--|--|--|

| Vdiff | Vp-p                                                                              | Vcm  | R1 | R2   | R3   | R4  | Note                           |  |  |  |

| 0.45v | 0.22v                                                                             | 1.08 | 33 | 150  | 100  | 100 |                                |  |  |  |

| 0.58  | 0.28                                                                              | 0.6  | 33 | 78.7 | 137  | 100 |                                |  |  |  |

| 0.80  | 0.40                                                                              | 0.6  | 33 | 78.7 | none | 100 | ICS874003i-02 input compatible |  |  |  |

| 0.60  | 0.3                                                                               | 1.2  | 33 | 174  | 140  | 100 | Standard LVDS                  |  |  |  |

R1a = R1b = R1 R2a = R2b = R2

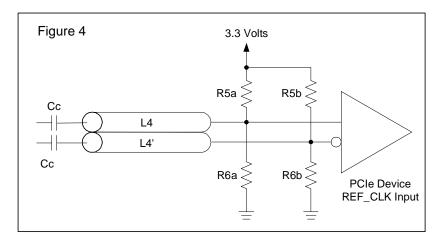

| Cable Connected AC Coupled Application (figure 4) |             |      |  |  |  |  |  |

|---------------------------------------------------|-------------|------|--|--|--|--|--|

| Component                                         | Value       | Note |  |  |  |  |  |

| R5a, R5b                                          | 8.2K 5%     |      |  |  |  |  |  |

| R6a, R6b                                          | 1K 5%       |      |  |  |  |  |  |

| Cc                                                | 0.1 µF      |      |  |  |  |  |  |

| Vcm                                               | 0.350 volts |      |  |  |  |  |  |

## General SMBus serial interface information for the ICS9DB801C

#### **How to Write:**

- · Controller (host) sends a start bit.

- Controller (host) sends the write address DC (h)

- ICS clock will acknowledge

- Controller (host) sends the begining byte location = N

- ICS clock will *acknowledge*

- Controller (host) sends the data byte count = X

- ICS clock will acknowledge

- Controller (host) starts sending Byte N through Byte N + X -1

- ICS clock will acknowledge each byte one at a time

- · Controller (host) sends a Stop bit

## How to Read:

- · Controller (host) will send start bit.

- Controller (host) sends the write address DC (h)

- ICS clock will acknowledge

- Controller (host) sends the begining byte location = N

- ICS clock will acknowledge

- Controller (host) will send a separate start bit.

- Controller (host) sends the read address DD (h)

- ICS clock will *acknowledge*

- ICS clock will send the data byte count = X

- ICS clock sends Byte N + X -1

- ICS clock sends Byte 0 through byte X (if X<sub>(h)</sub> was written to byte 8).

- · Controller (host) will need to acknowledge each byte

- · Controllor (host) will send a not acknowledge bit

- · Controller (host) will send a stop bit

| Ind   | Index Block Write Operation |      |                      |  |  |  |  |  |  |  |

|-------|-----------------------------|------|----------------------|--|--|--|--|--|--|--|

| Cor   | ntroller (Host)             |      | ICS (Slave/Receiver) |  |  |  |  |  |  |  |

| Т     | starT bit                   |      |                      |  |  |  |  |  |  |  |

| Slav  | e Address DC <sub>(h)</sub> |      |                      |  |  |  |  |  |  |  |

| WR    | WRite                       |      |                      |  |  |  |  |  |  |  |

|       |                             |      | ACK                  |  |  |  |  |  |  |  |

| Begi  | nning Byte = N              |      |                      |  |  |  |  |  |  |  |

|       |                             |      | ACK                  |  |  |  |  |  |  |  |

| Data  | Byte Count = X              |      |                      |  |  |  |  |  |  |  |

|       |                             |      | ACK                  |  |  |  |  |  |  |  |

| Begir | nning Byte N                |      |                      |  |  |  |  |  |  |  |

|       |                             |      | ACK                  |  |  |  |  |  |  |  |

|       | <b>\rightarrow</b>          | Byte |                      |  |  |  |  |  |  |  |

|       | $\Diamond$                  |      | $\Diamond$           |  |  |  |  |  |  |  |

|       | $\Diamond$                  | ×    | $\Diamond$           |  |  |  |  |  |  |  |

|       |                             |      | <b>\Q</b>            |  |  |  |  |  |  |  |

| Byte  | e N + X - 1                 |      |                      |  |  |  |  |  |  |  |

|       | · ·                         |      | ACK                  |  |  |  |  |  |  |  |

| Р     | stoP bit                    |      |                      |  |  |  |  |  |  |  |

| Ind   | Index Block Read Operation |                     |                    |  |  |  |  |  |  |  |

|-------|----------------------------|---------------------|--------------------|--|--|--|--|--|--|--|

| Con   | troller (Host)             | IC                  | S (Slave/Receiver) |  |  |  |  |  |  |  |

| Т     | starT bit                  |                     |                    |  |  |  |  |  |  |  |

| Slave | Address DC <sub>(h)</sub>  |                     |                    |  |  |  |  |  |  |  |

| WR    | WRite                      |                     |                    |  |  |  |  |  |  |  |

|       |                            |                     | ACK                |  |  |  |  |  |  |  |

| Begir | nning Byte = N             |                     |                    |  |  |  |  |  |  |  |

|       |                            |                     | ACK                |  |  |  |  |  |  |  |

| RT    | Repeat starT               |                     |                    |  |  |  |  |  |  |  |

| Slave | Address DD <sub>(h)</sub>  |                     |                    |  |  |  |  |  |  |  |

| RD    | ReaD                       |                     |                    |  |  |  |  |  |  |  |

|       |                            | ACK                 |                    |  |  |  |  |  |  |  |

|       |                            |                     |                    |  |  |  |  |  |  |  |

|       |                            | Data Byte Count = X |                    |  |  |  |  |  |  |  |

|       | ACK                        |                     |                    |  |  |  |  |  |  |  |

|       |                            |                     | Beginning Byte N   |  |  |  |  |  |  |  |

|       | ACK                        |                     |                    |  |  |  |  |  |  |  |

|       |                            | /te                 | <b>\Q</b>          |  |  |  |  |  |  |  |

|       | <b>\Q</b>                  | X Byte              | <b>\Q</b>          |  |  |  |  |  |  |  |

|       | <b>O</b>                   | ×                   | <b>\Q</b>          |  |  |  |  |  |  |  |

|       | <b>Q</b>                   |                     |                    |  |  |  |  |  |  |  |

|       |                            |                     | Byte N + X - 1     |  |  |  |  |  |  |  |

| N     | Not acknowledge            |                     |                    |  |  |  |  |  |  |  |

| Р     | stoP bit                   |                     |                    |  |  |  |  |  |  |  |

SMBus Table: Frequency Select Register, READ/WRITE ADDRESS (DC/DD)

| Ву    | rte 0 Pin | # Name    | <b>Control Function</b> | Туре | 0        | 1        | PWD |

|-------|-----------|-----------|-------------------------|------|----------|----------|-----|

| Bit 7 | -         | PD_Mode   | PD# drive mode          | RW   | driven   | Hi-Z     | 0   |

| Bit 6 | -         | STOP_Mode | SRC_Stop# drive mode    | RW   | driven   | Hi-Z     | 0   |

| Bit 5 | -         | Reserved  | Reserved                | RW   | Res      | Reserved |     |

| Bit 4 | -         | Reserved  | Reserved                | RW   | Reserved |          | X   |

| Bit 3 | -         | Reserved  | Reserved                | RW   | Reserved |          | Х   |

| Bit 2 | -         | PLL_BW#   | Select PLL BW           | RW   | High BW  | Low BW   | 1   |

| Bit 1 | -         | BYPASS#   | BYPASS#/PLL             | RW   | fan-out  | ZDB      | 1   |

| Bit 0 | -         | SRC_DIV#  | SRC Divide by 2 Select  | RW   | x/2      | 1x       | 1   |

**SMBus Table: Output Control Register**

| Ву    | te 1  | Pin# | Name                                  | Control Function | Туре | 0       | 1      | PWD |

|-------|-------|------|---------------------------------------|------------------|------|---------|--------|-----|

| Bit 7 | 42,41 |      | : <b>7</b> 42,41 DIF_7 Output Control |                  | RW   | Disable | Enable | 1   |

| Bit 6 | 38,   | ,37  | DIF_6                                 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 5 | 34,   | ,33  | DIF_5                                 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 4 | 30,   | ,29  | DIF_4                                 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 3 | 20,   | ,21  | DIF_3                                 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 2 | 16,   | ,17  | DIF_2                                 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 1 | 12,   | ,13  | DIF_1                                 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 0 | 8,    | ,9   | DIF_0                                 | Output Control   | RW   | Disable | Enable | 1   |

**SMBus Table: Output Control Register**

| Ву    | te 2  | Pin# | Name           | <b>Control Function</b> | Type  | 0              | 1         | PWD      |           |   |

|-------|-------|------|----------------|-------------------------|-------|----------------|-----------|----------|-----------|---|

| Bit 7 | 42    | ,41  | DIF_7          | Output Control          | RW    | Free-run       | Stoppable | 0        |           |   |

| Bit 6 | 38    | ,37  | DIF_6          | Output Control          | RW    | Free-run       | Stoppable | 0        |           |   |

| Bit 5 | 34    | ,33  | DIF_5          | Output Control          | RW    | Free-run       | Stoppable | 0        |           |   |

| Bit 4 | 30    | ,29  | DIF_4          | Output Control          | RW    | Free-run       | Stoppable | 0        |           |   |

| Bit 3 | 20,21 |      | <b>3</b> 20,21 |                         | DIF_3 | Output Control | RW        | Free-run | Stoppable | 0 |

| Bit 2 | 16    | ,17  | DIF_2          | Output Control          | RW    | Free-run       | Stoppable | 0        |           |   |

| Bit 1 | 12,   | ,13  | DIF_1          | Output Control          | RW    | Free-run       | Stoppable | 0        |           |   |

| Bit 0 | 8     | ,9   | DIF_0          | Output Control          | RW    | Free-run       | Stoppable | 0        |           |   |

**SMBus Table: Output Control Register**

| Ву    | te 3 | Pin # | Name                 | Control Function | Туре  | 0           | 1        | PWD |

|-------|------|-------|----------------------|------------------|-------|-------------|----------|-----|

| Bit 7 |      |       |                      | Reserved         | RW    | Rese        | Reserved |     |

| Bit 6 |      |       |                      | Reserved         | RW    | Rese        | Reserved |     |

| Bit 5 |      |       |                      | Reserved         | RW    | Rese        | Reserved |     |

| Bit 4 |      |       |                      | Reserved         | RW    | RW Reserved |          | X   |

| Bit 3 |      |       | Reserved RW Reserved |                  | erved | X           |          |     |

| Bit 2 |      |       |                      | Reserved         | RW    | Reserved    |          | X   |

| Bit 1 |      |       | Reserved RW Reserved |                  | erved | Х           |          |     |

| Bit 0 |      |       |                      | Reserved         | RW    | Rese        | erved    | X   |

SMBus Table: Vendor & Revision ID Register

| Ву    | te 4 Pin # | Name   | Control Function | Туре | 0 | 1 | PWD |

|-------|------------|--------|------------------|------|---|---|-----|

| Bit 7 | -          | RID3   |                  | R    | - | - | X   |

| Bit 6 | -          | RID2   | REVISION ID      | R    | - | - | Χ   |

| Bit 5 | -          | RID1   |                  | R    | - | - | Χ   |

| Bit 4 | -          | RID0   |                  | R    | - | - | X   |

| Bit 3 | -          | VID3   |                  | R    | • | - | 0   |

| Bit 2 | -          | VID2   | VENDOR ID        | R    | • | - | 0   |

| Bit 1 | -          | - VID1 |                  | R    | - | - | 0   |

| Bit 0 | -          | VID0   |                  | R    | - | - | 1   |

**SMBus Table: DEVICE ID**

| Ву    | rte 5               | Pin#                     | Name        | Control Function | Туре | 0        | 1        | PWD |

|-------|---------------------|--------------------------|-------------|------------------|------|----------|----------|-----|

| Bit 7 | Bit 7               |                          | Dev         | rice ID 7 (MSB)  | R    | Reserved |          | 1   |

| Bit 6 |                     | •                        |             | Device ID 6      | R    | Res      | Reserved |     |

| Bit 5 | -                   |                          |             | Device ID 5      | R    | Reserved |          | 0   |

| Bit 4 | - Device ID 4       |                          | Device ID 4 | R                | Res  | 0        |          |     |

| Bit 3 |                     | - Device ID 3 R Reserved |             | erved            | 0    |          |          |     |

| Bit 2 |                     | -                        |             | Device ID 2      | R    | Reserved |          | 0   |

| Bit 1 |                     | - Device ID 1 R Reserved |             | 0                |      |          |          |     |

| Bit 0 | - Device ID 0 R Res |                          | Res         | erved            | 1    |          |          |     |

**SMBus Table: Byte Count Register**

| Ву    | te 6 | Pin # | Name | Control Function          | Type | 0 | 1 | PWD |

|-------|------|-------|------|---------------------------|------|---|---|-----|

| Bit 7 | ,    | -     | BC7  |                           | RW   | • | - | 0   |

| Bit 6 |      | -     | BC6  |                           | RW   | • | - | 0   |

| Bit 5 | -    | -     | BC5  | Writing to this register  | RW   | • | - | 0   |

| Bit 4 |      | -     | BC4  | configures how many bytes | RW   | • | - | 0   |

| Bit 3 |      | -     | BC3  | will be read back.        | RW   | • | - | 0   |

| Bit 2 |      | -     | BC2  | Will be read back.        | RW   | • | - | 1   |

| Bit 1 | 1    |       | BC1  |                           | RW   | - | - | 1   |

| Bit 0 | ,    | - BC0 |      | RW                        | -    | - | 1 |     |

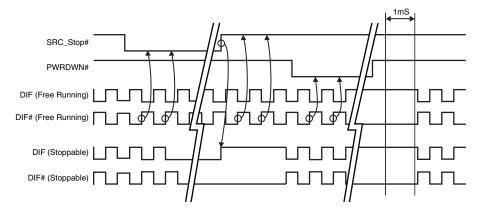

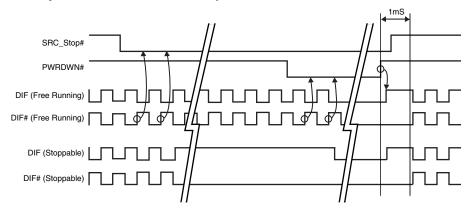

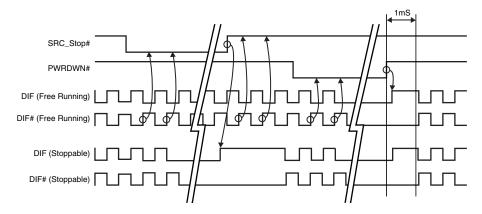

Note: Polarities in timing diagrams are shown OE\_INV = 0. They are similar to OE\_INV = 1.

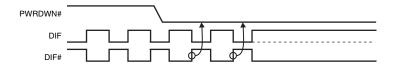

#### PD#, Power Down

The PD# pin cleanly shuts off all clocks and places the device into a power saving mode. PD# must be asserted before shutting off the input clock or power to insure an orderly shutdown. PD is asynchronous active-low input for both powering down the device and powering up the device. When PD# is asserted, all clocks will be driven high, or tri-stated (depending on the PD# drive mode and Output control bits) before the PLL is shut down.

#### **PD# Assertion**

When PD# is sampled low by two consecutive rising edges of DIF#, all DIF outputs must be held High, or tri-stated (depending on the PD# drive mode and Output control bits) on the next High-Low transition of the DIF# outputs. When the PD# drive mode bit is set to '0', all clock outputs will be held with DIF driven High with 2 x I<sub>REF</sub> and DIF# tri-stated. If the PD# drive mode bit is set to '1', both DIF and DIF# are tri-stated.

#### PD# De-assertion

Power-up latency is less than 1 ms. This is the time from de-assertion of the PD# pin, or VDD reaching 3.3V, or the time from valid SRC\_IN clocks until the time that stable clocks are output from the device (PLL Locked). If the PD# drive mode bit is set to '1', all the DIF outputs must driven to a voltage of >200 mV within 300 us of PD# de-assertion.

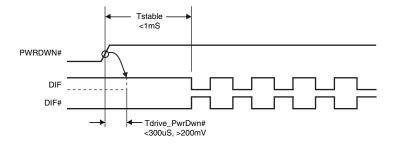

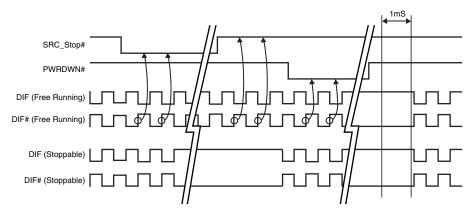

#### SRC STOP#

The SRC\_STOP# signal is an active-low asynchronous input that cleanly stops and starts the DIF outputs. A valid clock must be present on SRC\_IN for this input to work properly. The SRC\_STOP# signal is de-bounced and must remain stable for two consecutive rising edges of DIF# to be recognized as a valid assertion or de-assertion.

#### SRC STOP# - Assertion

Asserting SRC\_STOP# causes all DIF outputs to stop after their next transition (if the control register settings allow the output to stop). When the SRC\_STOP# drive bit is '0', the final state of all stopped DIF outputs is DIF = High and DIF# = Low. There is no change in output drive current. DIF is driven with 6xI<sub>REF</sub> DIF# is not driven, but pulled low by the termination. When the SRC\_STOP# drive bit is '1', the final state of all DIF output pins is Low. Both DIF and DIF# are not driven.

#### SRC\_STOP# - De-assertion (transition from '0' to '1')

All stopped differential outputs resume normal operation in a glitch-free manner. The de-assertion latency to active outputs is 2-6 DIF clock periods, with all DIF outputs resuming simultaneously. If the SRC\_STOP# drive control bit is '1' (tri-state), all stopped DIF outputs must be driven High (>200 mV) within 10 ns of de-assertion.

## SRC\_STOP\_1 (SRC\_Stop = Driven, PD = Driven)

#### SRC STOP 2 (SRC Stop =Tristate, PD = Driven)

## **SRC\_STOP\_3** (**SRC\_Stop** = **Driven**, **PD** = **Tristate**)

## SRC\_STOP\_4 (SRC\_Stop = Tristate, PD = Tristate)

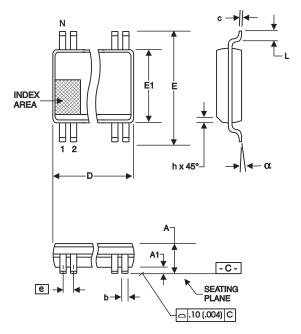

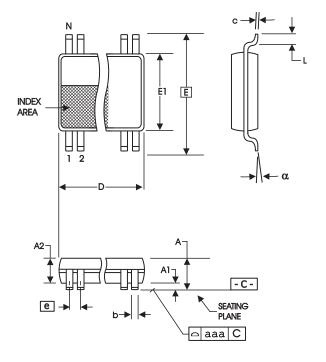

|        | In Millimeters    |       | In Inches         |       |

|--------|-------------------|-------|-------------------|-------|

| SYMBOL | COMMON DIMENSIONS |       | COMMON DIMENSIONS |       |

|        | MIN               | MAX   | MIN               | MAX   |

| Α      | 2.41              | 2.80  | .095              | .110  |

| A1     | 0.20              | 0.40  | .008              | .016  |

| b      | 0.20              | 0.34  | .008              | .0135 |

| С      | 0.13              | 0.25  | .005              | .010  |

| D      | SEE VARIATIONS    |       | SEE VARIATIONS    |       |

| Е      | 10.03             | 10.68 | .395              | .420  |

| E1     | 7.40              | 7.60  | .291              | .299  |

| е      | 0.635 BASIC       |       | 0.025 BASIC       |       |

| h      | 0.38              | 0.64  | .015              | .025  |

| L      | 0.50              | 1.02  | .020              | .040  |

| N      | SEE VARIATIONS    |       | SEE VARIATIONS    |       |

| α      | 0°                | 8°    | 0°                | 8°    |

#### **VARIATIONS**

| N  | D mm. |       | D (inch) |      |

|----|-------|-------|----------|------|

| IN | MIN   | MAX   | MIN      | MAX  |

| 48 | 15.75 | 16.00 | .620     | .630 |

Reference Doc.: JEDEC Publication 95, MO-118

10-0034

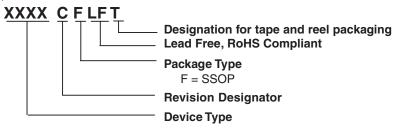

# **Ordering Information**

## 9DB801CFLFT

Example:

48-Lead, 6.10 mm. Body, 0.50 mm. Pitch TSSOP (240 mil) (20 mil)

|        | In Millimeters                |      | In Inches         |      |

|--------|-------------------------------|------|-------------------|------|

| SYMBOL | COMMON DIMENSIONS             |      | COMMON DIMENSIONS |      |

|        | MIN                           | MAX  | MIN               | MAX  |

| Α      |                               | 1.20 |                   | .047 |

| A1     | 0.05                          | 0.15 | .002              | .006 |

| A2     | 0.80                          | 1.05 | .032              | .041 |

| b      | 0.17                          | 0.27 | .007              | .011 |

| С      | 0.09                          | 0.20 | .0035             | .008 |

| D      | SEE VARIATIONS SEE VARIATIONS |      | RIATIONS          |      |

| E      | 8.10 BASIC                    |      | 0.319 BASIC       |      |

| E1     | 6.00                          | 6.20 | .236              | .244 |

| е      | 0.50 BASIC                    |      | 0.020 BASIC       |      |

| L      | 0.45                          | 0.75 | .018              | .030 |

| N      | SEE VARIATIONS                |      | SEE VARIATIONS    |      |

| а      | 0°                            | 8°   | 0°                | 8°   |

| aaa    |                               | 0.10 |                   | .004 |

#### **VARIATIONS**

| NI NI | D mm. |       | D (inch) |      |      |

|-------|-------|-------|----------|------|------|

|       | N     | MIN   | MAX      | MIN  | MAX  |

|       | 48    | 12.40 | 12.60    | .488 | .496 |

Reference Doc.: JEDEC Publication 95, MO-153

10-0039

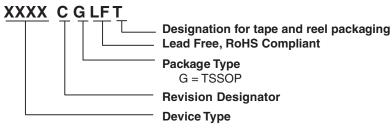

# **Ordering Information**

#### 9DB801CGLFT

Example:

## ICS9DB801C Eight Output Differential Buffer for PCI Express (50-200MHz)

# **Revision History**

| Rev. | Issue Date | Description                                                     | Page # |

|------|------------|-----------------------------------------------------------------|--------|

| Α    | 4/8/2005   | Release to Final                                                |        |

|      |            | . Added Polarity Table.                                         |        |

|      |            | 2. Updated Electrical Characteristics.                          |        |

|      |            | 3. Updated LF Ordering Information from "Annealed Lead Free" to | 1, 7,  |

| В    | 9/7/2006   | "RoHS Compliant".                                               | 16-17  |

| С    | 2/29/2008  | Added Input Clock Specs                                         | 8      |

| D    | 12/3/2008  | Removed ICS prefix from ordering information.                   | 17-18  |

| Е    | 1/27/2011  | Updated terminaton Figure 4.                                    |        |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.