# Low Power Clock for ATI RS/RD600 series chipsets for AMD CPUs

ICS9LPRS462

# Description

ATI RD/RS600 series systems using AMD CPUs

# **Output Features**

- Integrated Series Resistors on differential outputs

- Greyhound Compatible CPU outputs

- 2 0.7V Low Power differential CPU pairs

- 8 0.7V Low Power differential SRC pairs

- 4 0.7V Low Power differential ATIG pairs

- 1 66 MHz HyperTransport clock

- 2 48MHz USB clocks

- 3 14.318MHz Reference clocks

#### Features/Benefits:

- 3 Programmable Clock Request pins for SRC and ATIG clocks

- ATIGCLKs are programmable for frequency

- Spread Spectrum for EMI reduction

- Outputs may be disabled via SMBus

- External crystal load capacitors for maximum frequency accuracy

### **Key Specifications**

- CPU outputs cycle-to-cycle jitter <150ps</li>

- SRC outputs cycle-to-cycle jitter < 125ps

- ATIG outputs cycle-to-cycle jitter < 125ps</li>

- +/- 100ppm frequency accuracy on all outputs if REF is tuned to +/-100ppm

#### Funtionality

| FS2  | FS1 | FS0 | CPU    | HTT   | SRC    | ATIG   | USB   |

|------|-----|-----|--------|-------|--------|--------|-------|

| F 52 | F31 | F30 | MHz    | MHz   | MHz    | MHz    | MHz   |

| 0    | 0   | 0   | Hi-Z   | Hi-Z  | 100.00 | 100.00 | 48.00 |

| 0    | 0   | 1   | X/2    | X/3   | 100.00 | 100.00 | 48.00 |

| 0    | 1   | 0   | 230.00 | 76.67 | 100.00 | 100.00 | 48.00 |

| 0    | 1   | 1   | 240.00 | 80.00 | 100.00 | 100.00 | 48.00 |

| 1    | 0   | 0   | 100.00 | 66.66 | 100.00 | 100.00 | 48.00 |

| 1    | 0   | 1   | 133.33 | 66.66 | 100.00 | 100.00 | 48.00 |

| 1    | 1   | 0   | 166.67 | 66.66 | 100.00 | 100.00 | 48.00 |

| 1    | 1   | 1   | 200.00 | 66.66 | 100.00 | 100.00 | 48.00 |

#### **Power Groups**

| Pin Nu      | umber       | Description                  |

|-------------|-------------|------------------------------|

| VDD         | GND         | Description                  |

| 5           | 8           | USB_48 outputs               |

| 14,23,26,36 | 15,22,27,37 | SRCCLK outputs               |

| 33          | 32          | ATIGCLK differential outputs |

| 42          | 41          | Analog, PLL                  |

| 46          | 45          | CPUCLK8 differential outputs |

| 52          | 50          | HTTCLK output                |

| 2           | 1           | REF outputs                  |

# Pin Configuration

| figuratio           | on |          |    |                          |

|---------------------|----|----------|----|--------------------------|

| GNDREF              | 1  |          | 64 | FS0/REF0                 |

| VDDREF              | 2  |          | 63 | FS1/REF1                 |

| X1                  | 3  |          | 62 | FS2/REF2                 |

| X2                  | 4  |          | 61 | **PD                     |

| VDD48               | 5  |          | 60 | VDDHTT                   |

| 48MHz_0             | 6  |          | 59 | HTTCLK0                  |

| 48MHz_1             | 7  |          |    | GNDHTT                   |

| GND48               | -  |          |    | *CLKREQA#                |

| SMBCLK              | -  |          |    | CPUKG0T_LPR              |

| SMBDAT              |    |          |    | CPUKG0C_LPR              |

| RESET_IN#           |    |          | -  | VDDCPU                   |

| SRC7T_LPR           |    |          |    | GNDCPU                   |

| SRC7C_LPR           |    |          |    | CPUKG1T_LPR              |

| VDDSRC              |    | Ŋ        |    | CPUKG1C_LPR              |

| GNDSRC              | -  | 46       |    | VDDA                     |

| SRC6T_LPR           | -  | SE       | -  | GNDA                     |

| SRC6C_LPR           |    | 9LPRS462 | -  | NC                       |

| SRC5T_LPR           |    | <b>Ъ</b> |    | SRC0T_LPR                |

| SRC5C_LPR           |    | •        |    | SRC0C_LPR                |

| SRC4T_LPR           |    |          | -  | GNDSRC                   |

| SRC4C_LPR           |    |          |    | VDDSRC                   |

| GNDSRC              |    |          |    | SRC1T_LPR                |

| VDDSRC              |    |          |    | SRC1C_LPR                |

| SRC3T_LPR           |    |          |    | ATIG0T_LPR               |

| SRC3C_LPR           |    |          |    | ATIG0C_LPR               |

| SRC2T_LPR           |    |          |    | VDDATIG<br>GNDATIG       |

| SRC2C_LPR<br>VDDSRC |    |          |    |                          |

| GNDSRC              | -  |          |    | ATIG1T_LPR               |

| ATIG3T LPR          | -  |          |    | ATIG1C_LPR<br>ATIG2T_LPR |

| ATIG31_LPR          |    |          |    | ATIG2C_LPR               |

| *CLKREQB#           |    |          |    | *CLKREQC#                |

|                     | 02 |          | 00 |                          |

|                     |    | 64-TSSOP |    |                          |

\* Internal Pull-Up Resistor

# **Pin Description**

| PIN # | PIN NAME   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                      |

|-------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | GNDREF     | GND  | Ground pin for the REF outputs.                                                                                                                                                                                                                                  |

| 2     | VDDREF     | PWR  | Ref, XTAL power supply, nominal 3.3V                                                                                                                                                                                                                             |

| 3     | X1         | IN   | Crystal input, nominally 14.318MHz                                                                                                                                                                                                                               |

| 4     | X2         | OUT  | Crystal output, nominally 14.318MHz                                                                                                                                                                                                                              |

| 5     | VDD48      | PWR  | Power pin for the 48MHz outputs and core. 3.3V                                                                                                                                                                                                                   |

| 6     | 48MHz_0    | OUT  | 48MHz clock output.                                                                                                                                                                                                                                              |

| 7     | 48MHz_1    | OUT  | 48MHz clock output.                                                                                                                                                                                                                                              |

| 8     | GND48      | GND  | Ground pin for the 48MHz outputs                                                                                                                                                                                                                                 |

| 9     | SMBCLK     | IN   | Clock pin of SMBus circuitry, 5V tolerant.                                                                                                                                                                                                                       |

| 10    | SMBDAT     | I/O  | Data pin for SMBus circuitry, 5V tolerant.                                                                                                                                                                                                                       |

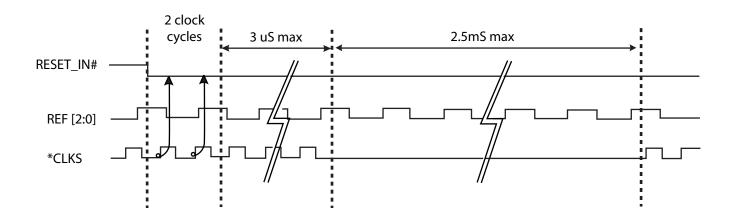

| 11    | RESET_IN#  | IN   | Real Time falling edge triggered input, When asserted, the part initiates a power up<br>reset with the SMBus being reset to it's power up values, and all PLL derived clocks<br>stopped for the duration of Power up Stabilization. REF outputs continue to run. |

| 12    | SRC7T_LPR  | OUT  | True clock of low power differential SRC clock pair with integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)                                                                                                                              |

| 13    | SRC7C_LPR  | OUT  | Complement clock of low power differential SRC clock pair with integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)                                                                                                                        |

| 14    | VDDSRC     | PWR  | Supply for SRC, 3.3V nominal                                                                                                                                                                                                                                     |

| 15    | GNDSRC     | GND  | Ground pin for the SRC outputs                                                                                                                                                                                                                                   |

| 16    | SRC6T_LPR  | OUT  | True clock of low power differential SRC clock pair with integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)                                                                                                                              |

| 17    | SRC6C_LPR  | OUT  | Complement clock of low power differential SRC clock pair with integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)                                                                                                                        |

| 18    | SRC5T_LPR  | OUT  | True clock of low power differential SRC clock pair with integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)                                                                                                                              |

| 19    | SRC5C_LPR  | OUT  | Complement clock of low power differential SRC clock pair with integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)                                                                                                                        |

| 20    | SRC4T_LPR  | OUT  | True clock of low power differential SRC clock pair with integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)                                                                                                                              |

| 21    | SRC4C_LPR  | OUT  | Complement clock of low power differential SRC clock pair with integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)                                                                                                                        |

| 22    | GNDSRC     | GND  | Ground pin for the SRC outputs                                                                                                                                                                                                                                   |

| 23    | VDDSRC     | PWR  | Supply for SRC, 3.3V nominal                                                                                                                                                                                                                                     |

| 24    | SRC3T_LPR  | OUT  | True clock of low power differential SRC clock pair with integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)                                                                                                                              |

| 25    | SRC3C_LPR  | OUT  | Complement clock of low power differential SRC clock pair with integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)                                                                                                                        |

| 26    | SRC2T_LPR  | OUT  | True clock of low power differential SRC clock pair with integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)                                                                                                                              |

| 27    | SRC2C_LPR  | OUT  | Complement clock of low power differential SRC clock pair with integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)                                                                                                                        |

| 28    | VDDSRC     | PWR  | Supply for SRC, 3.3V nominal                                                                                                                                                                                                                                     |

| 29    | GNDSRC     | GND  | Ground pin for the SRC outputs                                                                                                                                                                                                                                   |

| 30    | ATIG3T_LPR | OUT  | True clock of low-power differential push-pull PCI-Express pair with integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)                                                                                                                  |

| 31    | ATIG3C_LPR | OUT  | Complementary clock of low-power differential push-pull PCI-Express pair with<br>integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)                                                                                                      |

| 32    | *CLKREQB#  | IN   | Programmable Clock Request pin for SRC/ATIG/SB_SRC outputs. If output is selected for control, then that output is controlled as follows:<br>0 = Enabled, 1 = Tri-state                                                                                          |

# Pin Description (Continued)

| PIN # | PIN NAME    | TYPE  | DESCRIPTION                                                                            |

|-------|-------------|-------|----------------------------------------------------------------------------------------|

|       |             |       | Programmable Clock Request pin for SRC/ATIG/SB_SRC outputs. If output is selected      |

| 33    | *CLKREQC#   | IN    | for control, then that output is controlled as follows:                                |

|       |             |       | 0 = Enabled, 1 = Tri-state                                                             |

| 34    | ATIG2C_LPR  | OUT   | Complementary clock of low-power differential push-pull PCI-Express pair with          |

| 04    |             | 001   | integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)             |

| 35    | ATIG2T_LPR  | OUT   | True clock of low-power differential push-pull PCI-Express pair with integrated 33 ohm |

|       | /           |       | series resistor. (no 500hm shunt resistor to GND needed)                               |

| 36    | ATIG1C_LPR  | OUT   | Complementary clock of low-power differential push-pull PCI-Express pair with          |

|       | ////·       |       | integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)             |

| 37    | ATIG1T_LPR  | OUT   | True clock of low-power differential push-pull PCI-Express pair with integrated 33 ohm |

|       | _           |       | series resistor. (no 500hm shunt resistor to GND needed)                               |

| 38    | GNDATIG     | GND   | Ground pin for the ATIG outputs                                                        |

| 39    | VDDATIG     | PWR   | Power supply for ATIG core, nominal 3.3V                                               |

| 40    | ATIG0C_LPR  | OUT   | Complementary clock of low-power differential push-pull PCI-Express pair with          |

| 40    |             | 001   | integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)             |

| 41    | ATIG0T_LPR  | OUT   | True clock of low-power differential push-pull PCI-Express pair with integrated 33 ohm |

| - 1   |             | 001   | series resistor. (no 500hm shunt resistor to GND needed)                               |

| 42    | SRC1C_LPR   | OUT   | Complement clock of low power differential SRC clock pair with integrated 33 ohm       |

|       |             | 001   | series resistor. (no 500hm shunt resistor to GND needed)                               |

| 43    | SRC1T_LPR   | OUT   | True clock of low power differential SRC clock pair with integrated 33 ohm series      |

|       |             |       | resistor. (no 50ohm shunt resistor to GND needed)                                      |

| 44    | VDDSRC      | PWR   | Supply for SRC, 3.3V nominal                                                           |

| 45    | GNDSRC      | GND   | Ground pin for the SRC outputs                                                         |

| 46    | SRC0C_LPR   | OUT   | Complement clock of low power differential SRC clock pair with integrated 33 ohm       |

| 40    |             | 001   | series resistor. (no 500hm shunt resistor to GND needed)                               |

| 47    | SRC0T_LPR   | OUT   | True clock of low power differential SRC clock pair with integrated 33 ohm series      |

| 11    |             | 001   | resistor. (no 50ohm shunt resistor to GND needed)                                      |

| 48    | NC          | NC    | No Connect                                                                             |

| 49    | GNDA        | GND   | Ground for the Analog Core                                                             |

| 50    | VDDA        | PWR   | 3.3V Power for the Analog Core                                                         |

| E 4   |             | OUT   | Complementary signal of low-power differential push-pull AMD K8 "Greyhound" clock      |

| 51    | CPUKG1C_LPR | 001   | with integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)        |

| 52    | CPUKG1T_LPR | OUT   | True signal of low-power differential push-pull AMD K8 "Greyhound" clock with          |

| 52    | CFORGIT_EFR | 001   | integrated 33 ohm series resistor. (no 50ohm shunt resistor to GND needed)             |

| 53    | GNDCPU      | GND   | Ground pin for the CPU outputs                                                         |

| 54    | VDDCPU      | PWR   | Supply for CPU, 3.3V nominal                                                           |

|       |             | 0.117 | Complementary signal of low-power differential push-pull AMD K8 "Greyhound" clock      |

| 55    | CPUKG0C_LPR | OUT   | with integrated 33 ohm series resistor. (no 500hm shunt resistor to GND needed)        |

|       |             | 0.UT  | True signal of low-power differential push-pull AMD K8 "Greyhound" clock with          |

| 56    | CPUKG0T_LPR | OUT   | integrated 33 ohm series resistor. (no 50 ohm shunt resistor to GND needed)            |

|       |             |       | Programmable Clock Request pin for SRC/ATIG/SB_SRC outputs. If output is selected      |

| 57    | *CLKREQA#   | IN    | for control, then that output is controlled as follows:                                |

|       |             |       | 0 = Enabled, 1 = Tri-state                                                             |

| 58    | GNDHTT      | PWR   | Ground pin for the HTT outputs                                                         |

| 59    | HTTCLK0     | OUT   | 3.3V single ended 66MHz hyper transport clock                                          |

| 60    | VDDHTT      | PWR   | Supply for HTT clocks, nominal 3.3V.                                                   |

|       |             |       | Enter /Exit Power Down.                                                                |

| 61    | **PD        | IN    | 1 = Power Down, 0 = normal operation.                                                  |

| 62    | FS2/REF2    | I/O   | Frequency select latch input pin/ 3.3V 14.318MHz reference clock                       |

| 63    | FS1/REF1    | 1/O   | Frequency select latch input pin/ 3.3V 14.318MHz reference clock                       |

|       |             |       |                                                                                        |

| 64    | FS0/REF0    | I/O   | Frequency select latch input pin/ 3.3V 14.318MHz reference clock                       |

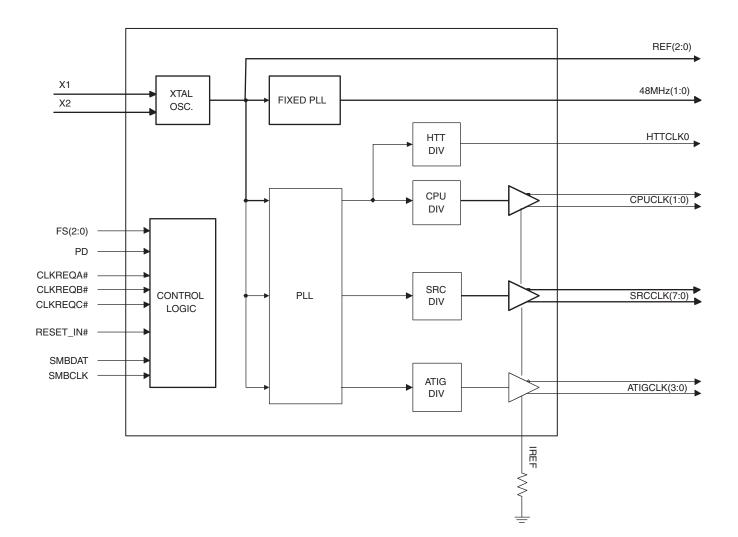

**General Description** The **ICS9LPRS462** is a main clock synthesizer chip that provides all clocks required for ATI RD/RS600-based systems. An SMBus interface allows full control of the device.

# **Funtional Block Diagram**

#### **Absolute Max**

| PARAMETER                          | PARAMETER SYMBOL |   | MIN          | TYP | MAX                    | UNITS | Notes |

|------------------------------------|------------------|---|--------------|-----|------------------------|-------|-------|

| 3.3V Core Supply Voltage           | VDD_A            | - |              |     | $V_{DD} + 0.5V$        | V     | 1     |

| 3.3V Logic Input Supply<br>Voltage | VDD_In           | - | GND -<br>0.5 |     | V <sub>DD</sub> + 0.5V | V     | 1     |

| Storage Temperature                | Ts               | - | -65          |     | 150                    | °C    | 1     |

| Ambient Operating Temp             | Tambient         | - | 0            |     | 70                     | °C    | 1     |

| Case Temperature Tcase             |                  | - |              |     | 115                    | °C    | 1     |

| Input ESD protection HBM           | ESD prot         | - | 2000         |     |                        | V     | 1     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

#### Electrical Characteristics - Input/Supply/Common Output Parameters

| PARAMETER                                  | SYMBOL               | CONDITIONS*                                              | MIN                   | TYP      | MAX                   | UNITS | Note |

|--------------------------------------------|----------------------|----------------------------------------------------------|-----------------------|----------|-----------------------|-------|------|

| Input High Voltage                         | V <sub>IH</sub>      | 3.3 V +/-5%                                              | 2                     |          | V <sub>DD</sub> + 0.3 | V     | 1    |

| Input Low Voltage                          | V <sub>IL</sub>      | 3.3 V +/-5%                                              | V <sub>ss</sub> - 0.3 |          | 0.8                   | V     | 1    |

| Input High Current                         | I <sub>IH</sub>      | $V_{IN} = V_{DD}$                                        | -5                    |          | 5                     | uA    | 1    |

| Input Low Current                          | I <sub>IL1</sub>     | V <sub>IN</sub> = 0 V; Inputs with no pull-up resistors  | -5                    |          |                       | uA    | 1    |

|                                            | I <sub>IL2</sub>     | V <sub>IN</sub> = 0 V; Inputs with pull-up<br>resistors  | -200                  |          |                       | uA    | 1    |

| Low Threshold Input-<br>High Voltage       | $V_{\rm IH\_FS}$     | 3.3 V +/-5%                                              | 0.7                   |          | V <sub>DD</sub> + 0.3 | V     | 1    |

| Low Threshold Input-<br>Low Voltage        | $V_{\rm IL_FS}$      | 3.3 V +/-5%                                              | V <sub>SS</sub> - 0.3 |          | 0.35                  | v     | 1    |

| Operating Current                          | I <sub>DD3.30P</sub> | 9LPRS462, all outputs driven                             |                       |          | 200                   | mA    | 1    |

| opolating outlott                          | DD3.30P              | 9LPRS464, all outputs driven                             |                       |          | 180                   | mA    | 1    |

| Powerdown Current                          | I <sub>DD3.3PD</sub> | all diff pairs low/low                                   |                       |          | 21                    | mA    | 1    |

| Input Frequency                            | F <sub>i</sub>       | $V_{DD} = 3.3 V$                                         |                       | 14.31818 |                       | MHz   | 2    |

| Pin Inductance                             | L <sub>pin</sub>     |                                                          |                       |          | 7                     | nH    | 1    |

|                                            | CIN                  | Logic Inputs                                             |                       |          | 5                     | pF    | 1    |

| Input Capacitance                          | C <sub>OUT</sub>     | Output pin capacitance                                   |                       |          | 6                     | pF    | 1    |

|                                            | C <sub>INX</sub>     | X1 & X2 pins                                             |                       |          | 5                     | pF    | 1    |

| Clk Stabilization                          | T <sub>STAB</sub>    | From VDD Power-Up or de-<br>assertion of PD to 1st clock |                       |          | 1.8                   | ms    | 1    |

| Modulation Frequency                       |                      | Triangular Modulation                                    | 30                    |          | 33                    | kHz   | 1    |

| Tdrive_PD                                  |                      | CPU output enable after<br>PD de-assertion               |                       |          | 300                   | us    | 1    |

| Tfall_PD                                   |                      | PD fall time of                                          |                       |          | 5                     | ns    | 1    |

| Trise_PD                                   |                      | PD rise time of                                          |                       |          | 5                     | ns    | 1    |

| SMBus Voltage                              | V <sub>DD</sub>      |                                                          | 2.7                   |          | 5.5                   | V     | 1    |

| Low-level Output Voltage                   | V <sub>OL</sub>      | @ I <sub>PULLUP</sub>                                    |                       |          | 0.4                   | V     | 1    |

| Current sinking at V <sub>OL</sub> = 0.4 V | I <sub>PULLUP</sub>  |                                                          | 4                     |          |                       | mA    | 1    |

| SMBCLK/SMBDAT<br>Clock/Data Rise Time      | T <sub>RI2C</sub>    | (Max VIL - 0.15) to<br>(Min VIH + 0.15)                  |                       |          | 1000                  | ns    | 1    |

| SMBCLK/SMBDAT<br>Clock/Data Fall Time      | T <sub>FI2C</sub>    | (Min VIH + 0.15) to<br>(Max VIL - 0.15)                  |                       |          | 300                   | ns    | 1    |

\*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V + -5%

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> Input frequency should be measured at the REF pin and tuned to ideal 14.31818MHz to meet ppm frequency accuracy on PLL outputs.

IDT<sup>™</sup>/ICS<sup>™</sup> Low Power Clock for ATI RS/RD600 series chipsets for AMD CPUs

|                                         |                       |                                               |       | ••••• |      |       |       |

|-----------------------------------------|-----------------------|-----------------------------------------------|-------|-------|------|-------|-------|

| PARAMETER                               | SYMBOL                | CONDITIONS                                    | MIN   | TYP   | MAX  | UNITS | NOTES |

| Crossing Point Variation                | $\Delta V_{CROSS}$    | Single-ended Measurement                      |       |       | 140  | mV    | 1,2,5 |

| Frequency                               | f                     | Spread Specturm On                            | 198.8 |       | 200  | MHz   | 1,3   |

| Long Term Accuracy                      | ppm                   | Spread Specturm Off                           | -300  |       | +300 | ppm   | 1,11  |

| Rising Edge Slew Rate                   | S <sub>RISE</sub>     | Differential Measurement                      | 0.5   |       | 10   | V/ns  | 1,4   |

| Falling Edge Slew Rate                  | S <sub>FALL</sub>     | Differential Measurement                      | 0.5   |       | 10   | V/ns  | 1,4   |

| Slew Rate Variation                     | t <sub>SLVAR</sub>    | Single-ended Measurement                      |       |       | 20   | %     | 1     |

| CPU, DIF HTT Jitter - Cycle to<br>Cycle | CPUJ <sub>C2C</sub>   | Differential Measurement                      |       |       | 150  | ps    | 1,6   |

| Accumulated Jitter                      | t <sub>JACC</sub>     | See Notes                                     |       |       | 1    | ns    | 1,7   |

| Peak to Peak Differential Voltage       | V <sub>D(PK-PK)</sub> | Differential Measurement                      | 400   |       | 2400 | mV    | 1,8   |

| Differential Voltage                    | V <sub>D</sub>        | Differential Measurement                      | 200   |       | 1200 | mV    | 1,9   |

| Duty Cycle                              | D <sub>CYC</sub>      | Differential Measurement                      | 45    |       | 55   | %     | 1     |

| Amplitude Variation                     | $\Delta V_D$          | Change in $V_{\rm D}\text{DC}$ cycle to cycle | -75   |       | 75   | mV    | 1,10  |

| CPU Skew                                | CPU <sub>SKEW10</sub> | Differential Measurement                      |       |       | 100  | ps    | 1     |

#### AC Electrical Characteristics - Low-Power DIF Outputs: CPUKG and HTT

Guaranteed by design and characterization, not 100% tested in production.

Single-ended measurement at crossing point. Value is maximum – minimum over all time. DC value of common mode is not important due to the blocking cap.

Minimum Frequency is a result of 0.5% down spread spectrum

Differential measurement through the range of  $\pm 100$  mV, differential signal must remain monotonic and within slew rate spec when crossing through this region.

<sup>5</sup> Defined as the total variation of all crossing voltages of CLK rising and CLK# falling. Matching applies to rising edge rate of CLK and falling edge of CLK#. It is measured using a +/-75mV window centered on the average cross point where CLK meets CLK#.

<sup>6</sup> Max difference of t<sub>CYCLE</sub> between any two adjacent cycles.

<sup>7</sup> Accumulated tjc.over a 10 µs time period, measured with JIT2 TIE at 50ps interval.

<sup>8</sup> VD(PK-PK) is the overall magnitude of the differential signal.

<sup>9</sup> VD(min) is the amplitude of the ring-back differential measurement, guaranteed by design, that ring-back will not cross 0V VD. VD(max) is the largest amplitude allowed.

<sup>10</sup> The difference in magnitude of two adjacent VD\_DC measurements. VD\_DC is the stable post overshoot and ring-back part of the signal.

<sup>11</sup> All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

| PARAMETER                             | SYMBOL               | CONDITIONS               | ONDITIONS MIN TYP MAX |  | UNITS | NOTES |       |

|---------------------------------------|----------------------|--------------------------|-----------------------|--|-------|-------|-------|

| Rising Edge Slew Rate                 | t <sub>slR</sub>     | Differential Measurement | 0.5                   |  | 2     | V/ns  | 1,2   |

| Falling Edge Slew Rate                | t <sub>FLR</sub>     | Differential Measurement | 0.5                   |  | 2     | V/ns  | 1,2   |

| Slew Rate Variation                   | t <sub>slvar</sub>   | Single-ended Measurement |                       |  | 20    | %     | 1     |

| Maximum Output Voltage                | V <sub>HIGH</sub>    | Includes overshoot       |                       |  | 1150  | mV    | 1     |

| Minimum Output Voltage                | V <sub>LOW</sub>     | Includes undershoot      | -300                  |  |       | mV    | 1     |

| Differential Voltage Swing            | V <sub>SWING</sub>   | Differential Measurement | 300                   |  |       | mV    | 1     |

| Crossing Point Voltage                | V <sub>XABS</sub>    | Single-ended Measurement | 300                   |  | 550   | mV    | 1,3,4 |

| Crossing Point Variation              | V <sub>XABSVAR</sub> | Single-ended Measurement |                       |  | 140   | mV    | 1,3,5 |

| Duty Cycle                            | D <sub>CYC</sub>     | Differential Measurement | 45                    |  | 55    | %     | 1     |

| SRC, ATIG, Jitter - Cycle to<br>Cycle | SRCJ <sub>C2C</sub>  | Differential Measurement |                       |  | 125   | ps    | 1     |

| SRC[5:0] Skew                         | SRC <sub>SKEW</sub>  | Differential Measurement |                       |  | 250   | ps    | 1     |

| SB_SRC[1:0] Skew                      | SRC <sub>SKEW</sub>  | Differential Measurement |                       |  | 100   | ps    | 1     |

| ATIG[3:0] Skew                        | SRC <sub>SKEW</sub>  | Differential Measurement |                       |  | 100   | ps    | 1     |

#### AC Electrical Characteristics - Low-Power DIF Outputs: SRC and ATIG

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> Slew rate measured through Vswing centered around differential zero

<sup>3</sup> Vxabs is defined as the voltage where CLK = CLK#

<sup>4</sup> Only applies to the differential rising edge (CLK rising and CLK# falling)

<sup>5</sup> Defined as the total variation of all crossing voltages of CLK rising and CLK# falling. Matching applies to rising edge rate of

<sup>6</sup> All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

#### **Electrical Characteristics - USB - 48MHz**

| PARAMETER              | SYMBOL                | CONDITIONS*                                      | MIN     | N TYP MAX |         | UNITS | NOTES |  |  |

|------------------------|-----------------------|--------------------------------------------------|---------|-----------|---------|-------|-------|--|--|

| Long Accuracy          | ppm                   | see Tperiod min-max values                       | -100    |           | 100     | ppm   | 1,2   |  |  |

| Clock period           | T <sub>period</sub>   | 48.00MHz output nominal                          | 20.8229 |           | 20.8344 | ns    | 2     |  |  |

| Clock Low Time         | T <sub>low</sub>      | Measure from < 0.6V                              | 9.3750  |           | 11.4580 | ns    | 2     |  |  |

| Clock High Time        | T <sub>high</sub>     | Measure from > 2.0V                              | 9.3750  |           | 11.4580 | ns    | 2     |  |  |

| Output High Voltage    | V <sub>OH</sub>       | I <sub>OH</sub> = -1 mA                          | 2.4     |           |         | V     | 1     |  |  |

| Output Low Voltage     | V <sub>OL</sub>       | I <sub>OL</sub> = 1 mA                           |         |           | 0.55    | V     | 1     |  |  |

|                        | 1                     | V <sub>OH</sub> @MIN = 1.0 V                     | -33     |           |         | mA    | 1     |  |  |

| Output High Current    | I <sub>ОН</sub>       | V <sub>OH</sub> @MAX = 3.135 V                   |         |           | -33     | mA    | 1     |  |  |

|                        |                       | V <sub>OL</sub> @ MIN = 1.95 V                   | 30      |           |         | mA    | 1     |  |  |

| Output Low Current     | I <sub>OL</sub>       | V <sub>OL</sub> @ MAX = 0.4 V                    |         |           | 38      | mA    | 1     |  |  |

| Rise Time              | t <sub>r_USB</sub>    | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ | 0.5     |           | 1.5     | ns    | 1     |  |  |

| Fall Time              | t <sub>f_USB</sub>    | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ | 0.5     |           | 1.5     | ns    | 1     |  |  |

| Duty Cycle             | d <sub>t1</sub>       | V <sub>T</sub> = 1.5 V                           | 45      |           | 55      | %     | 1     |  |  |

| Group Skew             | t <sub>skew</sub>     | V <sub>T</sub> = 1.5 V                           |         |           | 250     | ps    | 1     |  |  |

| Jitter, Cycle to cycle | t <sub>jcyc-cyc</sub> | V <sub>T</sub> = 1.5 V                           |         |           | 130     | ps    | 1,2   |  |  |

\*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%, CL = 5 pF with Rs =  $33\Omega$  (unless otherwise specified)

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup>ICS recommended and/or chipset vendor layout guidelines must be followed to meet this specification

| PARAMETER           | SYMBOL                | CONDITIONS                                                      | CONDITIONS MIN TYP MAX |       |         |     | Notes |

|---------------------|-----------------------|-----------------------------------------------------------------|------------------------|-------|---------|-----|-------|

| Long Accuracy       | ppm                   | see Tperiod min-max values                                      | -100                   | 0     | 100     | ppm | 1,2   |

| Clock period        | T <sub>period</sub>   | 14.318MHz output nominal                                        | 69.8270                | 69.84 | 69.8550 | ns  | 2     |

| Clock Low Time      | T <sub>low</sub>      | Measure from < 0.6V                                             | 30.9290                |       | 37.9130 | ns  | 2     |

| Clock High Time     | T <sub>high</sub>     | Measure from > 2.0V                                             | 30.9290                |       | 37.9130 | ns  | 2     |

| Output High Voltage | V <sub>OH</sub>       | I <sub>OH</sub> = -1 mA                                         | 2.4                    |       |         | V   | 1     |

| Output Low Voltage  | V <sub>OL</sub>       | I <sub>OL</sub> = 1 mA                                          | 0.4                    |       | V       | 1   |       |

| Output High Current | I <sub>OH</sub>       | V <sub>OH</sub> @MIN = 1.0 V,<br>V <sub>OH</sub> @MAX = 3.135 V | -29 -23                |       | mA      | 1   |       |

| Output Low Current  | I <sub>OL</sub>       | V <sub>OL</sub> @MIN = 1.95 V,<br>V <sub>OL</sub> @MAX = 0.4 V  | 29 27                  |       | mA      | 1   |       |

| Rise Time           | t <sub>r1</sub>       | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$                | 1                      |       | 1.5     | ns  | 1     |

| Fall Time           | t <sub>f1</sub>       | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$                | / 1 1.5                |       | ns      | 1   |       |

| Skew                | t <sub>sk1</sub>      | V <sub>T</sub> = 1.5 V                                          | 100                    |       | ps      | 1   |       |

| Duty Cycle          | d <sub>t1</sub>       | V <sub>T</sub> = 1.5 V                                          | 45 55                  |       | %       | 1   |       |

| Jitter              | t <sub>jcyc-cyc</sub> | V <sub>T</sub> = 1.5 V                                          |                        |       | 300     | ps  | 1     |

#### **Electrical Characteristics - REF-14.318MHz**

\*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%, CL = 5 pF with Rs =  $33\Omega$  (unless otherwise specified)

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

#### Table1: CPU and HTT Frequency Selection Table

|              |            | yte 0      |            |            |                |              |             |                |

|--------------|------------|------------|------------|------------|----------------|--------------|-------------|----------------|

| Bit4         | Bit3       | Bit2       | Bit1       | Bit0       | CPUCLK         |              | Converse    | Overalesk      |

| CPU<br>SS_EN | CPU<br>FS3 | CPU<br>FS2 | CPU<br>FS1 | CPU<br>FS0 | (2:0)<br>(MHz) | HTT<br>(MHz) | Spread<br>% | Overclock<br>% |

| 0            | 0          | 0          | 0          | 0          | Hi-Z           | Hi-Z         | None        |                |

| 0            | 0          | 0          | 0          | 1          | X / 2          | X / 3        | None        |                |

| 0            | 0          | 0          | 1          | 0          | 230.00         | 76.67        | None        | 15%            |

| 0            | 0          | 0          | 1          | 1          | 240.00         | 80.00        | None        | 20%            |

| 0            | 0          | 1          | 0          | 0          | 100.00         | 66.67        | None        |                |

| 0            | 0          | 1          | 0          | 1          | 133.33         | 66.67        | None        | 0%             |

| 0            | 0          | 1          | 1          | 0          | 166.67         | 66.67        | None        | 0%             |

| 0            | 0          | 1          | 1          | 1          | 200.00         | 66.67        | None        |                |

| 0            | 1          | 0          | 0          | 0          | 250.00         | 83.33        | None        | 25%            |

| 0            | 1          | 0          | 0          | 1          | 260.00         | 86.67        | None        | 30%            |

| 0            | 1          | 0          | 1          | 0          | 270.00         | 90.00        | None        | 35%            |

| 0            | 1          | 0          | 1          | 1          | 280.00         | 93.33        | None        | 40%            |

| 0            | 1          | 1          | 0          | 0          | 102.00         | 68.00        | None        |                |

| 0            | 1          | 1          | 0          | 1          | 136.00         | 68.00        | None        | 2%             |

| 0            | 1          | 1          | 1          | 0          | 170.00         | 68.00        | None        | 2%             |

| 0            | 1          | 1          | 1          | 1          | 204.00         | 68.00        | None        |                |

| 1            | 0          | 0          | 0          | 0          | 210.00         | 70.00        | -0.5%       | 5%             |

| 1            | 0          | 0          | 0          | 1          | 220.00         | 73.33        | -0.5%       | 10%            |

| 1            | 0          | 0          | 1          | 0          | 230.00         | 76.67        | -0.5%       | 15%            |

| 1            | 0          | 0          | 1          | 1          | 240.00         | 80.00        | -0.5%       | 20%            |

| 1            | 0          | 1          | 0          | 0          | 100.00         | 66.67        | -0.5%       |                |

| 1            | 0          | 1          | 0          | 1          | 133.33         | 66.67        | -0.5%       | 0%             |

| 1            | 0          | 1          | 1          | 0          | 166.67         | 66.67        | -0.5%       | 0%             |

| 1            | 0          | 1          | 1          | 1          | 200.00         | 66.67        | -0.5%       |                |

| 1            | 1          | 0          | 0          | 0          | 250.00         | 83.33        | -0.5%       | 25%            |

| 1            | 1          | 0          | 0          | 1          | 260.00         | 86.67        | -0.5%       | 30%            |

| 1            | 1          | 0          | 1          | 0          | 270.00         | 90.00        | -0.5%       | 35%            |

| 1            | 1          | 0          | 1          | 1          | 280.00         | 93.33        | -0.5%       | 40%            |

| 1            | 1          | 1          | 0          | 0          | 102.00         | 68.00        | -0.5%       |                |

| 1            | 1          | 1          | 0          | 1          | 136.00         | 68.00        | -0.5%       | <b>0</b> 0/    |

| 1            | 1          | 1          | 1          | 0          | 170.00         | 68.00        | -0.5%       | 2%             |

| 1            | 1          | 1          | 1          | 1          | 204.00         | 68.00        | -0.5%       |                |

Table2: SRC Frequency Selection Table

| Byte 0 |      | Byt  | te 5 |      |          |        | SRC            |

|--------|------|------|------|------|----------|--------|----------------|

| Bit 5  | Bit3 | Bit2 | Bit1 | Bit0 | SRC(7:0) | Spread | OverClock      |

| SRC    | SRC  | SRC  | SRC  | SRC  | (MHz)    | %      | OverClock<br>% |

| SS_EN  | FS3  | FS2  | FS1  | FS0  |          |        | 70             |

| 0      | 0    | 0    | 0    | 0    | 100.00   | 0      | 0%             |

| 0      | 0    | 0    | 0    | 1    | 101.00   | 0      | 1%             |

| 0      | 0    | 0    | 1    | 0    | 102.00   | 0      | 2%             |

| 0      | 0    | 0    | 1    | 1    | 103.00   | 0      | 3%             |

| 0      | 0    | 1    | 0    | 0    | 104.00   | 0      | 4%             |

| 0      | 0    | 1    | 0    | 1    | 105.00   | 0      | 5%             |

| 0      | 0    | 1    | 1    | 0    | 106.00   | 0      | 6%             |

| 0      | 0    | 1    | 1    | 1    | 107.00   | 0      | 7%             |

| 0      | 1    | 0    | 0    | 0    | 100.00   | 0      | 0%             |

| 0      | 1    | 0    | 0    | 1    | 101.00   | 0      | 1%             |

| 0      | 1    | 0    | 1    | 0    | 102.00   | 0      | 2%             |

| 0      | 1    | 0    | 1    | 1    | 103.00   | 0      | 3%             |

| 0      | 1    | 1    | 0    | 0    | 104.00   | 0      | 4%             |

| 0      | 1    | 1    | 0    | 1    | 105.00   | 0      | 5%             |

| 0      | 1    | 1    | 1    | 0    | 106.00   | 0      | 6%             |

| 0      | 1    | 1    | 1    | 1    | 107.00   | 0      | 7%             |

| 1      | 0    | 0    | 0    | 0    | 100.00   | -0.25% | 0%             |

| 1      | 0    | 0    | 0    | 1    | 101.00   | -0.25% | 1%             |

| 1      | 0    | 0    | 1    | 0    | 102.00   | -0.25% | 2%             |

| 1      | 0    | 0    | 1    | 1    | 103.00   | -0.25% | 3%             |

| 1      | 0    | 1    | 0    | 0    | 104.00   | -0.25% | 4%             |

| 1      | 0    | 1    | 0    | 1    | 105.00   | -0.25% | 5%             |

| 1      | 0    | 1    | 1    | 0    | 106.00   | -0.25% | 6%             |

| 1      | 0    | 1    | 1    | 1    | 107.00   | -0.25% | 7%             |

| 1      | 1    | 0    | 0    | 0    | 100.00   | -0.5%  | 0%             |

| 1      | 1    | 0    | 0    | 1    | 101.00   | -0.5%  | 1%             |

| 1      | 1    | 0    | 1    | 0    | 102.00   | -0.5%  | 2%             |

| 1      | 1    | 0    | 1    | 1    | 103.00   | -0.5%  | 3%             |

| 1      | 1    | 1    | 0    | 0    | 104.00   | -0.5%  | 4%             |

| 1      | 1    | 1    | 0    | 1    | 105.00   | -0.5%  | 5%             |

| 1      | 1    | 1    | 1    | 0    | 106.00   | -0.5%  | 6%             |

| 1      | 1    | 1    | 1    | 1    | 107.00   | -0.5%  | 7%             |

Table3: ATIG Frequency Selection Table

| Byte 0 |      | By   | te 9 |      |           |                   |           |

|--------|------|------|------|------|-----------|-------------------|-----------|

| Bit 6  | Bit4 | Bit3 | Bit1 | Bit0 | ATIG(2:0) | Spread            | ATIG      |

| ATIG   | ATIG | ATIG | ATIG | ATIG | (MHz)     | Spreau<br>%       | OverClock |

| SS_EN  |      | FS2  | FS1  | FS0  | (         | <i>,</i> <b>0</b> | %         |

|        |      |      |      |      |           |                   |           |

| 0      | 0    | 0    | 0    | 0    | 100.00    | 0                 | 0%        |

| 0      | 0    | 0    | 0    | 1    | 105.00    | 0                 | 5%        |

| 0      | 0    | 0    | 1    | 0    | 110.00    | 0                 | 10%       |

| 0      | 0    | 0    | 1    | 1    | 115.00    | 0                 | 15%       |

| 0      | 0    | 1    | 0    | 0    | 120.00    | 0                 | 20%       |

| 0      | 0    | 1    | 0    | 1    | 125.00    | 0                 | 25%       |

| 0      | 0    | 1    | 1    | 0    | 130.00    | 0                 | 30%       |

| 0      | 0    | 1    | 1    | 1    | 135.00    | 0                 | 35%       |

| 0      | 1    | 0    | 0    | 0    | 100.00    | 0                 | 0%        |

| 0      | 1    | 0    | 0    | 1    | 105.00    | 0                 | 5%        |

| 0      | 1    | 0    | 1    | 0    | 110.00    | 0                 | 10%       |

| 0      | 1    | 0    | 1    | 1    | 115.00    | 0                 | 15%       |

| 0      | 1    | 1    | 0    | 0    | 120.00    | 0                 | 20%       |

| 0      | 1    | 1    | 0    | 1    | 125.00    | 0                 | 25%       |

| 0      | 1    | 1    | 1    | 0    | 130.00    | 0                 | 30%       |

| 0      | 1    | 1    | 1    | 1    | 135.00    | 0                 | 35%       |

| 1      | 0    | 0    | 0    | 0    | 100.00    | -0.25%            | 0%        |

| 1      | 0    | 0    | 0    | 1    | 105.00    | -0.25%            | 5%        |

| 1      | 0    | 0    | 1    | 0    | 110.00    | -0.25%            | 10%       |

| 1      | 0    | 0    | 1    | 1    | 115.00    | -0.25%            | 15%       |

| 1      | 0    | 1    | 0    | 0    | 120.00    | -0.25%            | 20%       |

| 1      | 0    | 1    | 0    | 1    | 125.00    | -0.25%            | 25%       |

| 1      | 0    | 1    | 1    | 0    | 130.00    | -0.25%            | 30%       |

| 1      | 0    | 1    | 1    | 1    | 135.00    | -0.25%            | 35%       |

| 1      | 1    | 0    | 0    | 0    | 100.00    | -0.5%             | 0%        |

| 1      | 1    | 0    | 0    | 1    | 105.00    | -0.5%             | 5%        |

| 1      | 1    | 0    | 1    | 0    | 110.00    | -0.5%             | 10%       |

| 1      | 1    | 0    | 1    | 1    | 115.00    | -0.5%             | 15%       |

| 1      | 1    | 1    | 0    | 0    | 120.00    | -0.5%             | 20%       |

| 1      | 1    | 1    | 0    | 1    | 125.00    | -0.5%             | 25%       |

| 1      | 1    | 1    | 1    | 0    | 130.00    | -0.5%             | 30%       |

| 1      | 1    | 1    | 1    | 1    | 135.00    | -0.5%             | 35%       |

#### Table 4: CPU Divider Ratios

| B19b(7:4) |     |         |     | D       | ivider (3:2) |         |     |         |     |

|-----------|-----|---------|-----|---------|--------------|---------|-----|---------|-----|

|           | Bit | 00      |     | 01      |              | 10      |     | 11      | MSB |

| (1:0)     | 00  | 0000    | 2   | 0100    | 4            | 1000    | 8   | 1100    | 16  |

|           | 01  | 0001    | 3   | 0101    | 6            | 1001    | 12  | 1101    | 24  |

| Divider   | 10  | 0010    | 5   | 0110    | 10           | 1010    | 20  | 1110    | 40  |

| Div       | 11  | 0011    | 15  | 0111    | 30           | 1011    | 60  | 1111    | 120 |

|           | LSB | Address | Div | Address |              | Address | Div | Address | Div |

#### **Table 5: HTT Divider Ratios**

| B20b(3:0) |     |         |     | D       | vivider (3:2) |         |     |         |     |

|-----------|-----|---------|-----|---------|---------------|---------|-----|---------|-----|

|           | Bit | 00      |     | 01      |               | 10      |     | 11      | MSB |

| (1:0)     | 00  | 0000    | 4   | 0100    | 8             | 1000    | 16  | 1100    | 32  |

|           | 01  | 0001    | 3   | 0101    | 6             | 1001    | 12  | 1101    | 24  |

| Divider   | 10  | 0010    | 5   | 0110    | 10            | 1010    | 20  | 1110    | 40  |

| Div       | 11  | 0011    | 15  | 0111    | 30            | 1011    | 60  | 1111    | 120 |

|           | LSB | Address | Div | Address |               | Address | Div | Address | Div |

#### **Table 6: ATIG Divider Ratios**

| B19b(3:0) |     |         |     | D       | ivider (3:2) |         |     |         |     |

|-----------|-----|---------|-----|---------|--------------|---------|-----|---------|-----|

|           | Bit | 00      |     | 01      |              | 10      |     | 11      | MSB |

| (1:0)     | 00  | 0000    | 2   | 0100    | 4            | 1000    | 8   | 1100    | 16  |

|           | 01  | 0001    | 3   | 0101    | 6            | 1001    | 12  | 1101    | 24  |

| Divider   | 10  | 0010    | 5   | 0110    | 10           | 1010    | 20  | 1110    | 40  |

| Div       | 11  | 0011    | 7   | 0111    | 14           | 1011    | 28  | 1111    | 56  |

|           | LSB | Address | Div | Address |              | Address | Div | Address | Div |

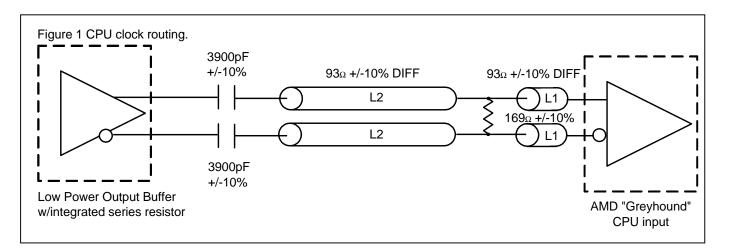

| CPU Clock                                       |                    |      |        |

|-------------------------------------------------|--------------------|------|--------|

| Common Recommendations for Differential Routing | Dimension or Value | Unit | Figure |

| L1 length, Route as coupled 93 ohm trace.       | 0.5 max            | inch | 1      |

| L2 length, Route as coupled 93 ohm trace.       | Contact AMD        | inch | 1      |

IDT<sup>™</sup>/ICS<sup>™</sup> Low Power Clock for ATI RS/RD600 series chipsets for AMD CPUs

1378A-04/07/08

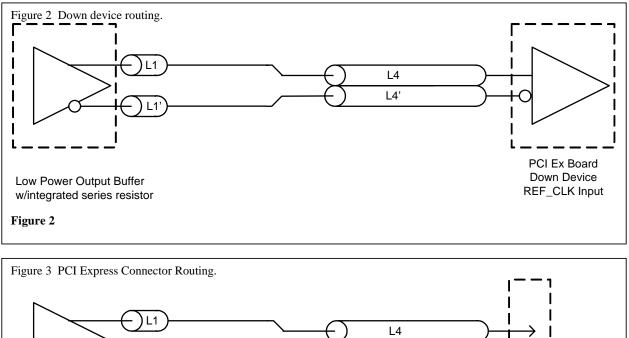

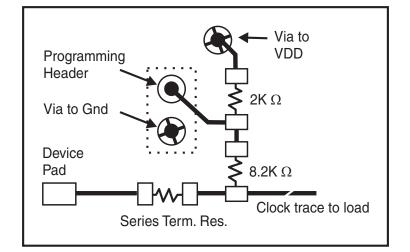

| SRC Reference Clock                             |                    |      |        |  |  |

|-------------------------------------------------|--------------------|------|--------|--|--|

| Common Recommendations for Differential Routing | Dimension or Value | Unit | Figure |  |  |

| L1 length, Route as non-coupled 50 ohm trace.   | 0.5 max            | inch | 2      |  |  |

| L2 length, Route as non-coupled 50 ohm trace.   | N/A                | inch | 2      |  |  |

| L3 length, Route as non-coupled 50 ohm trace.   | N/A                | inch | 2      |  |  |

| Rs                                              | 33                 | ohm  | 2      |  |  |

| Rt                                              | 49.9               | ohm  | 2      |  |  |

| Down Device Differential Routing                                          | Dimension or Value    | Unit   | Figure |

|---------------------------------------------------------------------------|-----------------------|--------|--------|

| L4 length, Route as coupled microstrip 100 ohm differential trace.        | 2 min to 16 max       | inch   | 2      |

| L4 length, Route as coupled stripline 100 ohm differential trace.         | 1.8 min to 14.4 max   | inch 2 |        |

|                                                                           |                       |        |        |

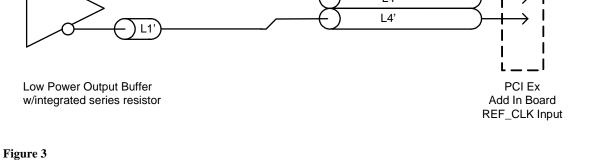

| Differential Routing to PCI Express Connector                             | Dimension or Value    | Unit   | Figure |

| L4 length, Route as coupled <b>microstrip</b> 100 ohm differential trace. | 0.25 to 14 max        | inch   | 3      |

| L4 length, Route as coupled <b>stripline</b> 100 ohm differential trace.  | 0.225 min to 12.6 max | inch   | 3      |

IDT<sup>™</sup>/ICS<sup>™</sup> Low Power Clock for ATI RS/RD600 series chipsets for AMD CPUs

# General SMBus serial interface information for the ICS9LPRS462

# How to Write:

- Controller (host) sends a start bit.

- Controller (host) sends the write address D2 (H)

- ICS clock will *acknowledge*

- Controller (host) sends the begining byte location = N

- ICS clock will *acknowledge*

- Controller (host) sends the data byte count = X

- ICS clock will *acknowledge*

- Controller (host) starts sending Byte N through Byte N + X -1

- ICS clock will acknowledge each byte one at a time

- Controller (host) sends a Stop bit

# How to Read:

- Controller (host) will send start bit.

- Controller (host) sends the write address D2 (H)

- ICS clock will acknowledge

- Controller (host) sends the begining byte location = N

- ICS clock will acknowledge

- Controller (host) will send a separate start bit.

- Controller (host) sends the read address D3 (H)

- ICS clock will acknowledge

- ICS clock will send the data byte count = X

- ICS clock sends Byte N + X -1

- ICS clock sends Byte 0 through byte X (if X<sub>(H)</sub> was written to byte 8).

- Controller (host) will need to acknowledge each byte

- Controllor (host) will send a not acknowledge bit

- Controller (host) will send a stop bit

| In    | dex Block W                 | /rit     | e Operation          |

|-------|-----------------------------|----------|----------------------|

| Сог   | ntroller (Host)             |          | ICS (Slave/Receiver) |

| Т     | starT bit                   |          |                      |

| Slav  | e Address D2 <sub>(H)</sub> |          |                      |

| WR    | WRite                       |          |                      |

|       |                             |          | ACK                  |

| Beg   | inning Byte = N             |          |                      |

|       |                             | ACK      |                      |

| Data  | Byte Count = X              |          |                      |

|       |                             |          | ACK                  |

| Begir | nning Byte N                |          |                      |

|       |                             |          | ACK                  |

|       | 0                           | fe       |                      |

|       | 0                           | X Byte   | 0                    |

|       | 0                           | $\times$ | 0                    |

|       |                             |          | 0                    |

| Byte  | e N + X - 1                 |          |                      |

|       |                             |          | ACK                  |

| Р     | stoP bit                    |          |                      |

| In    | dex Block Rea               |                     |                    |  |  |

|-------|-----------------------------|---------------------|--------------------|--|--|

| Cor   | troller (Host)              | IC                  | S (Slave/Receiver) |  |  |

| Т     | starT bit                   |                     |                    |  |  |

| Slave | e Address D2 <sub>(H)</sub> |                     |                    |  |  |

| WR    | WRite                       |                     |                    |  |  |

|       |                             |                     | ACK                |  |  |

| Begi  | nning Byte = N              |                     |                    |  |  |

|       |                             |                     | ACK                |  |  |

| RT    | Repeat starT                |                     |                    |  |  |

| Slave | e Address D3 <sub>(H)</sub> |                     |                    |  |  |

| RD    | ReaD                        |                     |                    |  |  |

|       |                             |                     | ACK                |  |  |

|       |                             |                     |                    |  |  |

|       |                             | Data Byte Count = X |                    |  |  |

|       | ACK                         |                     |                    |  |  |

|       |                             |                     | Beginning Byte N   |  |  |

|       | ACK                         |                     |                    |  |  |

|       |                             | X Byte              | 0                  |  |  |

|       | 0                           | B                   | 0                  |  |  |

|       | 0                           | $\times$            | 0                  |  |  |

| 0     |                             |                     |                    |  |  |

|       |                             |                     | Byte N + X - 1     |  |  |

| N     | Not acknowledge             |                     |                    |  |  |

| Р     | stoP bit                    |                     |                    |  |  |

#### SMBus Table: Spread Spectrum Enable and CPU Frequency Select Register

| Byte 0 | Pin # | Name       | Control Function                           | Туре | 0                                | 1       | PWD   |

|--------|-------|------------|--------------------------------------------|------|----------------------------------|---------|-------|

| Bit 7  | -     | FS Source  | Latched Input or SMBus<br>Frequency Select | RW   | Latched<br>Inputs                | SMBus   | 0     |

| Bit 6  | -     | ATIG SS_EN | ATIG Spread Spectrum Enable                | RW   | Disable Enable                   |         | 0     |

| Bit 5  | -     | SRC SS_EN  | SRC Spread Spectrum Enable                 | RW   | Disable                          | Enable  | 0     |

| Bit 4  | -     | CPU SS_EN  | CPU Spread Spectrum Enable                 | RW   | Disable                          | Enable  | 0     |

| Bit 3  | -     | CPU FS3    | CPU Freq Select Bit 3                      | RW   | Soo T                            | able 1: | 0     |

| Bit 2  | -     | CPU FS2    | CPU Freq Select Bit 2                      | RW   |                                  |         | Latch |

| Bit 1  | -     | CPU FS1    | CPU Freq Select Bit 1                      | RW   | CPU Frequency Selection<br>Table |         | Latch |

| Bit 0  | -     | CPU FS0    | CPU Freq Select Bit 0                      | RW   |                                  | 510     | Latch |

Note: Each Spread Spectrum Enable bit is independent from the other.

Bit(6:4) must all set to "1" in order to enable spread for CPU, SRC and ATIG clocks.

#### SMBus Table: Output Control Register

| Byte 1 | Pin # | Name    | Control Function      | Туре | 0       | 1      | PWD |

|--------|-------|---------|-----------------------|------|---------|--------|-----|

| Bit 7  | 7     | 48MHz_1 | 48MHz_1 Output Enable | RW   | Disable | Enable | 1   |

| Bit 6  | 6     | 48MHz_0 | 48MHz_0 Output Enable | RW   | Disable | Enable | 1   |

| Bit 5  | 54    | REF2    | REF2 Output Enable    | RW   | Disable | Enable | 1   |

| Bit 4  | 55    | REF1    | REF1 Output Enable    | RW   | Disable | Enable | 1   |

| Bit 3  | 56    | REF0    | REF0 Output Enable    | RW   | Disable | Enable | 1   |

| Bit 2  | 51    | HTTCLK0 | HTTCLK0 Output Enable | RW   | Disable | Enable | 1   |

| Bit 1  | 44,43 | CPUCLK1 | CPUCLK1 Output Enable | RW   | Disable | Enable | 1   |

| Bit 0  | 48,47 | CPUCLK0 | CPUCLK0 Output Enable | RW   | Disable | Enable | 1   |

#### SMBus Table: ATIGCLK and CLKREQB# Output Control Register

| Byte 2 | Pin # | Name     | Control Function       | Туре | 0                   | 1        | PWD |

|--------|-------|----------|------------------------|------|---------------------|----------|-----|

| Bit 7  |       |          | Reserved               |      |                     |          | 0   |

| Bit 6  |       |          | Reserved               |      |                     |          | 0   |

| Bit 5  | 31,30 | ATIGCLK1 | ATIGCLK1 Output Enable | RW   | Disable             | Enable   | 1   |

| Bit 4  | 35,34 | ATIGCLK0 | ATIGCLK0 Output Enable | RW   | Disable             | Enable   | 1   |

| Bit 3  | 20,21 | REQBSRC2 | CLKREQB# Controls SRC2 | RW   | Does not<br>control | Controls | 0   |

| Bit 2  |       |          | Reserved               |      |                     |          | 0   |

| Bit 1  | 24,25 | REQBSRC1 | CLKREQB# Controls SRC1 | RW   | Does not<br>control | Controls | 0   |

| Bit 0  |       |          | Reserved               |      |                     |          | 0   |

#### SMBus Table: SRCCLK Output Control Register

| Byte 3 | Pin # | Name     | Control Function                                                    | Туре | 0       | 1      | PWD |

|--------|-------|----------|---------------------------------------------------------------------|------|---------|--------|-----|

| Bit 7  | 12,13 | SRCCLK5  |                                                                     | RW   | Disable | Enable | 1   |

| Bit 6  | 16,17 | SRCCLK4  |                                                                     | RW   | Disable | Enable | 1   |

| Bit 5  | 18,19 | SRCCLK3  | Maatar Output control Enchlos                                       | RW   | Disable | Enable | 1   |

| Bit 4  | 20,21 | SRCCLK2  | Master Output control. Enables<br>or disables output, regardless of | RW   | Disable | Enable | 1   |

| Bit 3  |       | Reserved | CLKREQ# inputs.                                                     | -    | -       | -      | 1   |

| Bit 2  | 24,25 | SRCCLK1  |                                                                     | RW   | Disable | Enable | 1   |

| Bit 1  |       | Reserved |                                                                     | -    | -       | -      | 1   |

| Bit 0  | 39,38 | SRCCLK0  |                                                                     | RW   | Disable | Enable | 1   |

| Byte 4 | Pin # | Name      | Control Function        | Туре | 0                   | 1        | PWD |

|--------|-------|-----------|-------------------------|------|---------------------|----------|-----|

| Bit 7  | 12,13 | REQASRC5  | CLKREQA# Controls SRC5  | RW   | Does not<br>control | Controls | 0   |

| Bit 6  | 16,17 | REQASRC4  | CLKREQA# Controls SRC4  | RW   | Does not<br>control | Controls | 0   |

| Bit 5  | 18,19 | REQASRC3  | CLKREQA# Controls SRC3  | RW   | Does not<br>control | Controls | 0   |

| Bit 4  |       |           | Reserved                |      |                     |          | 0   |

| Bit 3  |       |           | Reserved                |      |                     |          | 0   |

| Bit 2  | 31,30 | REQCATIG1 | CLKREQC# Controls ATIG1 | RW   | Does not<br>control | Controls | 0   |

| Bit 1  | 35,34 | REQCATIG0 | CLKREQC# Controls ATIG0 | RW   | Does not<br>control | Controls | 0   |

| Bit 0  | 39,38 | REQCSRC0  | CLKREQC# Controls SRC0  | RW   | Does not<br>control | Controls | 0   |

#### SMBus Table: CLKREQB# and CLKREQC# Output Control Register

#### SMBus Table: CPU Stop Control and SRC Frequency Select Register

| Byte 5 | Pin # | Name     | Control Function                                    | Туре | 0                                                | 1              | PWD |

|--------|-------|----------|-----------------------------------------------------|------|--------------------------------------------------|----------------|-----|

| Bit 7  |       | IO_VOUT2 | IO Output Voltage Select (Most<br>Significant Bit)  | RW   | See Table 8: \                                   | / IO Solaction | 1   |

| Bit 6  |       | IO_VOUT1 | IO Output Voltage Select                            | RW   | (Default                                         | _              | 0   |

| Bit 5  |       | IO_VOUT0 | IO Output Voltage Select (Least<br>Significant Bit) | RW   | (Delauli                                         | 1              |     |

| Bit 4  |       |          | Reserved                                            |      |                                                  |                | 0   |

| Bit 3  | -     | SRC FS3  | SRC Freq Select Bit 3                               | RW   | Coo T                                            | abla O         | 0   |

| Bit 2  | -     | SRC FS2  | SRC Freq Select Bit 2                               | RW   | See Table 2:<br>SRC Frequency Selection<br>Table |                | 0   |

| Bit 1  | -     | SRC FS1  | SRC Freq Select Bit 1                               | RW   |                                                  |                | 0   |

| Bit 0  | -     | SRC FS0  | SRC Freq Select Bit 0                               | RW   |                                                  |                | 0   |

#### SMBus Table: Device ID Register

| Byte 6 | Pin # | Name             | Control Function | Туре | 0 | 1 | PWD |

|--------|-------|------------------|------------------|------|---|---|-----|

| Bit 7  | -     | Device ID7 (MSB) |                  | R    | - | - | 0   |

| Bit 6  | -     | Device ID6       |                  | R    | - | - | 1   |

| Bit 5  | -     | Device ID5       |                  | R    | - | - | 1   |

| Bit 4  | -     | Device ID4       | DEVICE ID        | R    | - | - | 0   |

| Bit 3  | -     | Device ID3       | DEVICE ID        | R    | - | - | 0   |

| Bit 2  | -     | Device ID2       |                  | R    | - | - | 1   |

| Bit 1  | -     | Device ID1       |                  | R    | - | - | 0   |

| Bit 0  | -     | Device ID0 (LSB) |                  | R    | - | - | 0   |

#### SMBus Table: Revision and Vendor ID Register

| Byte 7 | Pin # | Name | Control Function | Туре | 0 | 1 | PWD |

|--------|-------|------|------------------|------|---|---|-----|

| Bit 7  | -     | RID3 |                  | R    | - | - | 0   |

| Bit 6  | -     | RID2 | REVISION ID      | R    | - | - | 0   |

| Bit 5  | -     | RID1 |                  | R    | - | - | 0   |

| Bit 4  | -     | RID0 | Г                | R    | - | - | 0   |

| Bit 3  | -     | VID3 |                  | R    | - | - | 0   |

| Bit 2  | -     | VID2 | VENDOR ID        | R    | - | - | 0   |

| Bit 1  | -     | VID1 | VENDORID         | R    | - | - | 0   |

| Bit 0  | -     | VID0 |                  | R    | - | - | 1   |

#### SMBus Table: Byte Count Register

| Byte 8 | Pin # | Name | Control Function              | Туре | 0               | 1   | PWD |

|--------|-------|------|-------------------------------|------|-----------------|-----|-----|

| Bit 7  | -     | BC7  |                               | RW   |                 |     | 0   |

| Bit 6  | -     | BC6  |                               | RW   |                 |     | 0   |

| Bit 5  | -     | BC5  |                               | RW   | Writing to this | 0   |     |

| Bit 4  | -     | BC4  | Byte Count Programming b(7:0) | RW   | congiure how r  | 0   |     |

| Bit 3  | -     | BC3  | Byte Count Programming b(7.0) | RW   | be read back    | 1   |     |

| Bit 2  | -     | BC2  |                               | RW   | byt             | es. | 0   |

| Bit 1  | -     | BC1  |                               | RW   |                 |     | 0   |

| Bit 0  | -     | BC0  |                               | RW   |                 |     | 1   |

#### SMBus Table: REF2, 48MHz Output Strength Control and ATIG Frequency Select Register

| Byte 9 | Pin # | Name       | Control Function         | Туре | 0           | 1         | PWD |  |  |

|--------|-------|------------|--------------------------|------|-------------|-----------|-----|--|--|

| Bit 7  | 54    | REF2Str    | REF2 Strength Control    | RW   | 1X          | 2X        | 1   |  |  |

| Bit 6  | 7     | 48MHz_1Str | 48MHz_1 Strength Control | RW   | 1X          | 1         |     |  |  |

| Bit 5  | 6     | 48MHz_0Str | 48MHz_0 Strength Control | RW   | 1X          | 1         |     |  |  |

| Bit 4  |       | Reserved   |                          |      |             |           |     |  |  |

| Bit 3  | -     | ATIG FS3   | ATIG Freq Select Bit 3   | RW   |             |           | 0   |  |  |

| Bit 2  | -     | ATIG FS2   | ATIG Freq Select Bit 2   | RW   | See Tabl    | e 3: ATIG | 0   |  |  |

| Bit 1  | -     | ATIG FS1   | ATIG Freq Select Bit 1   | RW   | Frequency S | 0         |     |  |  |

| Bit 0  | -     | ATIG FS0   | ATIG Freq Select Bit 0   | RW   |             |           | 0   |  |  |

#### SMBus Table: PLLs M/N Programming Enable and REF1, REF0 Output Strength Control Register

| Byte 10 | Pin # | Name                                   | Control Function            | Туре | 0       | 1      | PWD |  |

|---------|-------|----------------------------------------|-----------------------------|------|---------|--------|-----|--|

| Bit 7   | -     | M/N_EN                                 | PLLs M/N Programming Enable | RW   | Disable | Enable | 0   |  |

| Bit 6   | 55    | REF1Str                                | REF1 Strength Control       | RW   | 1X      | 2X     | 1   |  |

| Bit 5   | 56    | REF0Str REF0 Strength Control RW 1X 2X |                             |      |         |        |     |  |

| Bit 4   |       | Reserved                               |                             |      |         |        |     |  |

| Bit 3   |       |                                        | Reserved                    |      |         |        | 0   |  |

| Bit 2   |       |                                        | Reserved                    |      |         |        | 0   |  |

| Bit 1   |       | Reserved                               |                             |      |         |        |     |  |

| Bit 0   |       |                                        | Reserved                    |      |         |        | 0   |  |

#### SMBus Table: CPU PLL VCO Frequency Control Register

| Byte 11 | Pin # | Name    | Control Function           | Туре | 0               | 1               | PWD |

|---------|-------|---------|----------------------------|------|-----------------|-----------------|-----|

| Bit 7   | -     | N Div8  | N Divider Prog bit 8       | RW   | The decimal re  | presentation of | Х   |

| Bit 6   | -     | N Div 9 | N Divider Prog bit 9       | RW   | M and N Divier  |                 |     |

| Bit 5   | -     | M Div5  |                            | RW   | 12 will config  | ure the VCO     | Х   |

| Bit 4   | -     | M Div4  |                            | RW   | frequency. D    | efault at power | Х   |

| Bit 3   | -     | M Div3  | M Divider Programming bits | RW   | up = latch-in c | or Byte 0 Rom   | Х   |

| Bit 2   | -     | M Div2  |                            | RW   |                 | requency =      | Х   |

| Bit 1   | -     | M Div1  |                            | RW   | 14.318 x [N     | · / -           | Х   |

| Bit 0   | -     | M Div0  | 1                          | RW   | [MDiv(          | 5:0)+2]         | Х   |

#### SMBus Table: CPU PLL VCO Frequency Control Register

| Byte 12 | Pin # | Name   | Control Function             | Туре | 0                        | 1               | PWD |

|---------|-------|--------|------------------------------|------|--------------------------|-----------------|-----|