#### CCG9020

Power Control IC Datasheet

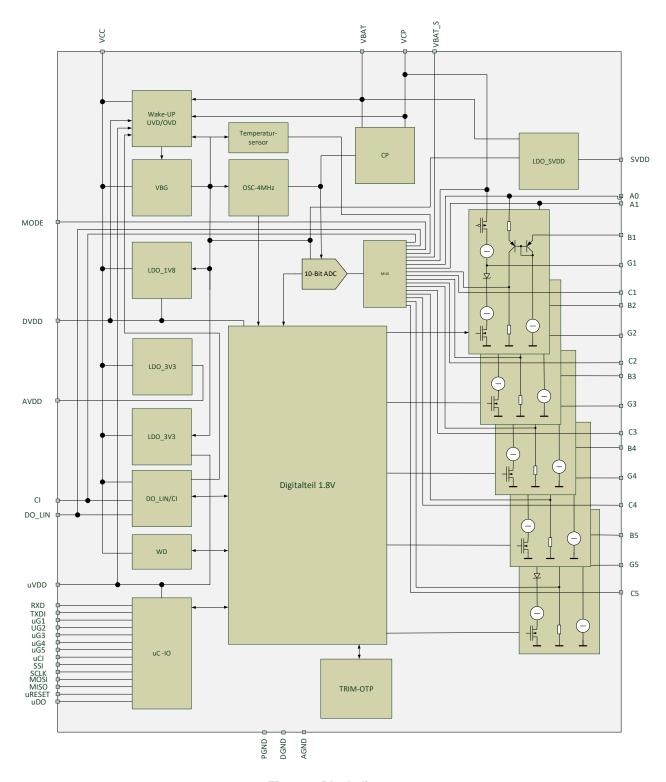

The CCG9020 is a 5-channel driver for external NMOS high-side switches with integrated charge-pump. It is intended for PWM operation controlled by an external uC.

A variety of configuration options can be selected via SPI, for example to optimize EMC performance.

The built-in 10-Bit ADC allows for measurements of channel currents, various interface voltages and the die temperature. An integrated programmable short-circuit protection, over- and under-voltage detection and overtemperature shut-down protect the chip and the load.

The IC is intended for operation in harsh environments including ground-shift, ground-loss, strong supply-transients, polarity reversal and a wiring-harness with significant inductance is supported.

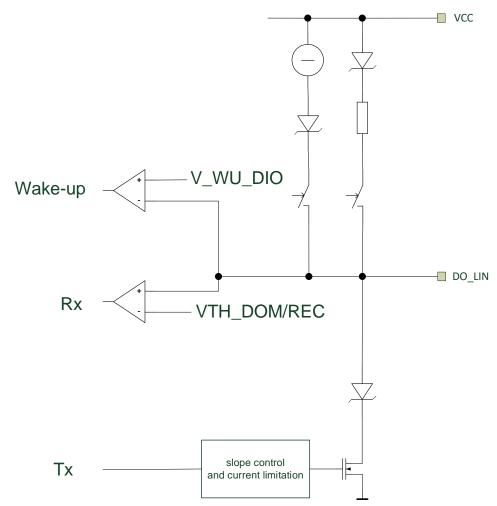

A programmable high-voltage control-input and a high-voltage diagnosis-output or a LIN compatible I/O PHY provide connection to the environment. Low-power sleep mode and different selectable wake-up mechanisms help to reduce the system-level power consumption.

# **Key Features**

- HV BCD process

- 5-channel operation available

- Integrated charge pump

- Short circuit shutdown

- Integrated 10-bit ADC

- Integrated current sensor

- Integrated die temperature sensor with overtemperature protection

- Integrated external uC interface, incl. LDO and Reset

- Suitable for Terminal 87 (T87) and Terminal 30 (T30) systems

- Low standby power

# **Applications**

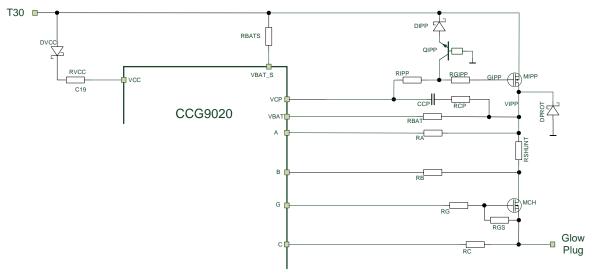

- Engine glow plug controller

- PTC heater controller for HVAC

- Seat heaters

Figure 1. Block diagram

# **Contents**

| Key | / Featu  | ıres     |                                                  | 1  |

|-----|----------|----------|--------------------------------------------------|----|

| Apı | olicatio | ons      |                                                  |    |

| Coı | ntents   |          |                                                  | 3  |

| Fig | ures     |          |                                                  | 4  |

| Tak | oles     |          |                                                  | 4  |

| 1.  | Pino     | ut       |                                                  | 6  |

| 2.  | Char     | acterist | ics                                              | 8  |

|     | 2.1      | Absolut  | te Maximum Ratings                               | 8  |

|     | 2.2      | Recom    | mended Operating Conditions                      | 11 |

|     | 2.3      | Electro  | static Discharge Ratings                         | 12 |

|     | 2.4      | Maximu   | um Power Dissipation and Case Thermal Resistance | 12 |

|     | 2.5      | Electric | cal Characteristics                              | 12 |

|     |          | 2.5.1    | Power Input                                      | 12 |

|     |          | 2.5.2    | Under- and Over-Voltage Thresholds               | 13 |

|     |          | 2.5.3    | Voltage Regulator                                | 15 |

|     |          | 2.5.4    | uC Interface                                     | 15 |

|     |          | 2.5.5    | Internal Logic                                   | 16 |

|     |          | 2.5.6    | Charge Pump                                      | 16 |

|     |          | 2.5.7    | Gate Control                                     | 16 |

|     |          | 2.5.8    | Short Circuit Power Shutdown                     | 18 |

|     |          | 2.5.9    | DIO_BUS                                          | 18 |

|     |          | 2.5.10   | DO                                               | 19 |

|     |          | 2.5.11   | ST                                               | 19 |

|     |          | 2.5.12   | Mode                                             | 20 |

|     |          | 2.5.13   | ADC                                              | 20 |

|     |          | 2.5.14   | Over-Temperature Shutdown                        | 21 |

| 3.  | Func     | tional D | Description                                      | 22 |

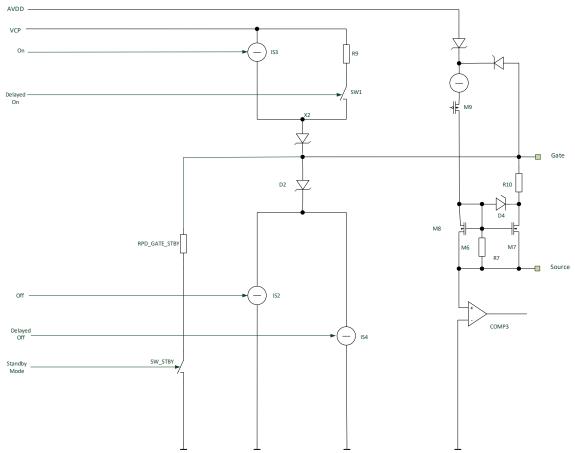

|     | 3.1      | Power    | Supply, Startup and Shutdown                     | 22 |

|     | 3.2      | Voltage  | e and Temperature Monitoring                     | 25 |

|     | 3.3      | Oscillat | tor Watchdog                                     | 25 |

|     | 3.4      | Short C  | Circuit Shutdown                                 | 26 |

|     | 3.5      | Charge   | Pump and Gate Control                            | 26 |

|     | 3.6      | Revers   | e-Polarity Protection                            | 28 |

|     | 3.7      | DIO_BI   | US/DO                                            | 29 |

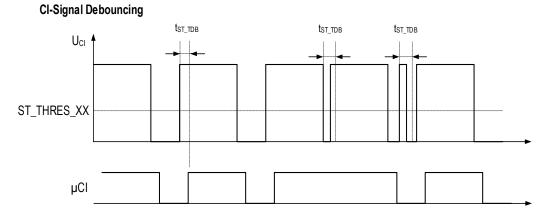

|     | 3.8      | CI Inpu  | ıt                                               | 30 |

|     | 3.9      | ADC      |                                                  | 31 |

|     | 3.10     | JTAG I   | nterface                                         | 34 |

|     | 3.11     | Digital  | Function                                         | 35 |

|     |          | 3.11.1   | uRESET Pin                                       | 35 |

|     |          | 3.11.2   | SPI Interface                                    | 35 |

| 4.  | Regis    | ster Def | initions                                         | 36 |

|     | 4.1      | Registe  | er Map                                           | 36 |

|     |          | 4.1.1    | Version Register                                 |    |

|     |          | 4.1.2    | VAD Register                                     |    |

|     |          |          |                                                  |    |

|      |         | 4.1.3     | State Register                                                                        | 40 |

|------|---------|-----------|---------------------------------------------------------------------------------------|----|

|      |         | 4.1.4     | Config Register                                                                       | 41 |

|      |         | 4.1.5     | Chctrl Register                                                                       | 42 |

|      |         | 4.1.6     | Chconfig Register                                                                     |    |

|      |         | 4.1.7     | STConfig Register                                                                     |    |

|      |         | 4.1.8     | ThShort Register                                                                      |    |

|      |         | 4.1.9     | ChShort Register                                                                      |    |

|      |         | 4.1.10    | IRiseFall Register                                                                    |    |

|      |         | 4.1.11    | TWdog Register                                                                        |    |

|      |         | 4.1.12    | WdogReset Register                                                                    |    |

|      |         |           |                                                                                       |    |

|      |         | 4.1.13    | DIOReg Register                                                                       |    |

| _    |         | 4.1.14    | Chip-ID Registers, Address 15 and Address 16                                          |    |

| 5.   |         | •         | rmation                                                                               |    |

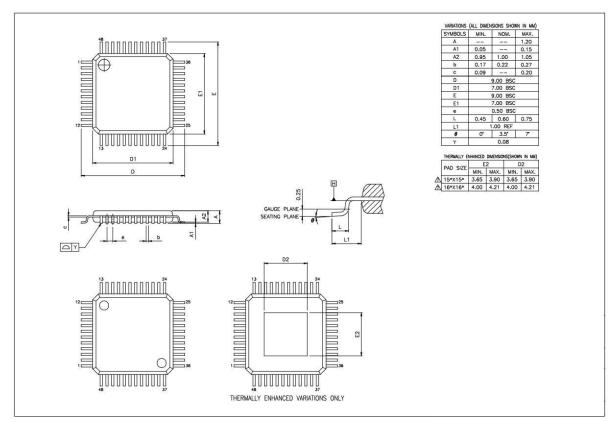

|      | 5.1     | ŭ         | e Outline                                                                             |    |

|      | 5.2     |           | e Sensitivity Level                                                                   |    |

| 6.   | Appl    | ication l | nformation                                                                            | 50 |

| Fi   | gure    | es        |                                                                                       |    |

|      |         |           | gram                                                                                  | 2  |

| _    |         |           | out diagram (Top view)                                                                |    |

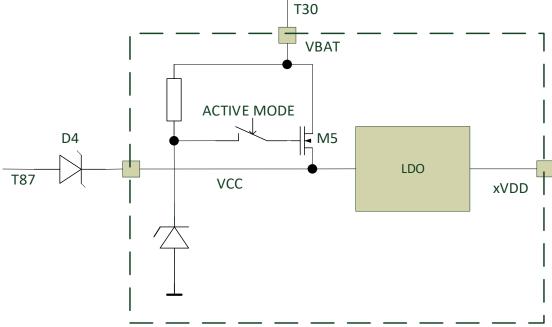

| _    |         |           | pply switch                                                                           |    |

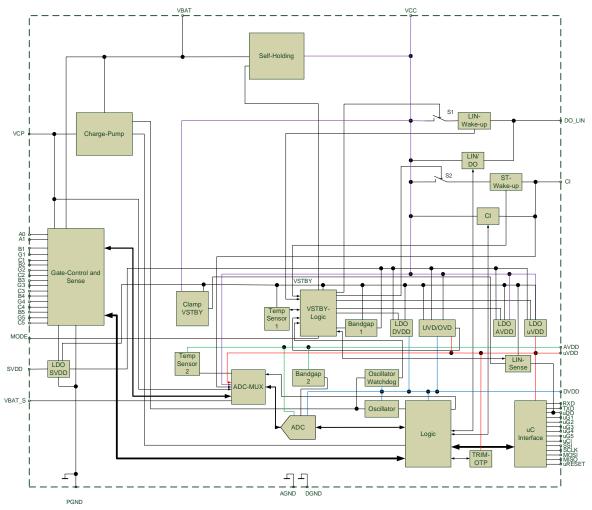

| _    |         |           | pply concept                                                                          |    |

| _    |         | •         | d diagram of gate control                                                             |    |

| _    |         | •         | d diagram of reverse polarity protection in the load path shows glow plug application |    |

| _    |         |           | lebouncing                                                                            |    |

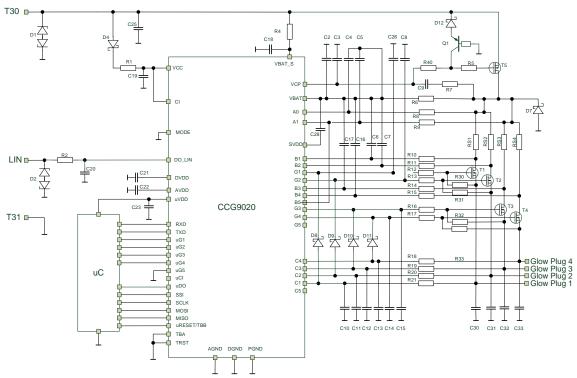

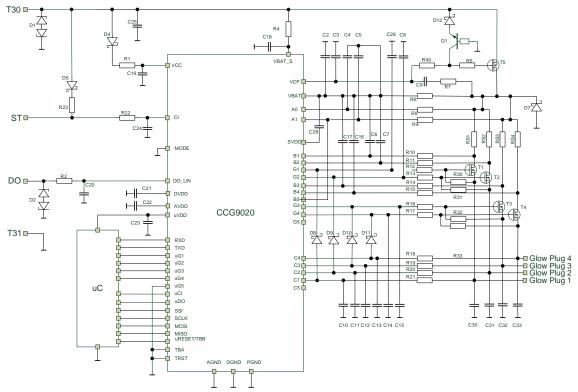

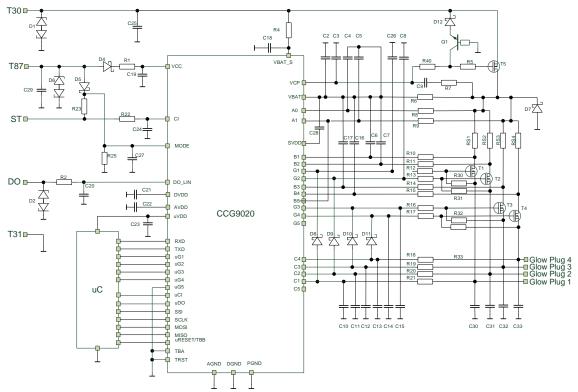

| _    |         | -         | otual schematic                                                                       |    |

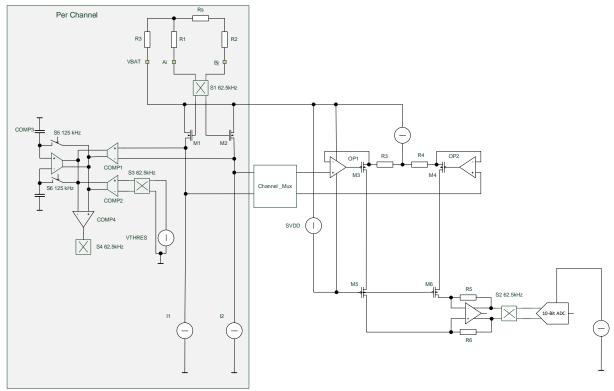

| _    |         |           | ed diagram of channel amplifier and short circuit comparators                         |    |

| _    |         | -         | ng                                                                                    |    |

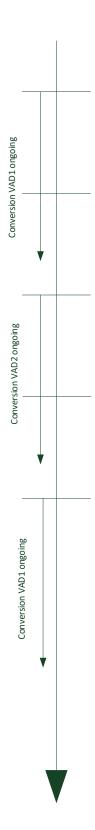

| _    |         |           | e of VAD register use                                                                 |    |

| _    |         | •         | ackage outline drawing                                                                |    |

| _    |         | •         | wiring for a four-channel T30 application with DIO_BUS, glow plug application         |    |

| _    |         |           | wiring for a four-channel T30 application with ST, glow plug application              |    |

| Figu | ıre 16. | Sample    | wiring for a four-channel T87 application, glow plug application                      | 53 |

| Та   | bles    | 5         |                                                                                       |    |

|      |         |           | ption                                                                                 |    |

|      |         |           | efinition                                                                             |    |

|      |         |           | maximum ratings                                                                       |    |

|      |         |           | voltage between pins                                                                  |    |

|      |         |           | ended operating conditions                                                            |    |

|      |         | •         | ure profile                                                                           |    |

|      |         |           | tic discharge ratingssipation                                                         |    |

|      |         |           | ut electrical characteristics                                                         |    |

|      |         |           | nd over-voltage thresholds electrical characteristics                                 |    |

|      |         |           | egulator electrical characteristics                                                   |    |

|      |         |           |                                                                                       | •  |

#### **Power Control IC Datasheet**

|           | uC interface electrical characteristics                       |    |

|-----------|---------------------------------------------------------------|----|

|           | Internal logic electrical characteristics                     |    |

| Table 14. | Charge pump electrical characteristics                        | 16 |

|           | Gate control electrical characteristics                       |    |

|           | Short Circuit power shutdown electrical characteristics       |    |

| Table 17. | DIO_BUS electrical characteristics                            | 18 |

| Table 18. | DO electrical characteristics                                 | 19 |

| Table 19. | ST electrical characteristics                                 | 19 |

| Table 20. | Mode electrical characteristics                               | 20 |

|           | ADC electrical characteristics                                |    |

|           | Over-temperatur shutdown electrical characteristics           |    |

|           | Startup                                                       |    |

| Table 24. | FSR of AD channels (see section 3.9)                          | 33 |

| Table 25. | Example 1 of calculated measured temperature                  | 34 |

|           | Example 2 of calculated measured temperature                  |    |

|           | Register map                                                  |    |

|           | SPI data format                                               |    |

| Table 29. | Status data format                                            | 37 |

| Table 30. | Version register                                              | 37 |

| Table 31. | VAD write access data format                                  | 37 |

|           | VAD read access data format                                   |    |

| Table 33. | ADC channels                                                  | 38 |

|           | State register                                                |    |

| Table 35. | Config register                                               | 41 |

| Table 36. | Programmable debounce times for voltage monitoring            | 41 |

| Table 37. | Programming the validity window for the software watchdog     | 41 |

| Table 38. | Chctrl register                                               | 42 |

| Table 39. | Chconfig register                                             | 42 |

|           | Typcial oscillator frequency                                  |    |

| Table 41. | STconfig register                                             | 42 |

| Table 42. | Thresholds at ST (during operation)                           | 43 |

| Table 43. | Debounce time coding at ST (during operation)                 | 43 |

| Table 44. | ThShort register                                              | 43 |

| Table 45. | Short circuit threshold coding                                | 43 |

| Table 46. | Short circuit detector debounce times                         | 44 |

| Table 47. | VGS short circuit dead time on gate shutdown                  | 44 |

| Table 48. | ChShort register                                              | 45 |

| Table 49. | IRiseFall register                                            | 45 |

| Table 50. | Programming the gate control currents                         | 45 |

| Table 51. | TWdog register                                                | 46 |

| Table 52. | Software watchdog elapsed time coding                         | 46 |

| Table 53. | WdogReset register                                            | 46 |

|           | DIOReg register                                               |    |

| Table 55. | DIO_BUS debounce time coding                                  | 47 |

| Table 56. | MSL classification                                            | 49 |

| Table 57. | Sample sizing for a four-channel T30 application with DIO_BUS | 50 |

| Table 58. | Sample sizing for a four-channel T30 application with ST      | 52 |

| Table 59. | Sample sizing for a four-channel T87 application              | 53 |

# 1. Pinout

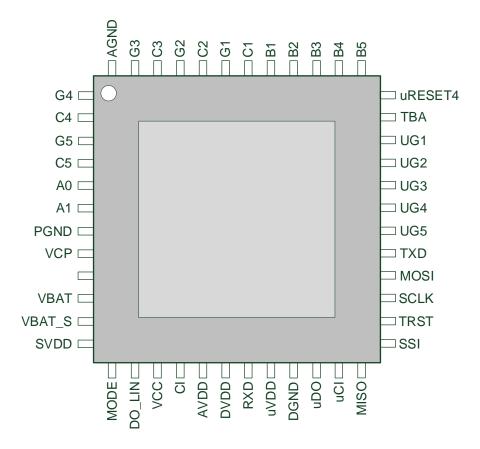

Figure 2. TQFP pinout diagram (Top view)

Table 1. Pin description

| Pin# | Pin name | Type (Table 2) | Description                                     |

|------|----------|----------------|-------------------------------------------------|

| 1    | G4       | 0              | Channel FET 4 gate control                      |

| 2    | C4       | I              | Channel FET 4 source                            |

| 3    | G5       | 0              | Channel FET 5 gate driver                       |

| 4    | C5       | I              | Channel FET 5 source                            |

| 5    | A0       | 1              | Channel 1/2 shunt high side                     |

| 6    | A1       | I              | Channel 3/4/5 shunt high side                   |

| 7    | PGND     | GND            | Charge pump and gate control ground             |

| 8    | VCP      | I/O            | Cp bulk capacitor connection                    |

| 9    | -        | -              | Unassigned                                      |

|      |          |                | Wire to ground in application                   |

| 10   | VBAT     | PWR            | Power supply (T30)                              |

| 11   | VBAT_S   | I              | Sense input for T30 monitoring                  |

| 12   | SVDD     | 0              | LDO output for powering channel amplifiers      |

| 13   | MODE     | I              | T87/T30 configuration pin and T87 sense pin     |

| 14   | DO_LIN   | I/O            | DIO_Bus/diagnostic output                       |

| 15   | VCC      | PWR            | Power supply (T87)                              |

| 16   | CI       | 1              | PWM signal input                                |

| 17   | AVDD     | 0              | LDO output for powering internal analog section |

| 19 R) 20 u\ 21 D( 22 uE 23 uC 24 M) 25 SS | IISO                    | O<br>O<br>O<br>GND<br>I | LDO output for powering internal digital section DIO_BUS data output to uC LDO output for powering external uC Digital section ground Diagnostic data output from uC |

|-------------------------------------------|-------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20 u\ 21 D0 22 uE 23 uC 24 M 25 SS        | GND<br>DO<br>CI         | O<br>GND<br>I<br>O      | DIO_BUS data output to uC  LDO output for powering external uC  Digital section ground  Diagnostic data output from uC                                               |

| 20 u\ 21 D0 22 uE 23 uC 24 Mi 25 SS       | GND<br>DO<br>CI         | O<br>GND<br>I<br>O      | LDO output for powering external uC  Digital section ground  Diagnostic data output from uC                                                                          |

| 21 D0<br>22 uE<br>23 uC<br>24 M<br>25 SS  | GND<br>DO<br>CI<br>IISO | GND<br>I<br>O           | powering external uC  Digital section ground  Diagnostic data output from uC                                                                                         |

| 22 uE<br>23 uC<br>24 M<br>25 SS           | DO<br>CI<br>IISO        | 0                       | Digital section ground Diagnostic data output from uC                                                                                                                |

| 22 uE<br>23 uC<br>24 M<br>25 SS           | DO<br>CI<br>IISO        | 0                       | Diagnostic data output from uC                                                                                                                                       |

| 23 uC<br>24 MI<br>25 SS                   | CI                      | 0                       | <u> </u>                                                                                                                                                             |

| 24 M<br>25 SS                             | IISO                    | _                       |                                                                                                                                                                      |

| 25 SS                                     |                         | _                       | Level-converted CI signal                                                                                                                                            |

|                                           | SI                      | 0                       | SPI data output                                                                                                                                                      |

| 26 TF                                     |                         | I                       | SPI chip select                                                                                                                                                      |

| 20   11                                   | RST                     | I                       | Test reset pin (JTAG)                                                                                                                                                |

|                                           |                         |                         | Wire to ground in application!                                                                                                                                       |

| 27 S0                                     | CLK                     | I                       | SPI clock input                                                                                                                                                      |

| 28 M                                      | IOSI                    | I                       | SPI data input                                                                                                                                                       |

| 29 T                                      | XD                      | I                       | DIO_BUS data input from uC                                                                                                                                           |

| 30 uC                                     | G5                      | I                       | Channel 5 control signal input                                                                                                                                       |

| 31 uC                                     | G4                      | I                       | Channel 4 control signal input                                                                                                                                       |

| 32 uC                                     | G3                      | I                       | Channel 3 control signal input                                                                                                                                       |

| 33 uC                                     | G2                      | I                       | Channel 2 control signal input                                                                                                                                       |

| 34 uC                                     | G1                      | I                       | Channel 1 control signal input                                                                                                                                       |

| 35 TE                                     | BA                      | I/O                     | Test Bus A                                                                                                                                                           |

|                                           |                         |                         | Wire to ground in application!                                                                                                                                       |

| 36 uF                                     | RESET                   | 0                       | uC reset (active-low, open-drain)                                                                                                                                    |

| 37 B5                                     | 5                       | I                       | Channel 5 shunt low side                                                                                                                                             |

|                                           |                         |                         | (Channel FET 5 drain)                                                                                                                                                |

| 38 B4                                     | 4                       | I                       | Channel 4 shunt low side                                                                                                                                             |

|                                           |                         |                         | (Channel FET 4 drain)                                                                                                                                                |

| 39 B3                                     | 3                       | ı                       | Channel 3 shunt low side                                                                                                                                             |

| 40 B2                                     | 2                       | 1                       | (Channel FET 3 drain) Channel 2 shunt low side                                                                                                                       |

| 40 B2                                     | 2                       | I                       | (Channel FET 2 drain)                                                                                                                                                |

| 41 B1                                     | 1                       | 1                       | Channel 1 shunt low side                                                                                                                                             |

|                                           | '                       |                         | (Channel FET 1 drain)                                                                                                                                                |

| 42 C                                      | 1                       | I                       | Channel FET 1 source                                                                                                                                                 |

| 43 G                                      |                         | 0                       | Channel FET 1 gate control                                                                                                                                           |

| 44 C2                                     |                         | I                       | Channel FET 2 source                                                                                                                                                 |

| 45 G:                                     |                         | 0                       | Channel FET 2 gate control                                                                                                                                           |

| 46 C3                                     |                         | ı                       | Channel FET 3 source                                                                                                                                                 |

| 47 G:                                     |                         | 0                       | Channel FET 3 gate control                                                                                                                                           |

|                                           | GND                     | GND                     | Analog section ground                                                                                                                                                |

| Exposed                                   |                         |                         | Connected to AGND.                                                                                                                                                   |

| pad                                       |                         |                         | Wire to ground in application                                                                                                                                        |

### Table 2. Pin type definition

| Pin Type | Description  | Pin Type | Description   |

|----------|--------------|----------|---------------|

| 1        | Input        | 0        | Output        |

| I/O      | Input/Output | AO       | Analog output |

| PWR      | Power        | GND      | Ground        |

## 2. Characteristics

## 2.1 Absolute Maximum Ratings

V(AGND) = V(DGND) = V(PGND) = 0 V

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, so functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification are not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

Table 3. Absolute maximum ratings

| Parameter   | Description                               | Conditions             | Min    | Max         | Unit |

|-------------|-------------------------------------------|------------------------|--------|-------------|------|

| VBAT_DC     | VBAT pin voltage                          | Note 2, Note 5         | -0.3   | 30          | V    |

| VBAT_dyn    | VBAT pin dynamic voltage                  | Note 3, Note 5         | -0.7   | 45          | V    |

| IVBAT_dyn   | VBAT pin dynamic injection current        | Note 3                 | -50    | 0           | mA   |

| VCP_DC      | VCP pin voltage                           | Note 2, Note 5         | -0.3   | 40          | V    |

| VCP_dyn     | VCP pin dynamic voltage                   | Note 3                 | -0.7   | 55          | V    |

| IVCP_dyn    | VCP pin dynamic injection current         | Note 3                 | -20    | 0           | mA   |

| Vai_DC      | A0, A1 pin voltage                        |                        | -0.3   | V(VBAT)+2   | V    |

| Vai_dyn     | A0, A1 pin dynamic voltage                | Note 3                 | -0.7   | V(VBAT)+2   | V    |

| IAi_dyn     | A0, A1 pin dynamic injection current      | Note 3                 | -2     | 0           | mA   |

| VBi_DC      | B1, B2, B3, B4, B5 pin voltage            | Note 2                 | -18    | V(VBAT)+2   | V    |

| VBi_dyn     | B1, B2, B3, B4, B5 pin<br>dynamic voltage | Note 3                 | -25    | V(VBAT)+2   | V    |

| VCi_DC      | C1, C2, C3, C4, C5 pin voltage            | Note 2                 | -18    | 30          | V    |

| VCi_dyn     | C1, C2, C3, C4, C5 pin dynamic voltage    | Note 3                 | -25    | 45          | V    |

| VGi_DC      | G1, G2, G3, G4, G5 pin voltage            | Note 2                 | -18    | 40          | V    |

| VGi_dyn     | G1, G2, G3, G4, G5 pin<br>dynamic voltage | Note 3                 | -25    | 55          | V    |

| VBAT_S_DC   | VBAT_S pin voltage                        | Note 2                 | -0.3   | 30          | V    |

| VBAT_S_dyn  | VBAT_S pin dynamic voltage                | Note 3                 | -0.3   | 45          | V    |

| IVBAT_S_DC  | VBAT_S pin injection current              |                        | -125   | 0           | mA   |

| IVBAT_S_dyn | VBAT_S pin dynamic injection current      | Note 3                 | -200   | 0           | mA   |

| VSVDD_DC    | SVDD pin voltage                          |                        | VBAT-5 | V(VBAT+0.3) | V    |

| VCC_DC      | VCC pin voltage                           | Note 2, Note 5, Note 6 | -0.3   | 30          | V    |

| VCC_dyn     | VCC pin dynamic voltage                   | Note 3, Note 5         | -0.3   | 45          | V    |

| VDOLIN_DC   | DO_LIN pin voltage                        |                        | -27    | 40          | V    |

| VCI_DC      | CI pin voltage                            | Note 2                 | -0.3   | 30          | V    |

| VCI_ dyn    | CI pin dynamic voltage                    | Note 3                 | -0.3   | 45          | V    |

| ICI         | CI pin injection current                  | Note 4                 | -5     | 0           | mA   |

| VMODE_DC    | MODE pin voltage                          | Note 2, Note 5         | -0.3   | 30          | V    |

| VMODE_dyn   | MODE pin dynamic voltage                  | Note 3, Note 5         | -0.7   | 45          | V    |

| IMODE_DC    | MODE pin injection current                |                        | -14    | 0           | mA   |

| IMODE_dyn   | MODE pin dynamic injection current        | Note 3                 | -25    | 0           | mA   |

#### **Power Control IC Datasheet**

| Parameter       | Description                                                                              | Conditions | Min  | Max                  | Unit |

|-----------------|------------------------------------------------------------------------------------------|------------|------|----------------------|------|

| VAVDD,<br>VuVDD | AVDD, uVDD pin voltage                                                                   | Note 1     | -0.3 | 5.0                  | V    |

| VDVDD           | DVDD pin voltage                                                                         | Note 1     | -0.3 | 2.0                  | V    |

| VuCIO           | RXD, TXD, uCI, uG1, uG2,<br>uG3, uG4, uG5, SSI, SCLK,<br>MOSI, MISO, TRST pin<br>voltage |            | -0.3 | V(uVDD)+0.3          | V    |

| VuDO            | uDO pin voltage                                                                          |            | -0.3 | 5.5                  | V    |

| VuRESET         | uRESET pin voltage                                                                       |            | -0.3 | VCC+0.3              | V    |

| VTBA            | TBA pins voltage                                                                         |            | -0.3 | 45                   | V    |

| TJ              | Junction temperature                                                                     |            | -40  | 150 170<br>< TProt_s | °C   |

| TI              | Storage temperature                                                                      |            | -40  | 150                  | °C   |

- Note 1 Do not use an external power supply (UVDD can be powered externally to program the external uC provided UVDD does not exceed VCC, does not exceed 5.0 V and the internal LDO is enabled).

- Note 2 DC value

- **Note 3** Dynamic value with pulse shape as per EMC requirements.

- Note 4 Consider parameter PTOT.

- Note 5 External reverse-polarity protection required.

- Note 6 Refers to VSUP\_NON\_OP in ISO/DIS 17987-7

Component reliability refers to operation at the following temperatures.

The values are cumulative and total an overall operating time of 8,000 hours plus 14 years of standby operation at a  $T_J$  < 50 °C.

Table 4. Maximum voltage between pins

|        |    |    |          | DO_ |     |     |    |   |    |    |    |         |     |     |                   |     |     |                   | Ci | Ai | 匨        |

|--------|----|----|----------|-----|-----|-----|----|---|----|----|----|---------|-----|-----|-------------------|-----|-----|-------------------|----|----|----------|

| ESD_H  |    | 0  | 0        |     |     |     |    |   |    |    |    | 0       | 0   | 0   |                   | 0   | 0   |                   | 2  | 2  | 2        |

| ST(CI) |    |    |          |     |     |     |    |   |    |    |    | 0       |     |     |                   |     |     |                   |    | _  |          |

| VCC    |    | na |          |     | 00) | 02  | 00 |   |    | 02 |    | 1)      |     |     |                   |     |     |                   |    |    | -        |

| DO_LIN |    |    | na<br>45 | 20  | 02) | 02  | 02 |   |    | 02 |    | 27      |     |     |                   |     |     |                   |    |    |          |

| DVDD   |    |    | 40       | na  | na  |     |    |   |    |    |    | 0       |     |     |                   |     |     |                   |    |    |          |

| AVDD   |    |    |          |     | IIa | na  |    |   |    |    |    | 0       |     |     |                   |     |     |                   |    |    | <u> </u> |

| UVDD   |    |    |          |     |     | IIa | Na | 0 | 3  | 0  |    | 0       |     |     |                   |     |     |                   |    |    |          |

| μlO    |    |    |          |     |     |     |    |   |    |    |    | 0       |     |     |                   |     |     |                   |    |    |          |

| μDO    |    |    |          |     |     |     |    |   | na |    |    | 0       |     |     |                   |     |     |                   |    |    |          |

| μReset |    |    |          |     |     |     |    |   |    | na |    | 0       |     |     |                   |     |     |                   |    |    |          |

| ТВА    |    |    |          |     |     |     |    |   |    |    | na | 0       |     |     |                   |     |     |                   |    |    |          |

| XGND   | 45 |    |          | 40  | 2   | 5.5 | 6  |   | 6  |    | 45 | 0       |     |     |                   |     |     | 55                |    |    |          |

| MODE   |    |    |          |     |     |     |    |   |    |    |    | 0       | N/A |     |                   |     |     |                   |    |    |          |

| VBAT_S |    |    |          |     |     |     |    |   |    |    |    | 0<br>1) |     | N/A |                   |     |     |                   |    |    |          |

| VCP    |    |    |          |     |     |     |    |   |    |    |    | 0<br>1) |     |     | N/A               | 2   |     |                   |    |    |          |

| VBAT   |    |    |          |     |     |     |    |   |    |    |    | 0<br>1) |     |     | 15                | N/A | 0   |                   |    | 2  | 2        |

| SVDD   |    |    |          |     |     |     |    |   |    |    |    | 5       |     |     |                   | 5   | N/A |                   |    |    |          |

| Gj     |    |    |          |     |     |     |    |   |    |    |    | 25      |     |     | 55?<br>OK<br>PA55 |     |     | 55?<br>OK<br>PA55 | 10 |    |          |

| Cj     |    |    |          |     |     |     |    |   |    |    |    | 25      |     |     | FASS              |     |     | 20                | 10 |    |          |

| -,     |    |    |          |     |     |     |    |   |    |    |    | 0       |     |     |                   |     |     | 20                |    |    |          |

| Aj     |    |    |          |     |     |     |    |   |    |    |    | 1)      |     |     |                   |     | 2   |                   |    |    |          |

| Bj     |    |    |          |     |     |     |    |   |    |    |    | 25      |     |     |                   |     |     |                   |    |    |          |

<sup>1):</sup>Injection currents at negative pin possible

For each combination, the column lists the pin with the positive voltage.

For combinations with no entry, the max. differential voltage is 45 V provided no other adjacent path specifies a lower differential voltage.

$\mu$ IO: uCI, MISO, SSI, TRST, SCLK, MOSI, TXD, RXD, uG5, uG4, uG3, uG2, uG1

The specified values factor in transient processes, particularly in case of fault, and do not apply to continuous operation.

<sup>2):</sup>Injection currents at positive pin possible

### 2.2 Recommended Operating Conditions

V(AGND) = V(DGND) = V(PGND) = 0 V

Table 5. Recommended operating conditions

| Parameter          | Description                                                                                                                 | Conditions     | Min   | Тур | Max | Unit |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------|-------|-----|-----|------|

| VCC_1              | VCC power supply<br>to generate uVDD, operate<br>the SPI interface, the<br>internal digital section and<br>for ADC metering | Note 1, Note 6 | 4.0   |     | 30  | V    |

| VCC_5              | Cold-start VCC power supply                                                                                                 | Note 7         | 4.5   |     | 30  | V    |

| VCC_2              | VCC power supply to operate the DIO_BUS interface                                                                           | Note 5         | 7.0   |     | 18  | V    |

| VCC_3              | VCC power supply to operate the DO interface                                                                                |                | 4.0   |     | 22  | V    |

| VCC_4              | VCC power supply for unrestricted ADC operation                                                                             | Note 6         | 4.5   |     | 30  | V    |

| VBAT_1             | VBAT power supply to generate uVDD (self-holding)                                                                           | Note 1         | 6.0   |     | 26  | V    |

| VBAT_2             | VBAT power supply to drive the FETs                                                                                         | Note 2         | 5.5   |     | 26  | V    |

| VBAT_3             | VBAT power supply                                                                                                           | Note 3         | 6.0   |     | 18  | V    |

| T <sub>J</sub> _op | Junction temperature                                                                                                        | Note 4         | -40   |     | 150 | °C   |

| I_uVDD             | uVDD current drain                                                                                                          |                | -12.5 |     | 0   | mA   |

- **Note 1** uVDD power can be operated as long as at least one of the two conditions (VCC\_1 or VBAT\_1) is met. ADC function is restricted (see section 3.9).

- Note 2 Device functionality is given.

- **Note 3** In this voltage range, the specified values for the electrical parameters are reached.

- Note 4 See Table 6.

- Note 5 Refers to VSUP in ISO/DIS 17987-7

- Note 6 See Note 4 of Table 24

- **Note 7** This supply voltage is required for approx. 10 ms after VCC is powered to enable startup. During this time, the fuse array in particular is read and the reference voltage trimmed.

Component reliability refers to operation at the following temperatures.

The values are cumulative and total an overall operating time of 8,000 hours plus 14 years of standby operation at a  $T_J$  < 50 °C.

Table 6. Temperature profile

| Junction temperature | Operating time (h) |

|----------------------|--------------------|

| -40 °C               | 480                |

| 23 °C                | 1600               |

| 85 °C                | 5200               |

| 135 °C               | 640                |

| 150 °C               | 80                 |

## 2.3 Electrostatic Discharge Ratings

Table 7. Electrostatic discharge ratings

| Parameter            | Description            | Conditions                        | Value | Unit |

|----------------------|------------------------|-----------------------------------|-------|------|

| V <sub>ESD_HBM</sub> | Maximum ESD protection | Human body model (HBM) Note 1     |       |      |

|                      |                        | AVDD pin                          | ±1.5  | kV   |

|                      |                        | Pin combinations with VCP and VGi | ±0.5  | KV   |

|                      |                        | All other pins                    | ±2    |      |

Note 1 According to ANSI/ESDA/JEDEC JS-001-2014

All pins are latchup-proof as per JESD78E.

# 2.4 Maximum Power Dissipation and Case Thermal Resistance

**Table 8. Power dissipation**

| Parameter                   | Description                        | Conditions                    | Min | Тур | Max | Unit |

|-----------------------------|------------------------------------|-------------------------------|-----|-----|-----|------|

| P <sub>tot</sub>            | Max. power dissipation             | 40°C < T <sub>J</sub> < 150°C |     |     | 1   | W    |

| TJ                          | Max. junction temperature          |                               | -40 |     | 150 | °C   |

| R <sub>th</sub> _<br>j_epad | Junction-to-pad thermal resistance |                               |     |     | 10  | K/W  |

#### 2.5 Electrical Characteristics

Unless otherwise specified, the following data applies to the operating conditions in section 2.2.

### 2.5.1 Power Input

Table 9. Power input electrical characteristics

| Parameter     | Description                                         | Conditions              | Min | Тур | Max | Unit |

|---------------|-----------------------------------------------------|-------------------------|-----|-----|-----|------|

|               |                                                     | I(VCC) + I(VBAT),       |     |     |     |      |

| Lon           | Operating power input                               | w/o external load       |     |     | 11  | mA   |

| I_op          |                                                     | V(VCC) < 25 V           |     |     | 11  | mA   |

|               |                                                     | V(VBAT) < 25 V          |     |     |     |      |

|               |                                                     | I(VBAT),                |     |     |     |      |

|               |                                                     | Standby mode            |     |     |     |      |

| L othy 97 120 | _stby_87_120 Standby power input in T87 application | V(VCC) = V(MODE) = 0 V  |     |     | 175 | uA   |

| 1_5109_67_120 |                                                     | V(VBAT) < 27 V          |     |     | 175 | uA   |

|               |                                                     | V(Ci)>-1.5 V            |     |     |     |      |

|               |                                                     | T <sub>J</sub> < 120 °C |     |     |     |      |

|               | Standby power input in                              | I(VBAT),                |     |     |     |      |

|               |                                                     | Standby mode            |     |     |     |      |

| I_stby_87_60  |                                                     | V(VCC) = V(MODE) = 0 V, |     |     | 95  | uA   |

| 1_3109_07_00  | T87 application                                     | V(VBAT) < 27 V          |     |     | 95  | u.A  |

|               |                                                     | V(Ci)>-1.5 V,           |     |     |     |      |

|               |                                                     | T <sub>J</sub> < 60 °C  |     |     |     |      |

|               |                                                     | I(VCC) + I(VBAT),       |     |     |     |      |

|               |                                                     | Standby mode            |     |     |     |      |

|               |                                                     | $V(VCC) = V(VBAT_S)$    |     |     |     |      |

| Lathy 30      | Standby power input in                              | V(VBAT_S) < 27 V        |     | 40  | 190 | uA   |

|               | T30 application                                     | V(MODE) = 0 V           |     | 40  | 190 | uA   |

|               |                                                     | V(ST) = V(VCC)          |     |     |     |      |

|               |                                                     | $V(DO_LIN) = V(VCC)$    |     |     |     |      |

|               |                                                     | T <sub>J</sub> < 120 °C |     |     |     |      |

## 2.5.2 Under- and Over-Voltage Thresholds

Table 10. Under- and over-voltage thresholds electrical characteristics

| Parameter      | Description                                             | Conditions                 | Min           | Тур           | Max           | Unit |

|----------------|---------------------------------------------------------|----------------------------|---------------|---------------|---------------|------|

| UVD_VCC_f      | VCC UVD threshold (falling edge)                        | Note 1                     | 3.2           |               |               | V    |

| UVD_VCC_s      | VCC UVD threshold (rising edge)                         | Note 1                     |               |               | 4.3           | V    |

| HYST_UVD_VCC   | VCC UVD hysteresis                                      |                            |               | 0.25          |               | V    |

| UVD_AVDD_f     | AVDD UVD<br>threshold<br>(falling edge)                 |                            | 0.86x<br>AVDD |               |               |      |

| UVD_AVDD_s     | AVDD UVD<br>threshold<br>(rising edge)                  | Note 3                     |               |               | 0.97x<br>AVDD |      |

| HYST_UVD_AVDD  | AVDD UVD<br>hysteresis                                  |                            |               | 0.06x<br>AVDD |               |      |

| UVD_DVDD_f     | DVDD UVD<br>threshold<br>(falling edge)                 |                            | 0.88x<br>DVDD |               |               |      |

| UVD_DVDD_s     | DVDD UVD<br>threshold<br>(rising edge)                  | Note 3                     |               |               | 0.97x<br>DVDD |      |

| UVD_DVDD_start | DVDD UVD<br>threshold<br>(rising edge) on<br>startup    | Note 4                     | 1.51          |               | 2.2           | V    |

| HYST_UVD_DVDD  | DVDD UVD hysteresis                                     |                            |               | 0.05x<br>DVDD |               |      |

| UVD_uVDD_f     | uVDD UVD<br>threshold<br>(falling edge)                 | See sections 3.2 and 4.1.3 | 0.88x<br>uVDD |               |               |      |

| UVD_uVDD_start | uVDD UVD<br>threshold<br>(rising edge) on cold<br>start | Note 4                     | 2.79          |               | 3.9           | V    |

| UVD_uVDD_s     | uVDD UVD<br>threshold<br>(rising edge)                  | See sections 3.2 and 4.1.3 |               |               | 0.97x<br>uVDD |      |

| HYST_UVD_uVDD  | uVDD UVD<br>hysteresis                                  |                            |               | 0.05x<br>uVDD |               |      |

| UVD_SVDD_f     | VBAT_SVDD UVD<br>threshold<br>(falling edge)            |                            | 0.75x<br>SVDD |               |               |      |

| UVD_SVDD_s     | VBAT_SVDD UVD<br>threshold<br>(rising edge)             | Note 3                     |               |               | 0.97x<br>SVDD |      |

| HYST_UVD_SVDD  | VBAT_SVDD UVD hysteresis                                |                            |               | 0.05x<br>SVDD |               |      |

| UVD_VBAT_f     | VBAT_S UVD<br>threshold<br>(falling edge)               | See sections 3.2 and 4.1.3 | 4.5           |               |               | V    |

| UVD_VBAT_s     | VBAT_S UVD<br>threshold<br>(rising edge)                | See sections 3.2 and 4.1.3 |               |               | 5.6           | V    |

#### **Power Control IC Datasheet**

| Parameter                           | Description                               | Conditions                                     | Min  | Тур | Max  | Unit |

|-------------------------------------|-------------------------------------------|------------------------------------------------|------|-----|------|------|

| HYST_UVD_VBAT                       | VBAT_S UVD hysteresis                     |                                                |      | 0.6 |      | V    |

| OVD_VBAT_f0                         | VBAT_S OVD<br>threshold<br>(falling edge) | S_OVD 1.0 = 0<br>(see section 4.1.4)           | 25.7 |     |      | V    |

| OVD_VBAT_s0                         | VBAT_S OVD<br>threshold<br>(rising edge)  | S_OVD 1.0 = 0<br>(see section 4.1.4)           |      |     | 31.0 | V    |

| HYST_OVD_VBAT_0                     | VBAT_S OVD hysteresis                     | S_OVD 1.0 = 0<br>(see section 4.1.4)           |      | 1.6 |      | V    |

| OVD_VBAT_f1                         | VBAT_S OVD<br>threshold<br>(falling edge) | S_OVD 1.0 = 1<br>(see section 4.1.4)           | 18.2 |     |      | V    |

| OVD_VBAT_s1                         | VBAT_S OVD<br>threshold<br>(rising edge)  | S_OVD 1.0 = 1<br>(see section 4.1.4)           |      |     | 22.0 | V    |

| HYST_OVD_VBAT_1                     | VBAT_S OVD hysteresis                     | S_OVD 1.0 = 1<br>(see section 4.1.4)           |      | 0.9 |      | V    |

| OVD_VBAT_f2                         | VBAT_S OVD<br>threshold<br>(falling edge) | S_OVD 1.0 = 2<br>(see section 4.1.4)           | 17.3 |     |      | V    |

| OVD_VBAT_s2                         | VBAT_S OVD<br>threshold<br>(rising edge)  | S_OVD 1.0 = 2<br>(see section 4.1.4)<br>Note 6 |      |     | 21.0 | V    |

| HYST_OVD_VBAT_2                     | VBAT_S OVD hysteresis                     | S_OVD 1.0 = 2<br>(see section 4.1.4)           |      | 0.9 |      | V    |

| OVD_VBAT_f3                         | VBAT_S OVD<br>threshold<br>(falling edge) | S_OVD 1.0 = 3<br>(see section 4.1.4)           | 16.3 |     |      | V    |

| OVD_VBAT_s3                         | VBAT_S OVD<br>threshold<br>(rising edge)  | S_OVD 1.0 = 3<br>(see section 4.1.4)<br>Note 6 |      |     | 19.7 | V    |

| HYST_OVD_VBAT_3                     | VBAT_S OVD hysteresis                     | S_OVD 1.0 = 3<br>(see section 4.1.4)           |      | 0.9 |      | V    |

| UVD_VCP_VBAT                        | VCP-VBAT UVD threshold                    | Note 2, Note 5                                 | 4.5  |     | 5.4  | V    |

| UVD_VBAT_S, OVD_VBAT_S, VD_VCP_VBAT | Debounce time                             | See Table 36                                   |      |     |      |      |

- **Note 1** Prolonged operation at this voltage range can trip the undervoltage detector at uVDD.

- Note 2 No hysteresis

- Note 3 This value only applies after the fuse array data has been read. For startup, see section 2.2.

- Note 4 This value applies to startup after VCC is powered until the fuse array has been read (see section 2.2).

- Note 5 Special characteristic as per VDA Vol. 2 or PPAP: S = safety

- **Note 6** Special characteristic as per VDA Vol. 2 or PPAP: F = functional

## 2.5.3 Voltage Regulator

Table 11. Voltage regulator electrical characteristics

| Parameter | Description                         | Conditions                                                               | Min  | Тур | Max  | Unit |

|-----------|-------------------------------------|--------------------------------------------------------------------------|------|-----|------|------|

| AVDD      | AVDD w/o external load current      | I(AVDD) = 0 A                                                            | 3.4  |     | 4.0  | V    |

| AVDD_load | AVDD w/ external load current       | I(AVDD) = -2 mA                                                          | 3.4  |     | 4.0  | V    |

| DVDD      | DVDD w/o external load current      | I(DVDD) = 0 A                                                            | 1.62 |     | 2.0  | V    |

| DVDD_load | DVDD w/ external load current       | I(DVDD) = -2 mA                                                          | 1.62 |     | 2.0  | V    |

| uVDD      | uVDD w/o external load current      | I(uVDD) = 0 A                                                            | 3.1  |     | 3.75 | ٧    |

| uVDD_load | uVDD w/ external load current       | I(uVDD) = -12.5 mA                                                       | 3.1  |     | 3.75 | V    |

| SVDD      | VBAT-SVDD w/o external load current | I(uVDD) = 0 A                                                            | 3.6  |     | 4.6  | V    |

| SVDD_load | VBAT-SVDD w/ external load current  | I(SVDD)=2 mA                                                             | 3.6  |     | 4.6  | V    |

| I_AVDD    | AVDD current limiting               |                                                                          | -15  |     |      | mA   |

| I_DVDD    | DVDD current limiting               |                                                                          | -15  |     |      | mA   |

| I_uVDD    | uVDD current limiting               |                                                                          | -40  |     |      | mA   |

| I_SVDD    | SVDD current limiting               |                                                                          |      |     | 15   | mA   |

| t_won     | Wake-up time                        | Startup time between identified wake-up condition and deactivated uRESET |      | 2   | 15   | ms   |

#### 2.5.4 uC Interface

Table 12. uC interface electrical characteristics

| Parameter     | Description         | Conditions                                | Min           | Тур | Max           | Unit |

|---------------|---------------------|-------------------------------------------|---------------|-----|---------------|------|

| VOH_uC        | VOH                 | Pins RXD, uCI, MISO<br>@ I = -1 mA        | 0.8x<br>uVDD  |     |               |      |

| VOL_uC        | VOL                 | Pins RXD, uCl, MISO,<br>uRESET @ I = 1 mA |               |     | 0.2x<br>uVDD  |      |

| VIH_uC        | VIH                 | Pins TXD, uGi, SSI, SCLK,<br>MOSI, uDO    |               |     | 0.75x<br>uVDD |      |

| VIL_uC        | VIL                 | Pins TXD, uGi, SSI, SCLK,<br>MOSI, uDO    | 0.25x<br>uVDD |     |               |      |

| RPD_uC        | PD resistor         | Pins uGi, MOSI, SCLK, TRST<br>Note 2      | 40            |     | 250           | kOhm |

| RPU_uC        | PU resistor         | Pins SSI, TXD<br>Note 2                   | 40            |     | 250           | kOhm |

| RPU_uC_uRESET | PU resistor (reset) | Pin uRESET                                | 10            |     | 60            | kOhm |

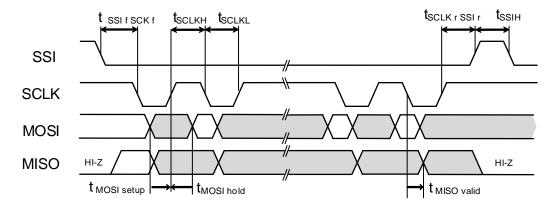

| fSPI          | SPI frequency       | See Figure 11                             |               |     | 8             | MHz  |

| tsclkh        | SCLK high time      | See Figure 11                             | 50            |     |               | ns   |

| tsclkl        | SCLK low time       | See Figure 11                             | 50            |     |               | ns   |

| tSSIH         | SSI high time       | See Figure 11                             | 180           |     |               | ns   |

| tSSIfSCLKf    | SSI setup time      | See Figure 11                             | 10            |     |               | ns   |

| tSCLKrSSIr    | SSI hold time       | See Figure 11                             | 10            |     |               | ns   |

| t_MOSI_setup  | MOSI setup time     | See Figure 11                             | 10            |     |               | ns   |

| t_MOSI_hold   | MOSI hold time      | See Figure 11                             | 10            |     |               | ns   |

| t_MISO_valid  | MISO valid time     | CL < 25 pF; see Figure 11                 |               |     | 20            | ns   |

| Parameter   | Description              | Conditions         | Min | Тур | Max | Unit |

|-------------|--------------------------|--------------------|-----|-----|-----|------|

| t_min_reset | Min. reset time          | Note 1             |     | 100 |     | us   |

| Imiso_leak  | MISO pin leakage current | V_MISO = 0.5(uVDD) | -1  |     | 1   | uA   |

| ludo_leak   | UDO pin leakage current  | V_UDO = 5 V        | -1  |     | 7   | uA   |

Note 1 Subject to the tolerance of the oscillator frequency F\_OSC

**Note 2** The uDO pin has neither PU nor PD resistance. Therefore, it must be wired in all applications. (Exception: T30 application with wake-up via DIO\_BUS.)

## 2.5.5 Internal Logic

Table 13. Internal logic electrical characteristics

| Parameter | Description     | Conditions | Min  | Тур | Max  | Unit |

|-----------|-----------------|------------|------|-----|------|------|

| F_OSZ     | Clock frequency |            | 14.4 | 16  | 17.6 | MHz  |

### 2.5.6 Charge Pump

Table 14. Charge pump electrical characteristics

| Parameter  | Description            | Conditions                                                                               | Min  | Тур | Max  | Unit |

|------------|------------------------|------------------------------------------------------------------------------------------|------|-----|------|------|

| VCP_VBAT_2 | VCP-VBAT under load    | In VBAT_2 range,<br>0 > I(VCP_DC) > -150 μA, all<br>gates on                             | 5.4  | 10  | 15   | V    |

| VCP_VBAT_3 | VCP-VBAT under load    | In VBAT_3 range,<br>0 > I(VCP_DC) > -150 μA, all<br>gates on                             | 6.0  | 10  | 15   | V    |

| VCP_clamp  | VCP–VBAT clamp voltage | I(VCP)=1 mA                                                                              | 11.0 |     | 16.0 | V    |

| ICP_Leak   | VCP_leakage            | VCP = VBAT + 10 V,<br>VBAT = VBAT_S = 30 V<br>CP_ON, no CP clock<br>Gates 1–5 static-low | 20   |     | 300  | uA   |

### 2.5.7 Gate Control

Table 15. Gate control electrical characteristics

| Parameter       | Description                                                                                                                          | Conditions                            | Min | Тур | Max | Unit |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|-----|-----|------|

| TOL_IGATE_UP    | Gate charging current tolerance                                                                                                      | V(Gi) = V(VCP) - 2 V,<br>see Table 50 | -45 |     | 45  | %    |

| TOL_IGATE_DOWN  | Gate discharge current tolerance                                                                                                     | V(Gi) = 2 V,<br>see Table 50          | -45 |     | 45  | %    |

| Delta120,IF0,R0 | Difference<br>between gate<br>discharge and<br>gate charging<br>current of two<br>different channels<br>IF0,x - IR0,y                | Temperature ≤ 120 °C<br>IR = IF = 0   | -35 |     | +39 | uA   |

| Delta150IF0,R0  | Difference<br>between gate<br>discharge and<br>gate charging<br>current of two<br>different channels<br>across entire<br>temperature | IR = IF = 0                           | -35 |     | +85 | uA   |

| Parameter         | Description                                                | Conditions                                                                                                                                                                  | Min   | Тур | Max  | Unit |

|-------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|------|

|                   | range<br>IF0,x - IR0,y                                     |                                                                                                                                                                             |       |     |      |      |

| IGATE_DOWN_FAST   | Fast discharge current                                     | V(Gi) = V(VCP) - 2 V,<br>See section 3.5                                                                                                                                    | -2.8  |     | -1.4 | mA   |

| RPU_GATE_15       | Effective PU resistance                                    | V(Gi) - V(Ci) > VTHRES_GATE, See section 3.5, Figure 5, R9 TR20 = 0, test condition: V(Gi) = V(VCP) - 2 V                                                                   | 2.5   |     | 8.0  | kΩ   |

| RPU_GATE_20       | Effective PU resistance                                    | V(Gi) - V(Ci) > VTHRES_GATE, See section 3.5, Figure 5, R9 TR20 = 1, test condition: V(Gi) = V(VCP) - 2 V                                                                   | 0.8   |     | 2.5  | kΩ   |

| Ishort_PU_15      | High-side short circuit current                            | TR20=0,<br>V(Gi)=0<br>Gate_charged                                                                                                                                          | -1.4  |     | -0.5 | mA   |

| Ishort_PU_20      | High-side short circuit current                            | TR20=1,<br>V(Gi)=0<br>Gate_charged                                                                                                                                          | -4.0  |     | -1.6 | mA   |

| RPD_GATE_STDBY    | Effective PD resistance in STDBY                           | See section 3.5, Figure 5, R5 Test condition: V(Gi) = 2.0 V Device in STDBY                                                                                                 | 4.0   |     | 10   | kΩ   |

| tD_Gi             | Gate control runtime                                       | Rising and falling edge<br>0.75(uVDD) or 0.25(uVDD)<br>and uGi up to 50% VCP at Gi<br>Cload at Gi = 100 pF,<br>VBAT = 12 V,<br>IR[3:0] = IF[3:0] = 0x5<br>EN_DLY[5:0] = 0x0 | 4     |     | 10   | us   |

| VGS_clamp_p       | Positive VGS clamp voltage                                 | I(Gi) = 4.5 mA<br>-25 V < V(Gi) < 35 V<br>TR20=x                                                                                                                            | 11.0  |     | 18   | V    |

| VGS_clamp_n       | Negative VGS clamp voltage                                 | I(Gi) = -4.5 mA<br>-25 V < V(Gi) < 35 V<br>TR20 = x                                                                                                                         | -18.0 |     | -11  | V    |

| VGS_standoff      | VGS standoff                                               | I(Gi) = 100 μA Can only be measured in test mode                                                                                                                            | 9.0   |     |      | V    |

| VC_shortGS_noBATS | V(Ci) to close<br>gate source<br>switch when<br>VBAT_S low | VBAT_S = 0V<br>V(Gi,Ci) < 600 mV<br>@I(G) = 300 μA<br>Note 1                                                                                                                |       |     | -2.0 | >    |

| VC_shortGS_BATS   | V(Ci) to close<br>gate source<br>switch                    | VBAT_S > 2 V<br>V(Gi,Ci) < 600 mV<br>@I(G) = 300 μA<br>Gate Off<br>Note 1                                                                                                   |       |     | -1.5 | V    |

| Parameter | Description                                      | Conditions | Min  | Тур | Max | Unit |

|-----------|--------------------------------------------------|------------|------|-----|-----|------|

| C_LT_GND  | Detection<br>threshold for V_C<br>lower than GND |            | -0.5 |     | 0.5 | V    |

Note 1 Special characteristic as per VDA Vol. 2 or PPAP: S = safety

### 2.5.8 Short Circuit Power Shutdown

#### Table 16. Short Circuit power shutdown electrical characteristics

| Parameter | Description         | Conditions             | Min | Тур | Max | Unit |

|-----------|---------------------|------------------------|-----|-----|-----|------|

| TOL_ISC   | Threshold tolerance | See Table 45<br>Note 1 | -10 |     | 15  | %    |

Note 1 Special characteristic as per VDA Vol. 2 or PPAP: S = safety

### 2.5.9 DIO\_BUS

#### Table 17. DIO\_BUS electrical characteristics

| Parameter            | Description               | Conditions                                                       | Min   | Тур      | Max   | Unit      |

|----------------------|---------------------------|------------------------------------------------------------------|-------|----------|-------|-----------|

| I <sub>BUS_LIM</sub> | Dominant current limiting | VBUS =18 V                                                       | 40    |          | 200   | mA        |

| BUS PAS dom          | Driver off, bus dominant  | Driver off,                                                      | -1    |          |       | mA        |

| IBUS_PAS_dom         | leakage current           | VBUS = 0 V, V(T87) = 12 V                                        | - 1   |          |       | ША        |

|                      |                           | Driver off,                                                      |       |          |       |           |

| IBUS_PAS_rec         | Driver off, bus recessive | 8 V < VBUS < 18 V                                                |       |          | 50    | uA        |

| 1200_1710_100        | leakage current           | 8 V < V(T87) < 18 V                                              |       |          |       | <b></b> . |

|                      |                           | VBUS > V(T87)                                                    |       |          |       |           |

|                      | Ground disconnect leakage | VCC = 0 V                                                        |       |          |       |           |

| IBUS_NO_GND          | current                   | V(KL87)-12 V < VBUS <<br>V(KL87) + 6 V                           | -2.5  |          | 1     | mA        |

| IBUS NO BAT          | T87 disconnect leakage    | VCC=0 V                                                          |       |          | 100   | uA        |

| IBUS_NO_BAT          | current                   | 0 V < VBUS < 18 V                                                |       |          | 100   |           |

| V <sub>BUS_dom</sub> | RX threshold dominant     |                                                                  |       |          | 0.4   | VCC       |

| V <sub>BUS_rec</sub> | RX threshold recessive    |                                                                  | 0.6   |          |       | VCC       |

| V <sub>BUS_cnt</sub> | RX mid-voltage            | $V_{BUS\_cnt} = (V_{th\_dom} + V_{th\_rec}) / 2$                 | 0.475 |          | 0.525 | VCC       |

| V BOO_CIII           | TOT THIS VOILAGE          | Note 1                                                           | 0.170 |          | 0.020 | , 00      |

| V <sub>HYS</sub>     | RX hysteresis             | VHYS = Vth_rec-Vth_dom                                           |       |          | 0.175 | VCC       |

|                      | ,                         | Note 1                                                           |       |          |       |           |

|                      |                           | $TH_{REC} = 0.744 \times VCC$                                    |       |          |       |           |

|                      | DIO_BUS                   | TH <sub>dom</sub> =0.581 x VCC                                   |       |          |       |           |

| D1                   | Duty Cycle 1              | 7.0 V < VCC < 18 V                                               | 0.396 |          |       |           |

|                      |                           | $t_{Bit} = 50 \ \mu s$                                           |       |          |       |           |

|                      |                           | D1 = t <sub>bus_rec</sub> / (2 x tBit)                           |       |          |       |           |

|                      |                           | TH <sub>REC</sub> = 0.422 x VCC                                  |       |          |       |           |

| D0                   | DIO_BUS                   | $TH_{dom} = 0.284 \times VCC$                                    |       |          | 0.504 |           |

| D2                   | Duty Cycle 2              | 7.6 V < VCC < 18 V                                               |       |          | 0.581 |           |

|                      |                           | $t_{Bit} = 50 \ \mu s$                                           |       |          |       |           |

|                      |                           | $D2 = t_{bus\_rec} / (2xt_{Bit})$                                |       |          |       |           |

|                      |                           | TH <sub>REC</sub> = 0.788 x VCC                                  |       |          |       |           |

| D3                   | DIO_BUS                   | TH <sub>dom</sub> = 0.616 x VCC<br>7.0 V < VCC < 18 V            | 0.417 |          |       |           |

| D3                   | Duty Cycle 3              |                                                                  | 0.417 |          |       |           |

|                      |                           | $t_{Bit} = 96 \mu s$<br>$D3 = t_{bus\_rec} / (2 \times t_{Bit})$ |       |          |       |           |

|                      |                           | DO - SUS_IECT (Z X CDIL)                                         |       | <u> </u> |       |           |

| Parameter           | Description                                 | Conditions                                                                                       | Min           | Тур | Max         | Unit |

|---------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------|---------------|-----|-------------|------|

| D4                  | DIO_BUS<br>Duty Cycle 4                     | THREC = 0.389 x VCC THdom = 0.251 x VCC 7.6 V < VCC < 18 V tBit = 96 µs D4 = tbus_rec / (2xtBit) |               |     | 0.590       |      |

| t <sub>rx_pd</sub>  | RX delay time                               |                                                                                                  |               |     | 6           | us   |

| t <sub>rx_sym</sub> | Symmetry trx_pd for rising and falling edge |                                                                                                  | -2            |     | 2           | us   |

| R <sub>SLAVE</sub>  | Bus pull-up                                 |                                                                                                  | 20            |     | 60          | kΩ   |

| IPU_STDBY           | Pull-up_power_source                        | Standby mode, wake-up condition: DIO_BUS V(VCC) > V(DO_LIN) > V(PGND)                            |               |     | 60          | uA   |

| V_WU_DIO            | DIO_BUS wake-up threshold                   |                                                                                                  | VCC-<br>3.8 V |     | VCC-<br>2 V |      |

| T_WU_DIO            | DIO_BUS wake-up debounce time               |                                                                                                  | 28            |     | 150         | us   |

| T_MAX_DO<br>M       | Max. dominant phase time at DIO-TX          |                                                                                                  | 6             | 9   | 12          | ms   |

Note 1  $V_{th\_dom}$  and  $V_{th\_rec}$  indicate the actual thresholds for  $V_{BUS\_dom}$  and  $V_{BUS\_rec}$ .

#### 2.5.10 DO

Table 18. DO electrical characteristics

| Parameter      | Description                                 | Conditions                                                       | Min | Тур | Max | Unit |

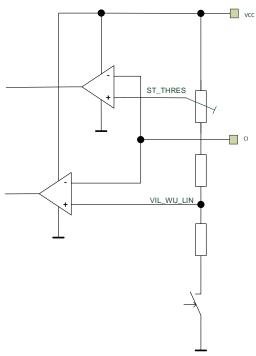

|----------------|---------------------------------------------|------------------------------------------------------------------|-----|-----|-----|------|