# 1-TO-12 DIFFERENTIAL CLOCK BUFFER

IDTCV128

#### **FEATURES:**

- · Compliant with Intel DB1200G rev. 0.5

- · DIF Clock Support

- 12differential clock output pairs @ 0.7 V

- 50 ps skew performance (same gear)

- OE pin Control of All Outputs

- · 3.3 V Operation

- Gear Ratio supporting generation of clocks at a different frequency ratioed from the input.

- Split outputs supporting options of 2 outputs @1:1 and remaining 10 pairs at an alternate gear

- · Pin level OE control of individual outputs

- Multiple output frequency options up to 400Mhz as a gear ratio of input clocks of 100-400Mhz

- · Output is HCSL compatible

- SMBus Programmable configurations

- · PLL Bypass Configurable

- SMBus address configurable to allow multiple buffer control in a single control network

- · Programmable Bandwidth

- · Glitchfree transition between frequency states

- Available in SSOP and TSSOP packages

#### **DESCRIPTION:**

The CV128 differential buffer complies with Intel DB1200G rev. 0.5, and is designed to work in conjunction with the main clock of CK409, CK410/CK410M and CK410B etc., PLL is off in bypass mode and no clock detect.

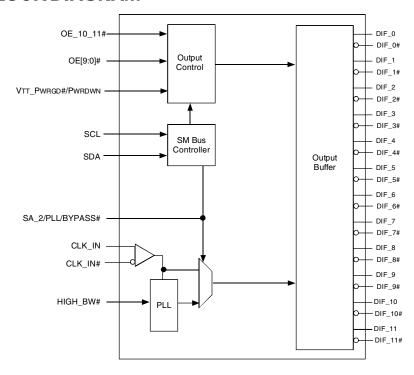

#### **FUNCTIONAL BLOCK DIAGRAM**

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

**COMMERCIAL TEMPERATURE RANGE**

**JUNE 29, 2007**

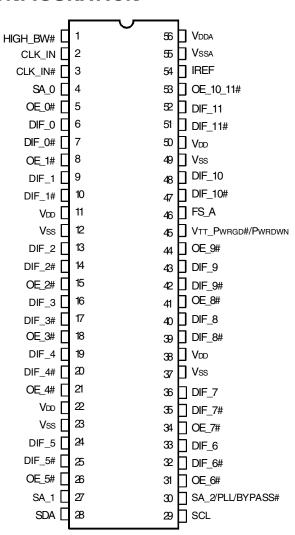

#### **PIN CONFIGURATION**

SSOP/ TSSOP TOP VIEW

#### ABSOLUTE MAXIMUM RATINGS(1)

| Symbol   | Description                     | Min.      | Max. | Unit |

|----------|---------------------------------|-----------|------|------|

| VDDA     | 3.3V Core Supply Voltage        |           | 4.6  | ٧    |

| VDD      | 3.3V Logic Input Supply Voltage | GND - 0.5 | 4.6  | V    |

| Tstg     | Storage Temperature             | -65       | +150 | °C   |

| TAMBIENT | Ambient Operating Temperature   | 0         | +70  | °C   |

| TCASE    | Case Temperature                |           | +115 | °C   |

| ESD Prot | Input ESD Protection            | 2000      |      | V    |

|          | Human Body Model                |           |      |      |

#### NOTE:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **OE FUNCTIONALITY**

| OE# - Pin | OE# - SMBus bit | DIF      | DIFF]#   |

|-----------|-----------------|----------|----------|

| 0         | 1               | Normal   | Normal   |

| 0         | 0               | Tristate | Tristate |

| 1         | 1               | Tristate | Tristate |

| 1         | 0               | Tristate | Tristate |

#### **PIN DESCRIPTION**

| Pin Name               | Туре    | Pin #                                                                             | Description                                                                                                                                             |

|------------------------|---------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_IN, CLK_IN#        | IN      | 2, 3                                                                              | 0.7v Differential input                                                                                                                                 |

| DIF_[9:0] & DIF_[9:0]# | OUT     | 6, 7, 9, 10, 13, 14, 16,<br>17, 19, 20, 24, 25, 32, 33,<br>35, 36, 39, 40, 42, 43 | 0.7 V Differential clock outputs, geared to a ratio of the input clock                                                                                  |

| DIF & DIF# [11:10]     | OUT     | 47, 48, 51, 52                                                                    | 0.7 V Differential clock outputs, which can be configured to be 1:1 instead of geared. Default is geared same as 0-9 outputs.                           |

| OE_[9:0]#              | IN      | 5, 8, 15, 18, 21, 26,<br>31, 34, 41, 44                                           | 3.3 V LVTTL active LOW input for enabling corresponding differential output clock. Clocks also can be disabled via SMBus registers                      |

| OE_10_11#              | IN      | 53                                                                                | 3.3 V L V TTL active low input for enabling both DIF10 and 11 differential output clocks. Clocks also can be disabled via SMBus registers individually. |

| HIGH_BW#               | IN      | 1                                                                                 | 3.3 V LVTTL input for selecting the PLL bandwidth. 0 = HIGH BW, 1 = LOW BW.                                                                             |

| SCL                    | IN      | 29                                                                                | SMBus slave clock input                                                                                                                                 |

| SDA                    | I/O, OC | 28                                                                                | Open collector SMBus data                                                                                                                               |

| IREF                   | IN      | 54                                                                                | A precision resistor is attached to this pin to set the differential output current                                                                     |

| SA_[0:1]               | IN      | 4, 27                                                                             | 3.3V LVTTL input selecting the address. SA_[2:0] set device SMBus address.                                                                              |

| (1) SA_2/PLL_BYPASS#   | IN      | 30                                                                                | 3.3 V L V TTL input for PLL bypass and SMB us address. 0=PLL bypass mode; 1=PLL mode                                                                    |

| FS_A                   | IN      | 46                                                                                | 3.3V LVTTL input to establish a HIGH (>200Mhz) or LOW frequency(<200Mhz) range                                                                          |

| Vtt_Pwrgd#/Pwrdwn      | IN      | 45                                                                                | 3.3 V LVTTL input to power up or power down the device.                                                                                                 |

#### NOTE:

(1) The SA\_2 pin shares functionality with PLL\_bypass# mode setting. The shared function restricts the device addresses that correspond to SA\_2 =0 as setting the buffer device in PLL\_Bypass#.

#### INDEX BLOCK WRITE PROTOCOL

| Bit   | # of bits | From   | Description                          |

|-------|-----------|--------|--------------------------------------|

| 1     | 1         | Master | Start                                |

| 2-9   | 8         | Master | See SMBus Address Mode table         |

| 10    | 1         | Slave  | Ack (Acknowledge)                    |

| 11-18 | 8         | Master | Register offset byte (starting byte) |

| 19    | 1         | Slave  | Ack (Acknowledge)                    |

| 20-27 | 8         | Master | Byte count, N (0 is not valid)       |

| 28    | 1         | Slave  | Ack (Acknowledge)                    |

| 29-36 | 8         | Master | first data byte (Offset data byte)   |

| 37    | 1         | Slave  | Ack (Acknowledge)                    |

| 38-45 | 8         | Master | 2nd data byte                        |

| 46    | 1         | Slave  | Ack (Acknowledge)                    |

|       |           |        | :                                    |

|       |           | Master | Nth data byte                        |

|       |           | Slave  | Acknowledge                          |

|       |           | Master | Stop                                 |

### **INDEX BYTE WRITE**

Setting bit[11:18] = starting address, bit[20:27] = 01h.

## INDEX BLOCK READ PROTOCOL

Master can stop reading any time by issuing the stop bit without waiting until Nth byte (byte count bit 30-37).

| Bit   | # of bits | From   | Description                                |

|-------|-----------|--------|--------------------------------------------|

| 1     | 1         | Master | Start                                      |

| 2-9   | 8         | Master | See SMBus Address Mode table               |

| 10    | 1         | Slave  | Ack (Acknowledge)                          |

| 11-18 | 8         | Master | Register offset byte (starting byte)       |

| 19    | 1         | Slave  | Ack (Acknowledge)                          |

| 20    | 1         | Master | Repeated Start                             |

| 21-28 | 8         | Master | See SMBus Address Mode table               |

| 29    | 1         | Slave  | Ack (Acknowledge)                          |

| 30-37 | 8         | Slave  | Byte count, N (block read back of N bytes) |

| 38    | 1         | Master | Ack (Acknowledge)                          |

| 39-46 | 8         | Slave  | first data byte (Offset data byte)         |

| 47    | 1         | Master | Ack (Acknowledge)                          |

| 48-55 | 8         | Slave  | 2nd data byte                              |

|       |           |        | Ack (Acknowledge)                          |

|       |           |        | :                                          |

|       |           | Master | Ack (Acknowledge)                          |

|       |           | Slave  | Nth data byte                              |

|       |           |        | Notacknowledge                             |

|       |           | Master | Stop                                       |

#### **INDEX BYTE READ**

Setting bit[11:18] = starting address. After reading back the first data byte, master issues Stop bit.

# **GEAR RATIOS**

| Select FSA | SMBus3 | SMBus2 | SMBus1 | SMBus0 | m  | n | Gear n/m |

|------------|--------|--------|--------|--------|----|---|----------|

| 0          | 0      | 0      | 0      | 0      | 3  | 1 | 0.333    |

| 0          | 0      | 0      | 0      | 1      | 5  | 2 | 0.400    |

| 0          | 0      | 0      | 1      | 0      | 12 | 5 | 0.417    |

| 0          | 0      | 0      | 1      | 1      | 2  | 1 | 0.500    |

| 0          | 0      | 1      | 0      | 0      | 5  | 3 | 0.600    |

| 0          | 0      | 1      | 0      | 1      | 8  | 5 | 0.625    |

| 0          | 0      | 1      | 1      | 0      | 3  | 2 | 0.667    |

| 0          | 0      | 1      | 1      | 1      | 4  | 3 | 0.750    |

| 0          | 1      | 0      | 0      | 0      | 6  | 5 | 0.833    |

| 0          | 1      | 0      | 0      | 1      | 1  | 1 | 1.000    |

| 0          | 1      | 0      | 1      | 0      | 5  | 6 | 1.200    |

| 0          | 1      | 0      | 1      | 1      | 4  | 5 | 1.250    |

| 0          | 1      | 1      | 0      | 0      | 3  | 4 | 1.333    |

| 0          | 1      | 1      | 0      | 1      | 2  | 3 | 1.500    |

| 0          | 1      | 1      | 1      | 0      | 3  | 5 | 1.667    |

| 0          | 1      | 1      | 1      | 1      | 1  | 2 | 2.000    |

| 1          | 0      | 0      | 0      | 0      | 3  | 1 | 0.333    |

| 1          | 0      | 0      | 0      | 1      | 5  | 2 | 0.400    |

| 1          | 0      | 0      | 1      | 0      | 12 | 5 | 0.417    |

| 1          | 0      | 0      | 1      | 1      | 2  | 1 | 0.500    |

| 1          | 0      | 1      | 0      | 0      | 5  | 3 | 0.600    |

| 1          | 0      | 1      | 0      | 1      | 8  | 5 | 0.625    |

| 1          | 0      | 1      | 1      | 0      | 3  | 2 | 0.667    |

| 1          | 0      | 1      | 1      | 1      | 5  | 4 | 0.800    |

| 1          | 1      | 0      | 0      | 0      | 6  | 5 | 0.833    |

| 1          | 1      | 0      | 0      | 1      | 1  | 1 | 1.000    |

| 1          | 1      | 0      | 1      | 0      | 5  | 6 | 1.200    |

| 1          | 1      | 0      | 1      | 1      | 4  | 5 | 1.250    |

| 1          | 1      | 1      | 0      | 0      | 3  | 4 | 1.333    |

| 1          | 1      | 1      | 0      | 1      | 2  | 3 | 1.500    |

| 1          | 1      | 1      | 1      | 0      | 3  | 5 | 1.667    |

| 1          | 1      | 1      | 1      | 1      | 1  | 2 | 2.000    |

# TARGETED INPUT AND OUTPUT FREQUENCIES

|             | REGOENOIES   |     |          |  |  |  |

|-------------|--------------|-----|----------|--|--|--|

| Input (MHz) | Output (MHz) | m:n |          |  |  |  |

| 200         | 200          | 1:1 |          |  |  |  |

| 267         | 133          | 2:1 |          |  |  |  |

| 160         | 320          | 1:2 |          |  |  |  |

| 333         | 167          | 2:1 |          |  |  |  |

| N/A         | N/A          | N/A |          |  |  |  |

| 400         | 200          | 2:1 |          |  |  |  |

| 200         | 133          | 3:2 |          |  |  |  |

| 133         | 200          | 2:3 |          |  |  |  |

| 400         | 133          | 3:1 |          |  |  |  |

| 133         | 167          | 4:5 |          |  |  |  |

| 167         | 133          | 5:4 |          |  |  |  |

| 333         | 133          | 5:2 |          |  |  |  |

| 200         | 267          | 3:4 |          |  |  |  |

| 267         | 200          | 4:3 |          |  |  |  |

| 400         | 160          | 5:2 |          |  |  |  |

| 167         | 200          | 5:6 |          |  |  |  |

| 200         | 167          | 6:5 |          |  |  |  |

| 200         | 333          | 3:5 |          |  |  |  |

| 333         | 200          | 5:3 |          |  |  |  |

| 267         | 167          | 8:5 | Targeted |  |  |  |

## **SMBUS ADDRESS MODE SELECTION**

| SA_[2:0] | Buffer Address         |

|----------|------------------------|

| 000      | D0h (write) D1h (read) |

| 001      | D2h, D3h               |

| 010      | D4h, D5h               |

| 011      | D6h, D7h               |

| 100      | D8h, D9h               |

| 101      | DAh, DBh               |

| 110      | DCh, DDh               |

| 111      | DEh, DFh               |

## **FUNCTIONALITY AT POWER-UP(1)**

| FSA_410 | CLK_IN (CPU FSB) | DIF[9:0] Output | DIF[11:10] Output |

|---------|------------------|-----------------|-------------------|

| 1       | 100MHz           | 100MHz          | 100MHz            |

| 1       | 133MHz           | 133MHz          | 133MHz            |

| 1       | 166MHz           | 166MHz          | 166MHz            |

| 1       | RESERVED         | RESERVED        | RESERVED          |

| 0       | 200MHz           | 200MHz          | 200MHz            |

| 0       | 266.66MHz        | 266.66MHz       | 266.66MHz         |

| 0       | 333.33MHz        | 333.33MHz       | 333.33MHz         |

| 0       | 400MHz           | 400MHz          | 400MHz            |

#### NOTE:

FSA\_410 is a low-threshold input. Please see the VIL\_Fs and VIH\_Fs specifications in the DC OPERATING CHARACTERISTICS table.

# **CONTROL REGISTERS**

# BYTE 0

| Bit | Output(s) Affected                               | Description/Function | 0            | 1        | Туре | Power On |

|-----|--------------------------------------------------|----------------------|--------------|----------|------|----------|

| 7   | Group of 10 gear #<br>DIF [9:0] Speed selection  |                      | GR selection | 1:1 = ln | RW   | 1        |

| 6   | Group of 2 gear #<br>DIF [11:10] Speed selection |                      | GR selection | 1:1 = In | RW   | 1        |

| 5   | Reserved                                         |                      |              |          | RW   | 1        |

| 4   | FSA latched input                                |                      |              |          | RW   |          |

| 3   | SMBus3                                           |                      |              |          | RW   |          |

| 2   | SMBus2                                           | see Gear Ratio table |              |          | RW   |          |

| 1   | SMBus1                                           |                      |              |          | RW   |          |

| 0   | SMBus0                                           |                      |              |          | RW   |          |

### **BYTE 1**

| Bit | Output(s) Affected | Description/Function | 0         | 1      | Туре | Power On |

|-----|--------------------|----------------------|-----------|--------|------|----------|

| 7   | DIF_7              | Output Enable        | Tri-State | Enable | RW   | 1        |

| 6   | DIF_6              | Output Enable        | Tri-State | Enable | RW   | 1        |

| 5   | DIF_5              | Output Enable        | Tri-State | Enable | RW   | 1        |

| 4   | DIF_4              | Output Enable        | Tri-State | Enable | RW   | 1        |

| 3   | DIF_3              | Output Enable        | Tri-State | Enable | RW   | 1        |

| 2   | DIF_2              | Output Enable        | Tri-State | Enable | RW   | 1        |

| 1   | DIF_1              | Output Enable        | Tri-State | Enable | RW   | 1        |

| 0   | DIF_0              | Output Enable        | Tri-State | Enable | RW   | 1        |

# **BYTE 2**

| Bit | Output(s) Affected      | Description/Function | 0           | 1          | Туре | Power On |

|-----|-------------------------|----------------------|-------------|------------|------|----------|

| 7   | Reserved                |                      |             |            | RW   | 1        |

| 6   | PLL_BW# adjust          |                      | 0 = HIGH BW | 1 = LOW BW | RW   | 1        |

| 5   | BYPASS# test mode / PLL |                      | 0 = Bypass  | 1 = PLL    | RW   | 1        |

| 4   | Reserved                |                      |             |            | RW   | 1        |

| 3   | DIF_11                  | Output Enable        | Tristate    | Enable     | RW   | 1        |

| 2   | DIF_10                  | Output Enable        | Tristate    | Enable     | RW   | 1        |

| 1   | DIF_9                   | Output Enable        | Tristate    | Enable     | RW   | 1        |

| 0   | DIF_8                   | Output Enable        | Tristate    | Enable     | RW   | 1        |

# **BYTE 3**

| Bit | Output(s) Affected     | Description / Function      | 0 | 1 | Туре | Power On |

|-----|------------------------|-----------------------------|---|---|------|----------|

| 7   | Readback - OE#_7 Input | Depends on the state of pin |   |   | R    |          |

| 6   | Readback - OE#_6 Input | Depends on the state of pin |   |   | R    |          |

| 5   | Readback - OE#_5 Input | Depends on the state of pin |   |   | R    |          |

| 4   | Readback - OE#_4 Input | Depends on the state of pin |   |   | R    |          |

| 3   | Readback - OE#_3 Input | Depends on the state of pin |   |   | R    |          |

| 2   | Readback - OE#_2 Input | Depends on the state of pin |   |   | R    |          |

| 1   | Readback - OE#_1 Input | Depends on the state of pin |   |   | R    |          |

| 0   | Readback - OE#_0 Input | Depends on the state of pin |   |   | R    |          |

### **BYTE 4**

| Bit | Output(s) Affected         | Description / Function         | 0 | 1 | Туре | Power On |

|-----|----------------------------|--------------------------------|---|---|------|----------|

| 7   | Readback - FSA input       | Latch value of pin at power up |   |   | R    |          |

| 6   | Readback - PLL_BW# In      | Latch value of pin at power up |   |   | R    |          |

| 5   | Readback-PLL_BYPASS# input | Latch value of pin at power up |   |   | R    |          |

| 4   | Reserved                   |                                |   |   |      |          |

| 3   | Reserved                   |                                |   |   |      |          |

| 2   | Readback - OE#_10-11 Input |                                |   |   | R    |          |

| 1   | Readback - OE#_9 Input     |                                |   |   | R    |          |

| 0   | Readback - OE#_8 Input     |                                |   |   | R    |          |

### **BYTE 5**

| Bit | Output(s) Affected | Description / Function | 0 | 1 | Туре | Power On |

|-----|--------------------|------------------------|---|---|------|----------|

| 7   |                    | Revision ID            |   |   |      | 0        |

| 6   |                    | Revision ID            |   |   |      | 0        |

| 5   |                    | Revision ID            |   |   |      | 0        |

| 4   |                    | Revision ID            |   |   |      | 0        |

| 3   |                    | Vendor ID              |   |   |      | 0        |

| 2   |                    | Vendor ID              |   |   |      | 1        |

| 1   |                    | Vendor ID              |   |   |      | 0        |

| 0   |                    | VendorID               |   |   |      | 1        |

## **BYTE 6 - DEVICE ID**

# **BYTE 7 - BYTE COUNT**

## DC OPERATING CHARACTERISTICS

Following Conditions Apply Unless Otherwise Specified: Operating Condition: VdD/Vdda =  $3.3V \pm 5\%$

| Symbol | Parameter                 | Test Conditions | Min.    | Тур. | Max.    | Unit |

|--------|---------------------------|-----------------|---------|------|---------|------|

| Vdda   | 3.3 V Core Supply Voltage | 3.3 V ±5%       | 3.135   |      | 3.465   | V    |

| Vdd    | 3.3 V I/O Supply Voltage  | 3.3 V ±5%       | 3.135   |      | 3.465   | V    |

| ViH    | 3.3 V Input High Voltage  | V <sub>DD</sub> | 2.0     |      | VDD+0.3 | V    |

| VIL    | 3.3 V Input Low Voltage   |                 | Vss-0.3 |      | 0.8     | V    |

| lıL    | Input Leakage Current     | 0 < VIN < VDD   | -5      |      | +5      | μΑ   |

| Vон    | 3.3 V Output High Voltage | Ioh = -1 mA     | 2.4     |      |         | V    |

| Vol    | 3.3 V Output Low Voltage  | IoI = 1 mA      |         |      | 0.4     | V    |

| Cin    | Input Pin Capacitance     |                 | 1.5     |      | 5       | pF   |

| Cout   | Output Pin Capacitance    |                 |         |      | 6       | pF   |

| Lpin   | Pin Inductance            |                 |         |      | 7       | nH   |

| Ta     | Ambient Temperature       | No Airflow      | 0       |      | 70      | °C   |

# **OUTPUT RELATIONAL TIMING PARAMETERS**

| Group                   | Parameter                                                     | Min.   | Тур. | Max.          |

|-------------------------|---------------------------------------------------------------|--------|------|---------------|

| CLK_IN, DIF [x:0]       | Input to Output Skew in PLL mode (1:1 only)                   | 0ps    |      | 20% of period |

| CLK_IN, DIF [x:0]       | Input to Output Skew in non PLL mode (1:1 only)               | 3ns    |      | 40% of period |

| DIF                     | DIFF[x:0] Pin-to-Pin Skew (output within same group)          | 0ps    |      | 50 ps         |

| DIF [9:0] - DIF [11:10] | Additive skew between pin groups (group of 2 and group of 10) | 0ps    |      | 75 ps         |

| DIF                     | Jitter, Cycle_cycle <sup>(1)</sup>                            | 0ps    |      | 50ps          |

| DIF                     | Accumulated Differential Phase Jitter                         | -100ps |      | +100ps        |

#### NOTE:

## **PLL BANDWIDTH AND PEAKING**

| Group | Parameter                        | Min. | Тур. | Max. | Unit |

|-------|----------------------------------|------|------|------|------|

| DIF   | PLL Peaking (HIGH_BW# = 0)       |      | 1    | 2    | dB   |

| DIF   | PLL Peaking (HIGH_BW# = 1)       |      | 1    | 2    | dB   |

| DIF   | PLL Bandwidth (HIGH_BW# = 0)     | 2    | 3    | 4    | MHz  |

| DIF   | PLL Bandwidth (HIGH_BW# = 1)     | 0.7  | 1    | 1.4  | MHz  |

| DIF   | Output phase jitter impact       | 0ps  | -    |      | ps   |

|       | (PCIe: including BW 1.5-22Mhz)   |      |      | 85   | ps   |

|       | (FBD/CSI: including BW 11-33Mhz) |      |      | 40   | ps   |

<sup>1.</sup> Bypass mode, additive.

# **DIF TIMING CHARACTERISTICS (NON SSC CLOCK INPUT)**

DIF 0.7 V AC Timing Characteristics (Non-Spread Spectrum Mode)

|                 |                                          |       | CLK - 100Mhz, 133.3Mhz, 166.6Mhz, 200Mhz, 233.3Mhz, 266.6Mhz, 333Mhz, 400Mhz |           |      |

|-----------------|------------------------------------------|-------|------------------------------------------------------------------------------|-----------|------|

| Symbol          | Parameter                                | Min.  | Тур.                                                                         | Max.      | Unit |

| Laccuracy       | Long Accuracy                            |       |                                                                              | 0         | ppm  |

| TPERIOD         | Average Period                           | -0.3% |                                                                              | +0.3%     | ns   |

| Tabsmin         | Absolute Minimum Host CLK Period         | -2.5% |                                                                              |           | ns   |

| TRISE           | Rise Time                                | 125   |                                                                              | 525       | ps   |

| TFALL           | Fall Time                                | 125   |                                                                              | 525       | ps   |

| $\DeltaT$ RISE  | Rise Time Variation                      |       |                                                                              | 75        | ps   |

| $\DeltaT$ FALL  | Fall Time Variation                      |       |                                                                              | 75        | ps   |

| VHIGH           | Voltage HIGH (typ 0.7 Volts)             | 660   |                                                                              | 850       | mV   |

| VLOW            | Voltage LOW (typ 0 Volts)                | -300  |                                                                              | +150      | mV   |

| Vcross absolute | Absolute Crossing Point Voltages         | 250   |                                                                              | 550       | mV   |

| Vcross relative | Relative Crossing Point Voltages         | Calc  |                                                                              | Calc      |      |

| Total ∆ Vcross  | Total Variation of Vcross Over All Edges |       |                                                                              | 140       | mV   |

| Tccjitter       | Cycle-to-Cycle Jitter <sup>(1)</sup>     |       |                                                                              | 50        | ps   |

| Duty Cycle      |                                          | 45    |                                                                              | 55        | %    |

| Vovs            | Maximum Voltage (Overshoot)              |       |                                                                              | VH + 0.3V |      |

| Vuds            | Minimum Voltage (Undershoot)             |       |                                                                              | - 0.3     |      |

| VrB             | Ringback Voltage                         | 0.2   |                                                                              | N/A       | Volt |

NOTE:

# **DIF TIMING CHARACTERISTICS (SSC CLOCK INPUT)**

DIF 0.7 V AC Timing Characteristics (-0.5% Spread Spectrum Mode)

|                 |                                          |                    | CLK - 100Mhz, 133.3Mhz, 166.6Mhz, 200Mhz, 233.3Mhz, 266.6Mhz, 333Mhz, 400Mhz |           |      |

|-----------------|------------------------------------------|--------------------|------------------------------------------------------------------------------|-----------|------|

| Symbol          | Parameter                                | Min.               | Тур.                                                                         | Max.      | Unit |

| Laccuracy       | Long Accuracy                            |                    |                                                                              | 0         | ppm  |

| TPERIOD         | Average Period                           | -0.3%              |                                                                              | +0.53%    | ns   |

| Tabsmin         | Absolute Minimum Host CLK Period         | (period - 0.125ns) |                                                                              |           | ns   |

| Trise           | Rise Time                                | 125                |                                                                              | 525       | ps   |

| TFALL           | Fall Time                                | 125                |                                                                              | 525       | ps   |

| Edge_rate       | Edge_rate                                | 0.5                |                                                                              | 2.8       | V/ns |

| $\Delta T$ rise | Rise Time Variation                      |                    |                                                                              | 75        | ps   |

| $\Delta T$ FALL | Fall Time Variation                      |                    |                                                                              | 75        | ps   |

| VHIGH           | Voltage HIGH (typ 0.7 Volts)             | 660                |                                                                              | 850       | mV   |

| VLOW            | Voltage LOW (typ 0 Volts)                | -300               |                                                                              | +150      | mV   |

| Vcross absolute | Absolute Crossing Point Voltages         | 250                |                                                                              | 550       | mV   |

| Vcross relative | Relative Crossing Point Voltages         | Calc               |                                                                              | Calc      |      |

| Total ∆ Vcross  | Total Variation of Vcross Over All Edges |                    |                                                                              | 100       | mV   |

| Tccjitter       | Cycle-to-Cycle Jitter <sup>(1)</sup>     |                    |                                                                              | 50        | ps   |

| Duty Cycle      |                                          | 45                 |                                                                              | 55        | %    |

| Vovs            | Maximum Voltage (Overshoot)              |                    |                                                                              | VH + 0.3V |      |

| Vuds            | Minimum Voltage (Undershoot)             |                    |                                                                              | - 0.3     |      |

| Vrb             | Ringback Voltage                         | Vx ± 0.2           |                                                                              | N/A       | Volt |

NOTE:

<sup>1.</sup> Bypass mode, additive.

<sup>1.</sup> Bypass mode, additive.

#### **PWRDWN FUNCTIONALITY**

| VTT_PwrGd#/Pwrdwn | DIF    | DIF#   |

|-------------------|--------|--------|

| 0                 | Normal | Normal |

| 1                 | Float  | Float  |

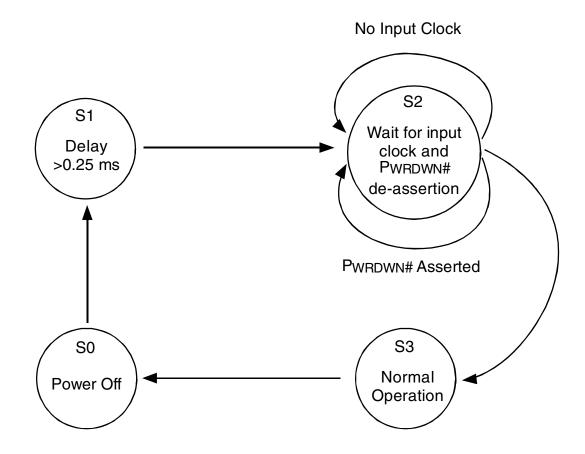

## **BUFFER POWER-UP STATE MACHINE**(1)

| State  | Description                                                                                                                                                                                                                        |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| State0 | Power off                                                                                                                                                                                                                          |

| State1 | After 3.3V supply is detected to rise above 1.8-2V, the buffer enters state 1 and initiates a 0.2ms-0.3ms delay. The total power up latency from power on to all outputs active must be less than 1ms (assume SRC_IN is available) |

| State2 | Buffer waits for a valid clock on the SRC_IN input and PD de-assertion.                                                                                                                                                            |

| State3 | Only after SRC_IN and power valid, PD de-asserted with the current mirror stable, or PLL lock, the DIF outputs are enabled                                                                                                         |

#### NOTE:

1. The total power up latency from power on to all outputs active must be less than 1ms (assuming a valid clock is present on CLK\_IN input). If power is valid and Pwrdwn is de-asserted but no input clocks are present on the CLK\_IN input, DIF clocks must remain disabled. Only after valid input clocks are detected, valid power, Pwrdwn# de-asserted with the PLL locked/stable and the DIF outputs enabled (doesn't apply to bypass mode).

## **BUFFER POWER-UP STATE DIAGRAM**

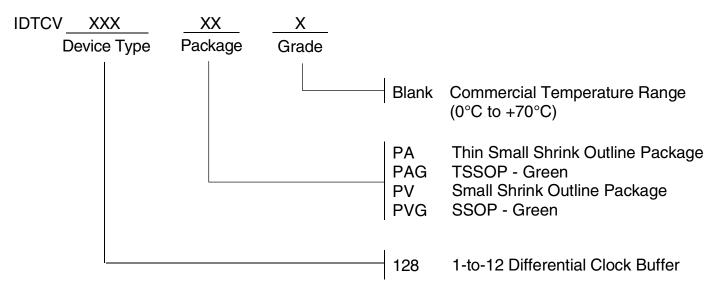

### **ORDERING INFORMATION**

# **Revision History**

| Rev. | Issue Date | Description       | Page # |

|------|------------|-------------------|--------|

| Α    | 06/29/07   | Release to Final. | -      |

|      |            |                   |        |

|      |            |                   |        |

|      |            |                   |        |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.