# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010

**Renesas Electronics Corporation**

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment, and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

To all our customers

# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

MITSUBISHI (DIGITAL ASSP)

### SERIAL BUS CONTROLLER

#### DESCRIPTION

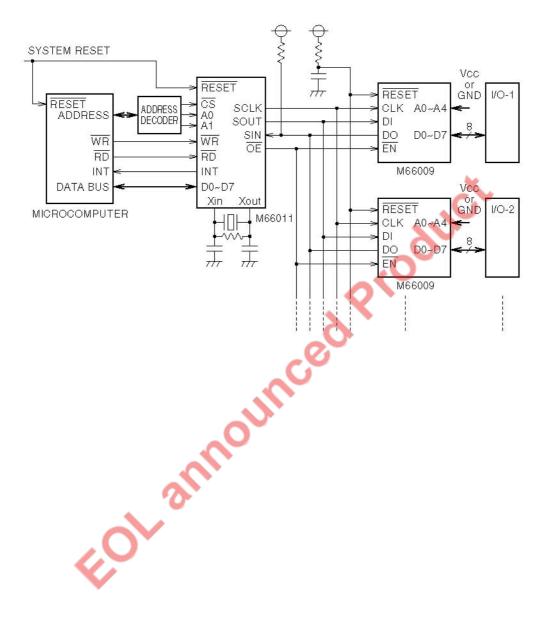

M66011 Semiconductor Integrated Circuit is a serial bus controller. It converts 2-byte parallel data that arrives from microcomputer into serial and outputs it to serial bus. It also converts serial data input from serial bus into parallel and outputs it to microcomputer.

The M66011 is used for the extension of microcomputer I/O ports and two-way communication with peripheral equipment connected with serial buses.

#### FEATURES

- Compatible with general-purpose 8-bit microprocessor busses

- TTL level input (one microcomputer side)

- Interrupt output

- Schmitt input (RESET, CS, SIN)

- Low power dissipation

- Wide operating temperature range (Ta = -20 to 75°C)

#### **APPLICATION**

Microcomputer I/O port extension, etc.

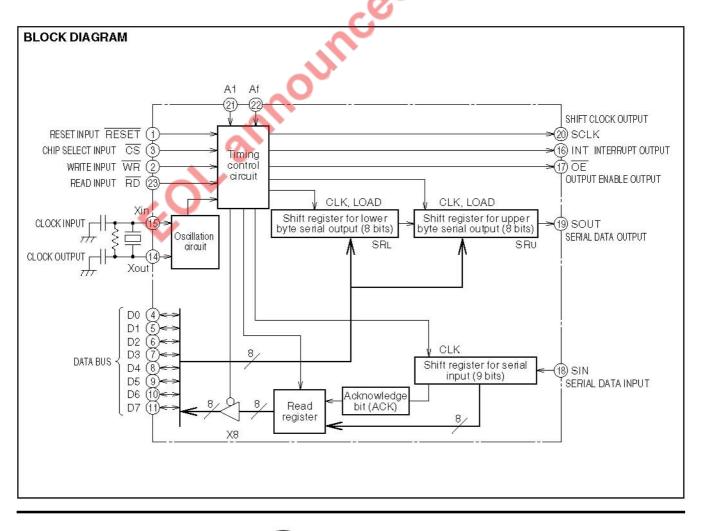

### FUNCTION

M66011 integrated circuit is a serial bus controller. It is equipped with two 8-bit shift registers used to convert parallel input data into serial for output, as well as with one 9-bit shift register used to convert serial input data into parallel for output.

This IC receives and sends 8-bit parallel in communication with microcomputer. In communication with serial bus, it outputs 16-bit data and receives 9-bit data.

Serial data input/output uses four signal lines: shift clock output SCLK, serial data output SOUT, serial data input SIN and output enable output  $\overline{\text{OE}}$ .

Serial data is output synchronously with shift clock fall edges, while input of serial data is synchronous with shift clock rise edges.

Serial communication data consists of one prefixed acknowledge bit and 8 data bits.

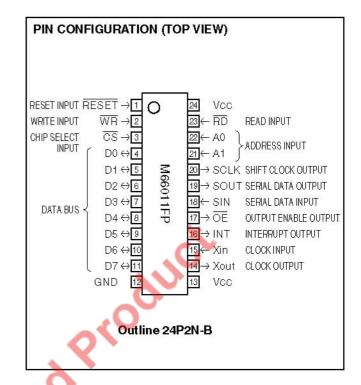

#### **PIN DESCRIPTIONS**

| Pin       | Name                 | Input/Output | Functions 🦢                                                                                                        |  |  |  |

|-----------|----------------------|--------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| RESET     | Reset input          | Input        | "L" level: M66011 is reset to initial state.                                                                       |  |  |  |

| <u>cs</u> | Chip select input    | Input        | "L" level: M66011 becomes accessible.                                                                              |  |  |  |

| WR        | Write input          | Input        | "L" level: 8-bit parallel data is input from data bus and written on M66011.                                       |  |  |  |

| RD        | Read input           | Input        | "L" level: Serial-input 8-bit data or internal status data is output in parallel to<br>data bus.                   |  |  |  |

| D0~D7     | Data bus             | Input/Output | Bi-directional 8-bit bus buffer. Used for communication with microcomputer (data write and read).                  |  |  |  |

| SCLK      | Shift clock output   | Output       | Outputs clock to serial bus. Active ("H") status normally.                                                         |  |  |  |

| SOUT      | Serial date output   | Output       | Outputs serial data to serial bus. Active ("H") status normally.                                                   |  |  |  |

| SIN       | Serial data input    | Input        | Inputs serial data from serial bus.                                                                                |  |  |  |

| ŌĒ        | Output enable output | Output       | "L" when serial data communication is executed. Active ("H") otherwise.                                            |  |  |  |

| INT       | Interrupt output     | Output       | Outputs interrupt command signal to microcomputer when serial data communication is finished.                      |  |  |  |

| A0, A1    | Address input        | Input        | Selects register on which data is written during write operation. Designate data to be read during read operation. |  |  |  |

| Xin       | Clock input          | Input        | Connected to ceramic resonator, generates M66011 activation clock and                                              |  |  |  |

| Xout      | Clock output         | Output       | SCLK output clock.<br>If clock is input from outside, use pin Xin and keep pin Xout open.                          |  |  |  |

| Vcc       | Positive supply pin  |              | Connected positive supply (5V).                                                                                    |  |  |  |

| GND       | Grounding pin        |              | Used for grounding (0V).                                                                                           |  |  |  |

| Vcc       | Positive supply pin  | 26           | Connected positive supply (5V).                                                                                    |  |  |  |

## OPERATION

1. Write operation

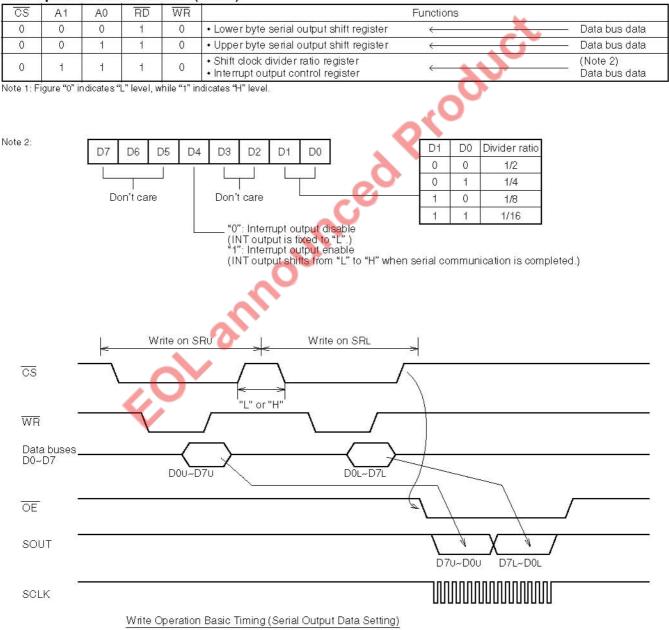

(1) Serial output data setting

The M66011 has two built-in 8-bit shift registers. They are used to set serial output data.

When the address setting is (A1, A0) = (0, 1), 8-bit data on data bus is written on the upper byte serial output shift register (SRU). When the address setting is (A1, A0) = (0, 0),

the data is written on the lower byte serial output shift register (SRL). In either case, data write starts when  $\overline{WR}$  is on the "L" level.

#### (2) Status register setting

When the address setting is (A1, A0) = (1, 1), written data becomes the setting of status register in M66011. (Refer to the table below.)

### Write Operation Basic Functions (Note 1)

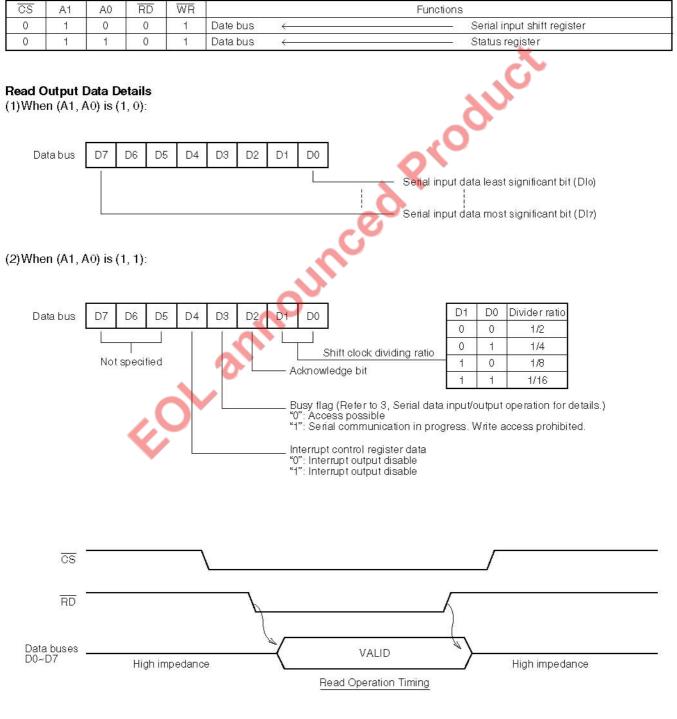

2. Read operation

When a read access arrives, M66011 outputs data in parallel to data bus. The data output at this moment may be serial input data, or data on internal status resister. When a read access arrives when the address setting is (A1, A0) = (1, 0), 8-bits of 9-bit serial input data, excluding the acknowledge bit, is output to data bus While  $\overline{RD}$  is "L". When a read access arrives when the address setting is (A1, A0) =(1, 1), interrupt control register, busy flag, serialinput acknowledge bit and clock dividing ratio register are output to data bus while  $\overline{RD}$  is "L".

#### **Read Operation Basic Function**

| 16T

DOO

(D0L)

DIo

D01

DI1

D02

DI2

D0:

DIs

3. Serial data input/output operation

SRL write operation

CS

Busy flag (in M66011)

OE

INT

SCLK

SOUT

SIN

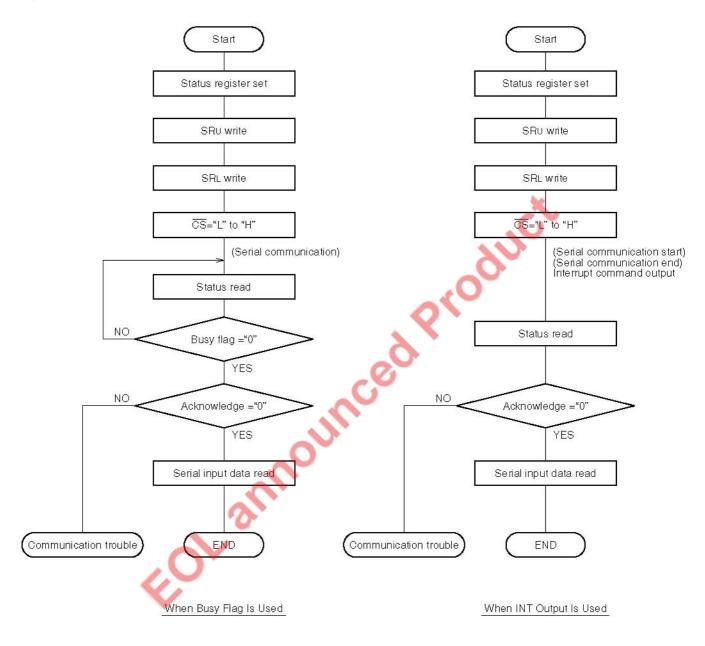

A cycle of 16-bit serial output data setting and serial data communication starts with a write access given by microcomputer to transmission shift registers in M66011.

M66011 has two 8-bit shift registers, on for upper byte (SRU), the other for lower byte (SRL). If the  $\overline{CS}$  status rises from "L" to "H" after a write access is given to SRL, serial data communication is started. SRU 8-bit data and SRL, 8-bit data are output in series in this order. Output of each data starts from its most significant bit.

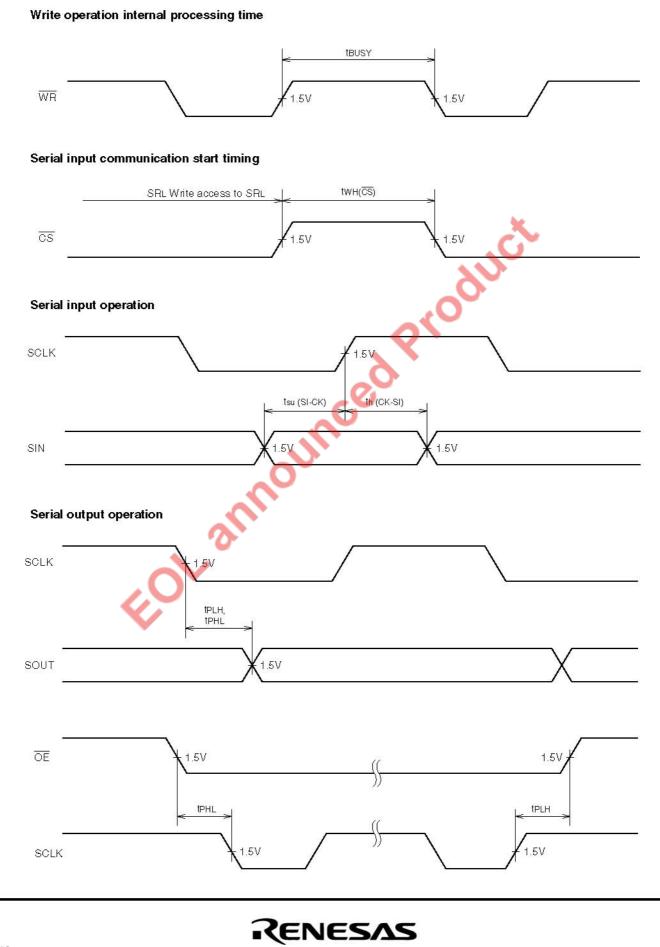

At the  $\overline{CS}$  rise edge, busy flag in M66011 is set, and  $\overline{OE}$  output shifts from "H" to "L". Shift clock SCLK and serial data SOUT are then output.

At SCLK fall edges, serial output shift register executes shifting operation, and data on shift register is output in series from pin SOUT. Serial input data from pin SIN is taken into input shift register at SCLK 8T thru 16T rise edges. However, data taken in at 8T rise edge is processed as acknowledge bit, while data taken in at 9T thru 16T rise edges are processed as data bits.

2T

D01

D015XD01

(D7u)

After the SCLK 16T rise edge, the status of SOUT and  $\overline{\text{OE}}$  shifts to "H" after one bit's delay of SCLK, and busy flag is reset. When interrupt output is being set to enable, INT output is set.

#### (Remarks)

- (1) If CS rises after write operation is executed on SRL only and not on SR∪, SR∪ data is unstable.

- (2) When write operations executed on SRL, M66011 becomes ready for start of serial communication and stands by for detection of CS rise. However, if a read access is given after data is written on SRL while CS is maintained on "L" level, this standby status is canceled. To resume serial communication in this case, rewrite data on SRL and raise CS.

ACK

8T

D09

D010

D01

DO8 X

(D0U) (D7L)

9T

D07

DI7

D06

DI6

D05

DI5

D0.

DI4

Serial communication period

4. Shift clock output

Shift clock output pin (SCLK) outputs clock pulses generated by ceramic resonator oscillation circuit connected between pins Xin and Xout, or divided clock pulses input via pin Xin from external clock. The dividing ratio can be selected from among 1/2, 1/4, 1/8 and 1/16.

5. Interrupt output

When interrupt output control register is set to "1" (interrupt output enable), the status of this output shifts from "L" to "H" at the end of a serial communication cycle, and an interrupt command is given to microcomputer. Interrupt output "H" is reset when read accessed.

When interrupt output control register is set to "0" (interrupt output disable), the status of this output is retained on the "L" level.

6. Conditions when reset

If "L" is input to RESET, M66011 are put under the conditions as specified below:

| Status                          | <i>.</i>                                                                    |

|---------------------------------|-----------------------------------------------------------------------------|

| Active ("H")                    |                                                                             |

| Reset ("L")                     | Murat                                                                       |

| Set ("H")                       | Mfg.                                                                        |

| Disable (continuous "L" output) | 0                                                                           |

| 1/2                             | 20                                                                          |

| alan                            |                                                                             |

|                                 | Active ("H")<br>Reset ("L")<br>Set ("H")<br>Disable (continuous "L" output) |

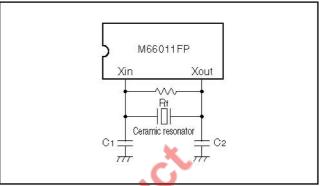

7. Oscillation circuit

An example of circuit connection and circuit constants are given below for the case where a ceramic resonator is used.

## **Clock Oscillation Circuit**

| Maker          | Ceramic<br>resonator | Frequency<br>(MHz) | C1<br>(pF)        | C2<br>(pF)        | Rf<br>(MΩ) |

|----------------|----------------------|--------------------|-------------------|-------------------|------------|

| Murata<br>Mfg. | CSA4.00 MG 040       | 4.0                | 100               | 100               | 1.0        |

|                | CST4.00 MGW 040      | 4.0                | 100<br>(built-in) | 100<br>(built-in) | 1.0        |

|                | CSA8.00 MT           | 8.0                | 30                | 30                | 1.0        |

|                | CSA8.00 MTW          | 8.0                | 30<br>(built-in)  | 30<br>(built-in)  | 1.0        |

## SERIAL BUS CONTROLLER

#### ABSOLUTE MAXIMUM RATINGS

| Symbol | Parameter           | Ratings          | Unit |

|--------|---------------------|------------------|------|

| Vcc    | supply voltage      | -0.5 ~ +7.0      | V    |

| VI     | Input voltage       | -0.5 ~ Vcc + 0.5 | V    |

| Vo     | Output voltage      | -0.5 ~ Vcc + 0.5 | V    |

| Pd     | Power dissipation   | 500              | mW   |

| Tstg   | Storage temperature | -60 ~ 150        | °C   |

#### **RECOMMENDED OPERATIONAL CONDITIONS**

| Symbol | Devementer            | Limits |           |     | Unit |  |

|--------|-----------------------|--------|-----------|-----|------|--|

| Symbol | Parameter –           |        | Min. Typ. |     | Unit |  |

| Vcc    | Supply voltage        | 4.5    | 5.0       | 5.5 | V    |  |

| VI     | Input voltage         | 0      |           | Vcc | V    |  |

| Vo     | Output voltage        | 0      |           | Vcc | V    |  |

| Topr   | Operating temperature | -20    |           | 75  | °C   |  |

## ELECTRICAL CHARACTERISTICS (Ta = -20 ~ 75°C, Vcc = 5V ± 10% and GND = 0V unless otherwise noted)

| Queshal | Parameter                           |                 | Test conditions         | Limits                                |      |         | Unit |

|---------|-------------------------------------|-----------------|-------------------------|---------------------------------------|------|---------|------|

| Symbol  | Parame                              | ler             | Test conditions         | Min.                                  | Тур. | Max.    | Unit |

| Vih     | "H" input voltage                   | WR, RD, A0, A1, |                         | 2.0                                   |      |         | V    |

| VIL     | "L" input voltage                   | D0~D7           |                         |                                       |      | 0.8     | V    |

| VIH     | "H" input voltage                   | Xin             | 0                       | VCC×0.8                               |      |         | V    |

| VIL     | "L" input voltage                   | /               |                         |                                       |      | VCC×0.2 | V    |

| VT+     | Positive threshold<br>voltage       |                 |                         |                                       |      | 2.4     | V    |

| VT-     | Negative threshold<br>voltage       | RESET, CS, SIN  |                         | 0.7                                   |      |         | V    |

| Vh      | Hysteresis width                    |                 |                         |                                       | 0.6  |         | V    |

| Voн     | "H" output voltage                  | D0~D7, SCLK,    | IOH=-4mA                | Vcc-0.8                               |      |         | V    |

| Vol     | "L" output voltage                  | INT, SOUT, OE   | IOL=4mA                 |                                       |      | 0.4     | V    |

| 11      | Input leak current 🛛 🏹              |                 | VI=0~VCC                |                                       |      | ±10     | μA   |

| loz     | Output leak current<br>in off state | D0~D7           | Vo=0~Vcc                |                                       |      | ±10     | μA   |

| lcc     | Quiescent supply current            |                 | VI=VCC, GND output open |                                       |      | 200     | μA   |

| CI/O    | Input/output pin capacitance        | D0~D7           |                         | · · · · · · · · · · · · · · · · · · · |      | 20      | pF   |

Note 3: Standard value measuring conditions: Ta = 25°C and Vcc =5V

SERIAL BUS CONTROLLER

| Course has l                        | Descenter                                             | Test conditions |        | Limits  |        |      |

|-------------------------------------|-------------------------------------------------------|-----------------|--------|---------|--------|------|

| Symbol                              | Parameter                                             |                 | Min.   | Тур.    | Max.   | Unit |

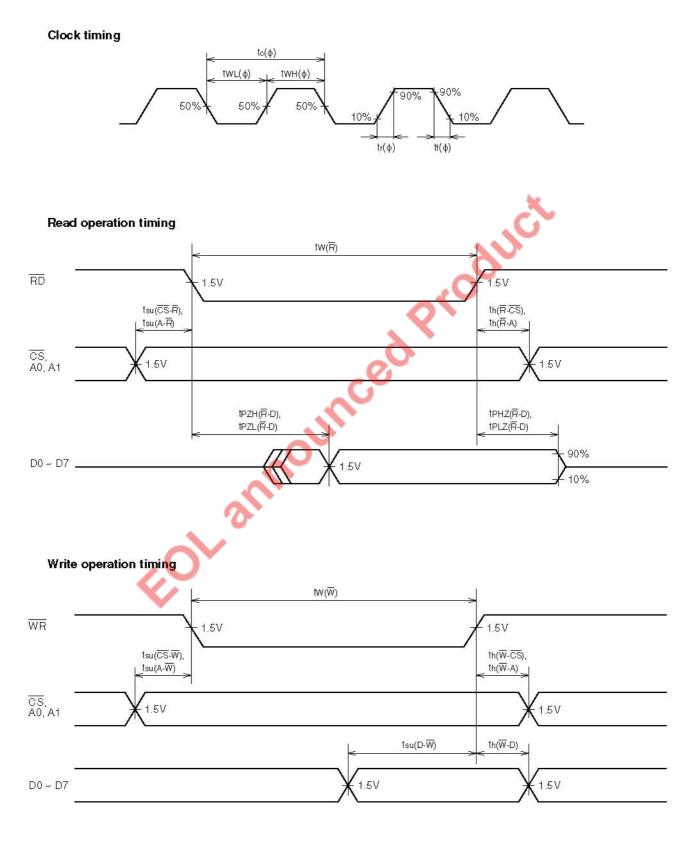

| tα(φ)                               | Clock cycle                                           |                 | 120    |         | 520    | ns   |

| tWH(φ)                              | Clock "H" pulse width                                 |                 |        | to(φ)/2 |        | ns   |

| tWL(q)                              | Clock "L" pulse width                                 |                 |        | to(φ)/2 |        | ns   |

| tr(φ)                               | Clock rise time                                       |                 |        |         | 20     | ns   |

| tf(φ)                               | Clock fall time                                       |                 |        |         | 20     | ns   |

| tw(R)                               | Read pulse width                                      |                 | 100    |         |        | ns   |

| tw(W)                               | Write pulse width                                     |                 | 100    |         |        | ns   |

| tsu( <del>CS</del> - <del>R</del> ) | Chip select setup time before read                    |                 | 0      |         |        | ns   |

| tsu(A- <del>R</del> )               | Address setup time before read                        |                 | 0      |         |        | ns   |

| tsu( <del>CS</del> -W)              | Chip select setup time before write                   |                 | 0      |         |        | ns   |

| tsu(A- <del>W</del> )               | Address setup time before write                       |                 | 0      |         |        | ns   |

| tsu(D-W)                            | Data setup time before write                          |                 | 40 🥖   |         |        | ns   |

| th(₩-CS)                            | Chip select hold time after read                      |                 | 0      |         |        | ns   |

| th(R-A)                             | Address hold time after read                          |                 | 0      |         |        | ns   |

| th(₩-CS)                            | Chip select hold time after write                     |                 | 0      |         |        | ns   |

| th(W-A)                             | Address hold time after write                         |                 | 0      |         |        | ns   |

| th(W-D)                             | Data hold time after write                            |                 | 0      |         |        | ns   |

| tsu(SI-CK)                          | Serial data setup time                                | 0               | 100    |         |        | ns   |

| th(CK-SI)                           | Serial data hold time                                 |                 | 100    |         |        | ns   |

| tBUSY                               | Internal processing time after write                  | A i             |        |         | 5to(q) | ns   |

| tWH(CS)                             | Chip select "H" time at serial communication start up |                 | 5to(ø) |         |        | Ins  |

## TIMING CONDITIONS (Ta = $-20 \sim 75^{\circ}$ C, Vcc = 5V ± 10%, GND = 0V)

## SWITCHING CHARACTERISTICS (Ta = $-20 \sim 75^{\circ}$ C, Vcc = 5V ± 10%, GND = 0V)

| Cirrente e l           | Deremet                     | Parameter Test conditions |                        | Unit     |                      |      |    |

|------------------------|-----------------------------|---------------------------|------------------------|----------|----------------------|------|----|

| Symbol                 | Parameter                   |                           | lest conditions        | Min.     | Тур.                 | Max. |    |

| tPZH(R-D)<br>tPZL(R-D) | Data output enable time aft | ter read                  |                        |          |                      | 80   | ns |

| tPHZ(R-D)<br>tPLZ(R-D) | Data output disable time af | ter read                  | CL=150pF               | 5        |                      | 50   | ns |

|                        | SCLK-S                      | SCLK-SOUT                 | - RL=2KΩ<br>- (Note 4) |          |                      | 60   | ns |

| tPLH, tPHL             | Serial output propagation   | OE-SCLK                   |                        | to(φ)+20 |                      |      | ns |

| IPCH, IPHL             | delay time                  |                           | ]                      |          | <u>n · to()</u><br>2 |      | ns |

n: Divider ratio

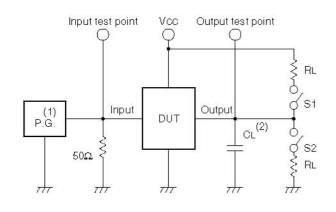

### NOTE 4: TEST CIRCUIT

| Symbol     | S1     | S2     |

|------------|--------|--------|

| tPZH(R-D)  | Open   | Closed |

| tPZL(R-D)  | Closed | Open   |

| tPHZ(R-D)  | Open   | Closed |

| tPLZ(R-D)  | Closed | Open   |

| tPLH, tPHL | Open   | Open   |

(1) Pulse generator (PG) characteristics: tr=tf=6ns, Z₀=50Ω

(2) Capacitance CL includes connection floating capacitance and probe input capacitance.

## TIMING CHARTS

SERIAL BUS CONTROLLER

SERIAL BUS CONTROLLER

#### **Operation Flow Chart**

SERIAL BUS CONTROLLER

### APPLICATION EXAMPLE