# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to <a href="http://www.renesas.com/inquiry">http://www.renesas.com/inquiry</a>.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# M66239FP

# High Speed Standard Clock Generator With Frequency Synthesizer

REJ03E0002-0100 Rev.1.00 Mar 16, 2005

#### **Description**

M66239FP is high speed synchronizing clock generator with frequency synthesizer which is fabricated by high performance silicon gate CMOS process technology.

It is able to output clock in sync with external trigger. And it features excellent synchronizing precision (sync accuracy: jitter) over a wide range frequency band.

Also, it has frequency synthesizer function which is able to modulate input frequency by resister setting before normal operation. Frequency modulation resolution is high accuracy 0.01%.

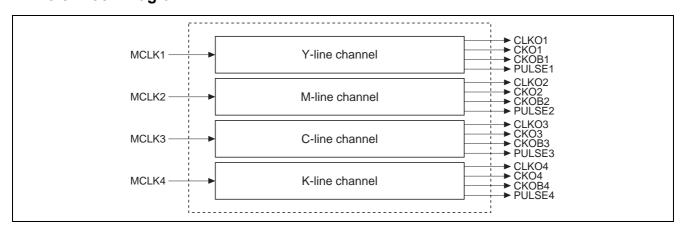

And in order to process the Y/M/C/K printing signal processing by 1 chip, M66239FP integrate fore synchronizing clock generator macro with frequency synthesizer function.

Also, this part can use various applications as frequency synthesizer LSI.

#### **Features**

- Power supply voltage: Single 3.3 V

- Frequency band: 28 MHz to 100 MHz

- Synchronizing precision (jitter):  $\Delta T = \pm 1.5$  ns

- Output clock type

- (1) Sync clock output (CKO)

- (2) Sync clock output inverted CKO (CKOB)

- (3) One-shot pulse output (PULSE)

- (4) Continuous clock output (CLKO: asynchronous to trigger)

- Trigger edge: Polarity (positive/negative) selectable

- Output clock phase control: T/8 step resolution (T: clock period)

- Frequency synthesizer type

- (1) Offset type modulation

- (2) Triangle type modulation

- (3) Polygon type modulation

- Frequency modulation resolution: 0.01%

- Output clock center frequency modulation: 0.01% step/Maximum ±2.55%

- Output clock peak frequency modulation: 0.01% step/Maximum ±2.55%

- Output clock modulation period: 16 bit resister setting

- Output clock modulation start position: 10 bit resister setting

- Output clock disable function: Disable CKOB and PULSE by OE pin control

- Integrated 4 synchronizing clock generator macro with frequency synthesizer function

#### **Application**

Digital color copier/Digital color laser beam printer

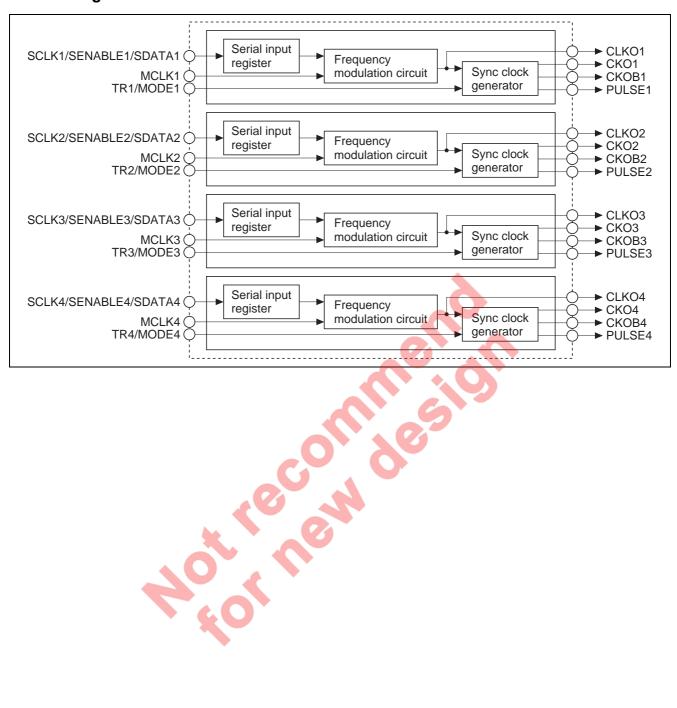

#### **Block Diagram**

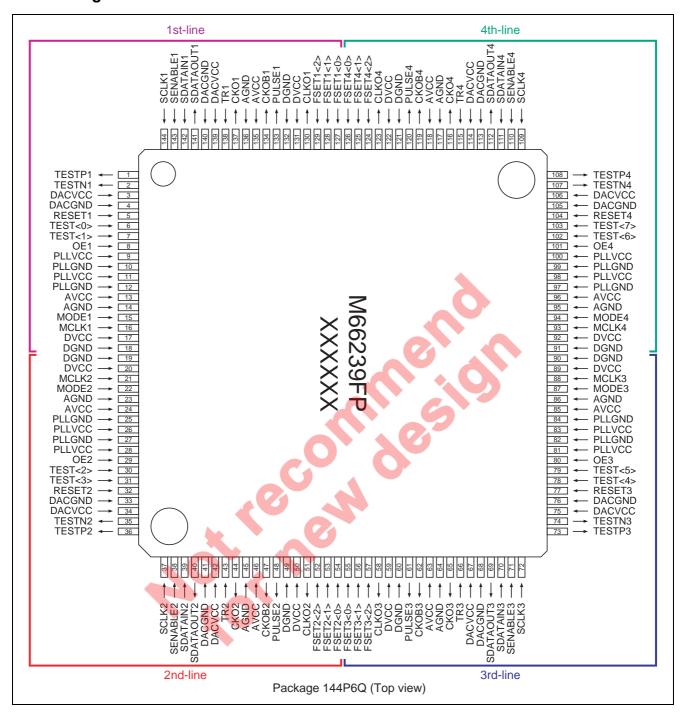

#### **Pin Configuration**

# **Pin Description**

| Pin Name   | I/O | Function                                                                               |

|------------|-----|----------------------------------------------------------------------------------------|

| MCLK       | I   | Input clock.                                                                           |

| SCLK       | Ι   | Serial resister clock input.                                                           |

| SENABLE    | Ι   | Serial resister enable input.                                                          |

|            |     | H level: disable, L level: enable                                                      |

| SDATAIN    | I   | Serial resister data input.                                                            |

| RESET      | I   | System reset input. When set to "L", system reset function.                            |

|            |     | Reset function initialize all resister data to the default settings.                   |

| FSET<2:0>  | I   | Frequency range settings correspond to MCLK frequency.                                 |

| MODE       | I   | Trigger edge polarity (positive/negative) select.                                      |

|            |     | H level: negative edge mode, L level: positive edge mode                               |

| TR         | I   | Trigger input for clock outputs.                                                       |

| CLKO       | 0   | Continuous clock output. CLKO is asynchronous clock output to trigger.                 |

| СКО        | 0   | Sync. clock output. Synchronized with trigger signal.                                  |

| CKOB       | 0   | Sync. clock output. Synchronized with trigger signal.                                  |

|            |     | CKOB is inverted clock of CKO.                                                         |

| PULSE      | 0   | Sync. clock output. Synchronized with trigger signal.                                  |

|            |     | PULSE is one-shot pulse synchronized with CKO.                                         |

| SDATAOUT   | 0   | Serial resister data output.                                                           |

| OE         | I   | Output enable control.                                                                 |

|            |     | H level: CKOB and PULSE will be disabled.  L level: All clock outputs will be enabled. |

| TEST<7:0>  | ı   | Test control input. Set to "L".                                                        |

| TESTP<4:1> | 0   | Test control input. Set to L.  Test control input. Set to open.                        |

| TESTP<4.1> |     | rest control input. Set to open.                                                       |

| DVCC       | 1   | Digital block VDD and GND.                                                             |

| DGND       |     |                                                                                        |

| AVCC       | I   | Analog block VDD and GND.                                                              |

| AGND       |     |                                                                                        |

| PLL VCC    | I   | PLL block VDD and GND.                                                                 |

| PLL GND    |     |                                                                                        |

| DAC VCC    | I   | DA converter VDD and GND.                                                              |

| DAC GND    |     |                                                                                        |

# **Whole Block Diagram**

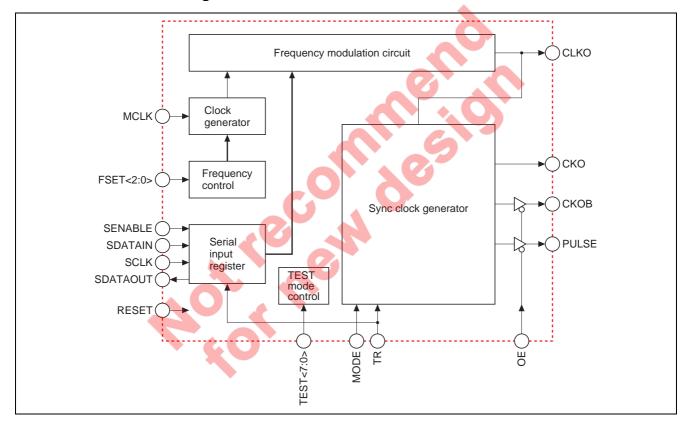

# **Unit Channel Block Diagram**

### **Function Summary**

#### **Sync Clock Generation Function**

M66239FP has standard clock generator function, it is able to output clock in sync with external trigger TR. And it features excellent synchronizing precision (sync accuracy: jitter) over a wide range frequency band.

Sync clock output timing is determined by trigger input signal edge. Trigger edge polarity (positive/negative) is selectable by MODE input.

Time-lag between trigger input signal edge and sync clock output equals the sum of clock input signal "L" pulse width and M66239FP internal delay.

Variation in this lag ( $\Delta t$ ) is  $\pm 1.5$ ns, ensuring excellent synchronizing accuracy.

There are three types of outputs: synchronous clock output (CKO), synchronous clock inverted output (CKOB), and one-shot pulse output (PULSE).

Synchronous clock output CKO is the same frequency as clock input signal MCLK. Synchronous clock inverted output CKOB is inverted signal of sync clock CKO. PULSE is one-shot pulse output which is almost equal to two cycles. All three sync outputs are suspended when trigger input signal is on "H" level when MODE is "H", and "L" level when MODE is "L" level. During these period, CKO and PULSE stay on "L" level, CKOB stay on "H" level.

Also, start phase of 3 sync. clocks are controlled by T/8 steps (T: Clock Period).

T/8 steps resolution is controlled by serial resister setting.

M66239FP integrate four synchronizing clock generator macro with frequency synthesizer function.

#### **Frequency Modulation Function**

M66239FP is able to modulate sync. clock frequency.

Frequency modulation profile is controlled by serial resister. Serial resister is controlled by serial input clock (SCLK), serial input enable (SENABLE) and serial input data (SDATAIN).

When SENABLE is "L" level, SDATAIN is able to write to serial input resister by SCLK. SDATAIN is composed by 4 bit address + 3 bit W/R distinction + 16 bit resister data.

After write operation completed, it can be able to confirm the resister status using read operation to serial input resister.

Resister setting is as follows.

| (1)  | Operation mode                               | : Resister 1  |

|------|----------------------------------------------|---------------|

| (2)  | Frequency modulation period (Trate)          | : Resister 2  |

| (3)  | Frequency modulation start position (Tstart) | : Resister 3  |

| (4)  | Output center frequency (fcenter)            | : Resister 4  |

| (5)  | Output peak frequency (fpeak)                | : Resister 5  |

| (6)  | 1st.pole position (1stPole)                  | : Resister 6  |

| (7)  | 2nd.pole position (2ndPole)                  | : Resister 7  |

| (8)  | 3rd.pole position (3rdPole)                  | : Resister 8  |

| (9)  | 4th.pole position (4thPole)                  | : Resister 9  |

| (10) | 1st.Pole frequency (f1stPole)                | : Resister 10 |

| (11) | 3rd.Pole frequency (f3rdPole)                | : Resister 11 |

There are four operation modes, center frequency offset type modulation (mode1), triangle type modulation (mode2 and 3), and polygon type modulation (mode4).

### **Sync. Clock Generation Operation Timing**

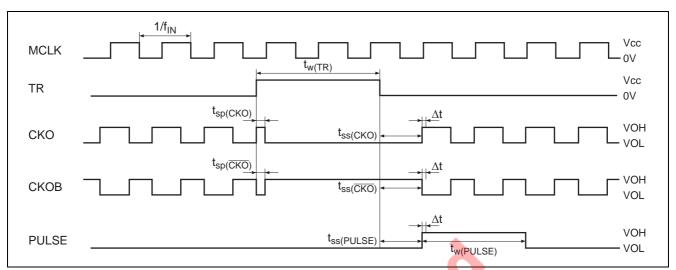

#### Trigger Mode 1 (Negative edge operation: MODE = "H")

Figure 1 Trigger Mode 1

#### Trigger Mode 2 (Positive edge operation: MODE = "L")

Figure 2 Trigger Mode 2

Notes: 1.  $t_{ss}$  (CKO, CKOB and PULSE) equals the sum of input clock "L" width and  $\alpha$ . Value  $\alpha$  refers to internal delay in M66239FP. Under environment where temperature and VCC do not change, value  $\alpha$  and  $t_{ss}$  are kept constant approximately. Dispersion of  $t_{ss}$  under such conditions is defined as  $\Delta t$  (synchronizing precision: jitter).

- 2. Outputs (CKO, CKOB and PULSE) are unknown until twice trigger pulse input TR reaches after power-on.

- 3. Internal trigger signal is generated by EXOR of TR and MODE signal.

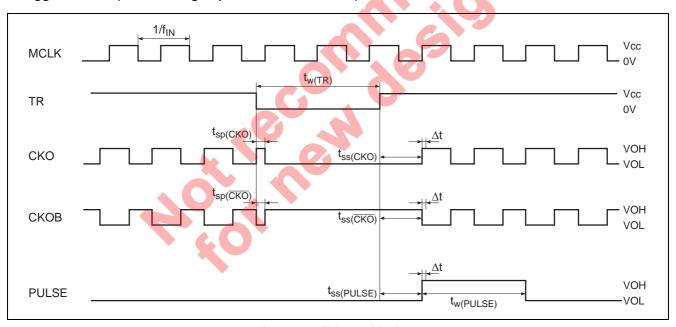

### Sync. Clock Phase Timing

M66239FP is able to control the phase of sync clock outputs (CKO, CKOB, PULSE) as each T/8 step. (T: clock period) This phase shift control is set up by serial input resister No. 13.

Also, 1st edge phase (= (1) position) of sync clock outputs is not shifted, and 2nd edge phase (= (2) position) of sync clock outputs is either not shifted position or resister set position, after 3rd edge phase (= (3) position) of sync clock outputs is shift as resister settings.

CLKO output can not use this phase shift function because CLKO is asynchronous clock output to trigger.

Figure 3 Sync. Clock Phase Timing

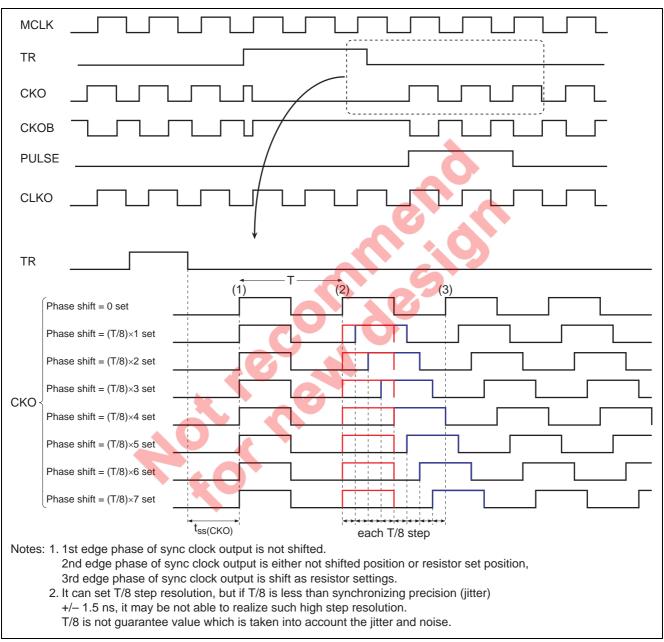

### **Frequency Modulation Operation Timing**

#### **Function Mode 1**

Mode 1 is frequency offset type modulation. Output clock frequency keep Fcenter-frequency.

Frequency modulation is set by serial input resister.

(1) Operation mode : Resister 1

(2) Frequency modulation start position (Tstart) : Resister 3

(3) Output center frequency (fcenter) : Resister 4

Figure 4 Operation Timing of Mode 1

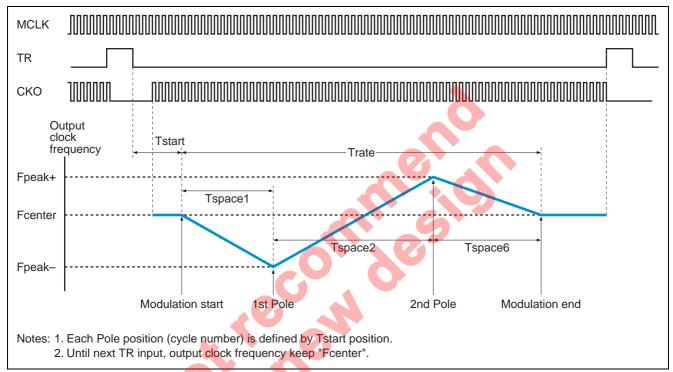

#### **Function Mode 2**

Mode 2 is triangle modulation type as following.

| (1) | Operation mode                               | : Resister 1 |

|-----|----------------------------------------------|--------------|

| (2) | Frequency modulation period (Trate)          | : Resister 2 |

| (3) | Frequency modulation start position (Tstart) | : Resister 3 |

| (4) | Output center frequency (fcenter)            | : Resister 4 |

| (5) | Output peak frequency (fpeak)                | : Resister 5 |

| (6) | 1st.pole position (1stPole)                  | : Resister 6 |

| (7) | 2nd.pole position (2ndPole)                  | : Resister 7 |

Figure 5 Operation Timing of Mode 2

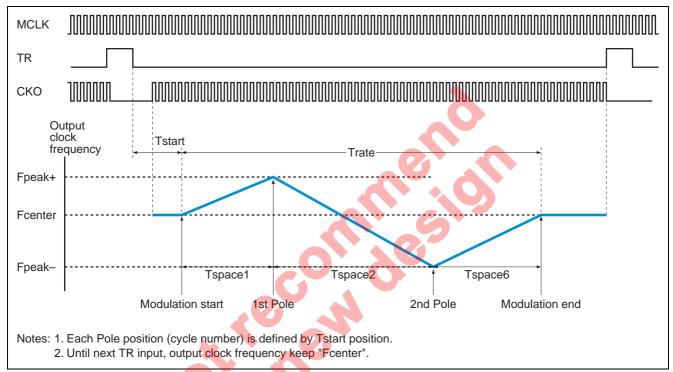

#### **Function Mode 3**

Mode 3 is triangle modulation type as following.

| (1) | Operation mode                               | : Resister 1 |

|-----|----------------------------------------------|--------------|

| (2) | Frequency modulation period (Trate)          | : Resister 2 |

| (3) | Frequency modulation start position (Tstart) | : Resister 3 |

| (4) | Output center frequency (fcenter)            | : Resister 4 |

| (5) | Output peak frequency (fpeak)                | : Resister 5 |

| (6) | 1st.pole position (1stPole)                  | : Resister 6 |

| (7) | 2nd.pole position (2ndPole)                  | : Resister 7 |

Figure 6 Operation Timing of Mode 3

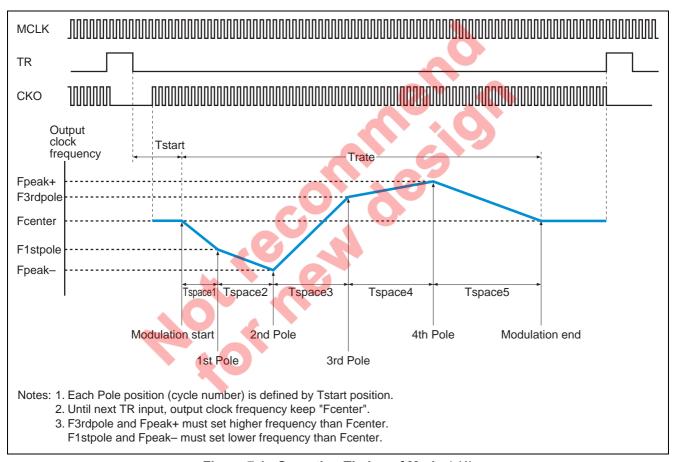

#### **Function Mode 4**

Mode 4 is polygon modulation type as following.

| (1)  | Operation mode                               | : Resister 1  |

|------|----------------------------------------------|---------------|

| (2)  | Frequency modulation period (Trate)          | : Resister 2  |

| (3)  | Frequency modulation start position (Tstart) | : Resister 3  |

| (4)  | Output center frequency (fcenter)            | : Resister 4  |

| (5)  | Output peak frequency (fpeak)                | : Resister 5  |

| (6)  | 1st.pole position (1stPole)                  | : Resister 6  |

| (7)  | 2nd.pole position (2ndPole)                  | : Resister 7  |

| (8)  | 3rd.pole position (3rdPole)                  | : Resister 8  |

| (9)  | 4th.pole position (4thPole)                  | : Resister 9  |

| (10) | 1st.Pole frequency (f1stPole)                | : Resister 10 |

| (11) | 3rd.Pole frequency (f3rdPole)                | : Resister 11 |

|      |                                              |               |

Figure 7.1 Operation Timing of Mode 4 (1)

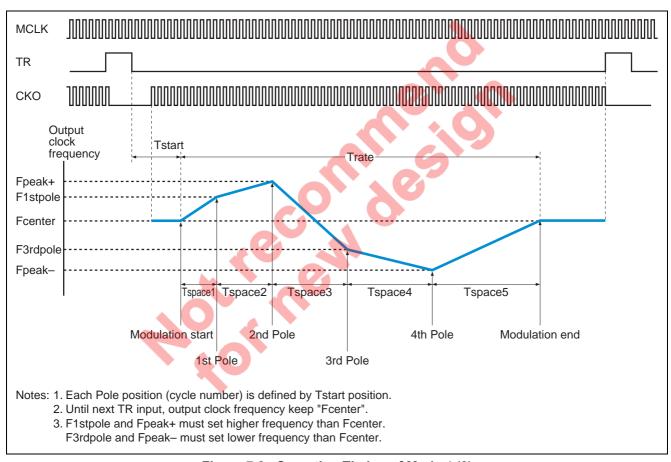

#### **Function Mode 4 (cont.)**

Mode 4 is polygon modulation type as following.

| (1)  | Operation mode                               | : Resister 1  |

|------|----------------------------------------------|---------------|

| (2)  | Frequency modulation period (Trate)          | : Resister 2  |

| (3)  | Frequency modulation start position (Tstart) | : Resister 3  |

| (4)  | Output center frequency (fcenter)            | : Resister 4  |

| (5)  | Output peak frequency (fpeak)                | : Resister 5  |

| (6)  | 1st.pole position (1stPole)                  | : Resister 6  |

| (7)  | 2nd.pole position (2ndPole)                  | : Resister 7  |

| (8)  | 3rd.pole position (3rdPole)                  | : Resister 8  |

| (9)  | 4th.pole position (4thPole)                  | : Resister 9  |

| (10) | 1st.Pole frequency (f1stPole)                | : Resister 10 |

| (11) | 3rd.Pole frequency (f3rdPole)                | : Resister 11 |

|      |                                              |               |

Figure 7.2 Operation Timing of Mode 4 (2)

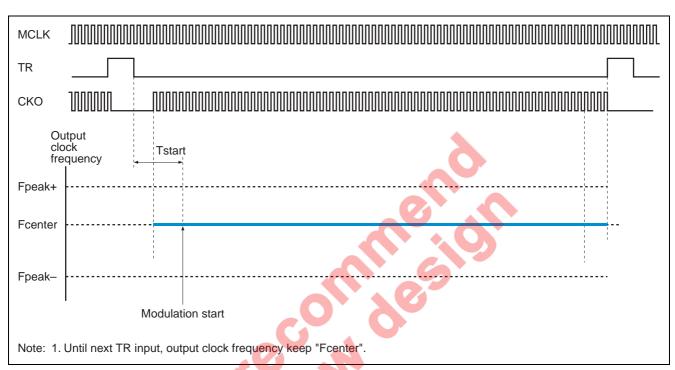

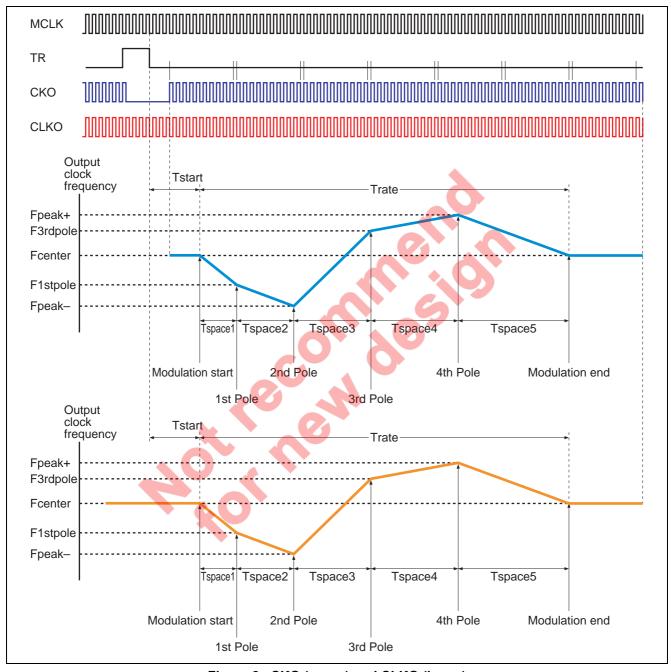

### **CLKO Operation Timing**

The CLKO output is the continuation clock output that frequency modulation is worked like CKO but to be in the asynchronous relation with TR. Of the operation timing specified in operation mode 4 in the figure below by it but the other operation mode is same.

Also, because CLKO is continuation clock output before synchronous clock generation circuit, phase relation during 4 channel is not guaranteed.

Figure 8 CKO (upper) and CLKO (lower)

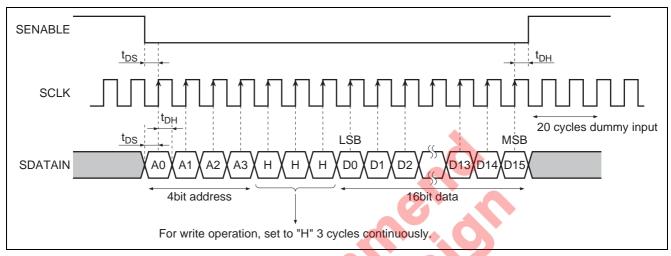

### **Frequency Modulation Resister Setting (Write Operation)**

#### **Write Operation**

Frequency modulation is set by serial input resister. Serial input resister is controlled by serial input clock (SCLK), serial input enable (SENABLE) and serial input data (SDATAIN).

When SENABLE is "L" level, SDATAIN is written to serial input resister by SCLK. SDATAIN is composed by 4 bit address + 3 bit W/R distinction data + 16 bit resister data.

After SENABLE change to "H", more than 20 dummy SLCK cycle is needed.

Figure 9 Frequency Modulation Resister Setting (Write Operation)

# **Frequency Modulation Resister**

| Resister    |                                   | Address | Bit    |            | Settir                                 | ng Rang            | je                      |          | Default                    | Value                               |                          |

|-------------|-----------------------------------|---------|--------|------------|----------------------------------------|--------------------|-------------------------|----------|----------------------------|-------------------------------------|--------------------------|

| Name        | Function                          | A3 A0   | Number |            | D15                                    |                    |                         | D15      |                            | D0                                  | Unit 1LSB                |

| Resister 1  | Operation                         | 0000    | 3 bit  | min        |                                        |                    | 000001                  |          |                            | 0001(1 dec)                         | _                        |

|             | mode                              |         |        | max        |                                        |                    | 000100                  |          | when 1 de                  |                                     |                          |

| Resister 2  | Modulation period                 | 0 0 0 1 | 16 bit | min<br>max |                                        |                    | 011100<br>111111        | 001000   | 0000000                    | 0000(8192 dec)                      | MCLK cycle               |

| Resister 3  | Modulation start position         | 0 0 1 0 | 10 bit | min<br>max |                                        |                    | 100100<br>111111        | 000000   | 010000                     | 0000(256 dec)                       | MCLK cycle               |

| Resister 4  | Center<br>frequency               | 0 0 1 1 | 9 bit  | * -        |                                        | 00111<br>en min. v |                         | * 0% whe | en 256 dec<br>te to + side | more than 256 dec less than 256 dec | MCLK frequency<br>×0.01% |

| Resister 5  | Peak<br>frequency                 | 0 1 0 0 | 8 bit  | max<br>* ± | 00000<br>00000<br>0.30% wh<br>2.55% wh | 00011<br>en min. v | 111111<br>/alue         |          | 001111<br>when 255         | 1111(255 dec)<br>dec                | MCLK frequency<br>×0.01% |

| Resister 6  | 1st-pole position                 | 0 1 0 1 | 16 bit | min<br>max |                                        |                    | 110100<br>111111        | 000001   | 1001100                    | 0110(1638 dec)                      | MCLK cycle               |

| Resister 7  | 2nd-pole position                 | 0 1 1 0 | 16 bit | min<br>max | 00000                                  |                    | 110100<br>111111        | 000011   | 001100                     | 1100(3276 dec)                      | MCLK cycle               |

| Resister 8  | 3rd-pole position                 | 0 1 1 1 | 16 bit | min<br>max |                                        |                    | 110100<br>111111        | 000100   | 1100110                    | 0010(4914 dec)                      | MCLK cycle               |

| Resister 9  | 4th-pole position                 | 1000    | 16 bit | min<br>max |                                        |                    | 110100<br>111111        | 000110   | 011001                     | 1000(6552 dec)                      | MCLK cycle               |

| Resister 10 | 1st-pole<br>frequency<br>(Mode 4) | 1 0 0 1 | 9 bit  | * -        | 00000<br>00000<br>2.55% wh<br>2.55% wh | 00111<br>en min. v | /alue                   |          | 001000<br>when 128         | 0000(128 dec)                       | MCLK frequency<br>×0.01% |

| Resister 11 | 3rd-pole<br>frequency<br>(Mode 4) | 1010    | 9 bit  | * -        | 00000<br>00000<br>2.55% wh<br>2.55% wh | 00111<br>en min. v | /alue                   |          | 011000<br>when 384         | 0000(384 dec)<br>dec                | MCLK frequency<br>×0.01% |

| Resister 12 | Modulation resolution             | 1011    | 1 bit  | * ±        |                                        | 00000<br>ode when  |                         |          | 0000000<br>mode wher       | 0000(0 dec)<br>n 0 dec              | _                        |

| Resister 13 | Output phase control              | 1 1 0 0 | 3 bit  | max<br>* D |                                        | 00000<br>en min.   | 000000<br>000111<br>ax. |          | 0000000<br>when 0 de       | 0000(0 dec)<br>ec                   | T/8<br>(Clock cycle)     |

Notes: 1. Set to the following value for resister 1.

- For operation mode 1: "00000000000000001"

For operation mode 2: "000000000000000010"

- For operation mode 4: "0000000000000011"

For operation mode 4: "0000000000000010"

- 2. Resister 12 must not change.

- 3. Above table intend to setting available value of resister, practical limits are described in page 20.

- 4. Resister 13 is for phase control of sync clock output.

- 5. If the default value of above resister use, write operation to all resister must be done.

- 6. Resister 6 to 9 refer to following.

- 1st Pole = Tspace1

- 2nd Pole = Tspace1 + Tspace2

- 3rd Pole = Tspace1 + Tspace2 + Tspace3

- 4th Pole = Tspace1 + Tspace2 + Tspace3 + Tspace4

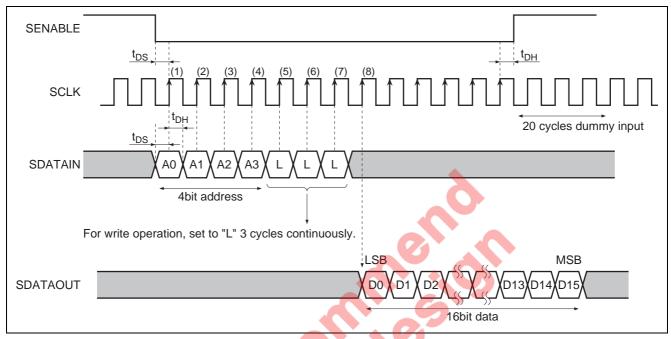

### **Frequency Modulation Resister Setting (Read Operation)**

#### **Read Operation**

After write operation completed, it can confirm the resister status using read operation to serial input resister.

When SENABLE is "L" level, SDATAIN is written to serial input resister by SCLK. SDATAIN is composed by 4 bit address + 3 bit W/R distinction data. After SENABLE change to "H", more than 20 dummy SLCK cycle is needed.

Figure 10 Frequency Modulation Resister Setting (Read Operation)

Notified

# **Absolute Maximum Ratings**

| Item                | Symbol | Ratings             | Unit | Conditions              |

|---------------------|--------|---------------------|------|-------------------------|

| Supply voltage      | Vcc    | -0.3 to +4.6        | V    |                         |

| Input voltage       | VI     | -0.3 to Vcc+0.3     | V    |                         |

| Output voltage      | Vo     | -0.3 to Vcc+0.3     | V    |                         |

| Storage temperature | Tstg   | -55 to +150         | °C   |                         |

| Power dissipation   | Pd     | 2500 * <sup>1</sup> | mW   | θja = 30°C/W, Ta = 50°C |

Note: 1. θja should be less than 30°C/W, Tjmax should be less than 125°C.

When  $\theta$ ja = 30°C/W and Tjmax is 125°C, Ta(max) will be 50°C.

PCB needs over 4 layers, over 100 mm  $\times$  100 mm size, over 70% Cu occupied ratio (average value of each layer) roughly.

Please contact to our sales division when you design PCB layout.

#### **Recommended Operating Conditions**

| Item                  | Symbol | Min  | Тур | Max  | Unit | Conditions |

|-----------------------|--------|------|-----|------|------|------------|

| Supply voltage        | Vcc    | 3.15 | 3.3 | 3.46 | V    |            |

| Supply voltage        | GND    | _    | 0   | _    | V    |            |

| Input voltage         | VI     | 0    | _   | Vcc  | V    |            |

| Output voltage        | Vo     | 0    | _   | Vcc  | V    |            |

| Operating temperature | Topr   | 0    | _   | 50   | °C   |            |

#### **DC Characteristics**

$(Ta = 0 \text{ to } +50^{\circ}\text{C}, \text{Vcc} = 3.15 \text{ to } 3.46\text{V}, \text{GND} = 0\text{V})$

| Item                    | Symbol          | Min      | Тур         | Max    | Unit     | Test Conditions                                          |

|-------------------------|-----------------|----------|-------------|--------|----------|----------------------------------------------------------|

| "H" input voltage       | $V_{IH}$        | 2.0      | <b>&gt;</b> | 1      | <b>V</b> |                                                          |

| "L" input voltage       | V <sub>IL</sub> | 4        | <b>/</b> –  | 0.8    | V        |                                                          |

| "H" output voltage      | V <sub>OH</sub> | 2.4      | -(-         | $\sim$ | V        | $I_{OH} = -4 \text{ mA}$                                 |

| "L" output voltage      | V <sub>OL</sub> | <u> </u> | A           | 0.4    | V        | I <sub>OH</sub> = 4 mA                                   |

| Supply current (static) | Icc (s)         | _        | 55          | 100    | mA       | V <sub>I</sub> = Vcc or GND                              |

| Supply current (active) | Icc (a)         | -        | 480         | 700    | mA       | f <sub>MCLK</sub> = 100 MHz, f <sub>SCLK</sub> = 20 MHz, |

|                         |                 |          |             |        |          | $C_L = 10 \text{ pF, OE} = L$                            |

|                         | > C             |          | 440         | _      |          | $f_{MCLK}$ = 80 MHz, $f_{SCLK}$ = 20 MHz,                |

|                         |                 |          |             |        |          | $C_L = 10 \text{ pF, OE} = L$                            |

|                         | · ·             | _        | 350         | _      |          | f <sub>MCLK</sub> = 40 MHz, f <sub>SCLK</sub> = 20 MHz,  |

|                         |                 |          |             |        |          | $C_L = 10 \text{ pF}, OE = L$                            |

|                         |                 | _        | 250         | _      |          | $f_{MCLK} = 20 \text{ MHz}, f_{SCLK} = 20 \text{ MHz},$  |

|                         |                 |          |             |        |          | $C_L = 10 \text{ pF}, OE = L$                            |

| "H" input current       | I <sub>IH</sub> |          | _           | 10     | μΑ       | V <sub>I</sub> = Vcc                                     |

| "L" input current       | I <sub>IL</sub> |          | _           | -10    | μΑ       | V <sub>I</sub> = GND                                     |

| Input capacitance       | Cı              | _        | _           | 10     | рF       |                                                          |

Note: The direction of current flowing to the circuit is specified to be positive. (No sign)

# **Timing Requirements**

$(Ta = 0 \text{ to } +50^{\circ}\text{C}, Vcc = 3.15 \text{ to } 3.46\text{V}, GND = 0\text{V})$

| Item                             | Symbol                | Min | Тур | Max | Unit | Test Conditions        |

|----------------------------------|-----------------------|-----|-----|-----|------|------------------------|

| MCLK frequency                   | f <sub>MCLK</sub>     | 28  | _   | 100 | MHz  | C <sub>L</sub> = 10 pF |

| MCLK and SCLK clock duty         | f <sub>DUTY</sub>     | 45  | _   | 55  | %    |                        |

| TR input pulse width             | t <sub>w(TR)</sub>    | 500 | _   |     | ns   |                        |

| MCLK and SCLK input rising time  | t <sub>r</sub>        | _   | _   | 5   | ns   |                        |

| MCLK and SCLK input falling time | t <sub>f</sub>        | _   | _   | 5   | ns   |                        |

| SDATA, SENABLE set-up time       | t <sub>DS</sub>       | 5   | _   | _   | ns   |                        |

| SDATA, SENABLE hold time         | t <sub>DH</sub>       | 5   | _   | _   | ns   |                        |

| SCLK frequency                   | f <sub>SCLK</sub>     | _   | _   | 20  | MHz  |                        |

| Internal PLL lock up time        | Tplllock              | _   | _   | 10  | ms   |                        |

| RESET pulse width                | t <sub>w(RESET)</sub> | 1   | _   | _   | μs   |                        |

# **Switching Characteristics**

$(Ta = 0 \text{ to } +50^{\circ}\text{C}, Vcc = 3.15 \text{ to } 3.46\text{V}, GND = 0\text{V})$

| Item                               | Symbol                    | Min                  | Тур | Max                  | Unit | Test Conditions        |

|------------------------------------|---------------------------|----------------------|-----|----------------------|------|------------------------|

| Synchronizing precision (jitter)   | Δt                        | _                    |     | ±1.5                 | ns   | C <sub>L</sub> = 10 pF |

| Sync. clock CKO output start time  | t <sub>ss(CKO)</sub>      | 7                    | 9   | t <sub>∟p</sub> +50  | ns   |                        |

| Sync. clock CKOB output start time | t <sub>ss(CKOB)</sub>     |                      |     |                      |      |                        |

| One-shot pulse output start time   | t <sub>ss(PULSE)</sub>    | 1                    | _   | t <sub>Lp</sub> +50  | ns   |                        |

| Sync clock CKO output stop time    | t <sub>sp(CKO)</sub>      | ·                    |     | 40                   | ns   |                        |

| Sync. clock CKOB output stop time  | t <sub>sp(CKOB)</sub>     |                      |     |                      |      |                        |

| One-shot pulse width               | t <sub>w(PULSE)</sub>     | 2 t <sub>p</sub> -10 | _   | 2 t <sub>p</sub> +10 | ns   |                        |

| Sync. clock CKO output duty        | f <sub>oDUTY(CKO)</sub>   | 40                   |     | 60                   | %    |                        |

| Sync. clock CKOB output duty       | f <sub>oDUTY</sub> (CKOB) |                      |     |                      |      |                        |

Notes: 1.  $t_p = 1/f_{IN}$ ,  $t_{Lp} = t_p \times (100 - f_{DUTY})/100$

2. Switching test waveform

Input pulse level MCLK: 0 to Vcc, TR: 0 to Vcc

Input clock rising time: 3 ns

Input clock falling time: 3 ns

Criteria Voltage MCLK: Vcc/2, TR: 1.3 V, Sync. clock: Vcc/2

### **Frequency Modulation Characteristics**

$(Ta = 0 \text{ to } +50^{\circ}\text{C}, Vcc = 3.15 \text{ to } 3.46\text{V}, GND = 0\text{V})$

| Item                                     | Symbol   | Min         | Тур                 | Max        | Unit  | Test Conditions        |

|------------------------------------------|----------|-------------|---------------------|------------|-------|------------------------|

| Frequency modulation start position      | Tstart   | 100         | 256                 | 1023       | Cycle | C <sub>L</sub> = 10 pF |

| Frequency modulation period              | Trate    | 1500        | 8192                | 65535      | Cycle |                        |

| Center frequency                         | Fcenter  | ±0          | _                   | ±2.55      | %     |                        |

| Center frequency resolution              | Fstep1   | 0.01        | _                   |            | %     |                        |

| Peak frequency (+ side)                  | Fpeak+   | +0.3        | _                   | +2.55      | %     |                        |

| Peak frequency (– side)                  | Fpeak-   | -0.3        | _                   | -2.55      | %     |                        |

| Peak frequency resolution                | Fstep2   | 0.01        | _                   |            | %     |                        |

| 1st.pole position                        | 1stPole  | Tstart+500  | _                   | 40959      | Cycle |                        |

| 2nd.pole position                        | 2ndPole  | 1stPole+500 | _                   | 40959      | Cycle |                        |

| 3rd.pole position                        | 3rdPole  | 2ndPole+500 | _                   | 40959      | Cycle |                        |

| 4th.pole position                        | 4thPole  | 3rdPole+500 | _                   | 40959      | Cycle |                        |

| Min cycle between 1stPole and Tstart     | Tspace1  | 500         |                     |            | Cycle |                        |

| Min cycle between 2ndPole and 1stPole    | Tspace2  | 500         |                     |            | Cycle |                        |

| Min cycle between 3rdPole and 2ndPole    | Tspace3  | 500         | _                   |            | Cycle |                        |

| Min cycle between 4thPole and 3rdPole    | Tspace4  | 500         | _                   |            | Cycle |                        |

| Min cycle between modulation end-4thPole | Tspace5  | 500         |                     | _          | Cycle |                        |

| Min cycle between modulation end-2ndPole | Tspace6  | 500         |                     | 1          | %     |                        |

| (In case of mode 2 or mode 3)            |          |             |                     |            |       |                        |

| 1st.Pole frequency (In case of page 12)  | F1stpole | Fcenter-0.1 | <b>▶</b> — <b>♦</b> | -Fpeak+0.1 | %     |                        |

| 1st.Pole frequency (In case of page 13)  |          | Fcenter+0.1 | _                   | +Fpeak-0.1 | %     |                        |

| 3rd.Pole frequency (In case of page 12)  | F3rdpole | Fcenter+0.1 |                     | +Fpeak-0.1 | %     |                        |

| 3rd.Pole frequency (In case of page 13)  |          | Fcenter-0.1 |                     | -Fpeak+0.1 | %     |                        |

- Notes: 1. Regarding Fpeak+/–, F1stpole, F3rdpole higher frequency than Fcenter is specified to be positive (+ sign), lower frequency than Fcenter is specified to be negative (- sign).

- The above limitations of Fcenter, Fstep1, Fpeak+/-, Fstep2, F1stpole, F3rdpole, 1stPole, 2ndPole, 3rdPole, and 4thPole are setting available vale.

Actual output clock is affected PLL jitter, above limitations are not guarantee value which is taken into

- 3. Minimum specification of modulation period is 1500 cycles, operation mode 4 needs over 2500 cycles.

# Frequency Range Setting of Input Clock

account the jitter and noise.

FEST<2:0> pins need to set correspond to following table.

Table 1 Frequency Range Setting of Input Clock

| Input Clock Frequency (MHz) | FSET<2> | FSET<1> | FSET<0> |

|-----------------------------|---------|---------|---------|

| 28 to 60                    | Н       | L       | L       |

| 60 to 80                    | Н       | L       | Н       |

| 80 to 100                   | Н       | Н       | L       |

Notes: 1. If MCLK frequency change under operating, it should need to start power on procedure again.

2. If FSET<2:0> setting are changed, reset function is needed again.

By the reset operation, all serial resisters are set to default settings, so it should set serial resister again.

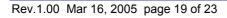

#### **After Power-On Procedure**

After power-on, M66239FP status is unknown. Following procedure must be done.

- 1. VCC power-on

- 2. After Vcc and input clock frequency is stable, set the FSET[2:0].

- 3. Reset pulse input.

Input more than MCLK 1000 clock cycle from FSET setting is completed to RESET set to "H" level.

- 4. Serial resister set.

- 5. After input MCLK clock till PLL lockup time (Tplllock), input twice TR pulse. Input more than 100 cycle MCLK clocks between 1st. TR and 2nd. TR.

- 6. After that, sync clock will be outputted from M66239FP.

Figure 11 After Power-On Procedure

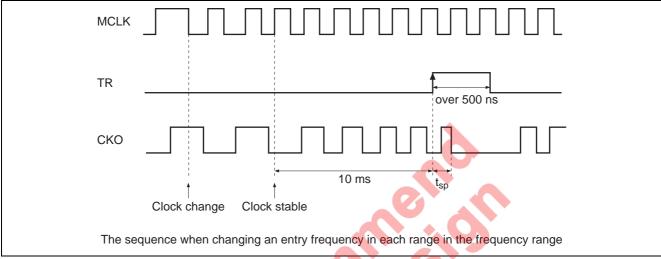

#### **Input Clock Change Sequence**

When changing the frequency of the input clock, if being the inside of each range in the frequency range which is specified in page 20, the change of the FSET is unnecessary but the lock of PLL sometimes comes when a frequency is changed even if it is the inside of each range in the frequency range. When the frequency of the input clock changes in each range in the frequency range and PLL comes off the lock condition, it adds that it takes time by locking 10 ms once again. To get a stable output clock, after passing in the PLL lock time in the frequency of input clock or it after phase change, enter TR signal. The output clock which was stable after entry is gotten in the TR signal. About the change of the frequency which exceeds the frequency range which is specified in page 20, for the purpose of FSET[2:0] to be changed, the sequence of power on must be done.

Figure 12 Input Clock Change Sequence

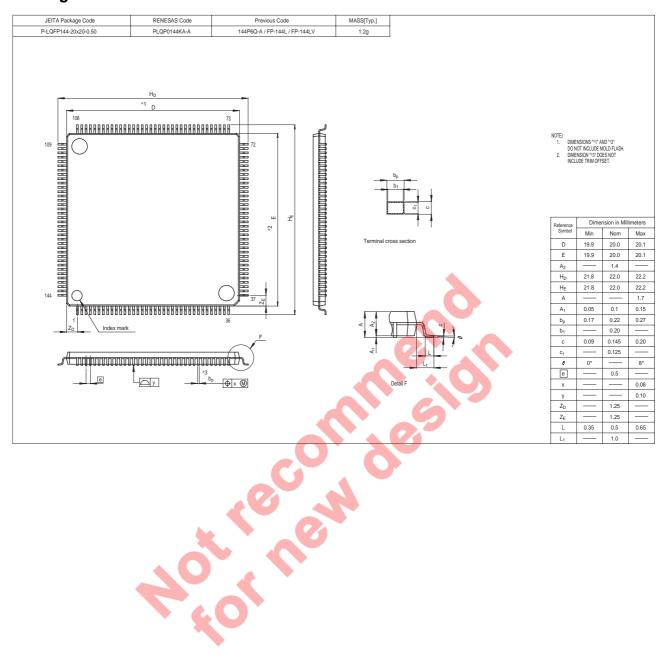

### **Package Dimensions**

Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Keep safety first in your circuit designs!

1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

- (ii) use of nontrammaple material of (iii) prevention against any maintention or misnap.

Notes regarding these materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained here

- use.

6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

# **CENESAS**

**RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology (Shanghai) Co., Ltd. Unit2607 Ruijing Building, No.205 Maoming Road (S), Shanghai 200020, China Tel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001