# SLG59M1456V

# Ultra-small 7.8 m $\Omega$ 5 A Load Switch with Discharge

#### **General Description**

The SLG59M1456V is a 7.8 m $\Omega$  5 A single-channel load switch that is able to switch 1 to 5 V power rails. The product is packaged in an ultra-small 1.5 x 2.0 mm package.

#### Features

- 1.5 x 2.0 mm FC-TDFN 8L package (2 fused pins for drain and 2 fused pins for source)

- Logic level ON pin capable of supporting 0.85 V CMOS Logic

- · User selectable ramp rate with external capacitor

- 7.8 m $\Omega$  RDS<sub>ON</sub>while supporting 5 A

- Discharges load when off

- Two Over Current Protection Modes

- Short Circuit Current Limit

- Active Current Limit

- Over Temperature Protection

- Pb-Free / Halogen-Free / RoHS compliant

- Operating Temperature: -20 °C to 70°C

- Operating Voltage: 2.5 V to 5.5 V

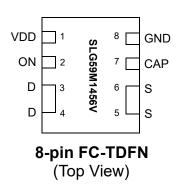

# **Pin Configuration**

#### Applications

- Notebook Power Rail Switching

- Tablet Power Rail Switching

- Smartphone Power Rail Switching

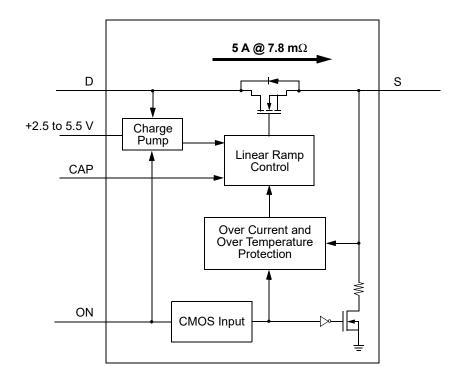

### **Block Diagram**

# **Pin Description**

| Pin # | Pin Name | Туре   | Pin Description                                                                                |

|-------|----------|--------|------------------------------------------------------------------------------------------------|

| 1     | VDD      | PWR    | VDD power for load switch control (2.5 V to 5.5 V)                                             |

| 2     | ON       | Input  | Turns MOSFET ON (4 M $\Omega$ pull down resistor)<br>CMOS input with VIL < 0.3 V, VIH > 0.85 V |

| 3     | D        | MOSFET | Drain of Power MOSFET (fused with pin 4)                                                       |

| 4     | D        | MOSFET | Drain of Power MOSFET (fused with pin 3)                                                       |

| 5     | S        | MOSFET | Source of Power MOSFET (fused with pin 6)                                                      |

| 6     | S        | MOSFET | Source of Power MOSFET (fused with pin 5)                                                      |

| 7     | CAP      | Input  | Capacitor for controlling power rail ramp rate                                                 |

| 8     | GND      | GND    | Ground                                                                                         |

# **Ordering Information**

| Part Number   | Туре                       | Production Flow             |  |  |

|---------------|----------------------------|-----------------------------|--|--|

| SLG59M1456V   | FC-TDFN 8L                 | Commercial, -20 °C to 70 °C |  |  |

| SLG59M1456VTR | FC-TDFN 8L (Tape and Reel) | Commercial, -20 °C to 70 °C |  |  |

# SLG59M1456V

## **Absolute Maximum Ratings**

| Parameter                                                                                                                                   | Description                       | Conditions                               | Min. | Тур. | Max. | Unit |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------|------|------|------|------|--|--|--|

| V <sub>DD</sub>                                                                                                                             | Power Supply                      |                                          |      |      | 7    | V    |  |  |  |

| Τ <sub>S</sub>                                                                                                                              | Storage Temperature               |                                          | -65  |      | 150  | °C   |  |  |  |

| ESD <sub>HBM</sub>                                                                                                                          | ESD Protection                    | Human Body Model                         | 2000 |      |      | V    |  |  |  |

| W <sub>DIS</sub>                                                                                                                            | Package Power Dissipation         |                                          |      |      | 1    | W    |  |  |  |

| MOSFET IDS <sub>PK</sub>                                                                                                                    | Peak Current from Drain to Source | For no more than 1 ms with 1% duty cycle |      |      | 7    | А    |  |  |  |

| Note: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating |                                   |                                          |      |      |      |      |  |  |  |

only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Electrical Characteristics**

$T_A$  = -20 to 70 °C (unless otherwise stated)

| Parameter              | Description                          | Conditions                                                                                       | Min.                      | Тур.        | Max.            | Unit |

|------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------|-------------|-----------------|------|

| V <sub>DD</sub>        | Power Supply Voltage                 | -20 to 70°C                                                                                      | 2.5                       |             | 5.5             | V    |

|                        | Dower Supply Current (DIN 1)         | when OFF                                                                                         |                           |             | 1               | μA   |

| I <sub>DD</sub>        | Power Supply Current (PIN 1)         | when ON, No load                                                                                 |                           | 70          | 100             | μA   |

| PDe                    | Static Drain to Source               | T <sub>A</sub> 25°C @ 100 mA                                                                     |                           | 7.8         | 8.5             | mΩ   |

| RDS <sub>ON</sub>      | ON Resistance                        | T <sub>A</sub> 70°C @ 100 mA                                                                     |                           | 8.5         | 9.6             | mΩ   |

| IDS                    | Operating Current                    | V <sub>D</sub> = 1.0 V to 5.5 V                                                                  |                           |             | 5               | А    |

| VD                     | Drain Voltage                        |                                                                                                  | 1.0                       |             | V <sub>DD</sub> | V    |

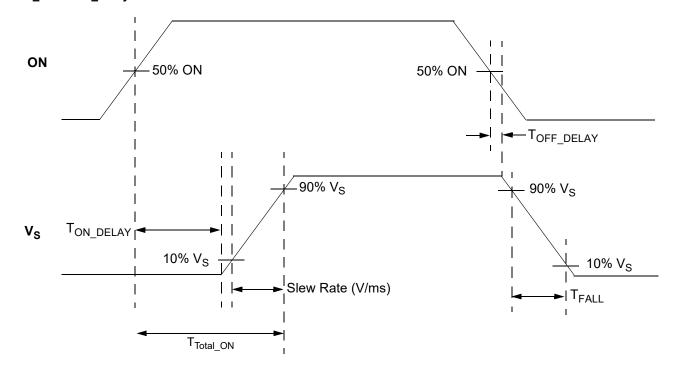

| T <sub>ON_Delay</sub>  | ON pin Delay Time                    | 50% ON to Ramp Begin                                                                             | 0                         | 300         | 500             | μs   |

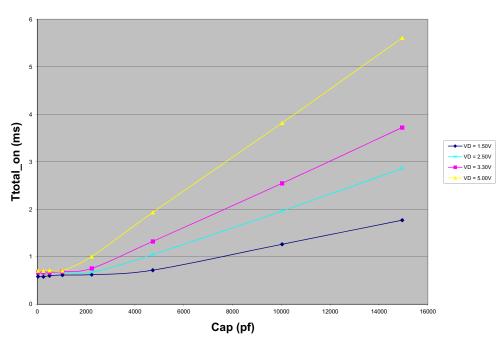

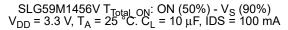

|                        |                                      | 50% ON to 90% V <sub>S</sub>                                                                     | Co                        | onfigurable | e <sup>1</sup>  | ms   |

| T <sub>Total_ON</sub>  | Total Turn On Time                   | Example: CAP (PIN 7) = 4 nF, $V_{DD}$<br>= $V_D$ = 5 V, Source_Cap = 10 $\mu$ F,<br>IDS = 100 mA |                           | 1.96        |                 | ms   |

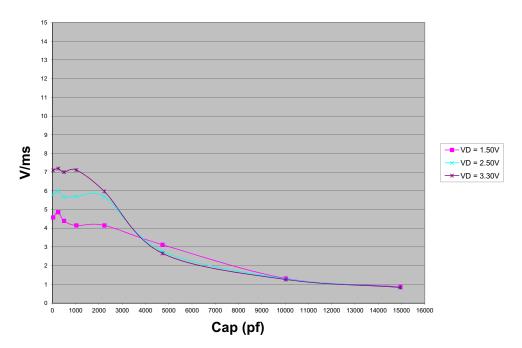

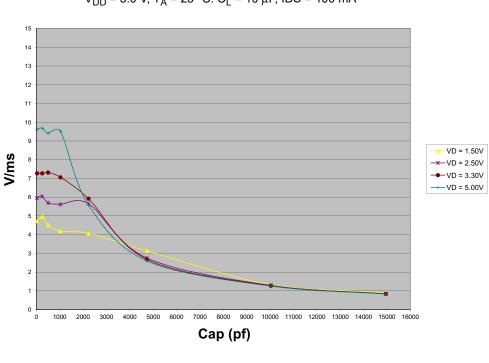

|                        |                                      | 10% $V_{\rm S}$ to 90% $V_{\rm S}$                                                               | Configurable <sup>1</sup> |             |                 | V/m  |

| T <sub>SLEWRATE</sub>  | Slew Rate                            | Example: CAP (PIN 7) = 4 nF, $V_{DD}$<br>= $V_D$ = 5 V, Source_Cap = 10 $\mu$ F,<br>IDS = 100 mA |                           | 3.0         |                 | V/ms |

| CAP <sub>SOURCE</sub>  | Source Cap                           | Source to GND                                                                                    |                           |             | 500             | μF   |

| R <sub>DIS</sub>       | Discharge Resistance                 |                                                                                                  | 100                       | 150         | 300             | Ω    |

| ON_V <sub>IH</sub>     | High Input Voltage on ON pin         |                                                                                                  | 0.85                      |             | V <sub>DD</sub> | V    |

| ON_V <sub>IL</sub>     | Low Input Voltage on ON pin          |                                                                                                  | -0.3                      | 0           | 0.3             | V    |

| 1                      | Active Current Limit                 | MOSFET will automatically limit current when $V_S > 250 \text{ mV}$                              |                           | 7.0         |                 | А    |

| I <sub>LIMIT</sub>     | Short Circuit Current Limit          | MOSFET will automatically limit current when $V_S < 250 \text{ mV}$                              |                           | 0.5         |                 | А    |

| THERMON                | Thermal shutoff turn-on temperature  |                                                                                                  |                           | 125         |                 | °C   |

| THERM <sub>OFF</sub>   | Thermal shutoff turn-off temperature |                                                                                                  |                           | 100         |                 | °C   |

| THERM <sub>TIME</sub>  | Thermal shutoff time                 |                                                                                                  |                           |             | 1               | ms   |

| T <sub>OFF_Delay</sub> | OFF Delay Time                       | 50% ON to V <sub>S</sub> Fall, V <sub>DD</sub> = V <sub>D</sub> = 5 V                            |                           |             | 15              | μs   |

| T <sub>FALL</sub>      | V <sub>S</sub> Fall Time             | 10% V <sub>S</sub> to 90% V <sub>S</sub> , V <sub>DD</sub> = V <sub>D</sub> = 5 V                |                           | TBD         |                 | μs   |

1. Refer to table for configuration details.

#### SLG59M1456V Turn ON

The normal power on sequence is first VDD, with VD only being applied after VDD is > 1 V, and then ON after VD is at least 90% of final value. The normal power off sequence is the power on sequence in reverse.

If VDD and VD are turned on at the same time then it is possible that a voltage glitch will appear on VS before VDD achieves 1 V which is the VT of the main MOSFET. The size of the glitch is dependent on source and drain capacitance loading and the ramp rate of VDD & VD.

#### SLG59M1456V Turn ON

The VS ramp follows a linear path, not an RC limitation provided the ramp is slow enough to not be current limited by load capacitance.

#### SLG59M1456V Current Limiting

The SLG59M1456V has two forms of current limiting.

#### 6 A Standard Current Limiting Mode

Current is measured by mirroring the current through the main MOSFET. The mirrored current is then sent through a resistor creating a voltage V(i) proportional to the MOSFET current. The V(i) is then compared with a Band Gap voltage V(BG). If V(i) exceeds the Band Gap voltage then the voltage V(g) on the gate of the main MOSFET is reduced. The V(g) continues to drop until V(i) < V(BG). This response is a closed loop response and is therefore very fast and current limits in less than a few micro-seconds. There is no difference between peak or constant current limit.

#### Temperature Cutoff

However, as the V(g) drops the Rds(ON) of the main MOSFET will increase, thus limiting the current, but also increasing the power dissipation of the IC. The IC is very small and cannot dissipate much power. Therefore, if a current limit condition is sustained the IC will heat up. If the temperature exceeds approximately 120°C, then V(g) will be brought low completely shutting off the main MOSFET. As the die cools the MOSFET will be turned back on at 100°C.

If the current limiting condition has not been mitigated then the die will again heat up to 120°C and the process will repeat.

#### Short Circuit Current Limiting Mode

When V(S) < 250 mV, which is the case if there is a solder bridge during the manufacturing process or a hard short on the power rail, then the current is limited to approximately 500 mA. This current limit is accomplished in the same manner as the Standard Current Limiting Mode with the exception that the current mirror is 15x greater. Because the current mirror is so much larger, a 15x smaller main MOSFET current is required to generate the same V(i). If V(S) rises above approximately 250 mV, then this mode is automatically switched out.

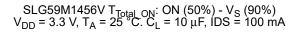

# $T_{Total ON}$ vs. CAP @ $V_{DD}$ = 3.3 V

# $T_{Total ON}$ vs. CAP @ $V_{DD}$ = 5.0 V

SLG59M1456V T<sub>Total\_ON</sub>: ON (50%) - V<sub>S</sub> (90%) V<sub>DD</sub> = 5.0 V, T<sub>A</sub> = 25 °C. C<sub>L</sub> = 10  $\mu$ F, IDS = 100 mA

# SLG59M1456V

# $T_{SLEW}$ vs. CAP @ $V_{DD}$ = 3.3 V

# $T_{SLEW}$ vs. CAP @ $V_{DD}$ = 5.0 V

SLG59M1456V T<sub>Total\_ON</sub>: ON (50%) - V<sub>S</sub> (90%) V<sub>DD</sub> = 5.0 V, T<sub>A</sub> = 25 °C. C<sub>L</sub> = 10  $\mu$ F, IDS = 100 mA

$T_{Total\_ON},\,T_{ON\_Delay}$  and Slew Rate Measurement

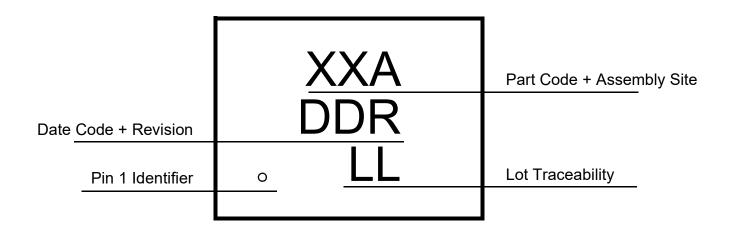

# Package Top Marking System Definition

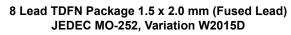

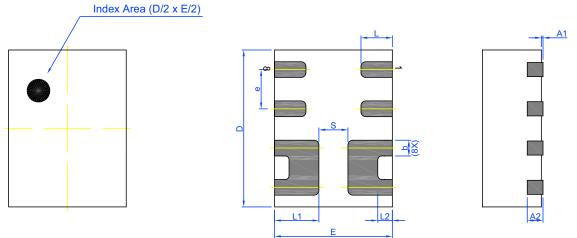

### **Package Drawing and Dimensions**

| Unit: mm |       |      |       |        |          |       |       |  |  |  |

|----------|-------|------|-------|--------|----------|-------|-------|--|--|--|

| Symbol   | Min   | Nom. | Max   | Symbol | Min      | Nom.  | Max   |  |  |  |

| Α        | 0.70  | 0.75 | 0.80  | L      | 0.35     | 0.40  | 0.45  |  |  |  |

| A1       | 0.005 | -    | 0.060 | L1     | 0.515    | 0.565 | 0.615 |  |  |  |

| A2       | 0.15  | 0.20 | 0.25  | L2     | 0.135    | 0.185 | 0.235 |  |  |  |

| b        | 0.15  | 0.20 | 0.25  | е      | 0.50 BSC |       |       |  |  |  |

| D        | 1.95  | 2.00 | 2.05  | S      | 0.37 REF |       |       |  |  |  |

| E        | 1.45  | 1.50 | 1.55  |        |          |       |       |  |  |  |

### **Tape and Reel Specifications**

| Package<br>Type     | # of<br>Pins | Nominal<br>Package Size<br>[mm] | Max Units |         | Reel &           | Leader (min) |                | Trailer (min) |                | Таре          | Part          |

|---------------------|--------------|---------------------------------|-----------|---------|------------------|--------------|----------------|---------------|----------------|---------------|---------------|

|                     |              |                                 | per Reel  | per Box | Hub Size<br>[mm] | Pockets      | Length<br>[mm] | Pockets       | Length<br>[mm] | Width<br>[mm] | Pitch<br>[mm] |

| TDFN 8L<br>FC Green | 8            | 1.5 x 2.0 x 0.75                | 3000      | 3000    | 178 / 60         | 100          | 400            | 100           | 400            | 8             | 4             |

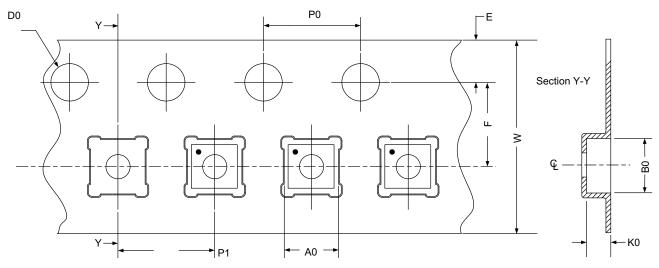

# **Carrier Tape Drawing and Dimensions**

| Package<br>Type     | PocketBTM<br>Length | PocketBTM<br>Width | Pocket<br>Depth | Index Hole<br>Pitch | Pocket<br>Pitch | Index Hole<br>Diameter | Index Hole<br>to Tape<br>Edge |     | Tape Width |

|---------------------|---------------------|--------------------|-----------------|---------------------|-----------------|------------------------|-------------------------------|-----|------------|

|                     | A0                  | В0                 | K0              | P0                  | P1              | D0                     | E                             | F   | W          |

| TDFN 8L<br>FC Green | 1.68                | 2.18               | 0.9             | 4                   | 4               | 1.5                    | 1.75                          | 3.5 | 8          |

Refer to EIA-481 specification

# **Recommended Reflow Soldering Profile**

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 2.25 mm<sup>3</sup> (nominal). More information can be found at www.jedec.org.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.