# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# MOS INTEGRATED CIRCUIT $\mu PD16447$

# 120-OUTPUT TFT LCD SOURCE DRIVER (NAVIGATION, AUTOMOBILE LCD-TV)

## **DESCRIPTION**

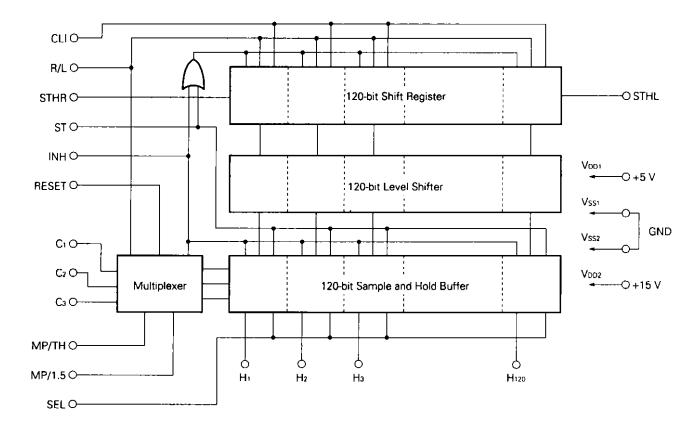

The  $\mu$ PD16447 is a TFT liquid crystal panel source driver. It consists of a multiplexer circuit that supports various pixel arrangements, a shift register generating sampling timing, and two sample and hold circuits that sample an analog voltage. The two sample and hold circuits alternately sample and hold an analog voltage, improving the definition on the LCD panel. Simultaneous sampling or sequential sampling mode can be automatically selected according to the pixel arrangement on the LCD panel used, so that the  $\mu$ PD16447 can be employed in a wide range of applications including navigation systems and automobile LCD-TVs.

## **FEATURES**

- Common inversion supported (maximum output voltage: 7.75 V, at VDD2 = 12 V)

- 5-V drive (supporting 882 × 240 dots)

fmax = 5 MHz, VDD1 = 4.5 V

- Simultaneous/sequential sampling mode automatically selected according to pixel arrangement (Vertical stripe mosaic arrangement; simultaneous, delta arrangement; sequential)

- Two sample and hold circuits

- Small output deviation between pins (±50 mV MAX.)

- Internal multiplexer supporting many pixel arrangements such as stripe, mosaic, and delta arrangements

- · Power-save circuit

- · R/L pin for left/right shift selection

- · For high-density mounting

## ORDERING INFORMATION

| Parts Number  | Package                   |

|---------------|---------------------------|

| μPD16447N-××× | TCP (TAB package)         |

| μPD16447N-051 | Standard TCP (200 μm OLB) |

The TCP model is a custom product. For details, consult NEC.

The information in this document is subject to change without notice.

# **BLOCK DIAGRAM**

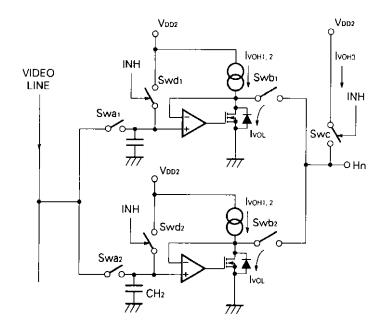

# SAMPLE AND HOLD, AND OUTPUT CIRCUITS

# **PIN FUNCTIONS**

| Pin Symbol                       | Pin Name                         | Description                                                                                                                                                                                                                                    |                                          |                                        |  |  |

|----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------|--|--|

| C <sub>1</sub> to C <sub>3</sub> | Video signal input               | These pins input video signals R, G,                                                                                                                                                                                                           | and B.                                   |                                        |  |  |

| H1 to H120                       | Video signal output              | These pins output video signals, which have been sampled and held, during the horizontal period.                                                                                                                                               |                                          |                                        |  |  |

| STHR<br>STHL                     | Cascade I/O                      | These pins input/output the start pulse for sample and hold timing. STHR serves as the input pin and STHL serves as the output pin for right shift. For left shift, STHL serves as the input pin and STHR serves as the output pin.            |                                          |                                        |  |  |

| SEL                              | Output hold current select input | This pin selects the high-level output signal (output hold current).  H; Ivon = -30 μA TYP.  SEL = L; Ivon = -8 μA TYP.                                                                                                                        | it current o                             | of the video                           |  |  |

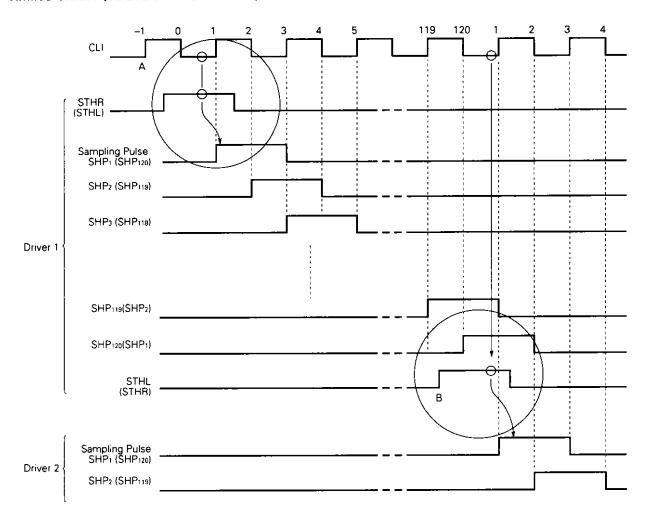

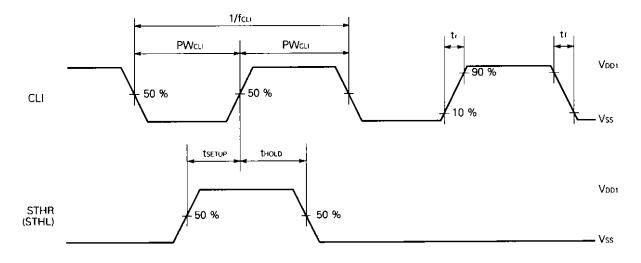

| CLI                              | Shift clock input                | The start pulse is read at rising edge sequential sampling mode, the sample generated at both the rising and fall signal. SPn is generated at either the of this signal in simultaneous sample refer to the TIMING CHART).                     | pling pulse<br>ling edges<br>ne rising o | e SPn is<br>of this<br>r falling edge  |  |  |

| INH                              | Inhibit input                    | When this signal goes high, the video signal output is made high, and the pixels in the LCD panel are precharged. When it goes low, multiplexer and two sample and hold circuits are switched.                                                 |                                          |                                        |  |  |

| RESET                            | Reset input                      | When this signal goes high, the sele multiplexer and the selectors of the circuits are reset.  The multiplexer is turned off once it Therefore, be sure to input one INH a video signal.  If a video signal is input without the not executed. | two samp<br>has been<br>pulse befo       | le and hold<br>reset.<br>ore inputting |  |  |

| ST                               | Power-save input                 | When this signal goes high, all outp<br>made high, reducing the bias curren<br>(during the vertical retrace line perio                                                                                                                         | nt of the ar                             |                                        |  |  |

| МР/ТН                            | Multiplexer selector input (1)   | By using MP/TH and MP/1.5 in combethree color filter arrangements can be a Mode Mosaic Arrangement Delta Arrangement                                                                                                                           |                                          |                                        |  |  |

| MP/1.5                           | Multiplexer selector input (2)   | With the vertical stripe or mosaic arreexecuted at the same time as video s With the delta arrangement, sampling executed. Do not select the combina MP/1.5 = H.                                                                               | signal inpu<br>g is seque                | t/output.<br>ntially                   |  |  |

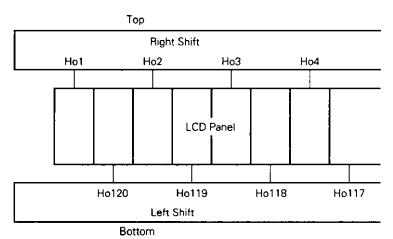

| R/L                              | Shift direction select input     | R/L = H; right shift: STHR → H <sub>1</sub> → H<br>R/L = L; left shift: STHL → H <sub>120</sub> → H                                                                                                                                            |                                          |                                        |  |  |

| VDD1                             | Logic power                      | 5 V ±10 %                                                                                                                                                                                                                                      |                                          |                                        |  |  |

| V <sub>DD2</sub>                 | Driver power                     | 12 V                                                                                                                                                                                                                                           |                                          |                                        |  |  |

| Vss                              | Ground                           | Connect this pin to system ground.                                                                                                                                                                                                             |                                          |                                        |  |  |

| TEST: to TEST:                   | Test pins                        | Fix these pins to the L level.                                                                                                                                                                                                                 |                                          |                                        |  |  |

#### Cautions

- 1. Turn on power to V<sub>DD1</sub>, logic input, V<sub>DD2</sub>, and video signal input in this order, to prevent latchup. Turn off power in the reverse order. Observe this power sequence even during a transitional period.

- The delay time of the clock and internal sampling pulse SHPn are designed to be about 15 to 30 ns (at VDD1 = 5 V, 25 °C). Delay the video input signal from the clock by this delay time.

- Never change the video input signal during one sampling period. The maximum frequency of the video input of this product is 3.3 MHz. If a video signal with a higher frequency is input, the data may not be correctly displayed.

- 4. Insert a capacitor of 0.1 to 1  $\mu$ F between V<sub>DD1</sub> and V<sub>SS</sub>, and V<sub>DD2</sub> and V<sub>SS</sub>. Unless the power supply is reinforced, the supply voltage may fluctuate, making the sampling voltage abnormal.

- 5. If noise is superimposed on the start pulse pin, the data may not be correctly displayed. For this reason, be sure to input the reset signal during the vertical blanking period.

- 6. If the start pulse width is extended by half the clock or longer, the sampling start timing SPH1 does not change from the normal timing; therefore, the sampling operation is performed normally.

- 7. The  $\mu$ PD16447 is designed to have logic frequency f<sub>max.</sub> = 5 MHz (5 V ±10%) on the assumption that it is used to drive an LCD panel of non-interlace, comb wiring with a maximum number of dots of 882 × 240. If this product is used with an LCD panel having a greater dot size, the LCD panel may malfunction or its display quality may be degraded.

- 8. The maximum operating temperature of this product is +85 °C. If this limit is exceeded, the REF value (output voltage) tends to decrease abruptly.

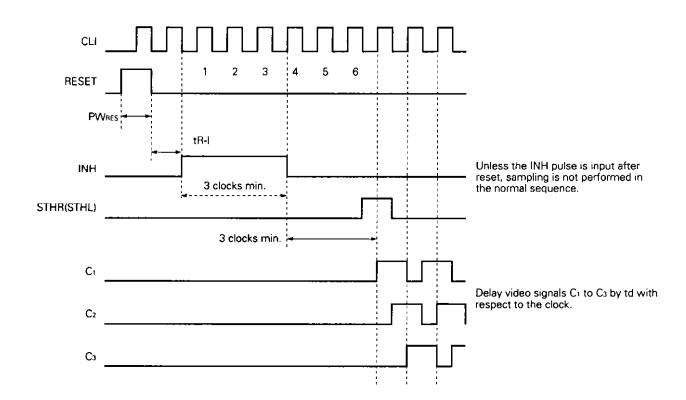

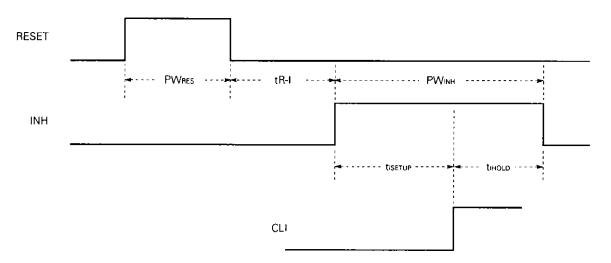

- 9. Recommended timing: For tR-I and PWRES, refer to ELECTRICAL CHARACTERISTICS. (The timing of the video signal inputs C<sub>1</sub> to C<sub>3</sub> is in sequential sampling mode.)

# **FUNCTIONAL DESCRIPTION**

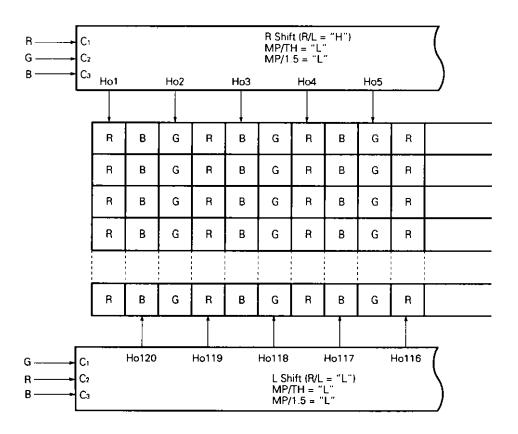

## 1. Multiplexer

This circuit selects video signals R, G, and B input to C<sub>1</sub>, C<sub>2</sub>, and C<sub>3</sub>, respectively, according to the pixel arrangement of the LCD panel, and outputs the signals to H<sub>1</sub> through H<sub>120</sub>. Vertical stripe, delta, or mosaic arrangement can be selected by using the MP/TH and MP/1.5 pins in combination.

# (1) VERTICAL STRIPE ARRANGEMENT MODE (MP/TH = L, MP/1.5 = L)

In this mode, the relation between the video signals C<sub>1</sub>, C<sub>2</sub>, and C<sub>3</sub>, and output pins is as shown below. This mode is used to drive an LCD panel in the vertical stripe arrangement. In this mode, the multiplexer circuit is in the through state.

# Relations between video signals C1, C2, and C3, and output pins

| Line No.<br>(No. of INHs) | RESET | INH | H1 (H120)         | H2 (H119)                                  | H2 (H118)                                  | H2 (H117)                                  | ŀ | H119 (H2)                                  | H120 (H1)                                  |

|---------------------------|-------|-----|-------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|---|--------------------------------------------|--------------------------------------------|

| 0                         | н     | L   | Undefined         | $\rightarrow$                              | →                                          | $\rightarrow$                              |   | $\rightarrow$                              | <b>→</b>                                   |

| 1                         | L     | L   | Output<br>C1 (C3) | Output<br>C <sub>2</sub> (C <sub>2</sub> ) | Output<br>C <sub>3</sub> (C <sub>1</sub> ) | Output<br>C <sub>1</sub> (C <sub>3</sub> ) |   | Output<br>C <sub>2</sub> (C <sub>2</sub> ) | Output<br>C <sub>3</sub> (C <sub>1</sub> ) |

| 2                         | L     | L   | Output<br>C1 (C3) | Output<br>C2 (C2)                          | Output<br>C3 (C1)                          | Output<br>C1 (C3)                          |   | Output<br>C2 (C2)                          | Output<br>C3 (C1)                          |

|                           |       | :   | :                 |                                            |                                            |                                            |   |                                            |                                            |

( ): for left shift

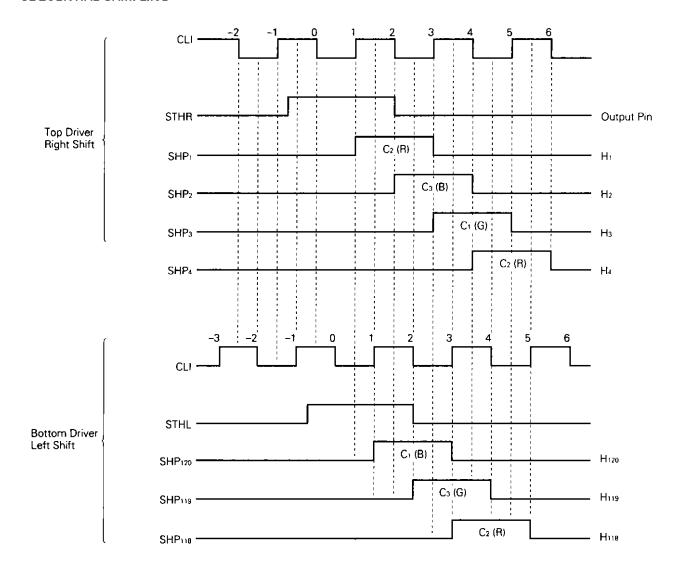

## **TIMING CHART**

# **EXAMPLE OF MULTIPLEXER OPERATION IN STRIPE ARRANGEMENT MODE**

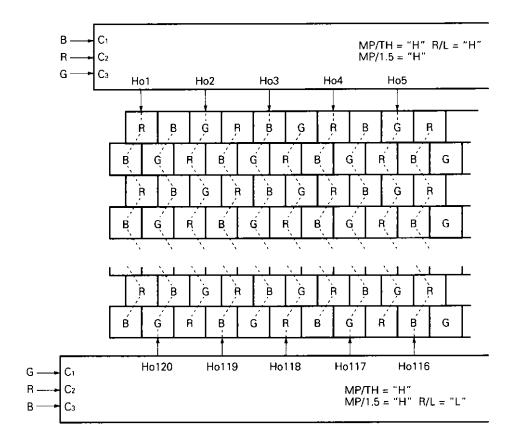

# (2) DELTA ARRANGEMENT MODE (MP/TH = H, MP/1.5 = H)

# Relations between video signals C1, C2, and C3, and output pins

| Line No.<br>(No. of INHs) | RESET | INH | H1 (H120)                                    | H2 (H119)                                    | H3 (H118)           | H4 (H117)                                    | H119 (H2)                                    | H120 (H1)                                    |

|---------------------------|-------|-----|----------------------------------------------|----------------------------------------------|---------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|

| 0                         | Н     | L   | Undefined                                    | ←                                            | ←                   | ←                                            | ←                                            | ← :                                          |

| 1                         | L     | L   | Sampling<br>C <sub>2</sub> (C <sub>3</sub> ) | Sampling<br>C <sub>3</sub> (C <sub>2</sub> ) | Sampling<br>C1 (C1) | Sampling<br>C <sub>2</sub> (C <sub>3</sub> ) | Sampling<br>C <sub>3</sub> (C <sub>2</sub> ) | Sampling<br>C <sub>1</sub> (C <sub>1</sub> ) |

| 2                         | L     | Ĺ   | Output<br>C2 (C3)                            | Output<br>C <sub>3</sub> (C <sub>2</sub> )   | Output<br>C1 (C1)   | Output<br>C <sub>2</sub> (C <sub>3</sub> )   | Output<br>C <sub>2</sub> (C <sub>2</sub> )   | Output<br>C1 (C1)                            |

| 3                         | L     | L   | Output<br>C1 (C1)                            | Output<br>C <sub>2</sub> (C <sub>3</sub> )   | Output<br>C3 (C2)   | Output<br>C1 (C1)                            | Output<br>C <sub>2</sub> (C <sub>2</sub> )   | Output<br>C3 (C2)                            |

|                           |       |     |                                              |                                              |                     |                                              |                                              |                                              |

( ): for left shift

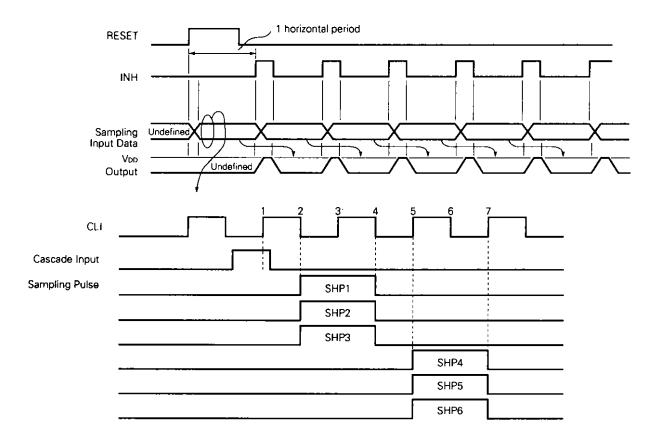

## **TIMING CHART**

# **SEQUENTIAL SAMPLING**

# EXAMPLE OF MULTIPLEXER OPERATION IN MOSAIC ARRANGEMENT MODE

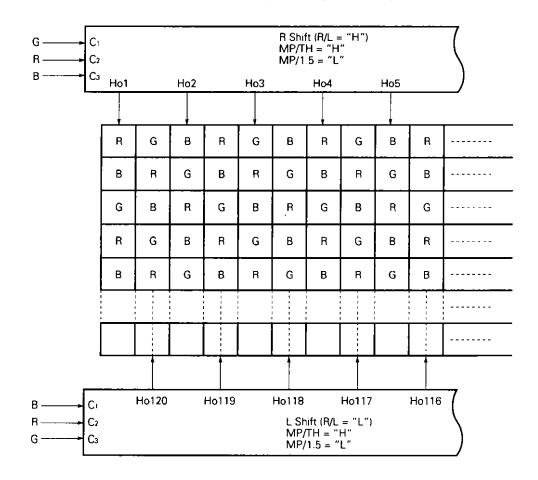

# (3) MOSAIC ARRANGEMENT MODE (MP/TH = H, MP/1.5 = L)

In this mode, the relation between video signals C<sub>1</sub>, C<sub>2</sub>, and C<sub>3</sub>, and the output pins is as shown below. This mode is used to drive an LCD panel in the mosaic arrangement.

Relations between video signals C1, C2, C3, and output pins

| Line No.<br>(INHs) | RESET | INH | H1 (H120)                                    | H2 (H119)                                    | H3 (H118)                                  | H4 (H117)                                    | H119 (H2)                                    | H120 (H1)                                  |

|--------------------|-------|-----|----------------------------------------------|----------------------------------------------|--------------------------------------------|----------------------------------------------|----------------------------------------------|--------------------------------------------|

| 0                  | Н     | L   | Undefined                                    | <b></b>                                      | ←                                          | ←                                            | ←                                            | _ ←                                        |

| 1                  | L     | L   | Sampling<br>C <sub>2</sub> (C <sub>3</sub> ) | Sampling<br>C <sub>3</sub> (C <sub>2</sub> ) | Sampling<br>C1 (C1)                        | Sampling<br>C <sub>2</sub> (C <sub>3</sub> ) | Sampling<br>C <sub>3</sub> (C <sub>2</sub> ) | Sampling<br>C1 (C1)                        |

| 2                  | L     | Ĺ   | Output<br>C2 (C3)                            | Output<br>C3 (C2)                            | Output<br>C1 (C1)                          | Output<br>Cz (Ca)                            | Output<br>C <sub>3</sub> (C <sub>2</sub> )   | Output<br>C1 (C1)                          |

| 3                  | L     | L   | Output<br>C <sub>3</sub> (C <sub>2</sub> )   | Output<br>C1 (C1)                            | Output<br>C <sub>2</sub> (C <sub>3</sub> ) | Output<br>C3 (C2)                            | Output<br>C1 (C1)                            | Output<br>C <sub>2</sub> (C <sub>3</sub> ) |

| 4                  | L     | L   | Output<br>C1 (C1)                            | Output<br>C <sub>2</sub> (C <sub>3</sub> )   | Output<br>C3 (C2)                          | Output<br>C1 (C1)                            | Output<br>C <sub>2</sub> (C <sub>3</sub> )   | Output<br>C <sub>3</sub> (C <sub>2</sub> ) |

|                    | :     |     |                                              |                                              |                                            |                                              |                                              |                                            |

( ): for left shift

# **EXAMPLE OF MULTIPLEXER OPERATION IN MOSAIC ARRANGEMENT MODE**

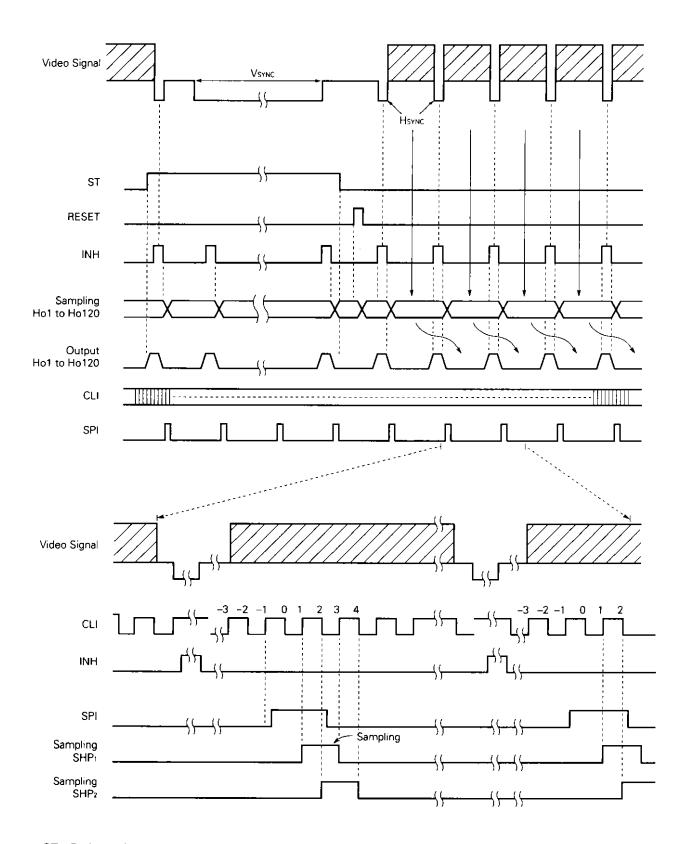

## **TIMING CHART (SEQUENTIAL SAMPLING)**

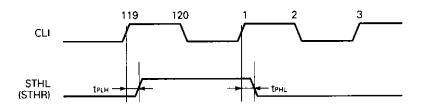

Remark The sampling pulse is set to the first stage of the shift register by the INH input. The shift register is started by the start trigger pulse that is generated when CL1 is low and STHR (STHL) is high, and is stopped when STHL (STHR) is output. STHR (STHL) is input three clocks after INH has fallen.

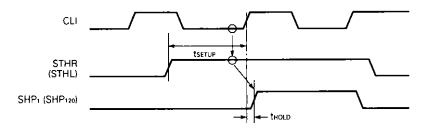

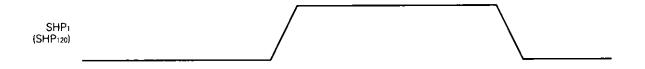

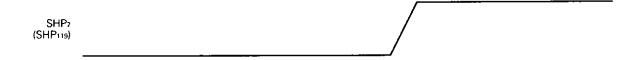

# **CASCADE INPUT TIMING (A of shift timing)**

## CASCADE OUTPUT TIMING (B of shift timing)

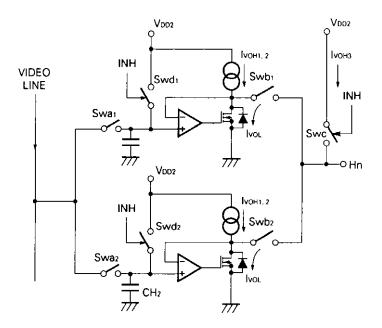

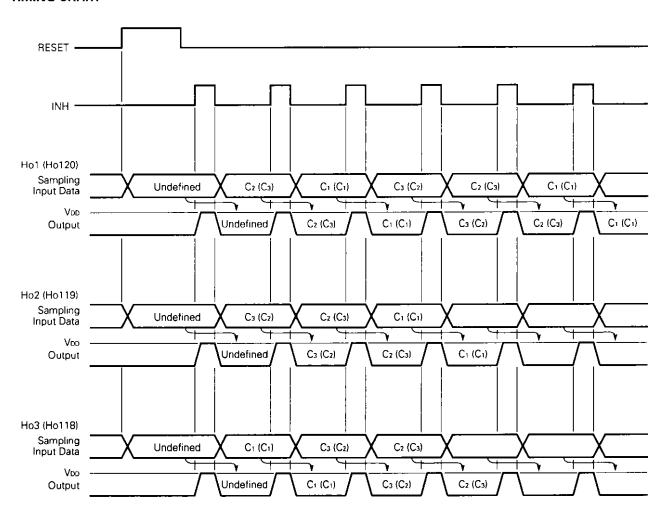

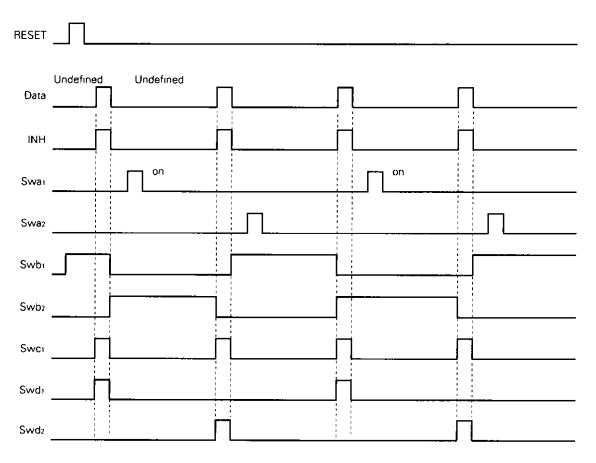

## **SAMPLE AND HOLD CIRCUITS**

The sample and hold circuits execute a sample and hold operation on video signals  $C_1$  through  $C_3$  selected by the multiplexer in the timing shown below, by using two latches.  $Sw_{a1}$  and  $Sw_{a2}$  are reset by the RESET signal and change at the rising and falling of the INH signal.

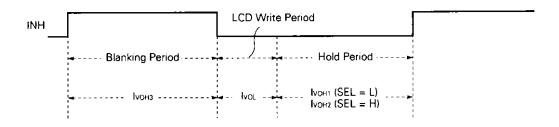

The timing sequence of the output buffer is illustrated below. During the blanking period, the LCD is reset (charged) once to the V<sub>DD2</sub> level by IvoH<sub>3</sub>. Next, the sampling voltage is written to the LCD by the sink current IvoL. When the specified voltage has been written, the LCD voltage is held by the source current IvoH<sub>1</sub> (-8  $\mu$ A typ.; SEL = L) or IvoH<sub>2</sub> (-30  $\mu$ A typ.; SEL = H), by using SEL (output current select input). SEL must be set to H or L in advance. IvoL is automatically switched to IvoH<sub>1</sub> or IvoH<sub>2</sub>, but the timing of INH is determined by the load capacitance of the LCD and other factors and therefore must be determined according to the individual LCD panel used.

# ABSOLUTE MAXIMUM RATINGS (TA = 25 °C, Vss = 0 V)

| Parameter             | Symbol          | Conditions | Ratings                        | Unit |

|-----------------------|-----------------|------------|--------------------------------|------|

| Logic Supply Voltage  | VDD1            |            | -0.5 to +7.0                   | ٧    |

| Driver Supply Voltage | Vooz            |            | -0.5 to +15                    | V    |

| Logic Input Voltage   | Vı              |            | -0.5 to V <sub>DD1</sub> + 0.5 | ٧    |

| Video Input Voltage   | Vvi             | C1, C2, C3 | -0.5 to V <sub>DD2</sub> + 0.5 | ٧    |

| Logic Output Voltage  | V <sub>01</sub> |            | -0.5 to VDD1 + 0.5             | ٧    |

| Video Output Voltage  | Voz             |            | -0.5 to VDD2 + 0.5             | ٧    |

| Driver Output Current | loz             |            | ±10                            | mA   |

| Operating Temperature | TA              |            | -20 to +85                     | °C   |

| Storage Temperature   | Tetg            |            | -65 to +125                    | °C   |

# RECOMMENDED OPERATING RANGE (TA = -20 to +85 °C, Vss = 0 V)

| Parameter                | Symbol           | Conditions | MIN.       | TYP. | MAX.                 | Unit |

|--------------------------|------------------|------------|------------|------|----------------------|------|

| Logic Supply Voltage     | V <sub>DD1</sub> |            | 4.5        |      | 5.5                  | V    |

| Driver Supply Voltage    | V <sub>DD2</sub> | -          |            |      | 12                   | V    |

| Driver Output Voltage    | Voz              |            | Vss2 + 2.5 |      | VDD2 - 2             | ٧    |

| High-level Input Voltage | ViH              |            | 0.7 VDD1   |      | Voot                 | ٧    |

| Low-level Input Voltage  | VIL              | · ·        | 0          |      | 0.3 V <sub>DO1</sub> | v    |

The elements are safe from damage and the functions work properly in the range  $T_A = -30$  to +85 °C.

14

# ELECTRICAL CHARACTERISTICS (TA = -20 to +85 °C, $VDD1 = 5 V \pm 10 \%$ , VDD2 = 12 V)

| Parameter                                   | Symbol | Condition                                                                            | MIN.                   | TYP.       | MAX.                 | Unit |

|---------------------------------------------|--------|--------------------------------------------------------------------------------------|------------------------|------------|----------------------|------|

| Video Signal Maximum<br>Output Voltage      | Vvoн   |                                                                                      | V <sub>DO2</sub> - 2.0 | VDD2 - 0.8 |                      | ٧    |

| Video Signal Minimum<br>Output Voltage      | Vvol   |                                                                                      |                        | 1.45       | 2.5                  | ٧    |

| Logic High-level Output Voltage             | VLOH   | STHL, STHR pin                                                                       | 0.9·VD01               |            |                      | ٧    |

| Logic Low-level Output Voltage              | VLOL   | STHL, STHR pin                                                                       |                        |            | 0.1·Vob1             | ٧    |

| High-level Input Voltage                    | Vін    |                                                                                      | 0.7·V <sub>DD1</sub>   |            | VDD1                 | ٧    |

| Low-level Input Voltage                     | VIL    |                                                                                      | 0                      |            | 0.3-V <sub>DD1</sub> | V    |

| Video Signal High-level<br>Output Current 1 | Ivon1  | INH = L, SEL = L<br>Vot = 6 V, Vo = 8 V                                              | -13                    | -8         | -2                   | μА   |

| Video Signal High-level<br>Output Current 2 | Ivo+2  | INH = L, SEL = H<br>Voi = 6 V, Vo = 8 V                                              |                        | -30        |                      | μΑ   |

| Video Signal High-level<br>Output Current 3 | Ivoнз  | INH = H<br>Vor = 10 V                                                                |                        |            | -0.3                 | mA   |

| Video Signal Low-level<br>Output Current    | IvoL   | INH = L<br>Vof = 11 V, Vo = 8 V                                                      | 0.3                    |            |                      | mA   |

| Video Signal Minimum Input<br>Voltage       | Vvil   | T <sub>A</sub> = 25 'C                                                               |                        |            | 1.5                  | V    |

| Reference Voltage 1                         | VREF1  | Vvi = 2 V, TA = 25 °C                                                                |                        | 1.99       |                      | ٧    |

| Reference Voltage 2                         | VAEF2  | Vvi = 6 V, TA = 25 °C                                                                |                        | 5.97       |                      | V    |

| Reference Voltage 3                         | VREF3  | Vvi = 10 V, TA = 25 °C                                                               |                        | 9.97       |                      | ٧    |

| Output Voltage deviation 1                  | ∆Vv01  | Vvi = 2 V, Ta = 25 °C                                                                |                        |            | ±50                  | mV   |

| Output Voltage deviation 2                  | ΔVνο2  | Vvi = 6 V, Ta = 25 °C                                                                |                        |            | ±50                  | mV   |

| Output Voltage deviation 3                  | ΔVv03  | Vvi = 10 V, TA = 25 °C                                                               |                        |            | ±50                  | mV   |

| Logic Input Leakage Current                 | lu     |                                                                                      |                        |            | ±1                   | μА   |

| Video Input Leakage Current                 | lvL    |                                                                                      |                        |            | ±10                  | μА   |

| Logic Dynamic Current<br>Consumption        | 1001   | $f_{CLK} = 5 \text{ MHz}$ $V_{VI} = 6 \text{ V, no load}$ $INH\text{-duty} = 4.5 \%$ |                        | 1.0        | 2.5                  | mA   |

| Driver Dynamic Current<br>Consumption       | 1002   | fc.x = 5 MHz<br>INH = H, no load<br>INH-duty = 4.5 %                                 |                        | 2.7        | 5.0                  | mA   |

Vot; output applied voltage, Vo; output voltage under no load

REF values are typical values only. The output deviation is the on-chip guaranteed value.

# SWITCHING CHARACTERISTICS (TA = -20 to +85 °C, $V_{DD1}$ = 5 V ±10 %, $V_{DD2}$ = 12 V, $C_L$ = 20 pF)

| Parameter                     | Symbol       | Condition                            | MIN. | TYP. | MAX. | Unit |

|-------------------------------|--------------|--------------------------------------|------|------|------|------|

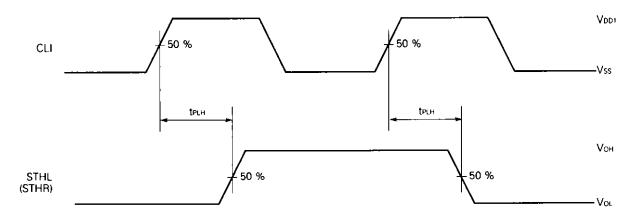

| Start Pulse Propagation Delay | <b>TPHL</b>  |                                      | 10   |      | 120  | ns   |

| Time                          | <b>t</b> PLH |                                      | 10   |      | 120  | ns   |

| Maximum Clock Frequency       | fmax.        | Cascade connection                   | 5    |      |      | MHz  |

| Logic Input Capacitance       | Cıı          | Other than STHL, STHR,<br>TA = 25 °C | -    |      | 15   | pF   |

| STHL, STHR Input Capacitance  | Cız          | STHL, STHR, TA = 25 °C               |      |      | 20   | ρF   |

| Video Input Capacitance       | C13          | C1 to C3, Vvi = 6 V, TA = 25 °C      |      | -    | 30   | ρF   |

TIMING REQUIREMENTS (TA = -20 to +85 °C,  $V_{DD1}$  = 5 V ±10 %,  $V_{DD2}$  = 12 V)

| Parameter              | Symbol  | Condition   | MIN. | TYP. | MAX. | Unit |

|------------------------|---------|-------------|------|------|------|------|

| Clock Pulse Width      | PWcLi   | Duty = 50 % | 100  |      |      | пѕ   |

| Start Pulse Setup Time | tsetup  |             | 80   |      |      | ns   |

| Start Pulse Hold Time  | thold   |             | 10   |      |      | ns   |

| ST Pulse Width         | PWst    |             | 100  | -    |      | ns   |

| Reset Pulse Width      | PWRES   |             | 100  |      |      | ns   |

| INH Setup Time         | TISETUP |             | 300  |      |      | ns   |

| INH Hold Time          | tinolo  |             | 300  |      |      | ns   |

| Reset - INH Time       | tR-I    |             | 100  |      |      | ns   |

Keep the rise and fall times of all the digital signals to within  $t_r = t_f = 5$  ns (10 % to 9 %). As an example, CLI is defined in the switching characteristic waveform diagram on the next page.

Make sure that the start INH pulse width PWINH is at least three clocks.

# **SWITCHING CHARACTERISTIC WAVEFORM**

# **Start Pulse Input Timing**

# **Start Pulse Output Timing**

ST: By inputting this signal during the vertical blanking period, the power consumption can be reduced.

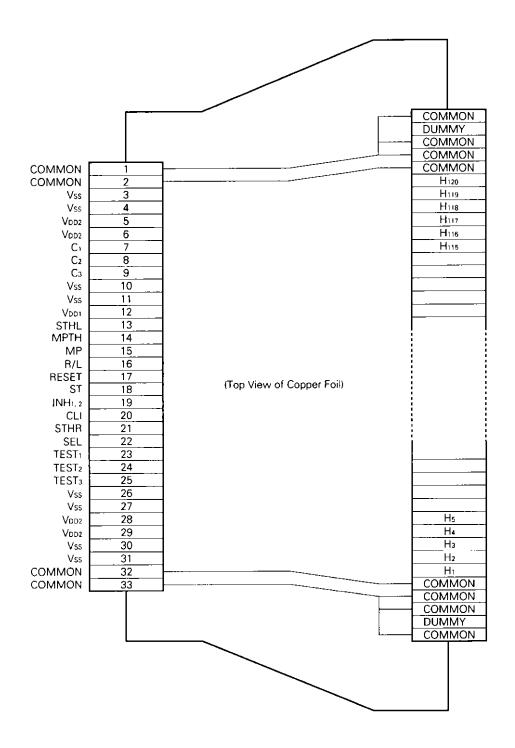

# STANDARD TCP PIN CONFIGURATION (µPD16447N-051)

Caution This figure indicates the pin configuration of the standard TCP and does not specify the dimensions of the TCP.

# **RECOMMENDED MOUNTING CONDITIONS**

The following mounting conditions for the  $\mu PD16447$  are recommended. For any other mounting conditions, consult NEC.

| Mounting Conditions | Mounting Method            | Conditions                                                                                                                                                                                                                  |

|---------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Thermocompression   | Soldering                  | Heating tool: 300 to 350 °C, Time: 2 to 3 seconds, Pressure: 100 g (per piece)                                                                                                                                              |

|                     | ACF (sheet adhesive agent) | Preliminary adhesion: 70 to 100 °C, Pressure: 3 to 8 kg/cm², Time: 3 to 5 seconds Actual adhesion: 165 to 180 °C, Pressure: 25 to 45 kg/cm², Time: 30 to 40 seconds (with Sumitomo Bakelite's anisotropie film SUMIZAC1003) |

Caution 1. For the mounting conditions for the ACF, consult the ACF manufacturer before using the ACF.

2. Do not use two or more mounting methods in combination.

# **REFERENCE**

| Document Name                                                | Document No. |

|--------------------------------------------------------------|--------------|

| NEC semiconductor device reliability/quality control system. | IEI-1212     |

| Quality grade on NEC semiconductor devices.                  | IEI-1209     |

| Semiconductor device mounting technology manual.             | IEI-1207     |

[MEMO]

## [MEMO]

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customer must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices in "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact NEC Sales Representative in advance.

Anti-radioactive design is not implemented in this product.

M4 94.11