# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# MOS INTEGRATED CIRCUIT

# $\mu$ PD70108H, 70116H

V20HL™, V30HL™ 16/8, 16-BIT MICROPROCESSOR

#### DESCRIPTION

The  $\mu$ PD70108H (V20HL) and  $\mu$ PD70116H (V30HL) are CMOS 16-bit microprocessors developed from the  $\mu$ PD70108 (V20<sup>TM</sup>) and  $\mu$ PD70116 (V30<sup>TM</sup>). It offers higher processing speed and lower power consumption than the  $\mu$ PD70108 and  $\mu$ PD70116.

The  $\mu$ PD70108H and  $\mu$ PD70116H are capable of operating at 16 MHz. In addition to the conventional standby function, fully static internal circuits are employed in the  $\mu$ PD70108H and  $\mu$ PD70116H. This allows the  $\mu$ PD70108H and  $\mu$ PD70116H to have the clock stop function. Therefore, power consumption is significantly reduced in the  $\mu$ PD70108H and  $\mu$ PD70116H. Additionally, the  $\mu$ PD70108H and  $\mu$ PD70116H can operate at 5 V. However, the  $\mu$ PD70108H and  $\mu$ PD70116H are designed to also operate at 3 V.

#### **FEATURES**

- High-speed, low-power consumption version of μPD70108 and μPD70116

- Single power supply (5 V or 3 V)

- 125-ns minimum instruction execution time at 16 MHz (5 V)

250-ns minimum instruction execution time at 8 MHz (3 V)

- High-speed multiplication/division instructions:

1.2 to 3.6 µs (at 16 MHz, 5 V)

2.4 to 7.1  $\mu$ s (at 8 MHz, 3 V)

High-speed block transfer instructions:

μPD70108H: 2M bytes/second (at 16 MHz, 5 V)

1M bytes/second (at 8 MHz, 3 V)

μPD70116H: 2M words/second (at 16 MHz, 5 V)

1M words/second (at 8 MHz, 3 V)

The information in this document is subject to change without notice.

# **ORDERING INFORMATION**

# (1) $\mu$ PD70108H

| Part number        | Package Max                                      | dimum operating fre | equency (MHz) |

|--------------------|--------------------------------------------------|---------------------|---------------|

| μPD70108HCZ-10     | 40-pin plastic DIP (600 mil)                     |                     | 10            |

| μPD70108HCZ-12     | 40-pin plastic DIP (600 mil)                     |                     | 12.5          |

| μPD70108HCZ-16     | 40-pin plastic DIP (600 mil)                     |                     | 16            |

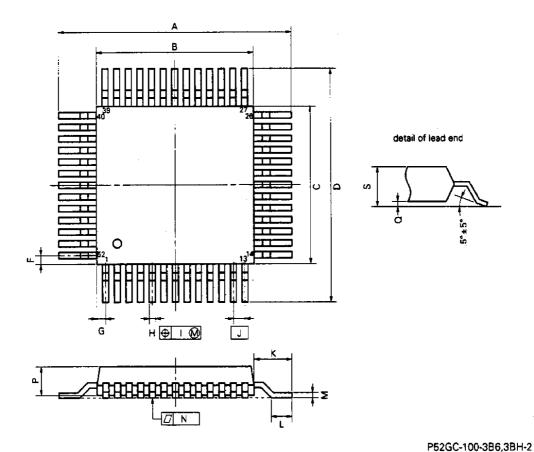

| μPD70108HGC-10-3B6 | 52-pin plastic QFP ( 114 mm) (resin thickness: 2 | .70 mm)             | 10            |

| μPD70108HGC-12-3B6 | 52-pin plastic QFP ( 14 mm) (resin thickness: 2  | .70 mm)             | 12.5          |

| μPD70108HGC-16-3B6 | 52-pin plastic QFP ( 14 mm) (resin thickness: 2  | .70 mm)             | 16            |

| μPD70108HG-10-22   | 52-pin plastic QFP ( 114 mm) (resin thickness: 1 | .50 mm)             | 10            |

| μPD70108HG-12-22   | 52-pin plastic QFP ( 14 mm) (resin thickness: 1  | .50 mm)             | 12.5          |

| μPD70108HG-16-22   | 52-pin plastic QFP ( 14 mm) (resin thickness: 1  |                     | 16            |

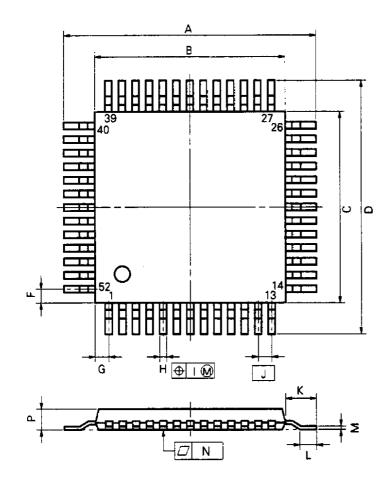

| μPD70108HLM-10     | 44-pin plastic QFJ ( 650 mil)                    |                     | 10            |

| μPD70108HLM-12     | 44-pin plastic QFJ ( 650 mil)                    |                     | 12.5          |

| μPD70108HLM-16     | 44-pin plastic QFJ (650 mil)                     |                     | 16            |

Remark Plastic QFJ is a new name for PLCC.

# (2) µPD70116H

| Part number        | Package Maximum o                                      | perating frequency (MHz) |

|--------------------|--------------------------------------------------------|--------------------------|

| μPD70116HCZ-10     | 40-pin plastic DIP (600 mil)                           | 10                       |

| μPD70116HCZ-12     | 40-pin plastic DIP (600 mil)                           | 12.5                     |

| μPD70116HCZ-16     | 40-pin plastic DIP (600 mil)                           | 16                       |

| μPD70116HGC-10-3B6 | 52-pin plastic QFP ( 14 mm) (resin thickness: 2.70 mm) | 10                       |

| μPD70116HGC-12-3B6 | 52-pin plastic QFP ( 14 mm) (resin thickness: 2.70 mm) | 12.5                     |

| μPD70116HGC-16-3B6 | 52-pin plastic QFP ( 14 mm) (resin thickness: 2.70 mm) |                          |

| μPD70116HG-10-22   | 52-pin plastic QFP ( 14 mm) (resin thickness: 1.50 mm) |                          |

| μPD70116HG-12-22   | 52-pin plastic QFP ( 14 mm) (resin thickness: 1.50 mm) | 12.5                     |

| μPD70116HG-16-22   | 52-pin plastic QFP ( 14 mm) (resin thickness: 1.50 mm) | ) 16                     |

| μPD70116HLM-10     | 44-pin plastic QFJ (☐650 mil)                          | 10                       |

| μPD70116HLM-12     | 44-pin plastic QFJ ( 650 mil)                          | 12.5                     |

| μPD70116HLM-16     | 44-pin plastic QFJ (650 mil)                           | 16                       |

Remark Plastic QFJ is a new name for PLCC.

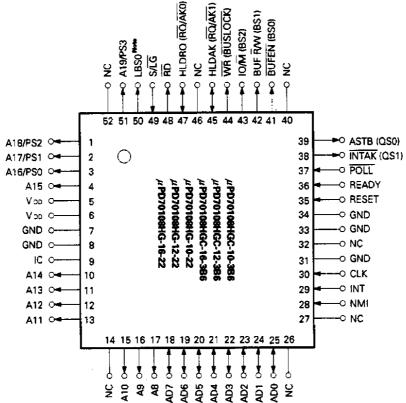

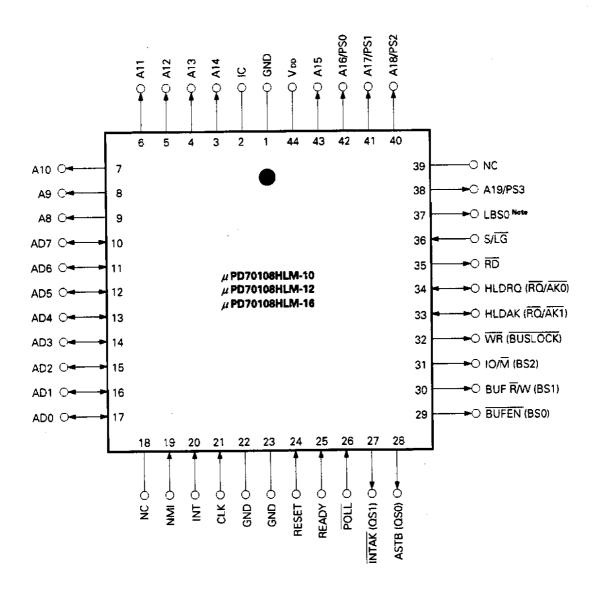

#### PIN CONFIGURATIONS (Top View)

#### (1) µPD70108H

Note Outputs high level in large-scale mode.

NC: No connection

IC: Internally connected to GND.

Note Outputs high level in large-scale mode.

NC: No connection

IC: Internally connected to GND.

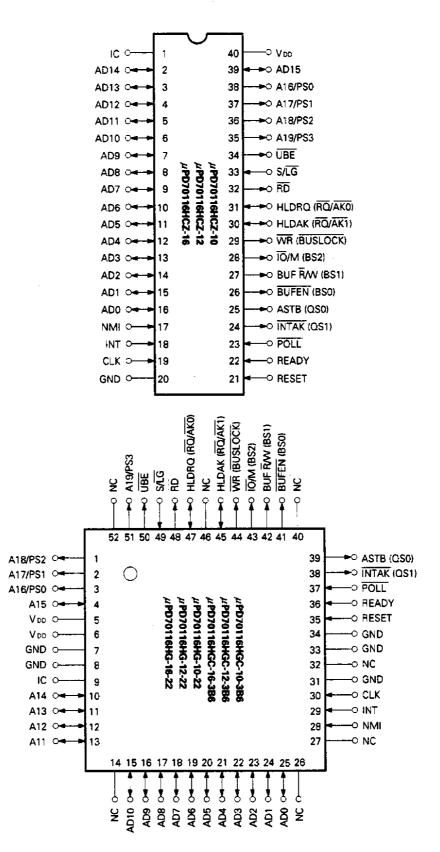

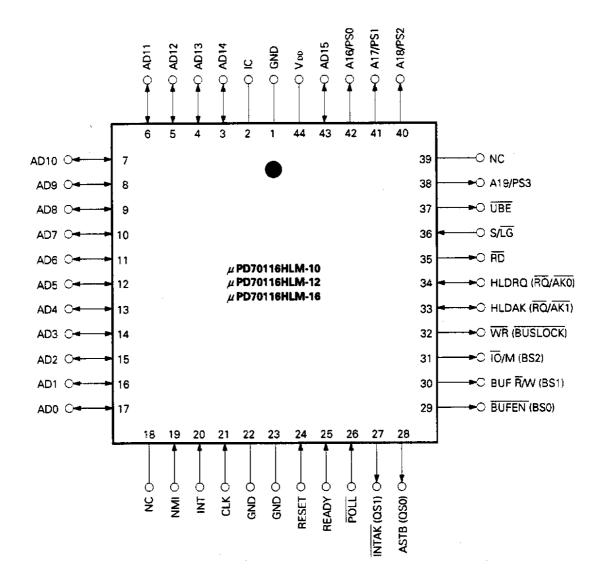

#### (2) µPD70116H

NC: No connection

IC: Internally connected to GND.

NC: No connection

IC: Internally connected to GND.

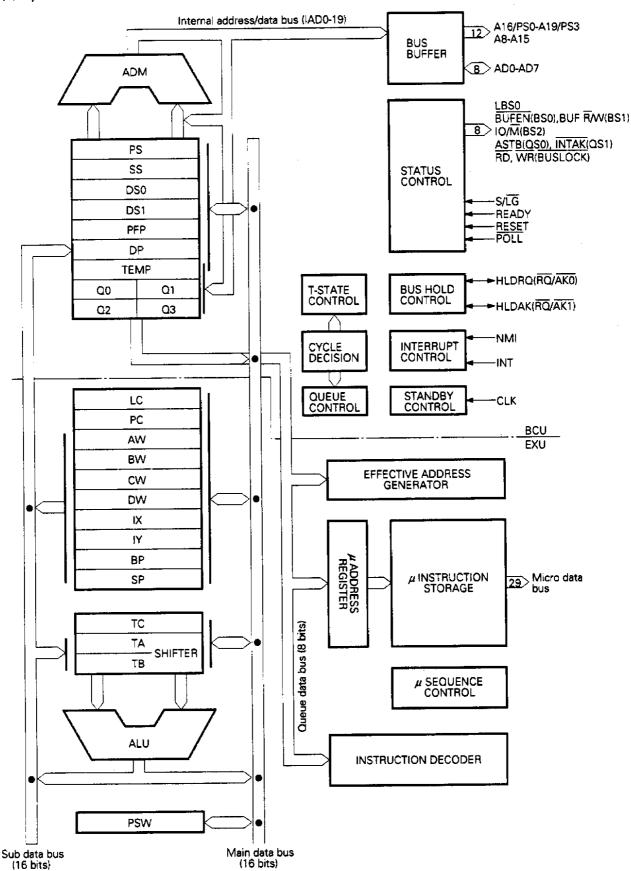

# INTERNAL BLOCK DIAGRAM

#### (1) $\mu$ PD70108H

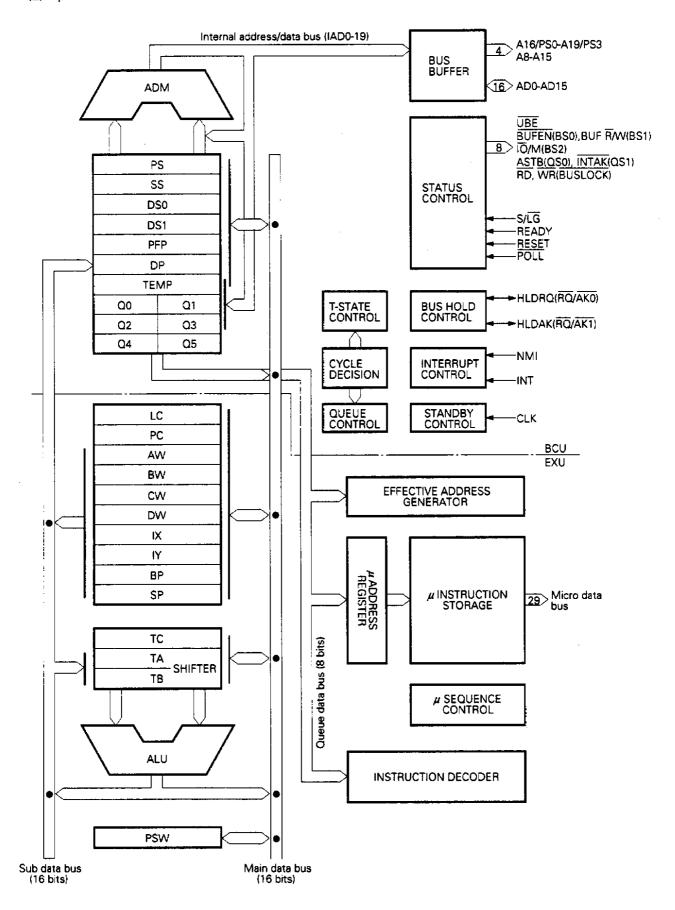

#### μPD70116H

# Differences between $\mu$ PD70108H and $\mu$ PD70116H, and $\mu$ PD70108 and $\mu$ PD70116

| ltem           | Product Name                                 | JED70108H, 70118H                   | μPD70108, 70116                    |

|----------------|----------------------------------------------|-------------------------------------|------------------------------------|

| Op             | erating Voltage                              | 5 V, 3 V                            | 5 V                                |

| Operating      | At VDD=5 V                                   | MAX.: 10, 12.5, 16 MHz<br>MIN. : DC | MAX.: 5, 8, 10 MHz<br>MIN. : 2 MHz |

| Frequency      | At VDD=3 V                                   | MAX.: 5, 6, 8 MHz<br>MIN. : DC      | Does not operate                   |

|                | esistor of RQ/AK Pin<br>Scale Mode)          | Not provided                        | Provided                           |

|                | BUFEN (BS0)Note1                             | н                                   | Hi-Z                               |

|                | BUFR/W (BS1)Note1                            | н                                   | Hi-Z                               |

| On Reset       | IO/M <sup>Note2</sup> (BS2) <sup>Note1</sup> | Н                                   | Hi-Z                               |

|                | IO/M <sup>Note3</sup> (BS2) <sup>Note1</sup> |                                     |                                    |

|                | WR (BUSLOCK)Note1                            | Н                                   | Hi-Z                               |

|                | RD                                           | Н                                   | Hi-Z                               |

| 52-Pin Plastic | : QTF (Resin Thick 1.50 mm)                  | Provided                            | Not provided                       |

Note 1. (): In large-scale mode.

**2.** μPD70108, 70108H

3. μPD70116, 70116H

# **CONTENTS**

| 1. | PIN I | FUNCTIONS                                     | 13 |

|----|-------|-----------------------------------------------|----|

|    | 1.1   | LIST OF PIN FUNCTIONS                         | 13 |

|    | 1.2   | PIN STATUS UNDER SPECIFIC CONDITIONS          | 15 |

|    | 1.3   | FUNCTIONAL DESCRIPTION                        | 18 |

| 2. | REGI  | STER CONFIGURATION                            | 25 |

|    | 2.1   | PFP (PREFETCH POINTER)                        | 25 |

|    | 2.2   | Q0-Q3, Q0-Q5 (PREFETCH QUEUES)                | 25 |

|    | 2.3   | DP (DATA POINTER)                             | 25 |

|    | 2.4   | TEMP (TEMPORARY COMMUNICATION REGISTER)       | 25 |

|    | 2.5   | SEGMENT REGISTERS (PS, SS, DS0, DS1)          | 25 |

|    | 2.6   | ADM (ADDRESS MODIFIER)                        | 26 |

|    | 2.7   | GENERAL-PURPOSE REGISTERS (AW, BW, CW, DW)    | 26 |

|    | 2.8   | POINTERS (SP, BP) AND INDEX REGISTER (IX, IY) | 27 |

|    | 2.9   | TA/TB (TEMPORARY REGISTER/SHIFTER A/B)        | 27 |

|    | 2.10  | TC (TEMPORARY REGISTER C)                     | 27 |

|    | 2.11  | ALU (ARITHMETIC & LOGIC UNIT)                 | 27 |

|    | 2.12  | PSW (PROGRAM STATUS WORD)                     | 27 |

|    | 2.13  | LC (LOOP COUNTER)                             | 28 |

|    | 2.14  | PC (PROGRAM COUNTER)                          | 28 |

|    | 2.15  | EAG (EFFECTIVE ADDRESS GENERATOR)             | 29 |

|    | 2.16  | INSTRUCTION DECODER                           | 29 |

|    | 2.17  | MICROADDRESS REGISTER                         | 29 |

|    | 2.18  | MICROINSTRUCTION ROM                          | 29 |

|    | 2.19  | MICROINSTRUCTION SEQUENCE CIRCUIT             | 29 |

| 3. | INCF  | EASING INSTRUCTION EXECUTION SPEED            | 30 |

|    | 3.1   | DUAL DATA BUS METHOD                          | 30 |

|    | 3.2   | EFFECTIVE ADDRESS GENERATOR                   | 31 |

|    | 3.3   | 16/32-BIT TEMPORARY REGISTER/SHIFTER (TA, TB) | 31 |

|    | 3.4   | LOOP COUNTER (LC)                             | 31 |

|    |       |                                               |    |

| 4.  | UNIC         | QUE µPD70108H INSTRUCTIONS                                | 32  |

|-----|--------------|-----------------------------------------------------------|-----|

|     | 4.1          | VARIABLE BIT FIELD MANIPULATION INSTRUCTIONS              | 32  |

|     | 4.2          | PACKED BCD OPERATION INSTRUCTIONS                         |     |

|     | 4.3          | STACK MANIPULATION INSTRUCTIONS                           | 35  |

|     | 4.4          | CHECK ARRAY BOUNDARY INSTRUCTION                          | 40  |

|     | 4.5          | MODE MANIPULATION INSTRUCTIONS                            | 41  |

|     | 4.6          | FLOATING-POINT OPERATION COPROCESSOR CONTROL INSTRUCTIONS | 43  |

| 5.  | INTE         | RRUPT OPERATION                                           | 44  |

| 6.  | STAI         | NDBY FUNCTION                                             | 46  |

| 7.  | I/O <i>A</i> | ADDRESS RESERVE                                           | 46  |

| 8.  | INST         | RUCTION SET                                               | 47  |

| 9.  | ELEC         | TRICAL SPECIFICATIONS                                     | 81  |

|     | 9.1          | WHEN VDD = 5 V ± 10%                                      | 81  |

|     | 9.2          | WHEN Vod = 3 V ± 10%                                      | 85  |

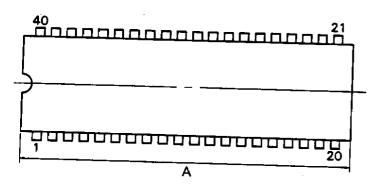

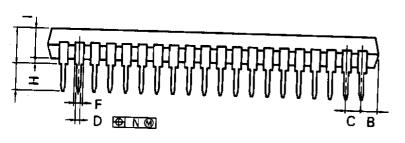

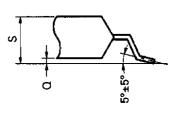

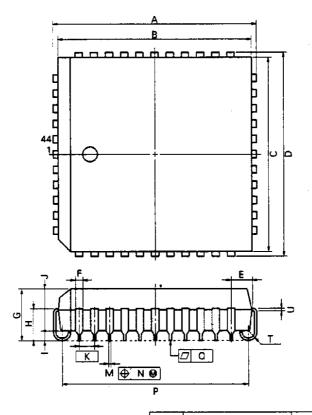

| 10. | PAC          | KAGE DRAWINGS                                             | 99  |

| 11. | REC          | DMMENDED SOLDERING CONDITIONS                             | 103 |

# 1. PIN FUNCTIONS

# 1.1 LIST OF PIN FUNCTIONS

# (1) Small-scale mode (S/LG = H)

| Pin Name             | input/Output           | Function                                    |

|----------------------|------------------------|---------------------------------------------|

| A16/PS0-A19/PS3      | Tri-state output       | Address bus/processor status                |

| A8-A15 (μPD70108H)   | Tri-state output       | Address bus                                 |

| AD0-AD7 (μPD70108H)  | Tri-state output       | Address/data bus                            |

| AD0-AD15 (μPD70116H) | Tri-state input/output | Address/data bus                            |

| ASTB                 | Output                 | Address strobe                              |

| INTAK                | Output                 | Interrupt acknowledge display               |

| BUFEN                | Tri-state output       | External data buffer enable                 |

| BUFR/W               | Tri-state output       | External data buffer read/write selection   |

| IO/M (μPD70108H)     | Tri-state output       | I/O, memory selection                       |

| ΙΟ/Μ (μPD70116H)     |                        |                                             |

| LSB0 (μPD70108H)     | Tri-state output       | Bus status                                  |

| UBE (μPD70116H)      | Tri-state output       | Data bus upper byte enable                  |

| RD                   | Tri-state output       | Read strobe                                 |

| WR                   | Tri-state output       | Write strobe                                |

| HLDRQ                | Input                  | Bus hold request                            |

| HLDAK                | Output                 | Bus hold enable                             |

| S/LG                 | Input                  | Small-scale/large-scale mode selection (=H) |

| NMI                  | Input                  | Non-maskable interrupt request              |

| INT                  | Input                  | Maskable interupt request                   |

| CLK                  | Input                  | System clock                                |

| READY                | Input                  | External ready display                      |

| POLL                 | input                  | External polling display                    |

| RESET                | Ínput                  | System reset                                |

# (2) Large-scale mode $(S/\overline{LG} = L)$

| Pin Name                                       | Input/Output           | Function                                    |

|------------------------------------------------|------------------------|---------------------------------------------|

| A16/PS0-A19/PS3                                | Tri-state output       | Address bus/processor status                |

| A8-A15 (μPD70108H)                             | Tri-state output       | Address bus                                 |

| AD0-AD7 (μPD70108H)                            | Tri-state input/output | Address/data bus                            |

| AD0-AD15 (µPD70116H)                           | Tri-state input/output | Address/data bus                            |

| QS0, QS1                                       | Output                 | Queue status                                |

| BS0-BS2                                        | Tri-state output       | Bus status                                  |

| LSB0 (µPD70108H)<br>(pin for small-scale mode) | Output                 | Outputs high level                          |

| ÜBE (μPD70116H)                                | Tri-state output       | Data bus upper byte enable                  |

| RD                                             | Tri-state output       | Read strobe                                 |

| BUSLOCK                                        | Tri-state output       | Write strobe                                |

| RQ/AKO, RQ/AK1                                 | Tri-state input/output | Bus hold request/enable                     |

| S/LG                                           | Input                  | Small-scale/large-scale mode selection (=L) |

| NMI                                            | Input                  | Non-maskable interrupt request              |

| INT                                            | Input                  | Maskable interupt request                   |

| CLK                                            | Input                  | System clock                                |

| READY                                          | Input                  | External ready display                      |

| POLL                                           | Input                  | External polling display                    |

| RESET                                          | Input                  | System reset                                |

#### 1.2 PIN STATUS UNDER SPECIFIC CONDITIONS

#### (1) Small-scale mode

|                                       |      | Conditions |       |

|---------------------------------------|------|------------|-------|

| Pin Name                              | Hold | Halt       | Reset |

| A8-A15 <sup>Note1</sup> (μPD70108H)   | Hi-Z | HorL       | Hi-Z  |

| AD0-AD7 <sup>Note1</sup> (μPD70108H)  | Hi-Z | H or L     | Hi-Z  |

| AD0-AD15 <sup>Note1</sup> (μPD70116H) | Hi-Z | HorL       | Hi-Z  |

| A16/PS0-A19/PS3Note1                  | Hi-Z | HorL       | Hi-Z  |

| ASTB                                  | L    | Note2      | L     |

| INTAK                                 | Н    | Н          | н     |

| BUFEN Note1                           | Hi-Z | Н          | Note3 |

| BUFR/W <sup>Mote1</sup>               | Hi-Z | H or L     | Nate3 |

| IO/M <sup>Note1</sup> (μPD70108H)     | Hi-Z | H or L     | Note3 |

| IO/M <sup>Note1</sup> (μPD70116H)     | Hi-Z | H or L     | Note3 |

| LSB0 <sup>Note1</sup> (μPD70108H)     | Hi-Z | Н          | Hi-Z  |

| ÜBE <sup>Note1</sup> (μPD70116H)      | HI-Z | Н          | Hi-Z  |

| RDNo1e1                               | Hi-Z | н          | Note3 |

| WR <sup>Note1</sup>                   | Hi-Z | н          | Note3 |

| HLDAK                                 | Н    | i L        | L     |

- Note 1. An internal latch is provided, so that the status before this pin goes into a high-impedance (Hi-Z) state is retained, until the pin is driven by an external source.

- 2. High level only once (for about half a clock cycle) during the halt acknowledge cycle, otherwise low level.

- 3. Outputs the high level as long as the reset signal is active, and goes into a Hi-Z state after the reset signal has become inactive and until the first bus cycle is started. Therefore, if the pin is not driven by an external source, the high level is retained by a latch.

## (2) Large-scale mode

|                                                                 | ,      | Conditions |        |

|-----------------------------------------------------------------|--------|------------|--------|

| Pin Name                                                        | Hold   | Halt       | Reset  |

| A8-A15 <sup>Note1</sup> (μPD70108H)                             | Hi-Z   | H or L     | Hi-Z   |

| AD0-AD7 <sup>Note1</sup> (μPD70108H)                            | Hi-Z   | H or L     | Hi-Z   |

| AD0-AD15 <sup>Note1</sup> (μPD70116H)                           | Hi-Z   | H or L     | Hi-Z   |

| A16/PS0-A19/PS3 <sup>Note1</sup>                                | Hi-Z   | H or L     | Hi-Z   |

| QS0                                                             | Note 2 | L          | L      |

| QS1                                                             | L      | L          | L      |

| BS0 <sup>Note1</sup>                                            | Hi-Z   | н          | Note 3 |

| BS1 <sup>Note1</sup>                                            | Hi-Z   | н          | Note 3 |

| BS2 <sup>Note1</sup>                                            | Hi-Z   | Н          | Note 3 |

| ÜBE <sup>Note1</sup> (μPD70116H)                                | Hi-Z   | н          | Hi-Z   |

| RD <sup>Note1</sup>                                             | Hi-Z   | Н          | Note 3 |

| BUSLOCK <sup>Note1</sup>                                        | Hi-Z   | H or L     | Note 3 |

| RQ/AK0 <sup>Note4</sup>                                         | Н      | Н          | Н      |

| RQ/AK1 Note4                                                    | н      | н          | Н      |

| LS80 <sup>Note2</sup> (µPD70108H)<br>(pin for small-scale mode) | Hi-Z   | н          | Hi-Z   |

- Note 1. An internal latch is provided, so that the status before this pin goes into a high-impedance (Hi-Z) state is retained, until the pin is driven by an external source.

- 2. High level only once (for about half a clock cycle) during the halt acknowledge cycle, otherwise low level.

- 3. Outputs the high level as long as the reset signal is active, and goes into a Hi-Z state after the reset signal has become inactive and until the first bus cycle is started. Therefore, if the pin is not driven by an external source, the high level is retained by a latch.

- 4. The RO/AK pin is connected with a pull-up resistor in the large-scale mode.

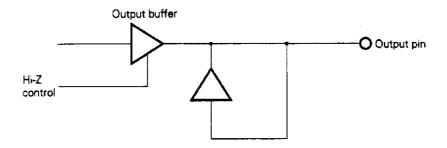

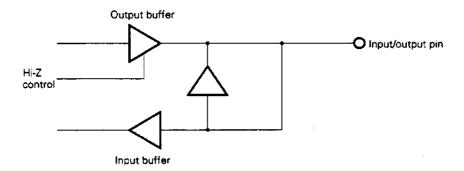

Remark The circuit configuration of the latch is as shown below. To invert the status of the pin with a latch, a drive current higher than the latch inverting current (ILE, ILL) is required.

# Output pin

# Input/output pin

#### 1.3 FUNCTIONAL DESCRIPTION

Some pins have meaning only for small-scale systems or large-scale systems, while others are used for both small- and large-scale systems.

- (1) A8-A15 (Address Bus) ... Small/Large Scale (µPD70108H)

- A8-A15 output the middle 8 bits of the 20-bit address information.

- A8-A15 are 3-state output pins and become high impedance during hold acknowledge cycles.

- (2) AD0-AD7 (Address/Data Bus) ... Small/Large Scale (μPD70108H)

AD0-AD7 serve as the time-multiplexed address/data bus. The lower 8-bit output of the 20-bit address information and data input/output are multiplexed.

16-bit data is input/output in two operations, the lower byte is the first byte, and the upper byte is the second.

These pins are 3-state input/output pins and become high impedance during hold acknowledge cycles and interrupt acknowledge cycles.

# (3) AD0 - AD15 (Address/Data Bus)... Small/Large Scale (μPD70116H)

This bus, which is for both addresses and data, performs the low 16-bit output of the 20-bit address information. The byte/word data input/output are performed as well in the time-sharing method.

$\mu$ PD70116H accesses memory or I/O operands, in terms of two separate areas, i.e., the byte data bank which is accessed with an even-numbered address (AD0=0) and the byte data bank which is accessed with an odd-number address (AD0=1). The least significant bit (AD0) does not have a meaning of its own as the address information word data; however, it is used to distinguish the byte bank of the odd-number address from that of the even-number address.

In addition to AD0, there are also the UBE signals available for the purpose of accessing byte/word data. The UBE signals are used in a combination as shown in the table below.

| Operand  Even-number Address Word |                  | UBE | AD0 | Bus Cycle Count |

|-----------------------------------|------------------|-----|-----|-----------------|

|                                   |                  | 0   | C C | 1               |

| Odd-number Address Word           | First bus cycle  | 0   | 1   | 2               |

|                                   | Second bus cycle | 1   | 0   |                 |

| Even-number Address Byte          |                  | 1   | 0   | 1               |

| Odd-number Address Byte           |                  | 0   | 1   | 1               |

The word operand of an odd-number address is accessed twice, i.e., in terms of the odd-number byte bank and the even-number byte bank. In the course of the access, "AD0=1" which indicates the odd-number address bank is output in the first bus cycle; and in the second bus cycle, "AD0=0" is automatically output in order to indicate the continuing even-number address bank. Each of the pins for 3-stated output. During hold acknowledge or interrupt acknowledge, they become high-impedance. In standby mode, they are fixed to either a high or low level.

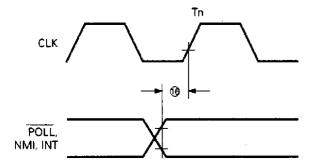

# (4) NMI (Non-Maskable Interrupt) ... Small/Large Scale

NMI is a non-maskable interrupt request signal input, which cannot be masked by software.

This signal is rising edge active, and is sampled in any clock cycle. However, interrupt processing is initiated after completing the current instruction execution.

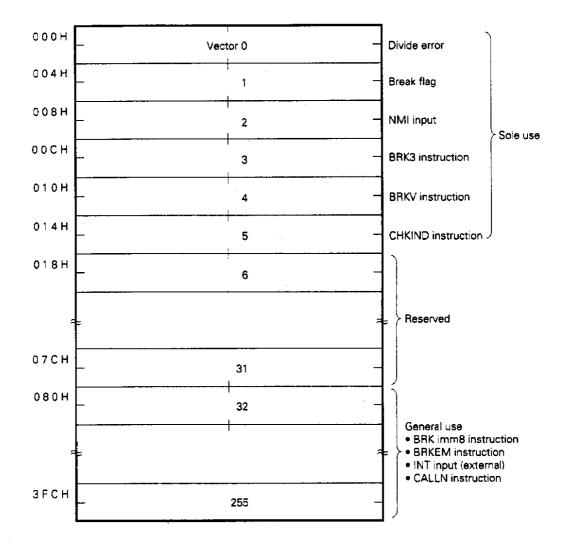

The interrupt start address for this interrupt is determined by interrupt vector 2.

The NMI signal must be held at high level, at least for five clock periods, after the rising edge.

The priority order for the NMI interrupt is as indicated below. The hold request is accepted during NMI

acknowledge cycles.

INT < NMI < HLDRQ (small scale) or RQ (large scale)

This interrupt is also used to release the standby mode.

#### (5) INT (Maskable Interrupt) .... Small/Large Scale

INT is a maskable interrupt request signal input, which can be masked by software.

This input is high level active and is sampled in the last clock period of an instruction. It is accepted, when interrupt is enabled (the interrupt enable flag (IE) is set). The external device checks whether or not the interrupt is accepted by the INTAK signal output from the CPU.

The INT signal must be held at high level at least until the first INTAK signal is output.

The priority order is as shown below. If NMI is simultaneously generated, the priority is given to the NMI, and INT will not be accepted. The hold request can be accepted during INT acknowledge cycles.

INT < NMI < HLDRQ (small scale) or RQ (large scale)

This interrupt is also used to release the standby mode.

#### (6) CLK (Clock) ... Small/Large Scale

CLK is the external clock input. The power supply current can be significantly reduced by stopping this CLK input (DC level). However, if the CLK input is halted while the RESET input is active (high level), the source current specifications are not satisfied.

#### (7) RESET (Reset) ... Small/Large Scale

RESET is the high level active CPU reset input. This input has priority over any other operation.

After reset, the CPU starts program execution from address FFFF0H.

The RESET input is used for normal CPU start. In addition, the RESET input is also used for releasing the standby mode.

Do not stop the clock input when making the RESET input active.

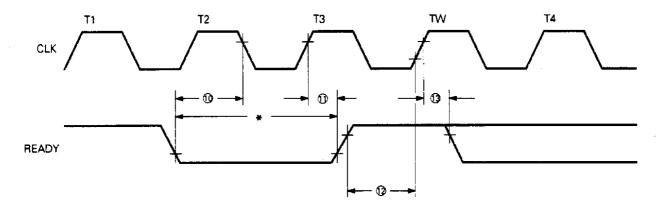

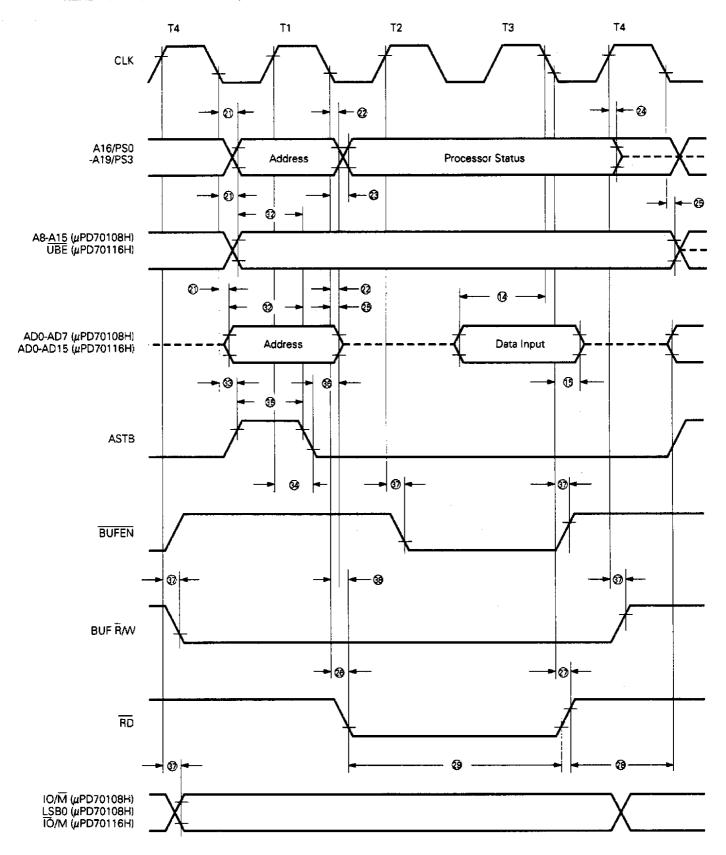

#### (8) READY (Ready) ... Small/Large Scale

When the memory or I/O cannot complete read/write operation within the basic CPU access time, this signal can be set to inactive (low level) to request the CPU to generate wait state (TW), in order to extend the read/write cycle.

The CPU will not generate wait state, if the READY signal is active (high level) during T3 or TW states.

The setup/hold time for this signal must be satisfied; otherwise, no correct operation can be guaranteed.

Therefore, external synchronization is necessary.

#### (9) POLL (Poll) ... Small/Large Scale

The POLL input is sampled by the POLL instruction. If this signal is low when checked, the processing moves to the next instruction execution. If it is high, the POLL input is sampled every 5 clock periods, until it becomes low.

This function is used to synchronize the CPU program with the external device operation.

#### (10) INTAK (Interrupt Acknowledge) ... Small Scale

INTAK signal is output, when an INT signal is accepted. The external device inputs the interrupt vector to the CPU through the data bus (AD7-AD0) in synchronization with this signal.

This output is fixed to high level in the standby mode.

#### (11) ASTB (Address Strobe) ... Small Scale

ASTB is the address strobe signal, used to latch the address information into the external latch. In standby mode, fix this pin to low level after setting it to a high level (for about 1/2 of a clock cycle).

#### (12) BUFEN (Buffer Enable) ... Small Scale

BUFEN signal is used as the external bi-directional buffer output enable signal. This signal is output, when transferring data between the memory and I/O or when inputting interrupt vector.

The BUFEN output is fixed to high during the standby mode.

This pin is a 3-state output, and becomes high impedance during hold acknowledge cycles.

#### (13) BUF R/W (Buffer Read/Write) ... Small Scale

BUF R/W signal is output to determine the data transfer direction for the external bi-directional buffer. High indicates CPU-to-external device transfer. Low indicates data transfer from the external device to the CPU.

The BUF R/W output is fixed to high or low during the standby mode.

This pin is a 3-state output, and becomes high impedance during hold acknowledge cycles.

## (14) IO/M (IO/Memory) ... Small Scale (μPD70108H)

IO/M signal distinguishes between I/O access and memory access. Low indicates I/O access, and high indicates memory access.

The IO/M output is fixed to high or low during the standby mode.

This pin is a 3-state output. It becomes high impedance during hold acknowledge cycles.

# (15) IO/M (IO/Memory) ... Small Scale (μPD70116H)

The signal for distinguishing the I/O access from the memory access is output. I/O is displayed at low; memory is displayed at high.

In standby mode, this output is fixed either to a high or low level.

This pin is for tri-state output. During hold acknowledge, it becomes high-impedance.

#### (16) WR (Write Strobe) ... Small Scale

$\overline{\text{WR}}$  signal is output, when writing to I/O or memory. Whether write operation is performed to the I/O or memory is determined by the IO/ $\overline{\text{M}}$  signal ( $\mu$ PD70108H) or  $\overline{\text{IO}}/\text{M}$  signal ( $\mu$ PD70116H).

The WR output is fixed to high, during the standby mode.

This pin is a 3-state output, and becomes high impedance during hold acknowledge cycles.

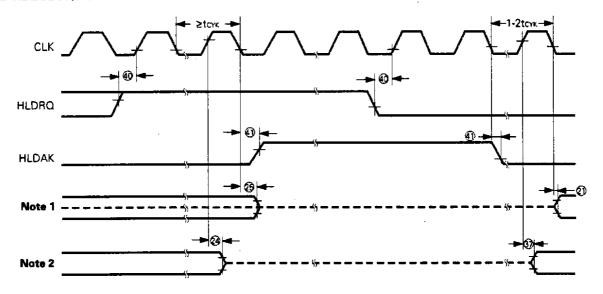

#### (17) HLDAK (Hold Acknowledge) ... Small Scale

HLDAK is the hold acknowledge signal, which indicates that the CPU has accepted the hold request (HLDRQ).

The address bus, address/data bus, and 3-state output control bus become high impedance when this pin is active.

#### (18) HLDRQ (Hold Request) ... Small Scale

HLDRQ signal is used by an external device to request the CPU for the release of the address bus, address/data bus, and the control bus.

The setup time for this signal must be satisfied; otherwise, no correct operation can be guaranteed. Therefore, external synchronization is necessary.

# (19) RD (Read Strobe) ... Small/Large Scale

RD signal is output when reading from I/O or memory. Whether read operation is performed with the I/O or memory is determined by the IO/M signal ( $\mu$ PD70108H) or IO/M signal ( $\mu$ PD70116H).

RD signal is provided basically for the small scale mode. However, this signal is output in the same timing in the large scale mode.

The RD output is fixed to high, during the standby mode.

This pin is a 3-state output, and becomes high impedance during hold acknowledge cycles.

#### (20) S/LG (Small/Large) ... Small/Large Scale

S/LG signal is used to determine the CPU operation mode. S/LG signal must be fixed to high or low. When set to high, the CPU operates in the small scale mode. When set to low, the CPU operates in the large scale mode.

Functions of pins listed below change, depending on the mode selected. These individual pins are assigned with different names as follows:

| Pin No. |     | •   | Pin Name                                 |                                         |  |

|---------|-----|-----|------------------------------------------|-----------------------------------------|--|

| DIP     | QFP | QFJ | In small-scale mode<br>(S/LG=High level) | in large-scale mode<br>(S/LG=Low level) |  |

| 24      | 38  | 27  | INTAK                                    | QS1                                     |  |

| 25      | 39  | 28  | ASTB                                     | QSO                                     |  |

| 26      | 41  | 29  | BUFEN                                    | BS0                                     |  |

| 27      | 42  | 30  | BUFR/W                                   | BS1                                     |  |

| 28      | 43  | 31  | IO/M (μPD70108H)                         | BS2                                     |  |

|         |     |     | ĪŌ/M (μPD70116H)                         |                                         |  |

| 29      | 44  | 32  | WR                                       | BUSLOCK                                 |  |

| 30      | 45  | 33  | HLDAK                                    | RQ/AK1                                  |  |

| 31      | 47  | 34  | HLDRQ                                    | RQ/AKO                                  |  |

| 34      | 50  | 37  | LBS0 (μPD70108H)                         | (Outputs high level)                    |  |

#### (21) LBS0 (Latched Bus Status 0) ... Small Scale (µPD70108H)

This signal is used in conjunction with the  $IO/\overline{M}$  and BUFR/W signal to externally indicate the type of the current bus cycle.

| IO/M | BUFR/W | LBS0 | Type of Bus Cycle     |

|------|--------|------|-----------------------|

| 0    | 0      | 0    | Program fetch         |

| 0    | 0      | 1    | Memory read           |

| 0    | 1      | 0    | Memory write          |

| o    | 1      | 1    | Passive state         |

| 1    | 0      | 0    | Interrupt acknowledge |

| 1    | 0      | 1    | I/O read              |

| 1    | 1      | 0    | I/O write             |

| 1    | 1      | 1    | Halt                  |

Remark Outputs high level in large-scale mode.

# (22) UBE (Upper Byte Enable) ... Small/Large Scale (μPD70116H)

This pin outputs the signal which indicates that the upper 8 bits (AD8 to AD15) of AD0 to AD15 are used in bus cycles T2 to T4.

The UBE signal becomes active (low level) during bus cycles T1 to T4. The bus cycles in which this signal becomes active include the following:

- · Bus cycle by the byte access to an odd-number address

- . Bus cycle by the first byte access to an odd-number address for the purpose of word data

- · Bus cycle by the access to an even-number address for the purpose of word data

Each cycle can be identified based on a combination of the address information and the UBE signal which are output during bus cycle T1 by the AD0 pin.

| Operand                  | i                | UBE | AD0 | Bus Cycle Count |  |  |

|--------------------------|------------------|-----|-----|-----------------|--|--|

| Even-number Address Word |                  | 0   | 0   | 1               |  |  |

| Odd-number Address Word  | First bus cycle  | 0   | 1   | 2               |  |  |

|                          | Second bus cycle | 1   | 0   |                 |  |  |

| Even-number Address Byte |                  | 1   | 0   | 1               |  |  |

| Odd-number Address Byte  | 0                | 1   | 1   |                 |  |  |

The UBE signal continues to be at a low level during interrupt acknowledge (word access of an evennumber address is required due to vector reading).

This pin is for tri-stated output. During hold acknowledge. It becomes high-impedance. In standby mode, it is fixed to a high level.

#### (23) A16/PS0-A19/PS3 (Address Bus/Processor Status) ... Small/Large Scale

A16/PS0-A19/PS3 serve as bits 16 to 19 of the address bus. They also serve as the processor status signal. These contents are output in multiplexed mode.

The upper 4 bits in the 20-bit memory address are output. During I/O access, all bits output 0.

The processor status signal is output for both memory and I/O accesses. PS3 is always set to 0 in the native mode, and 1 in the emulation mode. PS2 outputs the contents of the interrupt enable flag (IE). PS1 and PS0 indicate which segment is currently used.

| A17/PS1 | A16/PS0 | Segment         |

|---------|---------|-----------------|

| 0       | 0       | Data segment 1  |

| 0       | 1       | Stack segment   |

| 1       | 0       | Program segment |

| .1      | 1       | Data segment 0  |

These outputs are fixed to high during the standby mode.

The A16/PS0-A19/PS3 pins are 3-state outputs, and become high impedance during hold acknowledge cycles.

# (24) QS0, QS1 (Queue Status) ... Large Scale

QS0 and QS1 inform the external device (floating-point operation coprocessor) of the internal instruction queue status for the CPU.

| QS1 | QS0 | Instruction Queue Status                 |

|-----|-----|------------------------------------------|

| 0   | ٥   | No operation (no change in queue status) |

| 0   | 1   | First byte of instruction                |

| 1   | 0   | Empty                                    |

| 1   | 1   | After first byte of instruction          |

"Instruction queue status" indicates the status, when the EXU accesses the instruction queue. The contents output to QS0 and QS1 are effective only in the first clock period, immediately after the instruction queue is accessed.

This status signal is provided for the floating-point operation coprocessor to monitor the CPU's program execution status, so that the coprocessor can perform processing in synchronization with the CPU when the control is transferred (by FPO: Floating-Point Operation instruction).

These outputs are fixed to low in the standby mode.

#### (25) BS0-BS2 (Bus Status) ... Large Scale

BS0-BS2 are encoded to indicate the current bus cycle category to the external bus controller.

The external bus controller decodes these signals and generates a control signal for accessing the memory or I/O.

| BS2 | B\$1 | BS0 | Type of Bus Cycle     |

|-----|------|-----|-----------------------|

| 0   | 0    | 0   | Interrupt acknowledge |

| 0   | 0    | 1   | I/O read              |

| 0   | 1    | 0   | I/O write             |

| 0   | 1    | 1   | HALT                  |

| 1   | 0    | 0   | Program fetch         |

| 1   | 0    | 1   | Memory read           |

| 1   | 1    | 0   | Memory write          |

| 1   | 1    | 1   | Passive state         |

These outputs are fixed to high in the standby mode.

These pins are 3-state outputs. They become high impedance during hold acknowledge cycles.

These signals are high during the period from the rising edge of the clock immediately after RESET becomes active to the next rising edge of the clock. After the one clock cycle, these signals become high impedance.

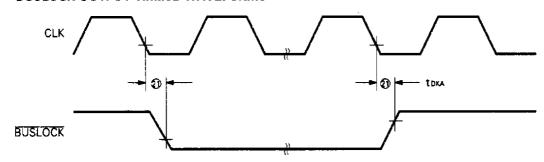

#### (26) BUSLOCK (Bus Lock) ... Large Scale

BUSLOCK is used to request other master CPUs in a multi-processor system not to use the system bus, when executing one instruction which follows the BUSLOCK prefixed instruction.

This output is fixed to high during the standby mode. (However, if the BUSLOCK instruction is placed before the HALT instruction, this signal is fixed to low during the standby mode.)

This pin is a 3-state output, and becomes high impedance during hold acknowledge cycles.

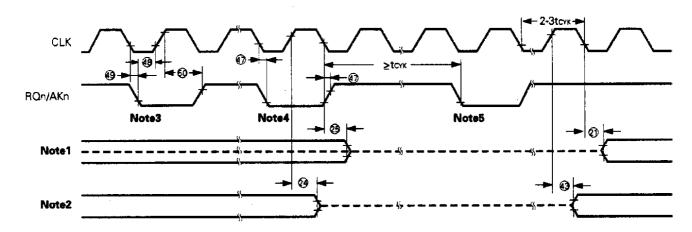

# (27) RQ/AK1, RQ/AK0 (Hold Request/Acknowledge) ... Large Scale

$\overline{RQ}/\overline{AK1}$  and  $\overline{RQ}/\overline{AK0}$  serve as the bus hold request input pins ( $\overline{RQ}$ ) and the bus hold acknowledge signal output pins ( $\overline{AK}$ ). The priority is as indicated below:

RQ/AK1 < RQ/AK0

These pins are 3-state inputs/outputs, and are provided with internal pull-up resistors. These pins are set to inactive state (high level) when open (float).

When used for bus hold request input (RQ), the setup/hold time for this signal must be satisfied; otherwise, no correct operation can be guaranteed. Therefore, external synchronization is necessary.

- (28) Vpb (Power Supply) ... Small/Large Scale Positive voltage power supply pins.

- (29) GND (Ground) ... Small/Large Scale GND.

- (30) IC (internally Connected)

IC must be set to GND potential level.

#### 2. REGISTER CONFIGURATION

#### 2.1 PFP (PREFETCH POINTER)

The prefetch pointer is a 16-bit binary counter, which retains the program memory address offset information for the instruction to be prefetched to the instruction queue by the BCU.

The PFP is incremented each time an instruction byte is prefetched from the program memory by the BCU. When branch, call, return, or break instruction is executed, a new location is loaded into the PFP. In this case, the PFP contents become the same as those for the PC (Program Counter).

The PFP is always used, together with PS (Program Segment) register.

#### 2.2 Q0-Q3, Q0-Q5 (PREFETCH QUEUES)

The  $\mu$ PD70108H contains a 4-byte instruction queue (FIFO), which can store up to 4 bytes of instruction code prefetched by the BCU. The  $\mu$ PD70116H is equipped with a 6-byte instruction queue (FIFO) and thus capable of storing up to 6 bytes of instruction codes prefetched by BCU.

The instructions stored in the queue are executed by the EXU.

The queue contents are cleared, when a branch, call, return, or break instruction is executed or external interrupt is processed, and an instruction at a new location will be prefetched.

Normally, the  $\mu$ PD70108H performs prefetching if there is an unused space of at least 1 byte available in the queue; and the  $\mu$ PD70116H does so if at least 1 word (2 bytes) is available.

When successively executing a number of instructions, if the average instruction execution time is faster than the number of clock periods necessary to prefetch each instruction code, when an instruction execution is completed, the next instruction code to be executed by the EXU is already provided in the queue. Therefore, the time necessary to fetch an instruction from the external memory can be excluded from the instruction execution time. As a result, the processing speed can be improved, compared to a CPU which fetches and executes instructions one at a time.

The queue effectiveness decreases as the number of instructions, which clear the queue, increases or the number of instructions, having shorter instruction execution time, increases.

# 2.3 DP (DATA POINTER)

The data pointer is a 16-bit register, which specifies the variable read/write address.

The effective address, generated by the EAG, and the contents of the register, including the memory address offset, are transferred to the data pointer.

#### 2.4 TEMP (TEMPORARY COMMUNICATION REGISTER)

TEMP is a 16-bit temporary register used for communication between the external data bus and the EXU. The TEMP can be accessed in byte units. Therefore, the upper byte and the lower byte can be independently read/written.

Basically, the EXU completes write operation when data is transferred to the TEMP; it completes read operation when confirming that data is transferred from an external data bus to TEMP.

#### 2.5 SEGMENT REGISTERS (PS, SS, DS0, DS1)

In the  $\mu$ PD70108H and  $\mu$ PD70116H, memory addresses are divided into logical segments, which are 64K bytes each. The start address for each segment register is specified by the corresponding segment register. The offset from the start address is specified by a different register or by the effective address.

The  $\mu$ PD70108H contains the following four kinds of segment registers.

| Segment Register     | Default Offset        |  |  |  |  |  |

|----------------------|-----------------------|--|--|--|--|--|

| PS (Program Segment) | PFP                   |  |  |  |  |  |

| SS (Stack Segment)   | SP, Effective address |  |  |  |  |  |

| DS0 (Data Segment 0) | IX, Effective address |  |  |  |  |  |

| DS1 (Data Segment 1) | IY                    |  |  |  |  |  |

The PS and the PFP (Prefetch Pointer), and the DS1 and the IY registers are always paired.

The SS is normally paired with the SP. However, when the BP register is selected as the base register, effective address is used as the offset.

The DS0 is used together with the IX register for block transfer processing. However, for other general processing, the effective address is used as the offset.

In addressing using the BP register as the base register and the SS register as the segment register, any one of three other registers can be selected as the segment selection, using the the segment override prefix instruction (PS:, DS0:, DS1:). However, eight or more prefix instructions cannot be attached to other than prefix instructions.

#### 2.6 ADM (ADDRESS MODIFIER)

ADM (Address Modifier) is used for generating a physical address (addition of segment register and PFP or DP), and increments the PFP (Prefetch Pointer).

#### 2.7 GENERAL-PURPOSE REGISTERS (AW, BW, CW, DW)

The  $\mu$ PD70108H contains four 16-bit registers. Each of these 16-bit registers can be used as a 16-bit register. In addition, each of these 16-bit registers can be divided into upper and lower 8 bits, so that each can be accessed as an 8-bit register (AH, AL, BH, BL, CH, CL, DH, DL).

Therefore, these registers can be used as 8-bit or 16-bit registers for various instructions, such as transfer, arithmetic operation, logical operation instruction, etc.

These registers are used as default registers for certain instruction processings as follows:

AW: Word multiplication/division, word input/output, BCD rotation, data conversion

AL : Byte multiplication/division, byte input/output, BCD rotation, data conversion

AH: Byte multiplication/division

BW: Data conversion

CW: Loop control branch, repeat prefix

CL: Shift instruction, rotate instruction, BCD operation

DW: Word multiplication/division, indirect addressing input/output

# 2.8 POINTERS (SP, BP) AND INDEX REGISTER (IX, IY)

SP and BP, and IX and IY are used as the base pointers or index registers, when accessing the memory in the based addressing mode, indexed addressing mode, etc.

In the same way as for general-purpose registers, these pointers and index registers are used for transfer, arithmetic, or logical operation instructions. However, in this case, these pointers and index registers cannot be used as 8-bit registers.

These registers are used as default registers for certain instruction processing, as follows:

SP: Stack manipulation

IX : Block transfer (source side), BCD string operation

IY: Block transfer (destination side), BCD string operation

#### 2.9 TA/TB (TEMPORARY REGISTER/SHIFTER A/B)

TA/TB is a 16-bit temporary register/shifter used for multiplication/division, and shift/rotate (including BCD rotate) instructions.

When executing a multiplication/division instruction, TA and TB are paired to form a 32-bit temporary register/shifter. When executing a shift/rotate instruction, only the TB serves as the 16-bit temporary register/shifter.

The upper and lower bytes individually for TA and TB can be independently read/written through the internal bus.

TA/TB becomes the ALU input.

#### 2.10 TC (TEMPORARY REGISTER C)

TC is a 16-bit temporary register, used for multiplication, division, and other internal processings.

The TC becomes the ALU input.

#### 2.11 ALU (ARITHMETIC & LOGIC UNIT)

ALU (Arithmetic Logic Unit) consists of the full adder and the logic operation circuit, and performs arithmetic operations (addition, subtraction, increment, decrement, and complement operations) and logical operations (test, AND, OR, XOR, and test, set, clear, and invert in bit units).

#### 2.12 PSW (PROGRAM STATUS WORD)

The program status word consists of six status flags and four control flags.

#### Status flags

- V (Overflow)

- · S (Sign)

- Z (Zero)

- AC (Auxiliary Carry)

- P (Parity)

- · CY (Carry)

#### Control flags

- · MD (Mode)

- · DIR (Direction)

- IE (Interrupt Enable)

- · BRK (Break)

These flags are manipulated in the stack in the following word image:

| 15     | 14 | 13 | 12 | 11 | 10     | 9 | 8   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | •   |

|--------|----|----|----|----|--------|---|-----|---|---|---|---|---|---|---|---|-----|

| M<br>D | 1  | 1  | 1  | ٧  | D<br>R | E | *XB | s | z | 0 | Ĉ | 0 | Р | 1 | C | PSW |

Status flags are automatically set or reset, according to instruction execution results (data value).

The CY flag can be directly set, reset, or inverted by an instruction.

The control flags are set or reset by an instruction, in order to control the CPU operation.

The MD flag can be modified only from the BRKEM instruction execution to the RETEM instruction. In other locations, the MD flag cannot be restored by executing the RETI or POP PSW instruction.

# 2.13 LC (LOOP COUNTER)

LC (Loop Counter) is a 16-bit register, which counts the number of loops for primitive block transfer, input/output instructions (MOVBK, OUTM, etc.) controlled by repeat prefix instructions (REP, REPC, etc.), or the number of shifts for multiple bit shift/rotate instructions.

#### 2.14 PC (PROGRAM COUNTER)

PC (Program Counter) is a 16-bit binary counter, which retains the offset information for the program memory address in the instruction to be executed next by the EXU.

The PC is incremented each time the decoder fetches an instruction byte from the instruction queue. When a branch, call, return, or break instruction is executed, a new address location is loaded into the PC, in this case, the PC contents become the same as those for the PFP (Prefetch Pointer).

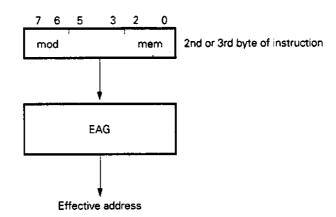

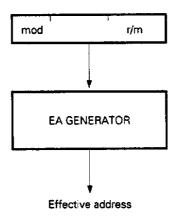

# 2.15 EAG (EFFECTIVE ADDRESS GENERATOR)

EAG (Effective Address Generator) logic computes an effective address necessary for accessing the memory at high speed. An address computation is completed in two clock period in any addressing mode.

The byte (2nd or 3rd byte) in which the instruction operand is specified is clocked in. If memory accessing is necessary, the EAG generates a control signal necessary for manipulating the ALU and related register, computes the effective address, and transfers it to the data pointer (DP).

In addition, the EAG requests a bus cycle (memor read) to the BCU as necessary.

#### 2.16 INSTRUCTION DECODER

The instruction decoder classifies the first byte in the instruction code into a group by function, and retains it during macro execution.

#### 2.17 MICROADDRESS REGISTER

The microaddress register specifies the microinstruction ROM address to be executed next.

The first byte for the instruction stored in the queue is clocked into this register as the start address to indicate the specified microinstruction sequence start address, when starting the microinstruction execution.

#### 2.18 MICROINSTRUCTION ROM

The microinstruction ROM contains 1024 words of 29-bit wide microinstructions.

# 2.19 MICROINSTRUCTION SEQUENCE CIRCUIT

This circuit manages microaddress register control, microinstruction ROM output control, and EXU and BCU synchronization.

# INCREASING INSTRUCTION EXECUTION SPEED

The  $\mu$ PD70108H and  $\mu$ PD70116H are provided with the following hardware functions in order to reduce the instruction execution time:

- · EXU internal dual data bus

- · Effective address generator

- 16/32-bit temporary register/shifter (TA, TB)

- 16-bit loop counter (LC)

- PC (Program Counter) and PFP (Prefetch Pointer)

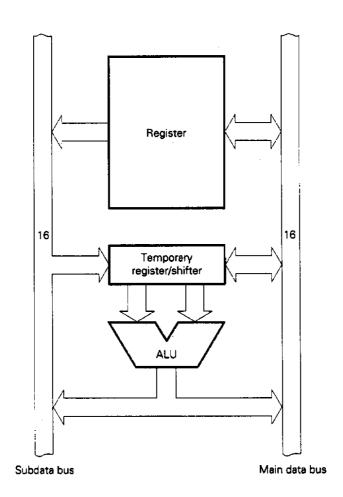

#### 3.1 DUAL DATA BUS METHOD

In order to reduce the number of processing steps necessary for instruction execution, a dual data bus concept, with the main data bus (16 bits) and the sub data bus (16 bits), is employed. With this concept, the processing time is reduced approximately 30%, compared to the processing time for a single bus system in implementing addition, subtraction, logic operation, and compare instructions.

Example: ADD AW, BW; AW ← AW+BW

3

Dual bus Single bus ALU ← AW ALU ← AW, BW Step 1 2 ALU ← BW AW ← ALU AW ← ALU

# 3.2 EFFECTIVE ADDRESS GENERATOR

The effective address generator computes at a high speed an effective address necessary for accessing the memory.

In the microprogram method, it took 5 to 12 clock periods to compute an effective address. However, with this sole use hardware, an effective address can be computed in two clock period for any addressing mode.

#### 3.3 16/32-BIT TEMPORARY REGISTER/SHIFTER (TA, TB)

The temporary register/shifter (TA, TB) are provided for multiplication, division, shift, and rotate instructions. With this circuit, especially, multiplication and division instruction execution speed is increased to approximately 4 time faster than a method using the microprogram.

TA+TB: 32-bit temporary register/shifter

- For multiplication/division instructions

TB: 16-bit temporary register/shifter

- For shift/rotate instructions

#### 3.4 LOOP COUNTER (LC)

The loop counter (LC) counts the number of loops for primitive block transfer, and input/output instructions controlled by the repeat prefix instruction, or counts the number of shifts for the multiple-bit shift/rotate instructions.

For example, register multiple-bit rotation will be performed as shown below, and the processing speed is increased approximately 2 time faster than that of microprogram method.

RORC AW, CL; CL = 5

Microprogram method

LC method

$8 + 4 \times 5 = 28$  clocks

7 + 5 = 12 clocks

#### 3.5 PC AND PFP

With the prefetch pointer (PFP), which addresses the program memory when prefetching an instruction, and the program counter (PC), which addresses the program memory for the current instruction execution, provided by hardware, the instruction execution time is reduced by several clock periods for branch, call, return, and break instructions, compared to that for the PFP only.

# 4. UNIQUE $\mu$ PD70108H INSTRUCTIONS

# 4.1 VARIABLE BIT FIELD MANIPULATION INSTRUCTIONS

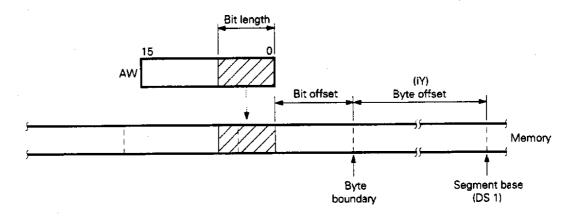

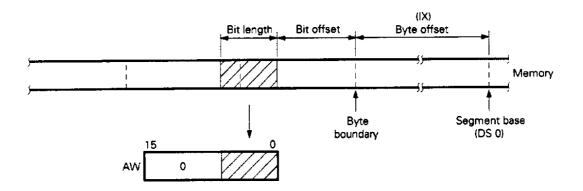

The INS (Insert Bit Field) and EXT (Extract Bit Field) instructions are provided as variable bit field manipulation instructions. These instructions are very effective for computer graphics and high level language. For example, these instructions are effective for Pascal packed array and record type data structure.

#### (1) INS reg8, reg8'/INS reg8, imm4

Of the 16 bits of data contained in the AW register, the data for the lower bits, specified by the second operand, is transferred to the memory area determined by the byte offset addressed by the DS1 segment register and IY indexed register plus the bit offset specified by the value (0-15) for the first operand.

After the transfer, the IY register and the register, specified by the first operand, are automatically updated to indicate the next bit field.

Only 0-15 (0 specifies 1-bit length, 15 specifies 16-bit length) are effective as the value for the second operand.

Bit field data can cross memory byte boundaries.

# (2) EXT reg8, reg8'/EXT reg8, imm4

Data for the bit field, whose length is specified by the second operand, is loaded from the memory area determined by the byte offset addressed by the DS0 segment register and IX indexed register, plus the bit offset specified by the value (0-15) for the first operand to the AW register.

After the transfer, the IX register and the register specified by the first operand are automatically updated to indicate the next bit field.

Only 0-15 (0 specifies 1 bit length, 15 specifies 16 bit length) are effective as the value for the second operand.

Bit-field data can cross memory byte boundaries.

#### 4.2 PACKED BCD OPERATION INSTRUCTIONS

The ADD4S, SUB4S, and CMP4S instructions process packed BCD as strings. The ROR4 and ROL4 instructions process packed BCD as byte or word format operands.

#### (1) ADD4S

This instruction adds the packed BCD string, addressed by the IX index register, to the packed BCD string, addressed by the IY index register, and stores the result in the string, addressed by the IY register. The length of the string (number of BCD digits) is specified by the CL register, and the operation result will affect the zero (Z) and carry (CY) flags.

BCD string (IY,CL) ← BCD string (IY,CL) + BCD string (IX,CL)

#### (2) SUB4S

This instruction subtracts the packed BCD string, addressed by the IX index register, from the packed BCD string, addressed by the IY index register, and stores the result in the string, addressed by the IY register. The length of the string (number of BCD digits) is specified by the CL register, and the operation result will affect the zero (Z) and carry (CY) flags.

BCD string (IY,CL) ← BCD string (IY,CL) – BCD string (IX,CL)

#### (3) CMP4S

This instruction performs the same operation as SUB4S, except that the result is not stored and only the zero flag (Z) and carry flag (CY) are affected.

BCD string (IY,CL) - BCD string (IX,CL)

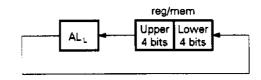

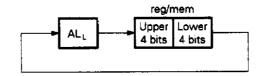

#### (4) ROL4

This instruction treats the byte data for the register or memory operand specified by the instruction as BCD data and uses the lower 4 bits of the AL register (ALL) to rotate that data one BCD digit to the left.

# (5) ROR4

This instruction treats the byte data for the register or memory operand specified by the instruction as BCD data and uses the lower 4 bits of the AL register (ALL) to rotate that data one BCD digit to the right.

#### 4.3 STACK MANIPULATION INSTRUCTIONS

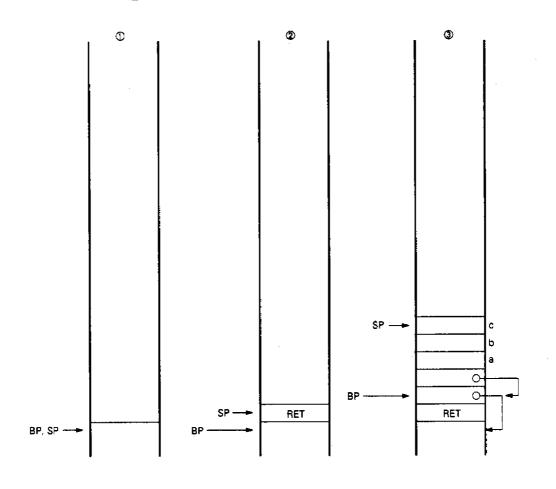

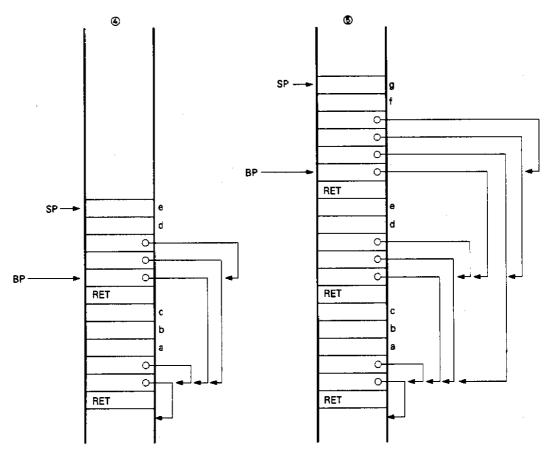

#### (1) PREPARE imm16.imm8

This instruction is used to generate a "stack frame" necessary for a block structure high level language (such as Pascal and Ada). The stack frame contains the pointers to point frames of variables that can be referenced from the procedure, and local variable area.

The following explanation uses the following program example written in a Pascal style language.

```

program EXAMPLE;

procedure P;

var a,b,c;

procedure Q;

var d,e;

procedure R;

var f,g;

begin

d:=a+f+g;

end:

begin

R:

b:=d+e;

end;

begin

a:=b+c;

Q;

end;

(*main program*)

begin

P;

end.

```

Remark All variables are word variables.

In this program, procedure blocks are nested in three levels. Procedure P defines variables a, b, and c, procedure Q defines variables d and e, and procedure R defines variables f and g. Therefore, a, b, and c are referenced from procedure Q, and d and e in addition to a, b, and c, are referenced from procedure R as global variables.

The PREPARE instruction copies the frame pointer, in order to assure local variable area and enable referencing to global variables. The first operand specifies the size (bytes) of the area assured for the local variables. The second operand indicates the depth of the procedure block (this depth is referred to as lexical level).

The base address for the frame generated by the PREPARE instruction is set into the base pointer BP. When the above EXAMPLE program is compiled, the assembler program, shown on the next page will be created (the DISPOSE instruction used in the assembler program returns the stack pointer SP and the base pointer BP to the condition which existed before the PREPARE instruction was executed. Refer to (2)).

## :ASSEMBLER PROGRAM

| START | : MOV<br>MOV | SP, SPTOP<br>BP, SP ; ①          |

|-------|--------------|----------------------------------|

|       | CALL         | P ; ②                            |

|       | BR           | SYSTEM                           |

| P:    | PREPARE      | 6, 1 ; ③                         |

|       | MOV          | AW, [BP] [B+BLEVEL*2]            |

|       | ADD          | AW, [BP] [C+CLEVEL*2]            |

|       | MOV          | [BP] [A+ALEVEL*2], AW            |

|       | CALL         | Q                                |

|       | DISPOSE      |                                  |

|       | RET          |                                  |

| Q:    | PREPARE      | 4, 2 ; ④                         |

|       | CALL         | R                                |

|       | MOV          | AW, [BP] [D+DLEVEL*2]            |

|       | ADD          | AW, [BP] [E+ELEVEL*2]            |

|       | MOV          | IY, [BP] [BLEVEL*2]              |

|       | MOV          | SS:[IY] [B+BLEVEL*2], AW         |

|       | DISPOSE      |                                  |

| ,     | RET          |                                  |

| R:    | PREPARE      | 4, 3 ; (5)                       |

|       | MOV          | AW, [BP] [F+FLEVEL*2]            |

|       | ADD          | AW, [BP] [G+GLEVEL*2]            |

|       | MOV          | IY, [BP] [ALEVEL*2]              |

|       | ADD          | AW,.SS:[IY] [A+ALEVEL*2], AW     |

|       | MOV          | IY, [BP] [DLEVEL*2]              |

|       | MOV          | SS:[IY] (D+DLEVEL*2), AW         |

|       | DISPOSE      |                                  |

|       | RET          |                                  |

|       |              |                                  |

| ; /   | 4 = -2 ALE   | /EL = -1                         |

| ; 6   | B = -4 BLE\  | /EL = -1                         |

|       |              |                                  |

| ; (   |              | /EL = -1                         |

| -     | D = -2 DEL\  | /EL = -1<br>/EL = -2<br>/EL = -2 |

; F = -2 FLEVEL = -3

GLEVEL = -3

; G = -4

The following shows the process in which stack frames are generated according to the program execution progress. The numbers correspond to the numbers written in the comment fields.

The PREPARE instruction first stores the BP into the stack. This is to restore the BP for the procedure which made the call, when the procedure is completed. The frame pointers (stored BP) in the range that can be referenced from the called procedure are then loaded into the stack. The range that can be referenced means a value which is the lexical level of the procedure minus 1.

If the lexical level is 1 or greater, the own frame pointer is also loaded into the stack. This is to copy the frame pointer for the procedure, which made the call, when copying the frame pointer in the procedure called from this procedure.

The value for the new frame pointer is then set into the BP, and the local variable area to be used by the procedure is assured in the stack. That is, the SP is decremented by the number of local variables.

```

display = 2nd operand

dynamics = 1st operand

SP = SP-2;

(SP) = BP;

temp = SP;

if display > 0 then begin

repeat display-1 times

begin

SP = SP-2;

BP = BP-2:

(SP) = (BP);

end

SP = SP-2;

(SP) = temp;

end

BP = temp;

SP = SP-dynamics

```

## **Data Access Method**

#### (a) Accessing local variable

A local variable is allocated in the procedure's own frame. Therefore, the effective address for the local variable EA.L can be computed as follows:

EA.L = SS:(BP+offset)

Where, offset value is the result of addition of the frame size (base value for the frame that can be referenced) loaded in the flame, with the offset value from the base value of the local variable area to the variable.

## (b) Accessing global variable

A global variable accesses the base pointer to be referenced from the old base pointers loaded in the stack frame, then add the offset value to the variable to be referenced to that value. This value is the address at which the global variable is located. Therefore, the the effective address for the global variable EA.G can be computed as follows:

EA.G = SS:((SS:(BP+offset1))+offset2)

Where, offset1 is the offset value from the base value (BP value) for the current frame to the address, in which the base address for frame containing the global variable is stored.

Offset2 is the offset value from the base value for the frame containing the variable to be referenced to that variable.

## (2) DISPOSE

The DISPOSE instruction releases one frame from stack frames generated by the PREPARE instruction. The point value, indicating the previous frame, is loaded into the BP, and the point value, indicating the bottom position of the frame, is loaded into the SP.

SP = BP;

BP = (SP);

SP = SP+2

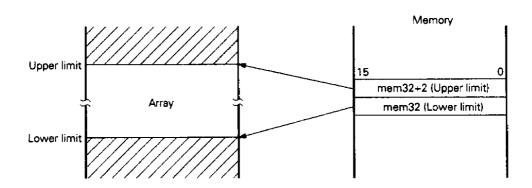

## 4.4 CHECK ARRAY BOUNDARY INSTRUCTION

This instruction is used to verify that index values, pointing to the elements of an array data structure, are within the defined range. If the index value is not between these defined ranges when CHKIND is executed, a BRK5 will occur.

When using the CHKIND instruction, the defined value must be set into 2 words (the 1st word defines the lower limit, the second word specifies the upper limit) in the memory in advance. The index value should be a register (an arbitrary 16-bit register) used by the array manipulation program.

CHKIND, reg 16, mem 32

PC ← TA

When (mem32) > reg16 or (mem 32+2) < reg16  $TA \leftarrow (015H, 014H)$   $TC \leftarrow (017H, 016H)$   $SP \leftarrow SP-2, (SP+1, SP) \leftarrow PSW$   $IE \leftarrow 0, BRK \leftarrow 0$   $SP \leftarrow SP-2, (SP+1, SP) \leftarrow PS$   $PS \leftarrow TC$   $SP \leftarrow SP-2, (SP+1, SP), \leftarrow PC$   $SP \leftarrow SP-2, (SP+1, SP), \leftarrow PC$

## 4.5 MODE MANIPULATION INSTRUCTIONS

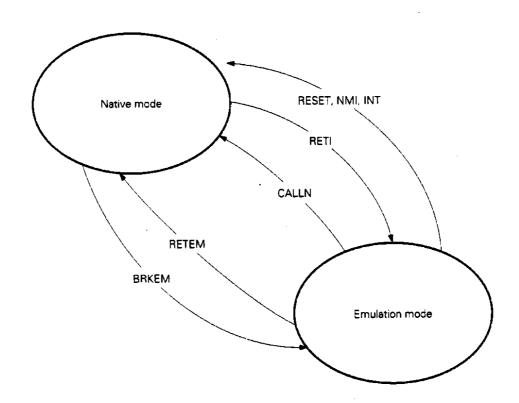

The  $\mu$ PD70108H and 70116H has two operation modes: native mode (normal operation mode) and emulation mode (emulates  $\mu$ PD8080AF instruction set). Bit 15 is provided as the mode flag to select these modes. Setting MD to 1 specifies the native mode, and 0 specifies the emulation mode.

The MD is directly or indirectly set/reset by the mode manipulation instruction.

The following instructions change the mode from the native mode to the emulation mode:

BRKEM (Break for Emulation) RETI (Return from Interrupt)

The following instructions change the mode from the emulation mode to the native mode:

RETEM (Return from Emulation)

CALLN (Call Native routine)

In addition, the mode returns from the emulation mode to the native mode, when a RESET is input or when an external interrupt is input (NMI, INT).

#### (1) BRKEM imm8

BRKEM is the basic instruction to initiate the emulation mode. This instruction stores the PSW, PS, and PC, resets the MD flag to 0, and loads the interrupt vector specified by the operand to the PS and PC. The interrupt enable flag (IE) and the break flag (BRK) are not affected by this instruction.

When an instruction code for interrupt service routine (for emulation) jumped in this manner is fetched, the CPU interprets and executes the instruction as an instruction of the  $\mu$ PD8080AF.

The CPU treats the emulation mode as an interrupt service.

In the emulation mode, the  $\mu$ PD8080AF registers and flags are substituted for by the following registers and flags:

| μPD70108H, 70116H |

|-------------------|

| AL                |

| СН                |

| CL                |

| DH                |

| DL                |

| ВН                |

| BL                |

| ВР                |

| PC                |

|                   |

| μPD8080AF | μPD70108H, 70116H |

|-----------|-------------------|

| С         | CY                |

| Z         | z                 |

| s         | s                 |

| Р         | Р                 |

| AC        | AC                |

For stack manipulation, SP serves as the stack pointer in the native mode. However, in the emulation mode, BP serves as the stack pointer. By employing an independent stack pointer, the stack area is assured independently for both modes, in order to prevent destroying the stack for some other mode by erroneous stack manipulation.

The SP, IX, IY, AH and four segment registers (PS, SS, DS0, DS1) used in the native mode are not affected by the emulation mode.

In the emulation mode, the segment base for the instruction is determined by the PS register (automatically determined by the interrupt vector), and the segment base of data is determined by the DS0 register (the programmer determines before entering the emulation mode).

### (2) RETEM (no operand)

When the RETEM instruction is executed in the emulation mode (the instruction is interpreted as the  $\mu$ PD8080AF instruction), the CPU restores the PS, PC, and PSW in the same way as when returning from an interrupt service, then returns to the native mode. In this case, the contents for the native mode (that is 1), stored in the stack by the BRKEM instruction, is restored. This sets the CPU to the native mode.

#### (3) CALLN imm8

When this instruction is executed in the emulation mode (the instruction is interpreted as the  $\mu$ PD8080AF instruction), the CPU stores the PS, PC, and PSW into the stack (MD=0 is stored here), sets the mode flag (MD) to 1, and loads the interrupt vector specified by the operand to the PS and PC.

The interrupt enable flag (IE) and the break flag (BRK) are not affected by this instruction. In this manner, the interrupt routine in the native mode can be called from the emulation mode. Use RETI instruction to return to the emulation mode from this interrupt routine.

#### (4) RETI (no operand)

The RETI instruction is generally used to return from an interrupt routine initiated by the BRK instruction or external interrupt in the native mode. However, if this instruction is executed at the end of the interrupt routine initiated by the CALLN instruction, PS, PC, and PSW are restored in the same way as normal. However, when the PSW is restored, the value (=0) for the mode flag (MD) for the emulation mode is restored to the MD. For this reason, the CPU is set to the emulation mode. Afterwards, instructions will be interpreted and executed as  $\mu$ PD8080AD instructions.

In the same manner, the RETI instruction is used to return from an interrupt routine for the native mode, initiated by NMI, or INT interrupt request, generated in the emulation mode.

# 4.6 FLOATING-POINT OPERATION COPROCESSOR CONTROL INSTRUCTIONS

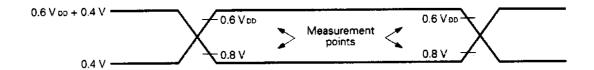

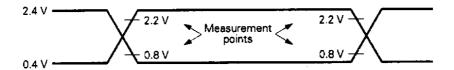

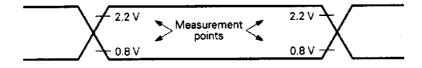

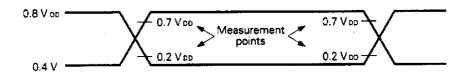

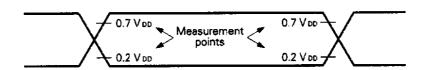

FPO1 fp-op/FPO1 fp-op, mem FPO2 fp-op/FPO2 fp-op, mem