## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# MOS INTEGRATED CIRCUIT $\mu$ PD78C17(A), 78C18(A)

#### 8-BIT SINGLE-CHIP MICROCOMPUTER (WITH A/D CONVERTER)

The  $\mu$ PD78C18(A) is an 8-bit CMOS microcomputer which integrates 16-bit ALU, ROM, RAM, an A/D converter, a multi-function timer/event counter, and a general-purpose serial interface onto a single chip, and whose memory (ROM/RAM) is externally expandable up to 31 Kbytes. The  $\mu$ PD78C18(A) can operate at low power consumption because of its CMOS architecure and is provided with a standby function that enables data retention with an even lower power consumption.

The  $\mu$ PD78C17(A) is the ROM-less version of the  $\mu$ PD78C18(A). Its memory (ROM/RAM) is expandable externally up to 63 Kbytes.

A detailed explanation of the functions is provided in the user's manual listed below. It should be read before starting design work. 87AD Series  $\mu$ PD78C18 User's Manual: IEU-1314

#### **FEATURES**

- High reliability compared with  $\mu$ PD78C17 and  $\mu$ PD78C18

- 159 types of instructions: 87AD series instruction set plus multiply/divide instructions and 16-bit operation instructions

- Instruction cycle: 0.8 μs (at 15-MHz operation)

- Internal ROM: 32768 x 8 bits (μPD78C18(A) only)

- Internal RAM: 1024 x 8 bits

- Up to 64 Kbytes of memory (ROM/RAM) can be directly addressed

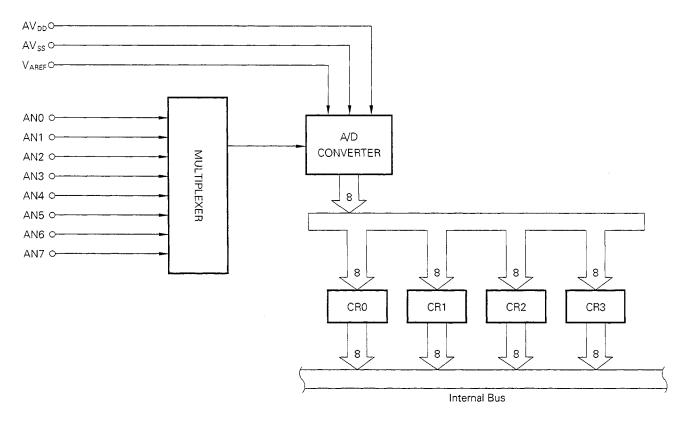

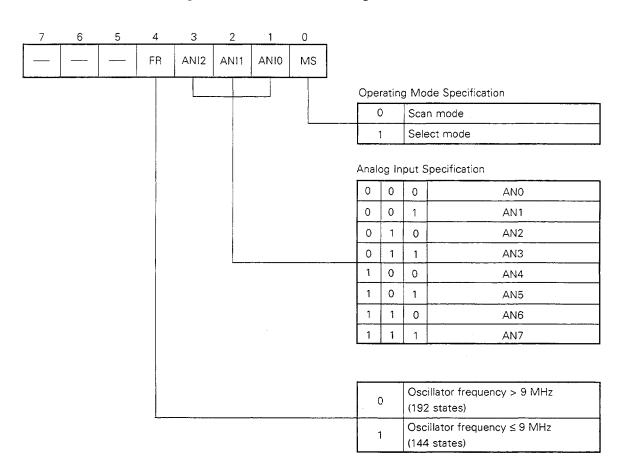

- High-resolution 8-bit A/D converter: 8 analog inputs

- General-purpose serial interface: Asynchronous, synchronous, I/O interface modes

- · Multi-function 16-bit timer/event counter

- Two 8-bit timers

- I/O lines Input/output ports

: 28 ( $\mu$ PD78C17(A)), 40 ( $\mu$ PD78C18(A))

Edge detection inputs: 4

• 11 interrupt functions external: 3, internal: 8

(Non-maskable: 1, maskable: 10)

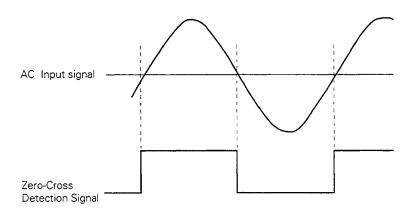

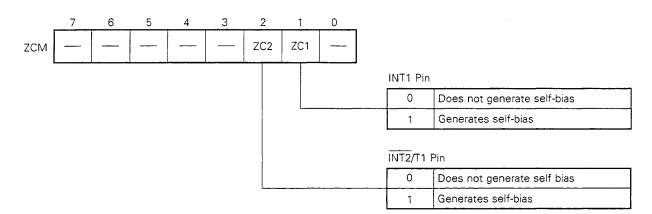

- Zero-cross detection function: (2 inputs)

- · Standby function: HALT mode, hardware/software STOP mode

- Mask option pull-up resistors can be incorporated into Ports A, B, and C: (μPD78C18(A) only)

#### **ORDERING INFORMATION**

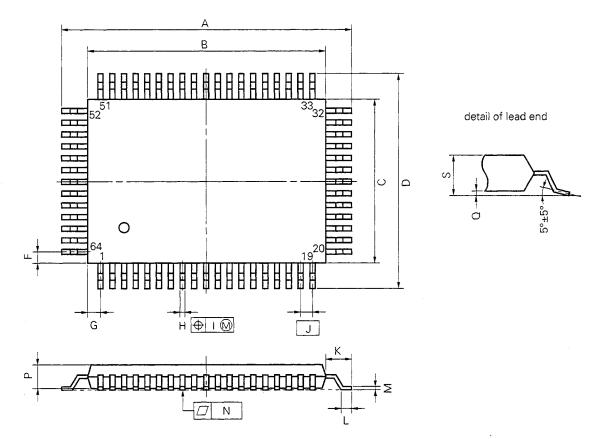

| Part Number           | Package                        | Quality Grade |

|-----------------------|--------------------------------|---------------|

| μPD78C17GF(A)-3BE     | 64-pin plastic QFP(14 x 20 mm) | Special       |

| μPD78C17GQ(A)-36      | 64-pin plastic QUIP            | Special       |

| μPD78C18GF(A)-xxx-3BE | 64-pin plastic QFP(14 x 20 mm) | Special       |

| μPD78C18GQ(A)-xxx-36  | 64-pin plastic QUIP            | Special       |

Please refer to "Quality grade on NEC semiconductor devices" (Document number IEI-1209) published by NEC corporation to know the specification of quality grade on the devices and its recommended applications.

The information in this document is subject to change without notice.

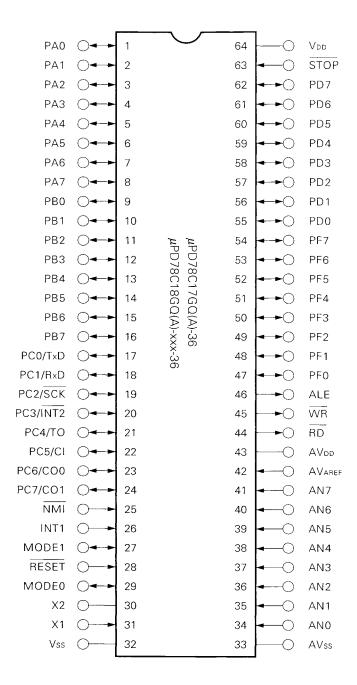

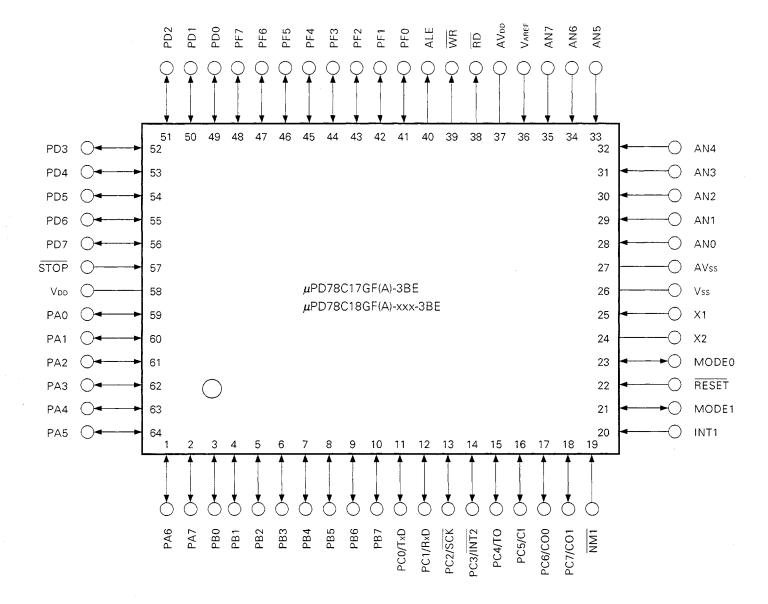

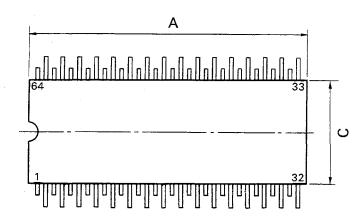

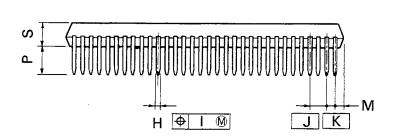

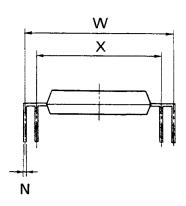

#### **PIN CONFIGURATION (TOP VIEW)**

-ბ - გ

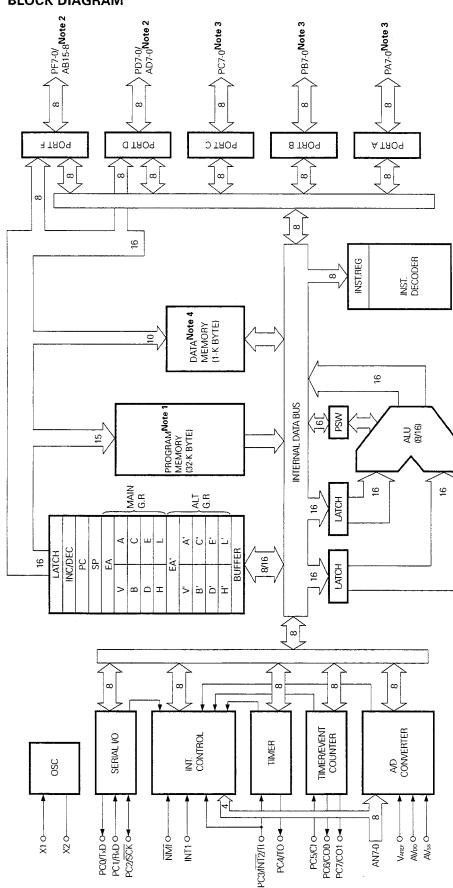

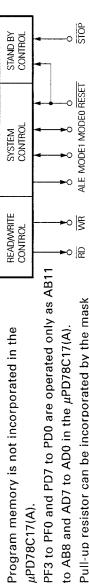

#### **BLOCK DIAGRAM**

Pull-up resistor can be incorporated by the mask to AB8 and AD7 to AD0 in the  $\mu$ PD78C17(A). က်

$\mu$ PD78C17(A).

ς.

Notes 1.

- option in the  $\mu$ PD78C18(A).

- Can be used only when RAE bit of MM register is 1. When it is 0, an external memory is necessary. 4

### DIFFERENCE BETWEEN $\mu$ PD78C17(A), 78C18(A) AND $\mu$ PD78C17, 78C18

| Part Number               | μ <b>PD78C17(A), 78C18(A)</b>                              | μPD78C17, 78C18                                                                                                               |

|---------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Quality grade             | Special                                                    | Standard                                                                                                                      |

| Electrical specifications | Input leakage current<br>AN7 to AN0: ±1 μA (MAX.)          | Input leakage current<br>AN7 to AN0; ±10 μA (MAX.)                                                                            |

| Package                   | • 64-pin plastic QFP (14 x 20 mm)<br>• 64-pin plastic QUIP | <ul> <li>64-pin plastic shrink DIP (750 mil)</li> <li>64-pin plastic QFP (14 x 20 mm)</li> <li>64-pin plastic QUIP</li> </ul> |

#### **CONTENTS**

| 1.  | PIN FUNCTIONS                                | 8   |

|-----|----------------------------------------------|-----|

|     | 1.1 LIST OF PIN FUNCTION                     | 8   |

|     | 1.2 PIN INPUT/OUTPUT CIRCUITS                | 10  |

|     | 1.3 PIN MASK OPTIONS                         | 16  |

|     | 1.4 UNUSED PIN CONNECTIONS                   | 16  |

| 2.  | INTERNAL BLOCK FUNCTIONS                     | 17  |

|     | 2.1 REGISTERS                                | 17  |

|     | 2.2 ARITHMETIC LOGIC UNIT (ALU)              | 18  |

|     | 2.3 PROGRAM STATUS WORD (PSW)                | 18  |

|     | 2.4 MEMORY                                   | 20  |

|     | 2.5 PORT FUNCTIONS                           | 23  |

|     | 2.6 TIMER                                    | 32  |

|     | 2.7 TIMER/EVENT COUNTER                      | 35  |

|     | 2.8 SERIAL INTERFACE                         | 42  |

|     | 2.9 ANALOG/DIGITAL CONVERTER                 | 53  |

|     | 2.10 ZERO-CROSS DETECTOR                     | 56  |

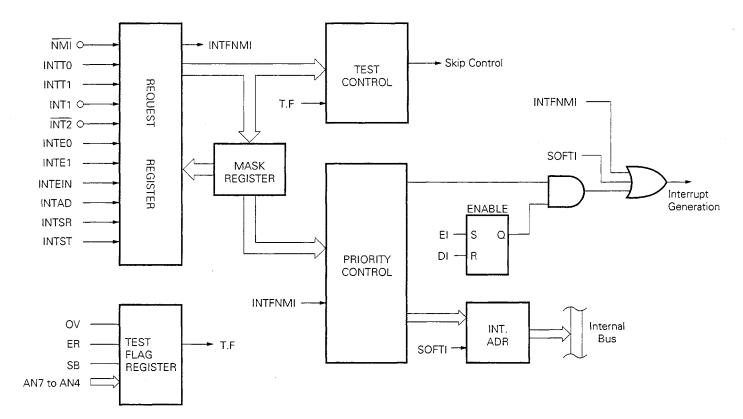

| 3.  | INTERRUPT FUNCTIONS                          |     |

|     | 3.1 INTERRUPT CONTROL CIRCUIT CONFIGURATION  | 59  |

|     | 3.2 NON-MASKABLE INTERRUPT OPERATION         |     |

|     | 3.3 MASKABLE INTERRUPT OPERATION             | 64  |

|     | 3.4 INTERRUPT OPERATION BY SOFTI INSTRUCTION | 65  |

| 4.  | STANDBY FUNCTIONS                            |     |

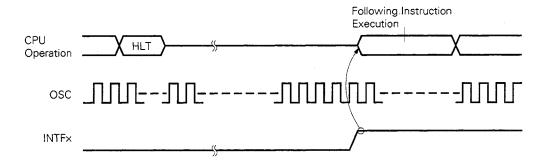

|     | 4.1 HALT MODE                                |     |

|     | 4.2 HALT MODE RELEASE                        |     |

|     | 4.3 SOFTWARE STOP MODE                       |     |

|     | 4.4 SOFTWARE STOP MODE RELEASE               | 69  |

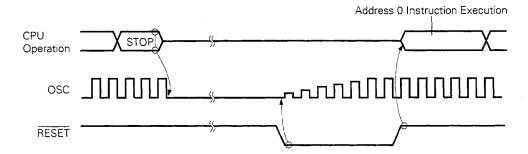

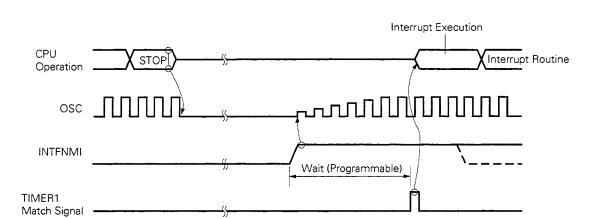

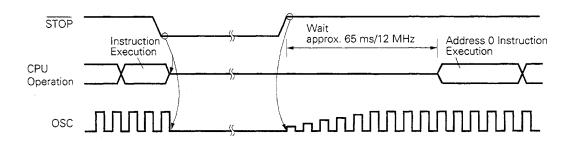

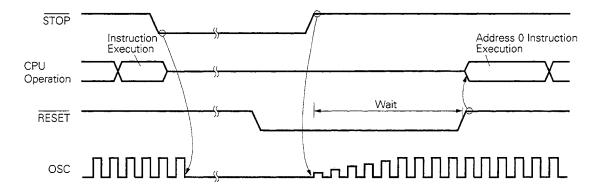

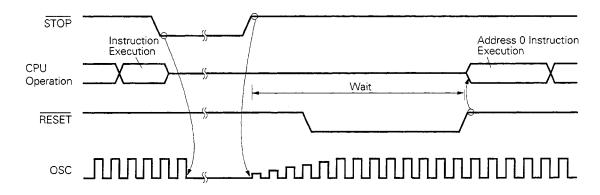

|     | 4.5 HARDWARE STOP MODE                       |     |

|     | 4.6 HARDWARE STOP MODE RELEASE               |     |

|     | 4.7 LOW SUPPLY VOLTAGE DATA RETENTION MODE   | 72  |

| 5.  | RESET OPERATIONS                             | 73  |

| 6.  | INSTRUCTION SET                              | 74  |

|     | 6.1 IDENTIFIER/DESCRIPTION OF OPERAND        | 74  |

|     | 6.2 SYMBOL DESCRIPTION OF INSTRUCTION CODE   | 75  |

|     | 6.3 INSTRUCTION EXECUTION TIME               | 76  |

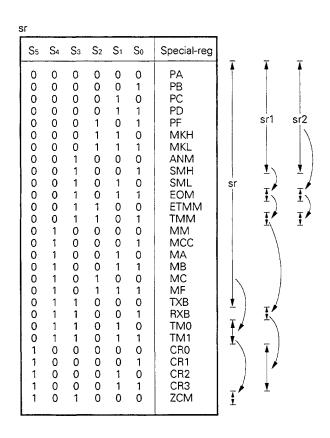

| 7.  | LIST OF MODE REGISTERS                       | 88  |

| 8.  | ELECTRICAL SPECIFICATIONS                    | 89  |

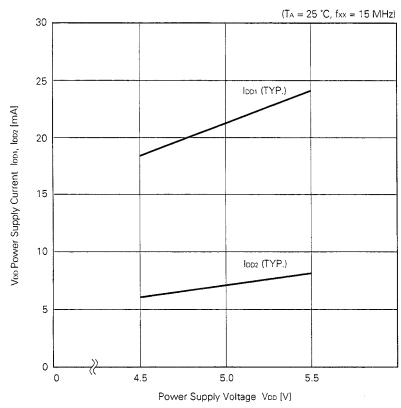

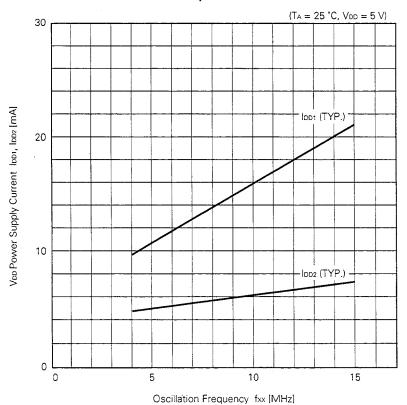

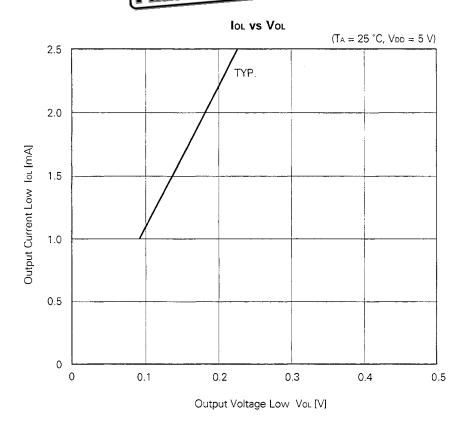

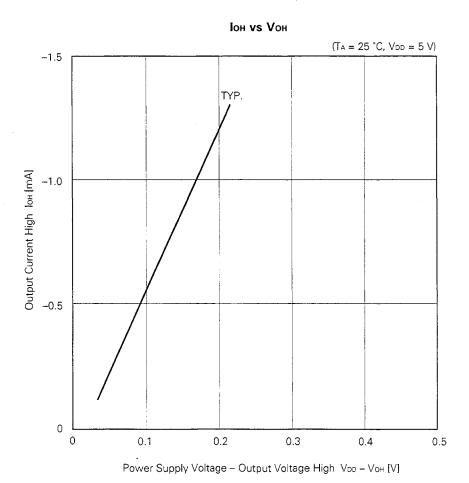

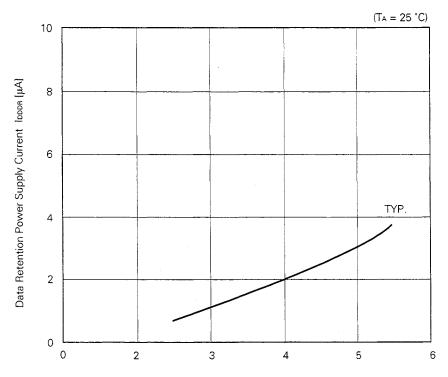

| 9.  | CHARACTERISTIC CURVES                        | 100 |

| 10. | PACKAGE INFORMATION                          | 103 |

## NEC

## Phase-out/Discontinued

## $\mu$ PD78C17(A),78C18(A)

| 11. | RECOMMENDED SOLDERING CONDITIONS                          | 105 |

|-----|-----------------------------------------------------------|-----|

| 12. | DIFFERENCES BETWEEN μPD78C18(A) AND μPD78C14(A)/78C12A(A) | 106 |

| API | PENDIX. DEVELOPMENT TOOLS                                 | 107 |

#### 1. PIN FUNCTIONS

#### 1.1 LIST OF PIN FUNCTION (1/2)

| Pin Name                         | I/O                           | Funct                                                                                                                                                                                                                                                      | tion                                                                                                                                                                                                       |  |  |  |  |

|----------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PA7 to PA0<br>(Port A)           | Input-output                  | 8-bit input-output port, which can specify input/output (Port A) bit-wise.                                                                                                                                                                                 |                                                                                                                                                                                                            |  |  |  |  |

| PB7 to PB0<br>(Port B)           | Input-output                  | oit input-output port, which can specify input/output (Port B) bit-wise.                                                                                                                                                                                   |                                                                                                                                                                                                            |  |  |  |  |

| PC0/TxD                          | Input-output/<br>Output       | Port C<br>8-bit input-output port,                                                                                                                                                                                                                         | Transmit Data Output pin for serial data.                                                                                                                                                                  |  |  |  |  |

| PC1/RxD                          | Input-output/                 | which can specify input/output bit-wise.                                                                                                                                                                                                                   | Receive Data<br>Input pin for serial data.                                                                                                                                                                 |  |  |  |  |

| PC2/SCK                          | Input-output/<br>Input-output |                                                                                                                                                                                                                                                            | Serial Clock Input-output pin for serial clock. It becomes output clock for the internal clock use, and input for the external.                                                                            |  |  |  |  |

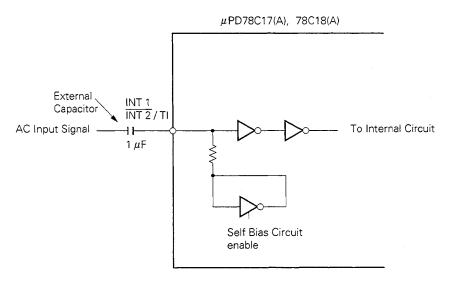

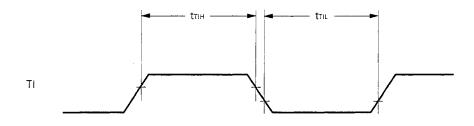

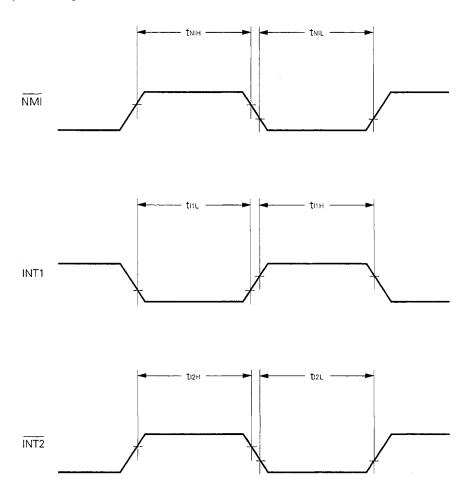

| PC3/INT2/TI                      | Input-output/<br>Input/Input  |                                                                                                                                                                                                                                                            | Interrupt Request/Timer Input Maskable interrut input pin of the edge trigger (falling edge), or an external clock input pin for a timer. Also, it can be used as a zero-cross detection pin for AC input. |  |  |  |  |

| PC4/TO                           | Input-output/<br>Output       |                                                                                                                                                                                                                                                            | Timer Output Square wave defining one cycle of internal clock or timer counter time as half cycle is output.                                                                                               |  |  |  |  |

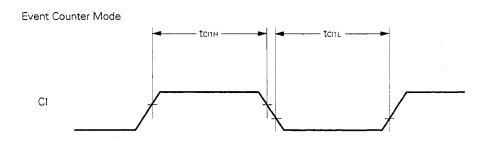

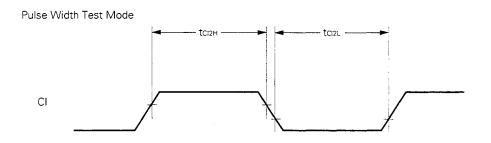

| PC5/CI                           | Input-output/<br>Input        |                                                                                                                                                                                                                                                            | Counter Input External pulse input pin to timer/event counter.                                                                                                                                             |  |  |  |  |

| PC6/CO0<br>PC7/CO1               | Input-output/<br>Output       |                                                                                                                                                                                                                                                            | Counter Output 0, 1 Programmable square wave output by timer/event counter.                                                                                                                                |  |  |  |  |

| PD7 to PD0/<br>AD7 to AD0        | Input-output/<br>Input-output | Port D<br>8-bit input-output port, which can specify<br>input/output in byte units (μPD78C18(A)).                                                                                                                                                          | Address/Data Bus When external memory is used, it becomes multiplexed address/data bus                                                                                                                     |  |  |  |  |

| PF7 to PF0/<br>AB15 to AB8       | Input-output/<br>Output       | Port F<br>8-bit input-output port, which can specify<br>input/output bit-wise.                                                                                                                                                                             | Address Bus When external memory is used, it becomes address bus.                                                                                                                                          |  |  |  |  |

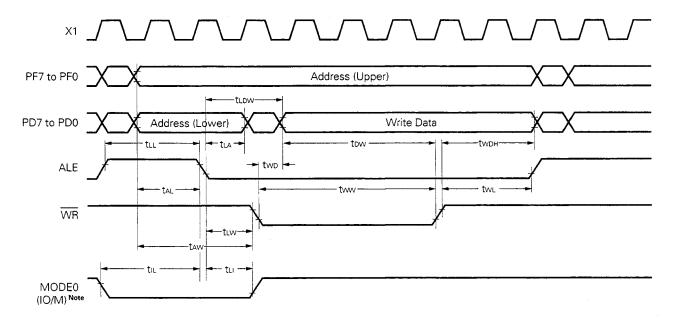

| WR<br>(Write Strobe)             | Output                        | Strobe signal which is output for write opera in any cycle other than the data write machir signal is either low or in the hardware STOP impedance.                                                                                                        | ne cycle of external memory. When RESET                                                                                                                                                                    |  |  |  |  |

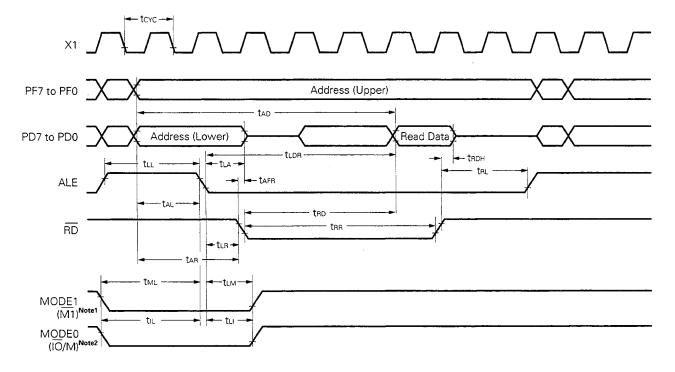

| RD<br>(Read Strobe)              | Output                        | Strobe signal which is output for read operation of external memory. It becomes high any cycle other than the read machine cycle of external memory. When RESET signal either low or in the hardware STOP mode, this signal becomes output high-impedance. |                                                                                                                                                                                                            |  |  |  |  |

| ALE<br>(Address Latch<br>Enable) | Output                        | Strobe signal to latch externally the lower ac PD0 pins to access external memory. When I STOP mode, this signal becomes output high                                                                                                                       | RESET signal is either low or in the hardwar                                                                                                                                                               |  |  |  |  |

#### 1.1 LIST OF PIN FUNCTION (2/2)

| Pin Name                                      | 1/0          | Function                                                                                                                                                                                                                                                       |                                                                                                                                    |            |                                                               |  |  |  |  |  |

|-----------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|--|--|

| MODE0<br>MODE1<br>(Mode)                      | Input-output | The $\mu$ PD78C18(A) sets MODE0 pin to "0" (low level), and MODE1 pin to "1" (high level) <sup>Note</sup> The $\mu$ PD78C17(A) allows you to set MODE0, MODE1 pins to select 4 K, 16 K, or 63 Kbytes for the size of the memory which is installed externally. |                                                                                                                                    |            |                                                               |  |  |  |  |  |

|                                               |              | М                                                                                                                                                                                                                                                              | MODE0   MODE1   External Memory                                                                                                    |            |                                                               |  |  |  |  |  |

|                                               |              |                                                                                                                                                                                                                                                                | 4K bytes<br>16K bytes<br>63K bytes                                                                                                 |            |                                                               |  |  |  |  |  |

|                                               |              | Also, when each of MODE0 at output a control signal.                                                                                                                                                                                                           | nd MOD                                                                                                                             | E1 pins is | set to "1"Note, it is synchronized to ALE to                  |  |  |  |  |  |

| NMI<br>(Non-Maskable<br>Interrupt)            | Input        | Non-maskable interrupt input                                                                                                                                                                                                                                   | t pin of t                                                                                                                         | he edge tr | igger (falling edge)                                          |  |  |  |  |  |

| INT1<br>(Interrupt<br>Request)                | Input        |                                                                                                                                                                                                                                                                | A maskable interrupt input pin of the edge trigger (rising edge). Also, it can be used as a zero-cross detection pin for AC input. |            |                                                               |  |  |  |  |  |

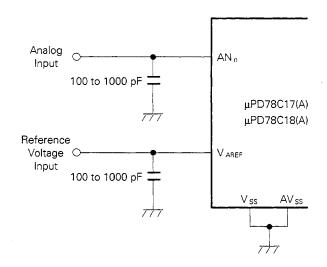

| AN7 to AN0<br>(Analog Input)                  | Input        | 8 pins of analog input to A/D (falling edge) input.                                                                                                                                                                                                            | 8 pins of analog input to A/D converter. AN7 to AN4 can be used as edge detection (falling edge) input.                            |            |                                                               |  |  |  |  |  |

| V <sub>AREF</sub><br>(Reference<br>Voltage)   | Input        |                                                                                                                                                                                                                                                                | A common pin serving both as a reference voltage input pin for A/D converter and as a control pin for A/D converter operation.     |            |                                                               |  |  |  |  |  |

| AV <sub>DD</sub><br>(Analog V <sub>DD</sub> ) |              | Power supply pin for A/D con                                                                                                                                                                                                                                   | verter.                                                                                                                            |            |                                                               |  |  |  |  |  |

| AVss<br>(Analog Vss)                          |              | GND pin for A/D converter.                                                                                                                                                                                                                                     |                                                                                                                                    |            |                                                               |  |  |  |  |  |

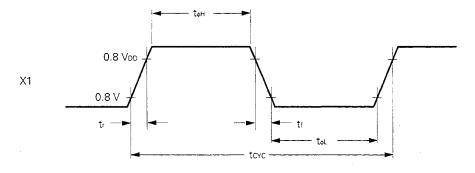

| X1, X2<br>(Crystal)                           |              | Crystal connection pins for sy supplied from outside. Invert                                                                                                                                                                                                   |                                                                                                                                    |            | tion. X1 should be input when a clock is ould be input in X2. |  |  |  |  |  |

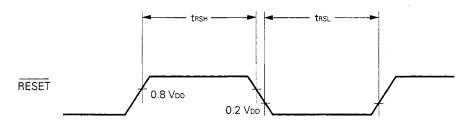

| RESET<br>(Reset)                              | Input        | Low-level active system reset                                                                                                                                                                                                                                  | t input.                                                                                                                           |            |                                                               |  |  |  |  |  |

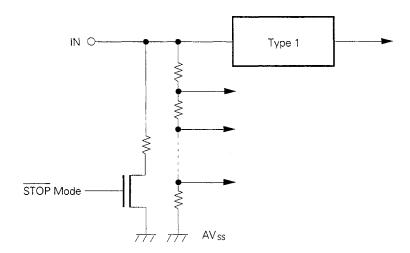

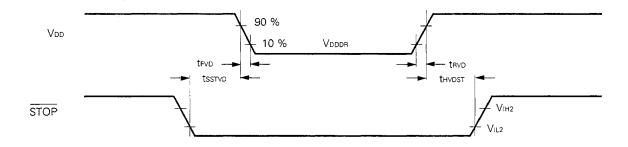

| STOP<br>(Stop)                                | Input        | Control signal input pin in ha level is input.                                                                                                                                                                                                                 | Control signal input pin in hardware STOP mode. The oscillation stops when the low-<br>evel is input.                              |            |                                                               |  |  |  |  |  |

| Voo                                           |              | Positive power supply pin.                                                                                                                                                                                                                                     |                                                                                                                                    |            |                                                               |  |  |  |  |  |

| Vss                                           |              | GND pin.                                                                                                                                                                                                                                                       |                                                                                                                                    |            |                                                               |  |  |  |  |  |

**Note** Pull-up. Pull-up resistor R is 4 [ $k\Omega$ ]  $\leq$  R  $\leq$  0.4 tcyc [ $k\Omega$ ] (tcyc is ns unit).

**Remark** The  $\mu$ PD78C18(A) can incorporate (mask option) pull-up resistors on to ports A, B, and C.

#### 1.2 PIN INPUT/OUTPUT CIRCUITS

Table 1-1 and 1-2, and figures (1) to (15) show input/output circuits of each pin in a schematic form.

Table 1-1 Pin Type No. for  $\mu$ PD78C17(A)

| Pin Name    | Type No. | Pin Name   | Type No. |  |

|-------------|----------|------------|----------|--|

| PA7 to PA0  | 5        | RESET      | 2        |  |

| PB7 to PB0  | 5        | RD         | 4        |  |

| PC1 and PC0 | 5        | WR         | 4        |  |

| PC2/SCK     | 8        | ALE        | 4        |  |

| PC3/INT2    | 10       | STOP       | 2        |  |

| PC7 to PC4  | 5        | MODE0      | 11       |  |

| AD7 to AD0  | 5        | MODE1      | 11       |  |

| AB11 to AB8 | 5        | AN3 to AN0 | 7        |  |

| PF7 to PF4  | 5        | AN7 to AN4 | 12       |  |

| NMI         | 2        | Varef 13   |          |  |

| INT1        | 9        |            |          |  |

Table 1-2 Pin Type No. for  $\mu$ PD78C18(A)

| Pin Name    | Type No. | Pin Name   | Type No. |

|-------------|----------|------------|----------|

| PA7 to PA0  | 5-A      | RESET      | 2        |

| PB7 to PB0  | 5-A      | RD         | 4        |

| PC1 and PC0 | 5-A      | WR         | 4        |

| PC2/SCK     | 8-A      | ALE        | 4        |

| PC3/INT2    | 10-A     | STOP       | 2        |

| PC7 to PC4  | 5-A      | MODE0      | 11       |

| PD7 to PD0  | 5        | MODE1      | 11       |

| PF7 to PF0  | 5        | AN3 to AN0 | 7        |

| NMI         | 2        | AN7 to AN4 | 12       |

| INT1        | 9        | VAREF      | 13       |

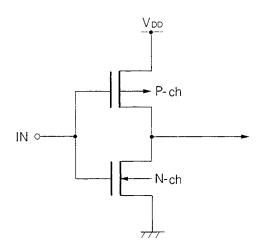

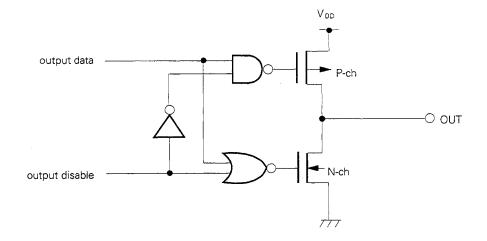

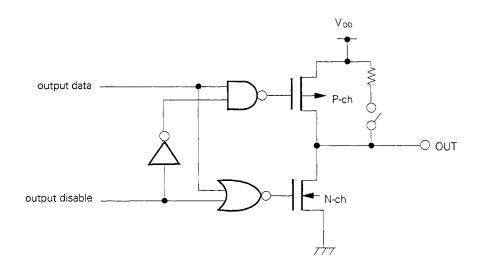

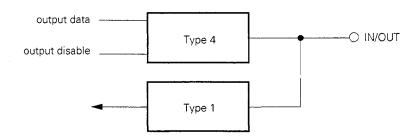

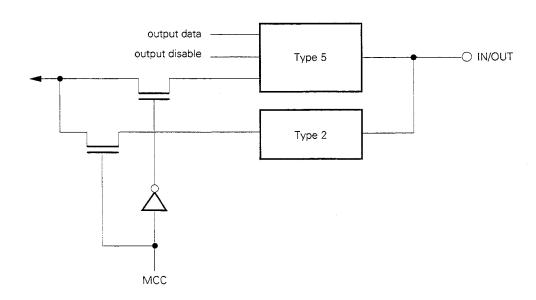

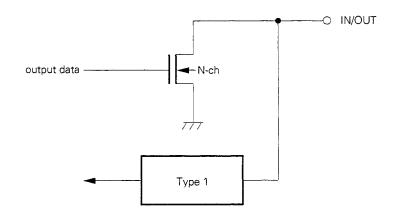

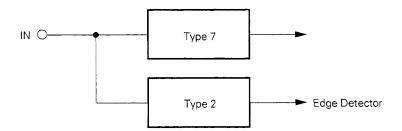

(1) Type 1

(2) Type 2

(3) Type 4

(4) Type 4-A

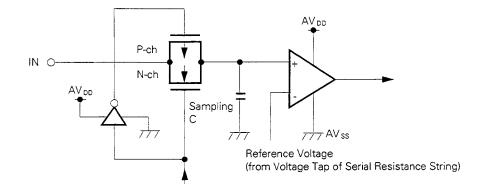

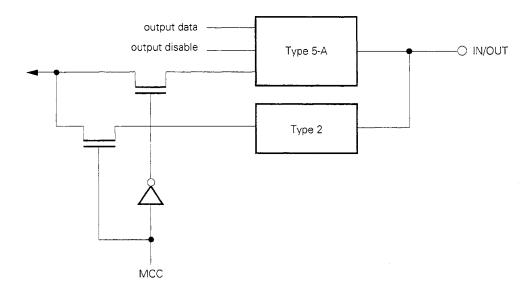

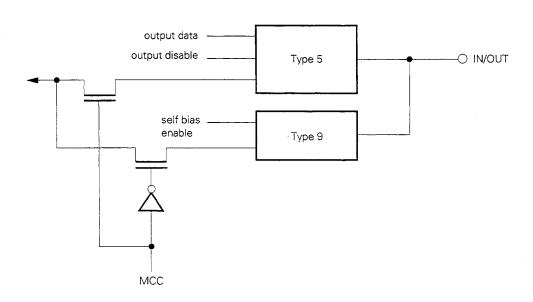

#### (5) Type 5

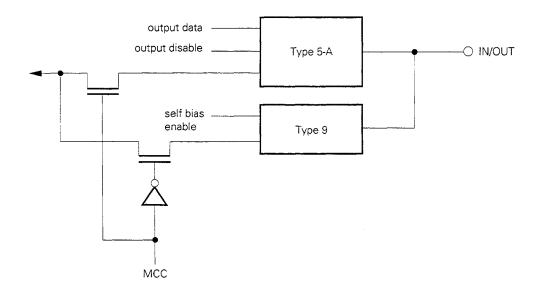

#### (6) Type 5-A

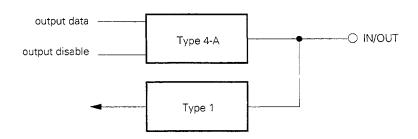

#### (7) Type 7

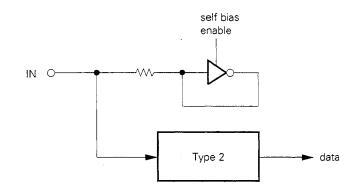

#### (8) Type 8

#### (9) Type 8-A

#### (10) Type 9

#### (11) Type 10

#### (12) Type 10-A

#### (13) Type 11

#### (14) Type 12

(15) Type 13

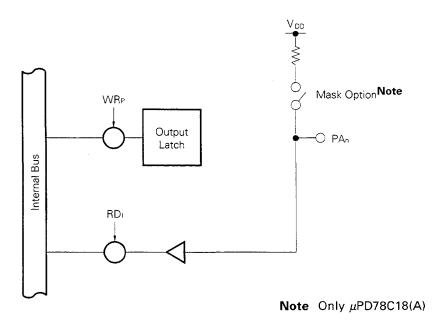

#### 1.3 PIN MASK OPTIONS

The  $\mu$ PD78C18(A) has the following mask options, which can be selected bit-wise according to the application.

| Pin Name   | Mask Options                         |

|------------|--------------------------------------|

| PA7 to PA0 |                                      |

| PB7 to PB0 | Pull-up resistor can be incorporated |

| PC7 to PC0 |                                      |

- ★ Cautions 1. Zero-cross function will not operate properly if pull-up resistor is incorporated in PC3.

- 2. The  $\mu$ PD78C17(A) has no mask option.

#### 1.4 UNUSED PIN CONNECTIONS

| Pin                                                                | Recommended Connection             |

|--------------------------------------------------------------------|------------------------------------|

| PA7 to PA0<br>PB7 to PB0<br>PC7 to PC0<br>PD7 to PD0<br>PF7 to PF0 | Connect to Vss or Vpp via resistor |

| RD<br>WR<br>ALE                                                    | Leave open                         |

| STOP                                                               | Connect to VDD                     |

| INT1, NMI                                                          | Connect to Vss or VDD              |

| AVpd                                                               | Connect to VDD                     |

| AVAREF<br>AVSS                                                     | Connect to Vss                     |

| AN7 to AN0                                                         | Connect to AVss or AVpb            |

#### 2. INTERNAL BLOCK FUNCTIONS

#### 2.1 REGISTERS

The central registers are the sixteen 8-bit registers and four 16-bit registers shown in Fig. 2-1.

15 PC SP 0 15 EΑ 7 0 7 0 Α MAIN В С D E Н L O EA' 0 7 0 V' A' ALT C' B' D' Е, Ľ' H'

Fig. 2-1 Register Configuration

#### (a) General registers (B, C, D, E, H, L)

There are two sets of general registers (MAIN: B, C, D, E, H, L; ALT: B', C', D', E', H', L'). They function as auxiliary registers for the accumulator, and have a data pointer function as register pairs (BC, DE, HL; B'C', D'E', H'L'). Four register pairs, DE, D'E', HL, and H'L' in particular, have a base register function.

When the two sets are used, if an interrupt occurs in one set, the register contents are saved into the other register set without saving them into the memory so that interrupt servicing can be carried out. The other set of registers can also be used as data pointer expansion registers. Single-step automatic increment/decrement modes and a two-step automatic increment addressing mode are available for the register pairs, DE, HL, D'E', and H'L', so that the processing time can be reduced. BC, DE, and HL can be simultaneously replaced with the ALT register by means of the EXX instruction. The HL register can be independently replaced with the ALT register by means of the EXH instruction.

#### (b) Working register vector register (V)

When a working area is set in the memory space, the high-order 8 bits of the memory address are selected using the V register and the low-order 8 bits are addressed by the immediate data in the instruction. Thus, the memory area specified with the V register can be used as working registers with a 256 x 8-bit configuration.

Because a working register can be specified with a 1-byte address field, program reduction is possible by using the working area for software flags, parameters and counters. The V register can be replaced with the ALT register paired with an accumulator by means of the EXA instruction.

#### (c) Accumulator (A)

In the  $\mu$ PD78C17(A)/78C18(A), because an accumulator type architecture is used, 8-bit data processing such as 8-bit arithmetic and logical operation instructions is mainly performed by this accumulator.

This accumulator can be replaced with the ALT register paired with the vector register (V) by means of the EXA instruction.

#### (d) Expansion accumulator (EA)

16-bit data processing such as 16-bit arithmetic and logical operation instructions is mainly performed by EA.

This accumulator can be replaced with the ALT register EA' by means of the EXA instruction.

#### (e) Program counter (PC)

This is a 16-bit register which holds information on the next program address to be executed. This register is normally incremented automatically according to the number of bytes of the instruction to be fetched. When an instruction associated with a branch is executed, immediate data or register contents are loaded. RESET input clears this counter to 0000H.

#### (f) Stack pointer (SP)

This is a 16-bit register which holds the start address of the memory stack area (LIFO format).

SP contents are decremented when a CALL or PUSH instruction is executed or an interrupt is generated, and incremented when a RETURN or POP instruction is executed.

#### 2.2 ARITHMETIC LOGIC UNIT (ALU) ...16 BITS

The ALU executes data processing such as 8-bit arithmetic and logical operations, shift and rotation, data processing such as 16-bit arithmetic and logical operations and shift operations, 8-bit multiplication and 16-bit by 8-bit division.

#### 2.3 PROGRAM STATUS WORD (PSW)

This word consists of 6 types of flags which are set/reset according to instruction execution results. Three of these flags (Z, HC, and CY) can be tested by an instruction. PSW contents are automatically saved to the stack when an interrupt (external, internal, or SOFTI instruction) is generated, and restored by the RETI instruction. RESET input resets all bits to (0).

Fig. 2-2 PSW Configuration

| 7 | 6 | 5  | 4  | 3  | 2  | 1 | 0  |

|---|---|----|----|----|----|---|----|

| 0 | Z | SK | нс | L1 | L0 | 0 | CY |

#### (a) Z (Zero)

When the operation result is zero, this flag is set (1). In all other cases, it is reset (0).

#### (b) SK (Skip)

When the skip condition is satisfied, this flag is set (1). If the condition is not satisfied, it is reset (0).

#### (c) HC (Half Carry)

If an 8-bit operation generates a carry out of bit 3 or a borrow into bit 3, this flag is set (1). In all other cases, it is reset (0).

#### (d) L1

When the "MVI A, byte" instruction is stacked, this flag is set (1). In all other cases, it is reset (0).

#### (e) L0

When the "MVI L, byte;LXI H, word" instruction is stacked, this flag is set (1). In all other cases, it is reset (0).

#### (f) CY (Carry)

When a 16-bit operation generates a carry out of or a borrow into bit 7 or 15, this flag is set (1). In all other cases, it is reset (0).

When one of 35 types of ALU instructions, rotation instructions, or carry manipulation instructions is executed, various flags are affected as shown in Table 2-1.

**Table 2-1 Flag Operations**

|                                               | (                                | Operation                        |                              | -             |          | D6        | D5                | D4 | D3 | D2 | D0        |

|-----------------------------------------------|----------------------------------|----------------------------------|------------------------------|---------------|----------|-----------|-------------------|----|----|----|-----------|

| reg. memory immediate                         |                                  |                                  |                              |               | skip     | Z         | sĸ                | нс | L1 | LO | CY        |

| ADD ADC SUB SBB DADD DADC DSUB DSBB EADD ESUB | ADDW<br>ADCW<br>SUBW<br>SBBW     | ADDX<br>ADCX<br>SUBX<br>SBBX     | ADI<br>ACI<br>SUI<br>SBI     |               |          | \$        | 0                 | \$ | 0  | 0  | <b>1</b>  |

| ANA<br>ORA<br>XRA<br>DAN<br>DOR<br>DXR        | ANAW<br>ORAW<br>XRAW             | ANAX<br>ORAX<br>XRAX             | ANI<br>ORI<br>XRI            | ANIW<br>ORIW  |          | 1         | 0                 | •  | 0  | 0  | •         |

| ADDNC SUBNB GTA LTA DADDNC DSUBNB DGT DLT     | ADDNCW<br>SUBNBW<br>GTAW<br>LTAW | ADDNCX<br>SUBNBX<br>GTAX<br>LTAX | ADINC<br>SUINB<br>GTI<br>LTI | GTIW<br>LTIW  |          | <b>\$</b> | $\leftrightarrow$ | 1  | 0  | 0  | <b>\$</b> |

| ONA<br>OFFA<br>DON<br>DOFF                    | ONAW<br>OFFAW                    | ONAX<br>OFFAX                    | ONI<br>OFFI                  | ONIW<br>OFFIW |          | \$        | 1                 | •  | 0  | 0  | •         |

| NEA<br>EQA<br>DNE<br>DEQ                      | NEAW<br>EQAW                     | NEAX<br>EQAX                     | NEI<br>EQI                   | NEIW          |          | 1         | 1                 | 1  | 0  | 0  | 1         |

| INR<br>DCR                                    | INRW<br>DCRW                     |                                  |                              |               |          | 1         | 1                 | 1  | 0  | 0  | •         |

| DAA                                           | DOM                              |                                  |                              |               |          | 1         | 0                 | 1  | 0  | 0  | 1         |

| RLR<br>DRLR                                   | RLL SLR<br>DRLL D                |                                  | SLL                          |               |          | •         | 0                 | •  | 0  | 0  | 1         |

| SLRC                                          | SLLC                             |                                  |                              |               |          | •         | 1                 | •  | 0  | 0  | 1         |

| STC                                           |                                  |                                  |                              |               |          | •         | 0                 | •  | 0  | 0  | 1         |

| CLC                                           |                                  |                                  | 1 8 85 44                    |               | <u> </u> | •         | 0                 | •  | 0  | 0  |           |

|                                               |                                  |                                  | ·                            | A, byte       |          | •         | 0                 | •  | 1  | 0  | •         |

|                                               | MVI L, byte<br>LXI H, word       |                                  |                              |               |          | •         | 0                 | •  | 0  | 1  | •         |

|                                               |                                  |                                  |                              |               |          |           | \$                | •  | 0  | 0  | •         |

|                                               | _                                |                                  |                              |               | RETS     | •         | 1                 | •  | 0  | 0  | •         |

|                                               |                                  | other All in                     | struction                    | ıs            |          | •         | 0                 | •  | 0  | 0  | •         |

| <b>1</b> | Affected<br>(Set or Reset) |

|----------|----------------------------|

| 1        | Set                        |

| 0        | Reset                      |

| <b></b>  | Not affected               |

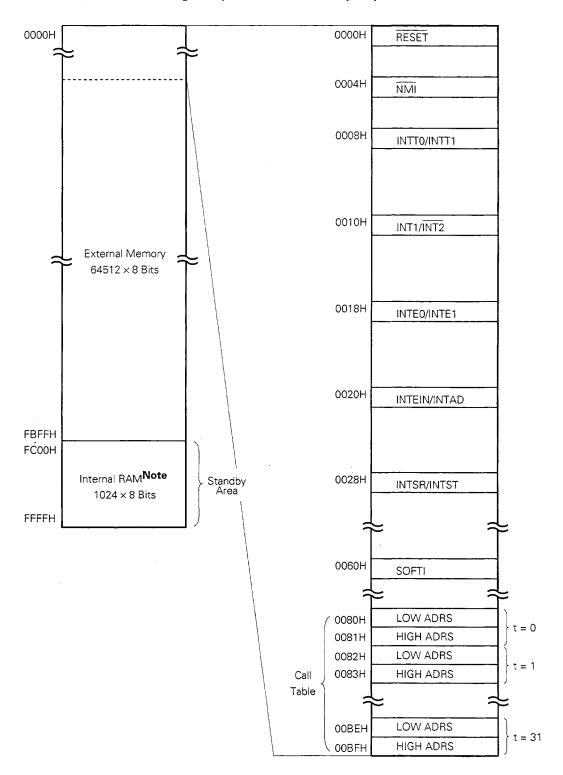

#### 2.4 MEMORY

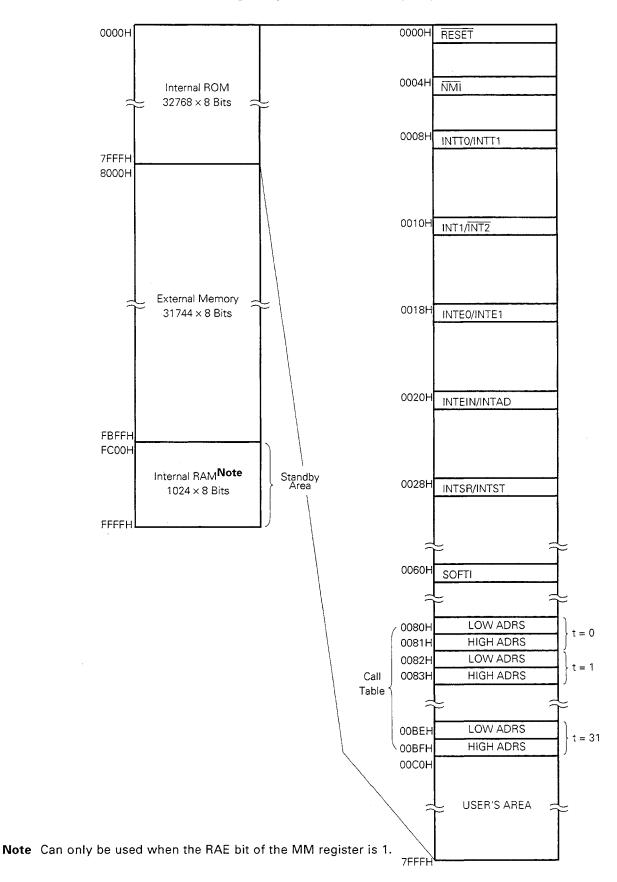

The  $\mu$ PD78C17(A)/78C18(A) can address a maximum of 64 Kbytes of memory. The memory maps are shown in Figs. 2-3 and 2-4. The external memory area and the internal RAM area can be freely used as program memory and data memory. Because the access timing for internal memory and external memory are the same, processing can be executed at high speeds.

#### (a) Interrupt start addresses

The interrupt start addresses are all fixed as follows:

| NMI          | 0004H |

|--------------|-------|

| INTTO/INTT1  | H8000 |

| INT1/INT2    | 0010H |

| INTEO/INTE1  | 0018H |

| INTEIN/INTAD | 0020H |

| INTSR/INTST  | 0028H |

| SOFTI        | 0060H |

#### (b) Call address table

The call address of a 1-byte call instruction (CALT) can be stored in the 64-byte area (for 32 call addresses) from address 0080H to address 00BFH.

#### (c) Specific memory area

The reset start address, interrupt start addresses, and the call table are allocated to addresses 0000H to 00BFH, and this area takes account of these in use. Addresses 0800H to 0FFFH are directly addressable by a 2-byte call instruction (CALF).

The  $\mu$ PD78C18(A) has on-chip mask programmable ROM in addresses 0000H to 7FFFH.

#### (d) Internal data memory area

1K-byte RAM is incorporated in addresses FC00H to FFFFH. The RAM contents are retained for 1K-byte internal data memory area in standby operation.

#### (e) External memory area

With the  $\mu$ PD78C17(A), the external memory can be expanded in steps in 63K-byte area (0000H to FBFFH) by setting the MODE0 and MODE1 pins (see **Table 2-3**).

With the  $\mu$ PD78C18(A), the external memory can be expanded in steps in 31K-byte area (8000H to FBFFH) by setting the MEMORY MAPPING register (see **Fig. 2-13**).

The external memory is accessed using AD7 to AD0 (multiplexed address/data bus), AB7 to AB0 (address bus), and the  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ , and ALE signals. Both programs and data can be stored in the external memory.

#### (f) Working register area

A 256-byte working register area can be set in any memory location (specified by the V register) and working register addressing is possible.

Fig. 2-3  $\mu$ PD78C17(A) Memory Map

Note Can only be used when the RAE bit of the MM register is 1.

Fig. 2-4  $\mu$ PD78C18(A) Memory Map

#### 2.5 PORT FUNCTIONS

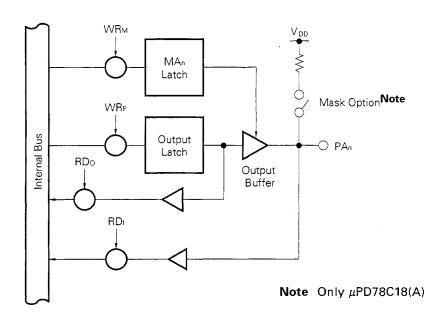

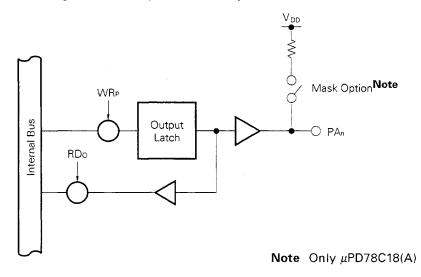

#### (1) PA7 to PA0 (PORT A)

This is an 8-bit input/output port which has input/output buffer and output latch functions. Port A can be set as to input or output bit-wise using the MODE A register. And  $\mu$ PD78C18(A) port A pull-up resistor specification is performed bit-wise by mask option.

Port A is set as follows when setting the input port or after reset.

High-impedance: Without pull-up resistor

High level: With pull-up resistor

Fig. 2-5 Port A

#### (a) When specified as output port (MAn = 0)

The output latch is effective, enabling data exchange by a transfer instruction between the output latch and the accumulator. Direct bit setting/resetting of output latch contents is possible by an arithmetic or logical operation instruction without the use of an accumulator. Once data is written to the output latch, the data is held until a port A manipulation instruction is executed or the data is reset.

Fig. 2-6 Port A Specified as Output Port

#### (b) When specified as input port (MAn = 1)

PA line contents can be loaded into an accumulator by a transfer instruction. They can also be directly tested bit-wise by an arithmetic or logical operation instruction without the use of an accumulator.

Fig. 2-7 Port A Specified as Input Port

Actual execution of an instruction which manipulates port A is performed in 8-bit units. If a port A read instruction (MOV A, PA) is executed, the input line contents of the port specified for input and the output latch contents of the port specified for output are loaded into an accumulator. When a port A write instruction (MOV PA, A) is executed, data is written to the output latch of both ports specified for input and output. However, the output latch contents of a bit specified as an input port cannot be loaded to the accumulator and are not output to an external pin (which functions as input pin), because the output buffer is off.

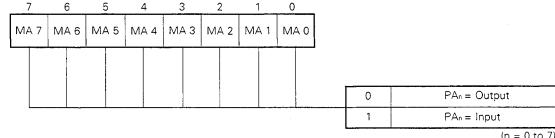

#### MODE A register (MA)

8-bit register which specifies port A input/output.

Port A input/output can be specified bit-wise. If the MODE A register corresponding bit is set (1), this register is input, and if the bit is reset (0), this register is output.

After RESET input or in the hardware STOP mode, all the bits are set, and port A is in the input mode resulting in the below status.

High-impedance: Without pull-up resistor : With pull-up resistor High level

Fig. 2-8 MODE A Register Format

#### (2) PB7 to PB0 (PORT B)

Like port A, port B is an 8-bit input/output port with input/output buffer and output latch functions. Port B can be set as an input or output port bit-wise using the MODE B register (MB).  $\mu$ PD78C18(A) port B pull-up resistor specification is performed bit-wise by mask option.

Port B is set as follows when setting the input port or after reset.

High-impedance: Without pull-up resistor

High level: With pull-up resistor

As with port A, direct bit setting/resetting of port B output latch contents is possible by an arithmetic or logical operation instruction without the use of an accumulator. Data transfer to/from an accumulator is also possible.

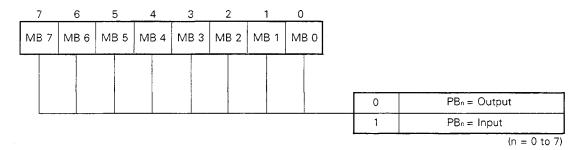

#### • MODE B Register (MB)

Like the MODE A register, the MODE B register is an 8-bit register which specifies port B input/output bit-wise.

After RESET input or in the hardware STOP mode, all the bits are set (1), and port B is in the input mode resulting in the status below.

High-impedance : Without pull-up resistor High level : With pull-up resistor

Fig. 2-9 Mode B Register Format

#### (3) PC7 to PC0 (PORT C)

Port C (PC7 to PC0) is an 8-bit special input/output port which functions as various control signals as well as general-purpose input/output ports in which input/output is set bit-wise like port A. These are switched over bit-wise according to the setting of the MODE C register and MODE CONTROL C register as shown below.

Table 2-2 Operation of PC7 to PC0

|     | MCCn = 1         | $MCC_n = 0$ |            |  |  |

|-----|------------------|-------------|------------|--|--|

|     | $MC_n = x$       | MCCn = 0    | $MC_n = 1$ |  |  |

| PC0 | TxD output       | Output      | Input      |  |  |

| PC1 | RxD inpit        | Output      | Input      |  |  |

| PC2 | SCK input/output | Output      | Input      |  |  |

| PC3 | INT2/TI input    | Output      | Input      |  |  |

| PC4 | TO output        | Output      | Input      |  |  |

| PC5 | Cl input         | Output      | Input      |  |  |

| PC6 | CO0 output       | Output      | Input      |  |  |

| PC7 | CO1 output       | Output      | Input      |  |  |

(n = 0 to 7)

μΡD78C18(A) port C pull-up resistor specification is performed bit-wise by mask option.

In the operation when data is set in the general-purpose input/output ports, as with port A, direct bit setting/resetting/testing of port C output latch contents is possible by an arithmetic or logical operation instruction without the use of an accumulator. Data transfer to/from an accumulator is also possible.

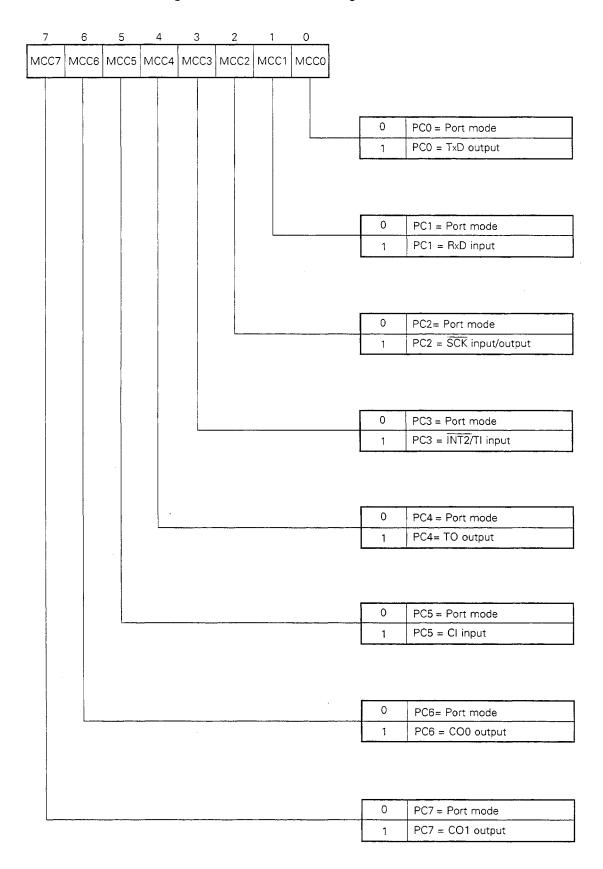

#### MODE CONTROL C Register (MCC)

8-bit register which specifies the port C port/ control signal input/output mode bit-wise.

If the MODE CONTROL C register corresponding bits are set (1), PC7 to PC0 are in the control signal input/output mode, and if these are reset (0), in the port mode.

After RESET input or in the hardware STOP mode, all the bits of the MODE CONTROL C register are reset (0), and the port mode is set.

#### Fig. 2-10 MODE CONTROL C Register Format

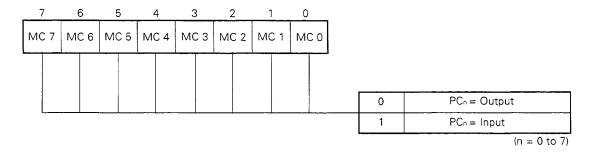

#### MODE C register (MC)

The MODE C register is an 8-bit register by which, like the MODE A register of port A, port C input/output specification is performed bit-wise.

Contents of the MODE C register corresponding to the bits set to the control mode by the MODE CONTROL C register are ignored.

After RESET input or in the hardware STOP mode, all bits of the MODE C register are set (1). Because all bits of the MODE CONTROL C register are reset (0), port C is an input port and the below state is set.

High-impedance: Without pull-up resistor

High level: With pull-up resistor

Fig. 2-11 MODE C register Format

#### (4) PD7 to PD0 (PORT D)

#### $\blacksquare \mu PD78C17(A)$

Can be used for address/data bus. These have no functions as a port.

#### ■ μPD78C18(A)

8-bit general-purpose input/output ports shared as multiplexed address/data bus. These ports can be specified for input/output in byte units (8-bit unit) as general-purpose input/output ports, and function as multiplexed address/data bus when external expansion memory is connected. This switchover is performed by the MEMORY MAPPING register.

In the operation when data is set in the general-purpose input/output ports, unless input/output is specified in byte units, as with port A, direct bit setting/resetting/testing of port F output latch contents is possible by an arithmetic or logical operation instruction without the use of an accumulator. Data transfer to/from an accumulator is also possible.

#### (5) PF7 to PF0 (PORT F)

#### ■ μPD78C17(A)

General-purpose input/output ports shared as address bus.

These pins function as address outputs corresponding to the size of externally installed memory according to the MODE0 and MODE1 pin settings.

Pins which are not used for address output can be used for general-purpose input/output ports which have the same port function as for port A. Input/output setting is performed by the MODE F register.

Table 2-3 Operation of PF7 to PF0  $\mu$ PD78C17(A)

| MODE1 | MODE0 | PF 7               | PF 6 | PF 5 | PF 4 | PF 3 | PF 2 | PF 1 | PF 0 | External Address<br>Space |

|-------|-------|--------------------|------|------|------|------|------|------|------|---------------------------|

| 0     | 0     | Port               | Port | Port | Port | AB11 | AB10 | AB9  | AB8  | 4 Kbytes                  |

| 0     | 1     | Port               | Port | AB13 | AB12 | AB11 | AB10 | AB9  | AB8  | 16 Kbytes                 |

| 1     | 0     | Setting prohibited |      |      |      |      |      |      |      |                           |

| 1     | 1     | AB15               | AB14 | AB13 | AB12 | AB11 | AB10 | AB9  | AB8  | 63 Kbytes                 |

When this is set as general-purpose input/output ports, as with port A, direct bit setting/resetting/ testing of port C output latch contents is possible by an arithmetic or logical operation instruction without the use of an accumulator. Data transfer to/from an accumulator is also possible.

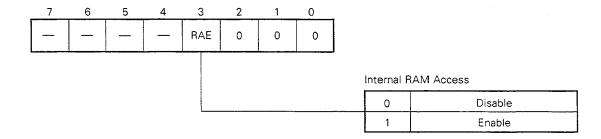

#### μPD78C17(A) MEMORY MAPPING register (MM)

A register which controls internal RAM access permission.

Bit 3 (RAE) of the MEMORY MAPPING register controls whether or not internal RAM is permitted.

When internal RAM is used in external extension and external memory is used in the area, RAE bit is set to "0" and internal RAM access is prohibited.

Contents of RAE bit is retained, even if RESET signal is input in the normal operation. However, at power-on reset, RAE bit is undefined and RAE bit should be initialized by an instruction.

Fig. 2-12 μPD78C17(A) MEMORY MAPPING Register Format

#### **■** μPD78C18(A)

8-bit general-purpose input/output ports shared as address bus.

Can specify input/output bit-wise as general-purpose input/output ports, and address signal is output according to external extension memory size when the external expansion memory of 256 bytes or greater is accessed.

This switchover is performed by the MEMORY MAPPING and MODE F registers.

| PF7  | PF6  | PF5  | PF4  | PF3  | PF2  | PF1  | PF0  | External Memory   |

|------|------|------|------|------|------|------|------|-------------------|

| Port | Maximum 256 bytes |

| Port | Port | Port | Port | AB11 | AB10 | AB9  | AB8  | Maximum 4 Kbytes  |

| Port | Port | AB13 | AB12 | AB11 | AB10 | AB9  | AB8  | Maximum 16 Kbytes |

| AB15 | AB14 | AB13 | AB12 | AB11 | AB10 | AB9  | AB8  | Maximum 31 Kbytes |

When this is set as general-purpose input/ourput ports, as with port A, direct bit setting/resetting/testing of port C output latch contents is possible by an arithmetic or logical operation instruction without the use of an accumulator. Data transfer to/from an accumulator is also possible.

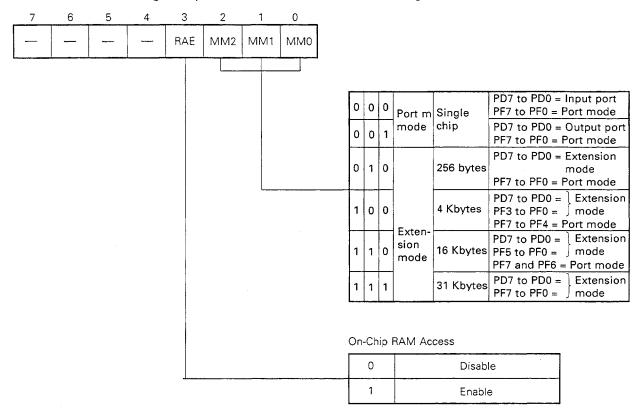

#### • μPD78C18(A) MEMORY MAPPING register (MM)

4-bit register which specifies PD7 to PD0 and PF7 to PF0 port/extension mode and controls internal RAM access permission.

Bits 0, 1, and 2 (MM0, MM1, MM2) in the MEMORY MAPPING register control specification of PD7 to PD0 port/extension mode, input/output, and PF7 to PF0 address line.

When bits MM1 and MM2 in the MEMORY MAPPING register are "0", PD7 to PD0 and PF7 to PF0 are set as general-purpose input/output port, input/output of PD7 to PD0 is specified by MM0, and input/output of PF7 to PF0 is specified by the MODE F register.

4 types of external extension memory (256 bytes, 4 Kbytes, 16 Kbytes, and 31 Kbytes) can be selected, and ports which are not used for address line are used as general-purpose input/output ports.

Bit 3 (RAE) of the MEMORY MAPPING register controls whether or not the access to internal RAM is permitted.

When internal RAM is not used in external extension and external memory uses the area, RAE bit is set to "0" and internal RAM access is prohibited.

After RESET input or in the hardware STOP mode, bits MM0, MM1, and MM2 of the MEMORY MAPPING register are reset (0), and PD7 to PD0 are input ports (high-impedance).

Even if the RESET signal is input to the RAE bit in the normal operation, contents in input time are retained. However, the RAE bit is undefined at power-on reset, the RAE bit should be initialized by an instruction.

Fig. 2-13 μPD78C18(A) MEMORY MAPPING Register Format

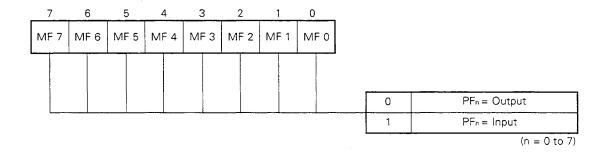

#### MODE F register (MF)

The MODE F register specifies port F input/output in the same way as for the MODE A register in port A. However, contents of the MODE F register corresponding to port F bits specified as address line by the MEMORY MAPPING register are in the output mode.

After RESET input or in the hardware STOP mode, all the bits of the MODE F register are set (1) and port F is an input port (high-impedance).

Fig.2-14 MODE F Register Format

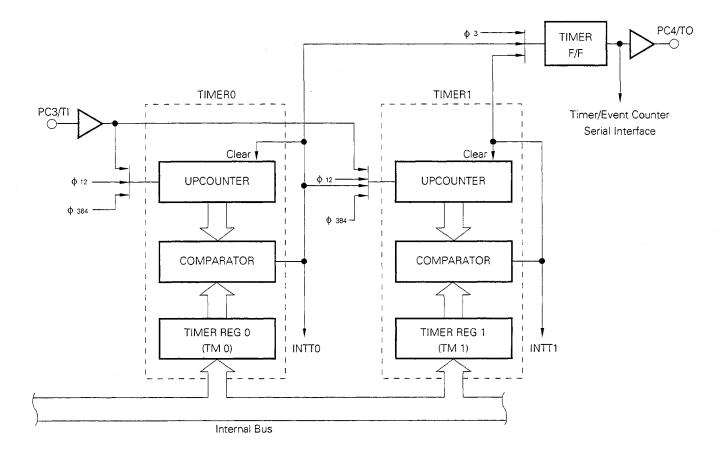

#### 2.6 TIMER

This is an interval timer which has two 8-bit timers (TIMER0, TIMER1). These are programmable independently. By cascading these can also be used as 16-bit interval timer, and can be used for counting TI input.

The timer is composed of TIMER0 and TIMER1, as shown in 2-15, including 8-bit TIMER REG (TM0, TM1), 8-bit COMPARATOR, 8-bit UPCOUNTER, and TIMER F/F. Input selection, timer operation and TO output are controlled by the timer mode register (TMM).

In TIMER0,  $\phi_{12}$  (1  $\mu$ s: 12-MHz operation) and  $\phi_{384}$  (32  $\mu$ s: 12-MHz operation) internal clock and TI input are input. In TIMER1, not only these inputs but also TIMER0 match signal are input.

Because TIMER0 operates in the same way as TIMER1, TIMER0 operation is described below.

At first, a count value is set in TIMER REGO, and TIMERO input and TIMERO start data (bit 4 in the timer mode register = "0") are set in the timer mode register to start TIMERO. The UPCOUNTER is incremented one input at a time. The COMPARATOR always compares contents of the incremented UPCOUNTER with those of TIMER REGO, and if these match, the match signal (internal interrupt: INTTO) is generated. This match clears contents of UPCOUNTER and increment starts again from 00H. Therefore, the interval is set by count time, which is a count value set by TIMER REGO. This allows the timer to operate as an interval timer which generates interrupts repeatedly.

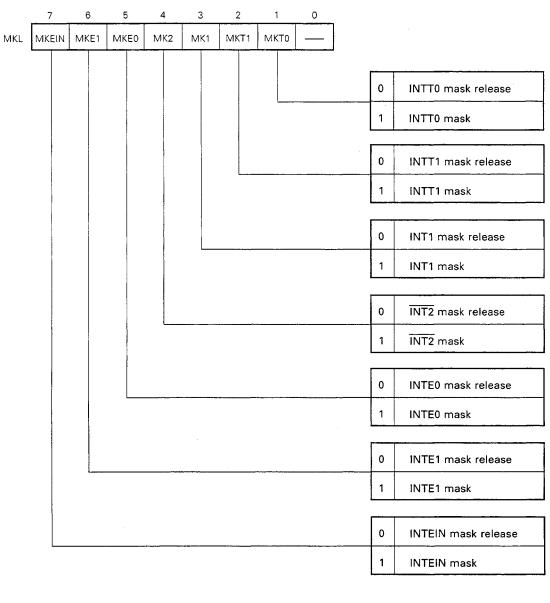

By setting (1) bit 1 (MKT0) of the interrupt mask register (MKL), internal interrupt (INTT0) is disabled.

The TO output has timers COMPARATOR match signal and TIMER F/F complemented by  $\phi_3$  (250 ns: 12-MHz operation) internal clocks, and can obtain a square wave which has a half period of the count time or  $\phi_3$ . By setting the timer/event counter mode register (ETMM), this output can be used for the timer event counter reference time.

By setting the serial mode register (SMH), the timer can be used as the serial clock (SCK) in serial interface.

Fig. 2-15 Timer Block Diagram

- **Remarks 1.**  $\phi_3 = f_{XX} \times 1/3$

- $\phi_{12} = f_{XX} \times 1/12$

Where, fxx = oscillation frequency (MHz)

$\phi_{384} = f_{XX} \times 1/384$

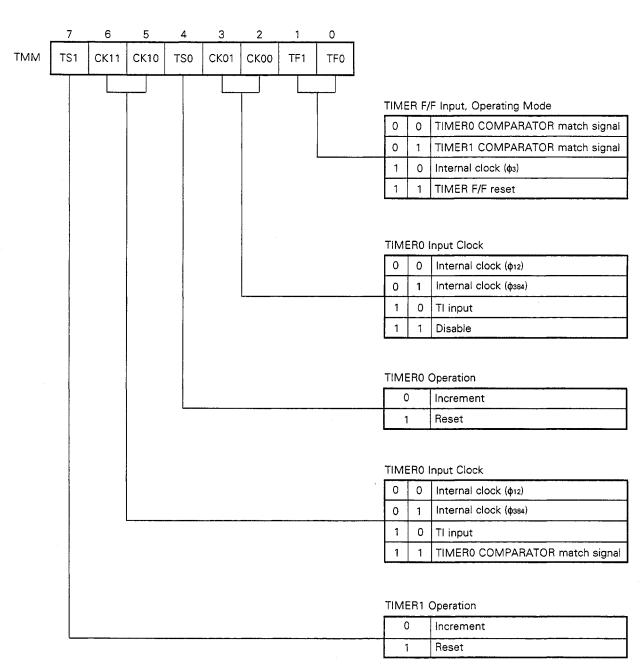

#### (1) Timer mode register (TMM)

This is an 8-bit register which controls TIMER0, TIMER1, and TIMER F/F operation (see Fig. 2-16).

The timer mode register bits 0 and 1 (TF0, TF1) control the TIMER F/F operating mode, bits 2 and 3 (CK00, CK01) control TIMER0 input clock, bit 4 (TS0) controls TIMER0 operation. Bits 5 and 6 (CK10, CK11) control TIMER1 input clock, and bit 7 (TS1) controls TIMER1 operation.

TS0 and TS1 bits clear these UPCOUNTERs to 00H by "1", and stop increment. By changing "1" to "0", the UPCOUNTER starts increment from 00H.

The internal clock  $(\phi_3)$  divides the oscillator frequency by 3, the internal clock  $(\phi_{12})$  divides it by 12, and the internal clock  $(\phi_{384})$  divides it by 384.

After RESET input, the timer mode register is set to FFH, the UPCOUNTERs in TIMER0 and TIMER1 are cleared in the suspended state, and TIMER F/F is reset.

Fig. 2-16 Timer Mode Register (TMM) Format

# 2.7 TIMER/EVENT COUNTER

The  $\mu$ PD78C17(A)/78C18(A) have a 16-bit multi-function timer/event counter which has the functions shown below.

- o Interval timer

- o External event counter

- o Frequency measurement

- o Pulse width measurement

- o Programmable square wave output

- o One pulse output

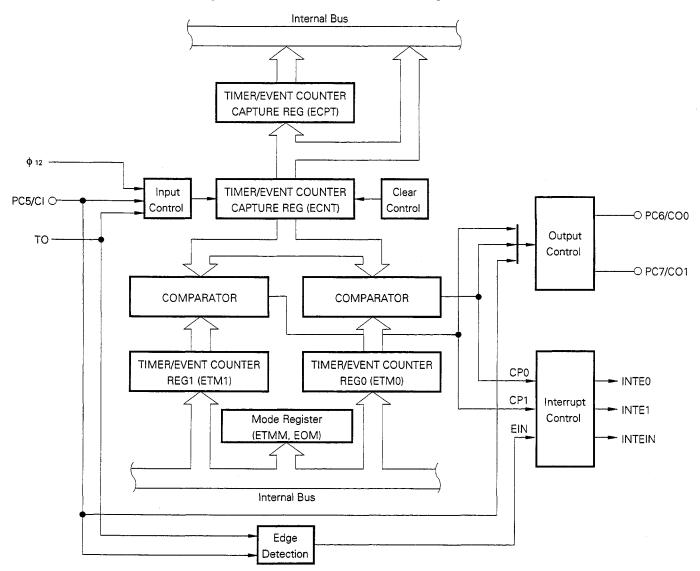

The timer/event counters are composed of 16-bit timer/event counter upcounter (ECNT), timer/event counter capture register (ECPT), comparator, timer/event counter REG0 and REG1 (ETM0, ETM1), and output/input and interrupt and clear control circuits.

ECNT is a 16-bit upcounter which counts an input pulse, and cleared by the clear control circuit.

The ECPT register is a 16-bit buffer register which retains the contents of ECNT. The timing to latch contents of ECNT by the ECPT register is the falling edge of CI input when input to ECNT is an internal clock, and is the falling edge of TO output when input to ECNT is CI input.

The ETM0 and ETM1 registers are two 16-bit registers which set a number of counts and data is exchanged by 16-bit data transfer instructions via an extended accumulator.

The comparator compares contents of ECNT with contents of the ETM0 and ETM1 registers, and if these match, match signals are generated.

The interrupt control circuit is a circuit which controls interrupts from the timer/event counter. The following interrupt sources are generated. These are generated by three signals: the ECNT and ETM0 register match signal (INTE0), the ECNT and ETM1 register match signal (INTE1), and the CI input or timer output (TO) falling edge (INTEIN).

Fig. 2-17 Timer/Event Counter Block Diagram

**Remarks**  $\phi_{12} = fxx \times 1/12$ , where fxx = oscillation frequency (MHz)

Next, using pulse width measurement as an example, the operation is described.

This operation purpose is measurement for high-level width of external pulse input to Cl. This is performed by setting the timer/event counter mode register (ETMM) to 09H.

ECNT continues internal clock ( $\phi_{12}$ ) count while CI is high. If the external pulse which is input to CI falls, the contents of ECNT are transferred to the ECPT register. ECNT is cleared and an internal interrupt (INTEIN) is generated (see **Fig. 2-18**). Therefore, using contents of the ECPT register and internal clock period, the pulse width is measured.

Fig. 2-18 Pulse Width Measurement

Reference Clock (\$\phi\_{12}\$)

CI Input

ECNT Input

EIN Interrupt

Transfer ECNT contents to ECPT register

Clear ECNT

The  $\mu$ PD78C17(A)/78C18(A) have an output control circuit which outputs pulses which can be changed in pulse width and period by interlocking with the timer/event counter.

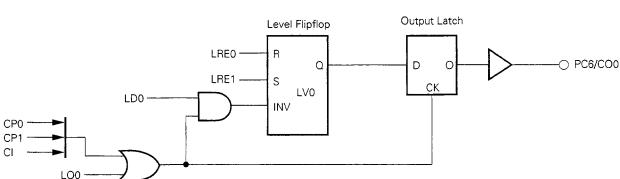

The output control circuit outputs are CO0 output and CO1 output. Because these share the same configuration, CO0 output is described. Fig. 2-19 shows the CO0 configuration. CO0 output is a master-slave type output. The first phase level F/F (LV0) retains the level which is output next, and the second phase output latch outputs the LV0 level to off-chip.

By setting the timer/event counter output mode register (EOM), LV0 can be set/reset. LV0 has a level inversion pin (INV) and LV0 level can be inverted at the output time by setting the timer/event counter mode register.

Timing when the output latch outputs LV0 level to off-chip is performed by output timing of the timer/event counter mode register setting.

Fig. 2-19 Output Control Circuit

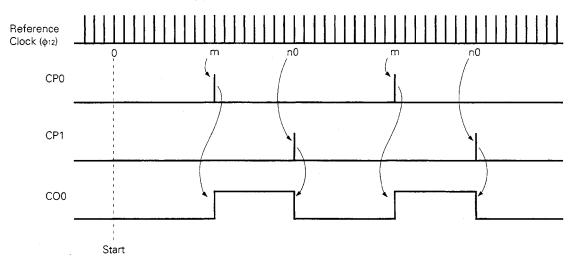

Next, the operation which outputs a square wave to the COO pin is described.

At first, after ECNT is cleared, a count value (ETM0 < ETM1) is set in the ETM0 and ETM1 registers, and data for LV0 initial status specification and to enable LV0 level inversion is set in the timer/event counter output mode register.

In the timer/event counter mode register, by setting an input to ECNT to φ12 (1 μs: 12-MHz operation) internal clock, the ECNT clear mode to the ECNT and ETM1 register match signal, and CO0 pin output timing to the ECNT and ETM0 register match signal or ECNT and ETM1 register match signal, the timer/event counter starts operation.

ECNT is incremented one \$12 internal clock at a time, the comparator compares incremented ECNT with the ETM0 and ETM1 registers, and if these match, the match signal (CP0, CP1) is generated. By this match signal, LV0 level is output to the CO0 pin, and LV0 level is inverted.

ECNT is cleared by the ECNT and ETM1 register match signal (CP1), ECNT increments again from 0000H, and the above-mentioned steps are repeated (see Fig. 2-20).

Therefore, a programmable square wave which has the ETM0 and ETM1 register count as a pulse width is output.

Fig. 2-20 Square Wave Output

Remarks ETM0 register = m

ETM1 register = n

(m < n: m and n are count values.)

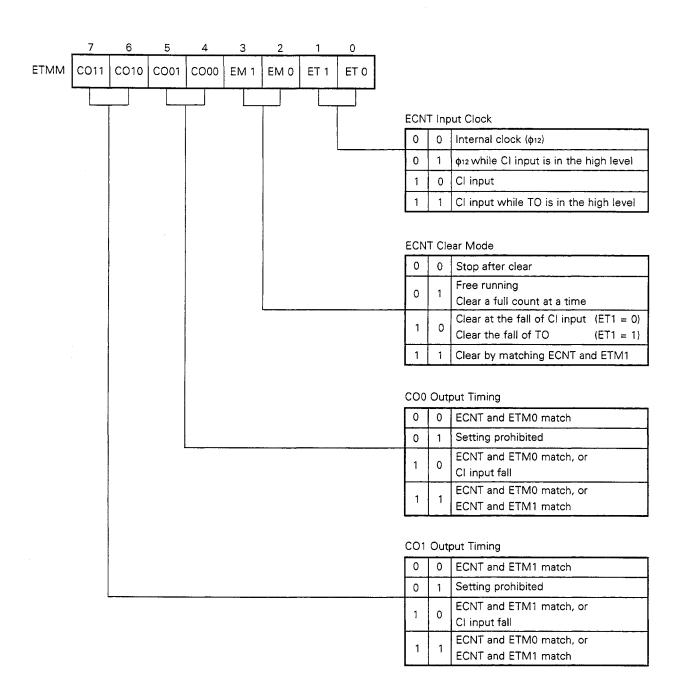

# (1) Timer/event counter mode register (ETMM)

This is an 8-bit register which controls the timer/event counter (see Fig. 2-21).

The timer/event counter mode register bits 0 and 1 (ET0, ET1) control the timer event counter upcounter (ECNT) input clock, bits 2 and 3 (EM0, EM1) control the ECNT clear mode, bits 4 and 5 (CO00, CO01) control output timing when the output latch contents are output to the counter output0 (CO0). Bits 6 and 7 (CO10, CO11) control CO1 output timing.

The internal clock  $(\phi_{12})$  divides the oscillation frequency by 12.

After RESET input or in the hardware STOP mode, the timer/event counter mode register is reset to 00H.

Fig. 2-21 Timer/Event Counter Mode Register Format

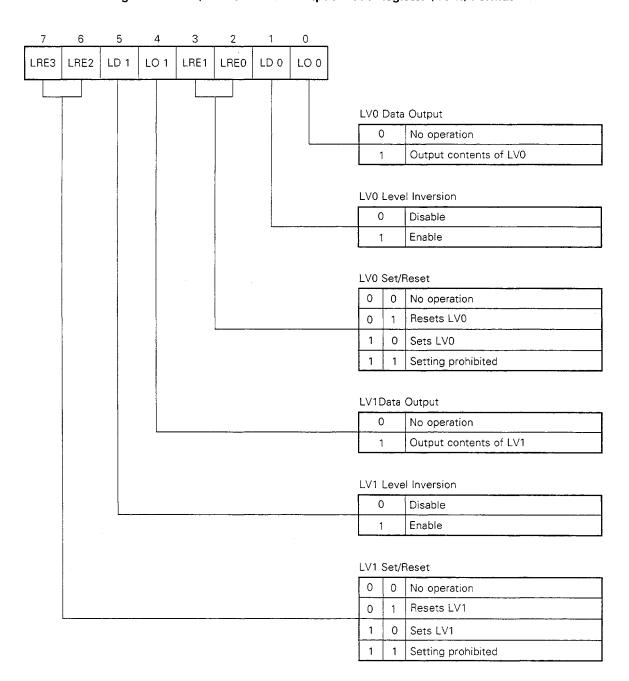

(2) Timer/event counter output mode register (EOM)

This is an 8-bit register which controls the timer/event counters CO0 and CO1 (Counter Output 0, 1) operating mode.

The timer/event counter output mode register bits 0 and 4 (LO0, LO1) control whether or not LV0 and LV1 level are output to the CO0 and CO1 pins, bits 1 and 5 (LD0, LD1) control whether or not LV0 and LV1 level are inverted at an output timing specified by the timer/event counter mode register, bits 2, 3, 6, and 7 (LRE0, LRE1, LRE2, LRE3) control LV0 and LV1 setting/resetting.

Bits LO0, LO1, LRE0, LRE1, LRE2, and LRE3 are automatically reset (0) after individual operations.

After RESET input or in the hardware STOP mode, the timer/event counter output mode register is reset to 00H.

Fig. 2-22 Timer/Event Counter Output Mode Register (EOM) Format

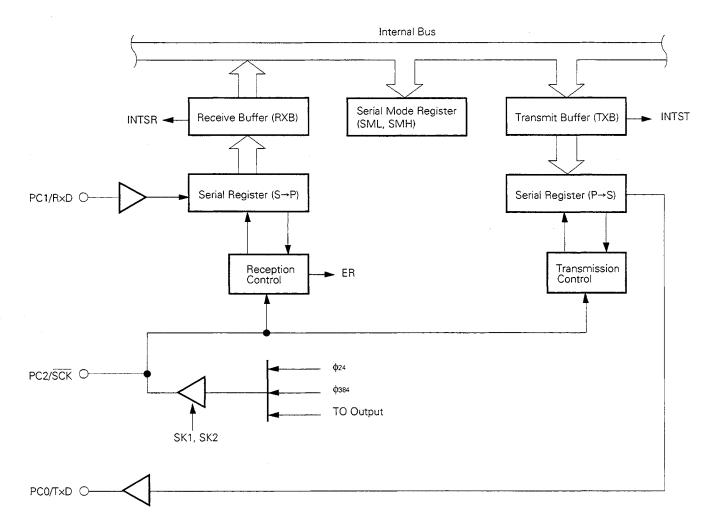

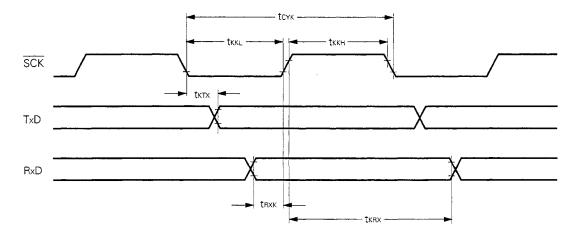

#### 2.8 SERIAL INTERFACE

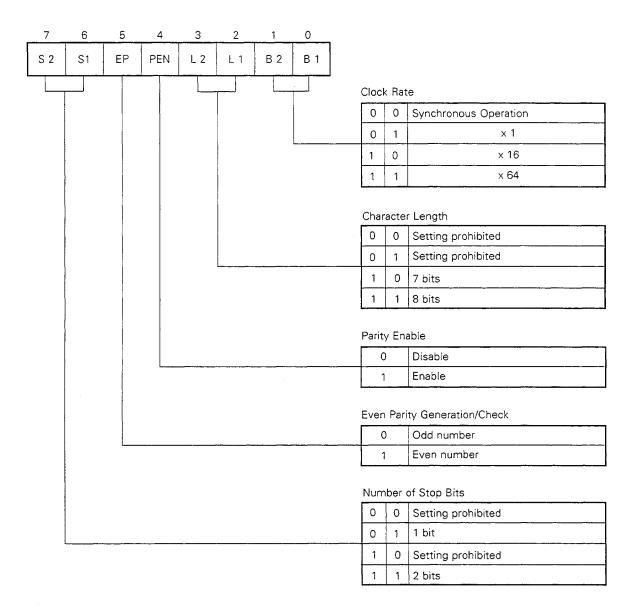

The  $\mu$ PD78C17(A)/78C18(A) have the serial interface using the transmit/receive method by start/stop bit. The three types of operating modes are shown below.

Asynchronous (start-stop) mode: Establishes data bit synchronization and character synchronization by start bit.

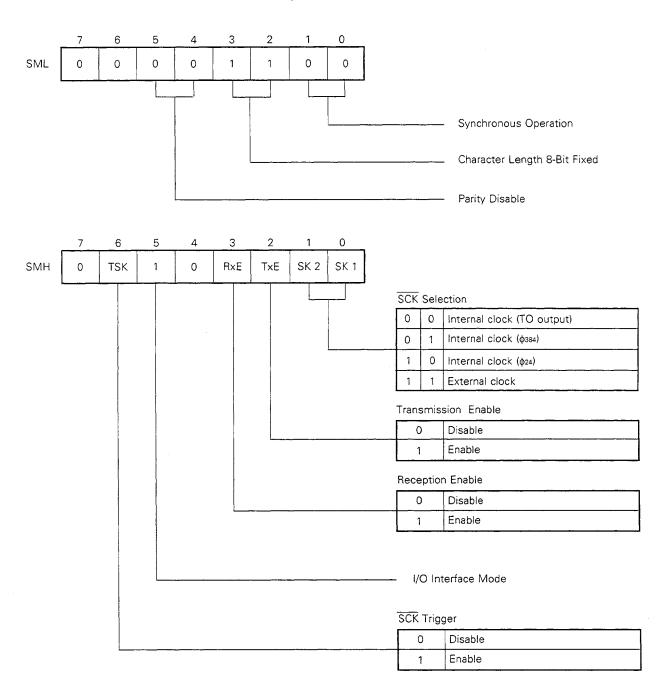

· Synchronous mode

: Data transfer is performed in synchronization with the serial clock.

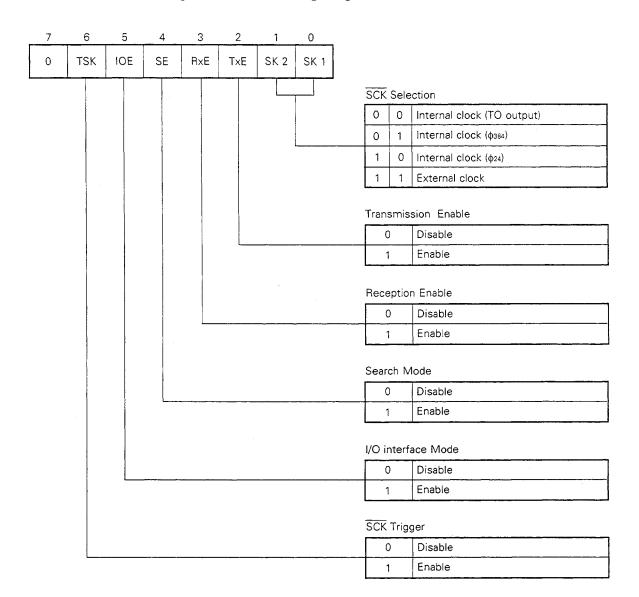

· I/O interface mode

: As for serial data transfer in the  $\mu$ PD7801/78C06A etc., data transfer

is performed in synchronization with the serial clock.

The serial interface block is composed of the serial data input (RxD), serial data output (TxD), 3 serial clock input/output (SCK) pins, transfer control block, two 8-bit serial registers for transmission and reception, and 8-bit transmission buffer and reception buffer (see Fig. 2-23).

As the serial registers and buffers for transmission and reception are provided, transmission or reception is individually performed (full-duplex double buffer transmitter/receiver).

However, the serial clock (SCK) is shared in transmission and reception, and half-duplex transmission/reception is performed in the synchronous mode and I/O mode.

Fig. 2-23 Serial Interface Block Diagram

**Remarks**  $\phi_{24} = f_{xx} \times 1/24$  $\phi_{384} = f_{xx} \times 1/384$  Where, fxx = oscillation frequency (MHz)

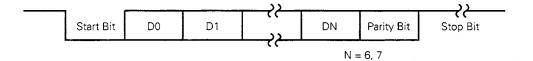

# (1) Asynchronous mode

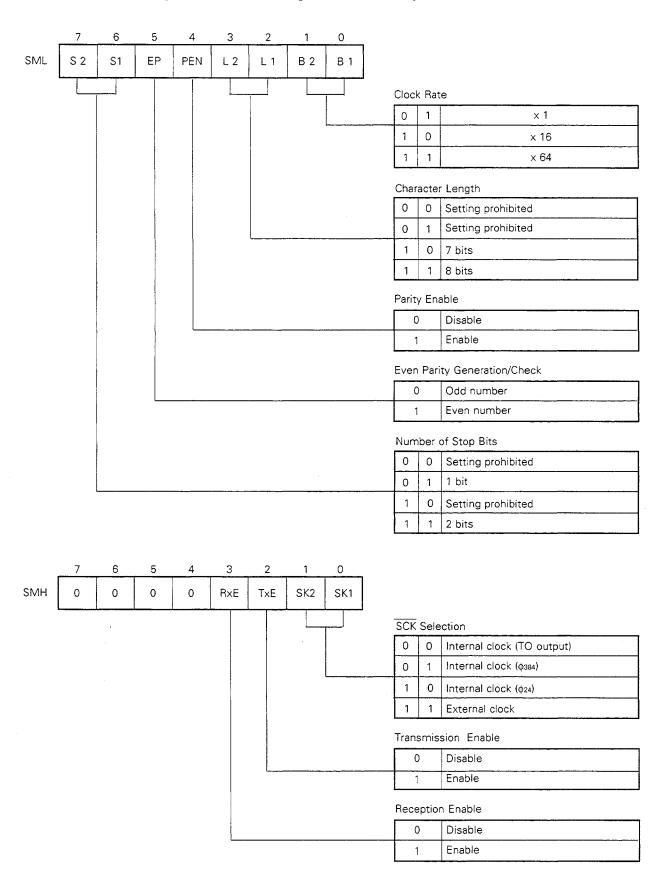

In case of the asynchronous mode, clock rate, character length, number of stop bits, parity enable, and odd or even parity specifications can be controlled by the serial mode register (SML).

Transmission operation is enabled by setting (1) bit 2 (TxE) of the serial mode register (SMH).

If data is written to the transmission buffer by the "MOV TXB, A" instruction and preceding data transfer is terminated, contents of the transmission buffer are transferred to the serial register automatically. The start bit (1 bit), parity bit (odd/even number, no parity), and stop bit (1 or 2 bits) are automatically added to data which is transferred to the serial register. And this data is transmitted from the TxD pin starting from the least significant bit (LSB).

If the transmit buffer is empty, the internal interrupt (INTST) is generated.

Transmission data is transmitted from the TxD pin at the fall of SCK in the clock rate of x 1, x 1/16, or x 1/64 serial clock ( $\overline{SCK}$ ).

The maximum data transfer speed in transmission is set by SCK and clock rate in 12-MHz operation as shown below.

| SCK        | Intern   | al Clock               | External Clock |                        |  |  |

|------------|----------|------------------------|----------------|------------------------|--|--|

| Clock Rate | SCK      | Data Transfer<br>Speed | SCK            | Data Transfer<br>Speed |  |  |

| x 1        | 500 kHz  | 500 kbps               | 660 kHz        | 660 kbps               |  |  |

| x 16       | 2 MHz    | 125 kbps               | 2 MU-          | 125 kbps               |  |  |

| x 64       | 2 IVITIZ | 31.25 kbps             | 2 MHz          | 31.25 kbps             |  |  |

When TxE is "0" or the serial register has no transmitted data, the TxD pin is in the marking state (1). By setting bit 2 (MKST) of the interrupt mask register (MKH), the interrupt (INTST) is disabled.

Fig. 2-24 Asynchronous Data Format

# Fig. 2-25 Serial Mode Register Format in Asynchronous Mode

Receive operation is enabled by setting (1) bit 3 (RxE) of the serial mode register (SMH).

The start bit is confirmed by detecting the low level of RxD input and the low level after 1 or 2 bits. Reception is performed by sampling character bit, parity bit, and stop bit following the low level. When data specified in the serial register from RxD is input, data is transferred to the receive buffer. If the receive buffer is full, the internal interrupt (INTSR) is generated.

By setting (1) bit 1 (MKSR) of the interrupt mask register (MKH), the internal interrupt (INTSR) is disabled.

In reception, odd or even parity is checked (when PEN bit = 1). If data do not match (parity error), if stop bit is low (framing error), or if the next data is transferred to the receive buffer when the receive buffer is full (overrun error), the error flag is set (1).

However, because error interrupt mechanism is not provided, test is executed by the skip instruction (SKIT, SKNIT).

The serial clock (SCK) can be selected as an external or internal clock by the serial mode register (SMH).

Three types of  $\phi_{24}$ ,  $\phi_{384}$ , or TO outputs can be selected as internal clock. This clock can be output to offchip. Or the external serial clock can be input.

By using the internal clock (TO output) as SCK, the data transfer speed can be flexibly changed by program.

The maximum data transfer speed in reception is set by SCK and the clock rate in 12-MHz operation as shown below.

| SCK                  | Interna   | al Clock               | Extern           | External Clock                      |  |  |  |

|----------------------|-----------|------------------------|------------------|-------------------------------------|--|--|--|

| Clock Rate           | SCK       | Data Transfer<br>Speed | SCK              | Data Transfer<br>Speed              |  |  |  |

| × 1 <sup>Note2</sup> | 500 kHz   | 500 kbps               | 660 kHz<br>1 MHz | 660 kbps<br>1 Mbps <sup>Note1</sup> |  |  |  |

| × 16                 | 2 MHz     | 125 kbps               | 2 MHz            | 125 kbps                            |  |  |  |

| × 64                 | 2 (4)1112 | 31.25 kbps             | 2 1411 12        | 31.25 kbps                          |  |  |  |

Notes 1. If data of transfer speed 660 kbps to 1 Mbps is received, 2 stop bits are required.

2. In x 1 clock rate, RxD and SCK synchronization needs to be externally established.

For an example, when data is transferred in the data transfer speed of 110 to 9600 bps, when the timer input clock is set as internal clock ( $\phi_{12}$ ), the timer count value (C) is shown below.

| Oscillation Frequency (MHz)  |      |     |     |     | 11.0592 |    |     | 14.7456 |     |    |     |     |     |    |

|------------------------------|------|-----|-----|-----|---------|----|-----|---------|-----|----|-----|-----|-----|----|

| Data Transfer<br>Speed (bps) | N    |     | 16  |     | 64      |    |     | 16      |     | 64 | 16  |     | 6   | 64 |

|                              | 9600 | C = | 2   |     |         | -  | C = | 3       |     | -  | C = | 4   | C = | 1  |

|                              | 4800 |     | 4   | C = |         | 1  |     | 6       |     | ~  |     | 8   |     | 2  |

|                              | 2400 |     | 8   |     |         | 2  |     | 12      | C = | 3  |     | 16  |     | 4  |

|                              | 1200 |     | 16  |     |         | 4  |     | 24      |     | 6  |     | 32  |     | 8  |

|                              | 600  |     | 32  |     |         | 8  |     | 48      |     | 12 |     | 64  |     | 16 |

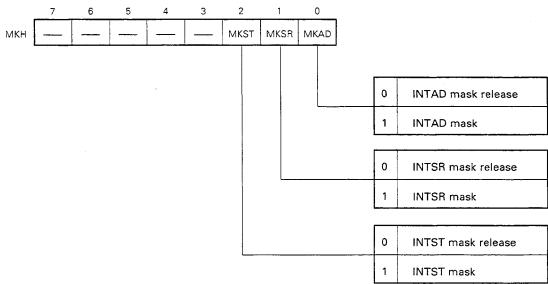

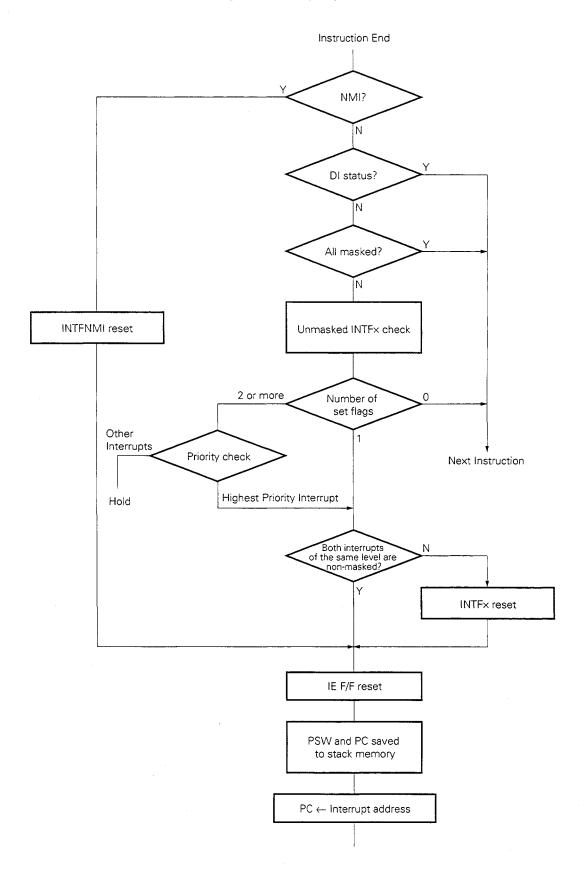

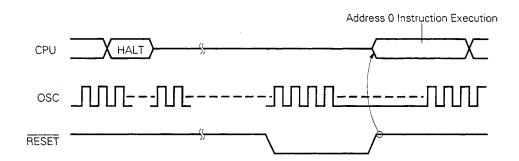

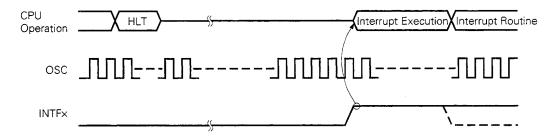

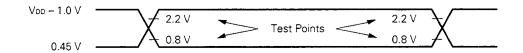

|                              | 300  |     | 64  |     |         | 16 |     | 96      |     | 24 |     | 128 |     | 32 |