### **Brief Description**

The ZSPM4121 battery management load switch can be used to protect a battery from excessive discharge. It actively monitors the battery voltage and disconnects the battery from the load if the battery drops below a set voltage threshold. When the input battery voltage reaches 500mV above the set voltage threshold, the load switch turns on and connects the battery to the load. The 500mV hysteresis between the Off Mode and the On Mode prevents intermittent operation.

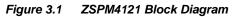

The voltage threshold ( $V_{THRESH}$ ) can be programmed at manufacturing to a customer-selected set point in the voltage range of 1.2V to 4.2V in 100mV increments to support a wide range of applications in consumer, medical, portable, and industrial applications.

This device has ultra-low quiescent current, which makes it ideal for battery-powered applications. Typical quiescent current is 100pA in the Off Mode and 70nA in the On Mode.

The ZSPM4121 includes a slew rate control P-channel load switch, over-current protection, and an open-drain power indicator pin (NPG). The slew-rate controlled turn-on characteristic prevents inrush current and voltage droop on the voltage. The overcurrent limit protects the device in case of an overload, short-circuit, or ground fault event.

## **Benefits**

- Best-in-class ultra-low quiescent current in Off Mode: 100pA (typical)

- Ultra-low quiescent current in On Mode: 70nA (typical)

- Accurate on/off voltage threshold

- Low Rds(on): 175mΩ (typical) @ 5V

## Features

- Threshold voltage options of 1.2V to 4.2V in 100mV steps (factory programmed)

- Wide input voltage range: 1.2V to 5.5V

- Supervisory over-current limit shutdown: (3A)

- Low drop-out disconnect from VCC to loads

- Controlled turn-on slew rate

- 500mV Off Mode to On Mode hysteresis

## **Related IDT Smart Power Products**

• ZSPM4141 Ultra-Low-Power Linear Regulator

## **Available Support**

- Evaluation Kit

- Support Documentation

### **Physical Characteristics**

• Package: 8-pin DFN (2mm x 2mm)

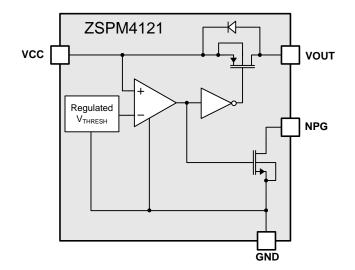

## **ZSPM4121 Block Diagram**

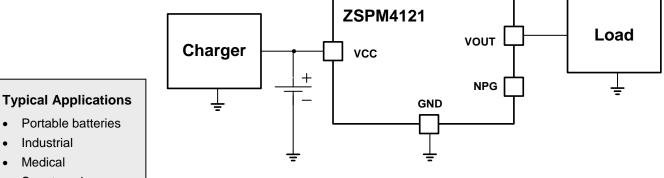

## **Typical Application Circuit**

- Smart cards

- RFID

## **Ordering Information**

| Ordering Code*          | Description                                                                | Package                    |

|-------------------------|----------------------------------------------------------------------------|----------------------------|

| ZSPM4121AI1 <i>W</i> 17 | ZSPM4121 Under-Voltage Load Switch—VTHRESH factory set to 1.7V             | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121AI1W21          | ZSPM4121 Under-Voltage Load Switch—V <sub>THRESH</sub> factory set to 2.1V | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121AI1W23          | ZSPM4121 Under-Voltage Load Switch—VTHRESH factory set to 2.3V             | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121AI1W24          | ZSPM4121 Under-Voltage Load Switch—V <sub>THRESH</sub> factory set to 2.4V | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121AI1W25          | ZSPM4121 Under-Voltage Load Switch—VTHRESH factory set to 2.5V             | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121AI1W26          | ZSPM4121 Under-Voltage Load Switch—V <sub>THRESH</sub> factory set to 2.6V | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121AI1W28          | ZSPM4121 Under-Voltage Load Switch—V <sub>THRESH</sub> factory set to 2.8V | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121AI1W30          | ZSPM4121 Under-Voltage Load Switch—V <sub>THRESH</sub> factory set to 3.0V | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121KIT             | ZSPM4121 Evaluation Kit                                                    |                            |

\* For a 13" reel (3300 parts), replace the W in the ordering code with an R. Custom V<sub>THRESH</sub> values are also available: 1.2V to 4.2V (typical) in 100mV increments.

# RENESAS

# Contents

| 1  | ZSI  | PM4121 Characteristics                 | 5  |

|----|------|----------------------------------------|----|

| 1  | .1.  | Absolute Maximum Ratings               | 5  |

| 1  | .2.  | Thermal Characteristics                | 5  |

| 1  | .3.  | Recommended Operating Conditions       | 5  |

| 1  | .4.  | Electrical Characteristics             | 6  |

| 2  | Тур  | vical Performance Characteristics      | 7  |

| 3  | Des  | scription of Circuit                   | 8  |

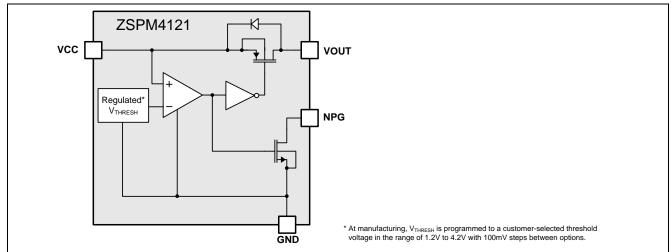

| 4  | App  | plication Circuit                      | 9  |

| 4  | .1.  | Typical Application Circuit            | 9  |

| 5  | Pin  | Configuration and Package              |    |

| 5  | 5.1. | Package Dimensions and Marking Diagram | 10 |

| 5  | 5.2. | Pin Description for 8-Pin DFN (2x2 mm) |    |

| 6  | Lay  | out and Soldering Requirements         | 12 |

| 6  | 5.1. | Recommended Landing Pattern for PCBs   | 12 |

| 6  | 5.2. | Multi-Layer PCB Layout                 | 13 |

| 6  | 5.3. | Single-Layer PCB Layout                | 14 |

| 7  | Orc  | dering Information                     | 15 |

| 8  | Rel  | ated Documents                         | 15 |

| 9  |      | ssary                                  |    |

| 10 | Doo  | cument Revision History                | 16 |

# List of Figures

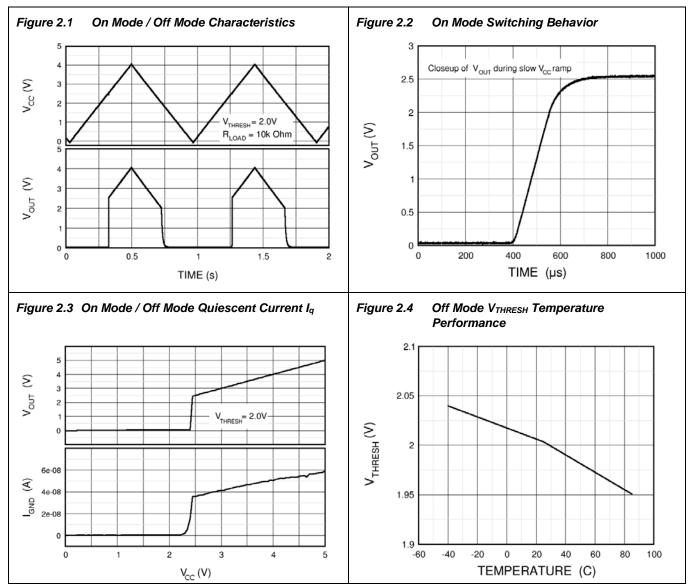

| Figure 2.1 | On Mode / Off Mode Characteristics                             | 7  |

|------------|----------------------------------------------------------------|----|

| Figure 2.2 | On Mode Switching Behavior                                     | 7  |

| Figure 2.3 | On Mode / Off Mode Quiescent Current Iq                        | 7  |

| Figure 2.4 | Off Mode V <sub>THRESH</sub> Temperature Performance           | 7  |

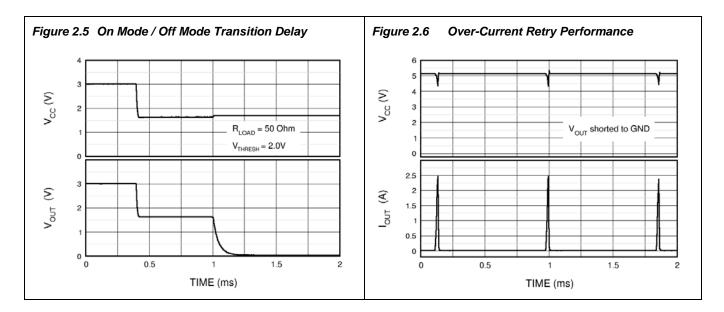

| Figure 2.5 | On Mode / Off Mode Transition Delay                            | 8  |

| Figure 2.6 | Over-Current Retry Performance                                 | 8  |

| Figure 3.1 | ZSPM4121 Block Diagram                                         |    |

| Figure 4.1 | Application Circuit for Disconnecting the Load                 | 9  |

| Figure 5.1 | ZSPM4121 Package Drawing                                       | 10 |

| Figure 5.2 | ZSPM4121 Pin Assignments (top view)                            | 11 |

| Figure 6.1 | Recommended Landing Pattern for 8-Pin DFN                      | 12 |

| Figure 6.2 | Package and PCB Land Configuration for Multi-Layer PCB         | 13 |

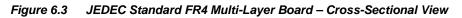

| Figure 6.3 | JEDEC Standard FR4 Multi-Layer Board – Cross-Sectional View    | 13 |

| Figure 6.4 | Conducting Heat Away from the Die using an Exposed Pad Package | 14 |

| Figure 6.5 | Application Using a Single-Layer PCB                           |    |

# List of Tables

| Table 1.1 | Absolute Maximum Ratings                                  | .5 |

|-----------|-----------------------------------------------------------|----|

| Table 1.2 | Thermal Characteristics for 8-Pin DFN (2mm x 2mm) Package | .5 |

| Table 1.3 | Recommended Operating Conditions                          | .5 |

| Table 1.4 | Electrical Characteristics                                | .6 |

| Table 5.1 | Pin Description, 8-Pin DFN (2x2)                          | 11 |

## 1 **ZSPM4121** Characteristics

Stresses beyond those listed under "Absolute Maximum Ratings" (section 1.1) may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those recommended under "Recommended Operating Conditions" (section 1.3) is not implied. Exposure to absolute–maximum conditions for extended periods may affect device reliability.

### 1.1. Absolute Maximum Ratings

Over operating free-air temperature range unless otherwise noted. All voltage values are with respect to network ground terminal.

| Table 1.1 Absolute Maximum Ratings |  |

|------------------------------------|--|

|------------------------------------|--|

| Parameter                                                                                              | Symbol           | Value       | Unit |

|--------------------------------------------------------------------------------------------------------|------------------|-------------|------|

| Maximum voltage applied to the VCC, VOUT, and NPG pins                                                 |                  | -0.3 to 6.0 | V    |

| Electrostatic Discharge – Human Body Model, according to the respective JESD22 JEDEC standard          | 0 2 kV           |             | kV   |

| Electrostatic Discharge – Charged Device Model, according to the respective JESD22-C101 JEDEC standard |                  | 500         |      |

| Operating Junction Temperature Range                                                                   | TJ               | -20 to 85   | °C   |

| Storage Temperature Range                                                                              | T <sub>stg</sub> | -65 to 150  | °C   |

| Lead Temperature (soldering, 10 seconds)                                                               |                  | 260         | °C   |

## 1.2. Thermal Characteristics

#### Table 1.2 Thermal Characteristics for 8-Pin DFN (2mm x 2mm) Package

| θ <sub>JA</sub> (°C/W) <sup>1)</sup> |                                                                                                                    | θ <sub>JC</sub> (°C/W) <sup>2)</sup> |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|

|                                      | 73.1                                                                                                               | 10.7                                 |  |  |

| 1)                                   | This rating assumes a FR4 board only.                                                                              |                                      |  |  |

| 2)                                   | 2) This rating assumes a 1oz. copper JEDEC standard board with thermal vias. See section 6.1 for more information. |                                      |  |  |

## 1.3. Recommended Operating Conditions

#### Table 1.3 Recommended Operating Conditions

| Parameter                                                                                                                                                    | Symbol          | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| Unregulated Supply Input at VCC Pin                                                                                                                          | V <sub>CC</sub> | 1.2 |     | 5.5 | V    |

| Operating Ambient Temperature <sup>1)</sup>                                                                                                                  | T <sub>A</sub>  | -20 |     | 55  | °C   |

| Operating Junction Temperature                                                                                                                               | TJ              | -20 |     | 85  | °C   |

| <ol> <li>Operating ambient temperature is only intended as a guideline. The operating junction temperature requirements must not be<br/>exceeded.</li> </ol> |                 |     |     |     |      |

## 1.4. Electrical Characteristics

Electrical characteristics for  $V_{CC}$  = 1.2V to 5.5V (unless otherwise noted). Minimum and maximum characteristics are tested at  $T_J$  = 25°C.

| Table 1.4 Electrical Characteris |

|----------------------------------|

|----------------------------------|

| Parameter                                | Symbol                | Condition                                                                                                                                                       | Min               | Тур                 | Max                           | Unit |

|------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|-------------------------------|------|

| Input Supply                             |                       |                                                                                                                                                                 |                   |                     |                               |      |

| Input Supply Voltage at VCC pin          | Vcc                   |                                                                                                                                                                 | 1.2               |                     | 5.5                           | V    |

| Quiescent Current: On Mode               | I <sub>q-ON</sub>     | $V_{CC} = 5V$ , no load                                                                                                                                         |                   | 70                  | 150                           | nA   |

| Quiescent Current: Off Mode              | I <sub>q-OFF</sub>    | V <sub>CC</sub> < V <sub>THRESH</sub> , no load                                                                                                                 |                   | 100                 |                               | pА   |

| Load Switch                              |                       |                                                                                                                                                                 |                   |                     |                               |      |

| Over-Current Shutdown                    | loc                   | $V_{CC} = 5.0V$                                                                                                                                                 |                   | 3                   |                               | А    |

| Over-Current Retry Period                | t <sub>oc</sub>       | $V_{CC} = 5.0V$                                                                                                                                                 |                   | 1.7                 |                               | ms   |

| Output Switch Leakage Current            | I <sub>LEAK-SW</sub>  | $V_{CC} < V_{THRESH}$ ; $V_{OUT}$ grounded                                                                                                                      |                   | 100                 |                               | pА   |

| Switch ON-Resistance                     | Rds-on                | $V_{CC} = 5.0V$                                                                                                                                                 |                   | 175                 |                               | mΩ   |

|                                          |                       | $V_{CC} = 3.3V$                                                                                                                                                 |                   | 200                 |                               | mΩ   |

|                                          |                       | V <sub>CC</sub> = 1.8V                                                                                                                                          |                   | 350                 |                               | mΩ   |

| Transition Times                         | ı.                    |                                                                                                                                                                 |                   |                     | <u> </u>                      |      |

| Transition Delay:<br>On Mode to Off Mode | t <sub>d1</sub>       | $V_{OFF} = 2.0V, V_{CC} = 3.0V \rightarrow 1.5V$                                                                                                                |                   | 650                 |                               | μS   |

| Transition Delay:<br>Off Mode to On Mode | t <sub>d2</sub>       | $V_{OFF} = 2.0V, V_{CC} = 1.5V \rightarrow 3.0V$                                                                                                                |                   | 1.7                 |                               | ms   |

| Output Turn-on Rise Time                 | t <sub>ON</sub>       | $V_{CC}$ = 2.5V, $R_{LOAD}$ = 50 $\Omega$                                                                                                                       |                   | 200                 |                               | μs   |

| NPG Output                               | 1                     |                                                                                                                                                                 |                   |                     | <u> </u>                      |      |

| Output Leakage                           | I <sub>LEAK-NPG</sub> | $V_{CC} = 5.0V, V_{NPG} = 5.5V$                                                                                                                                 |                   |                     | 100                           | nA   |

| Low-Level Output Voltage                 | V <sub>OL-NPG</sub>   | I <sub>NPG</sub> = 5 mA                                                                                                                                         |                   |                     | 0.4                           | V    |

| Off Thresholds                           | •                     |                                                                                                                                                                 |                   | •                   |                               |      |

| Off Threshold                            | V <sub>OFF</sub>      | V <sub>THRESH</sub> = customer-selected<br>threshold voltage in the range of<br>1.2V to 4.2V with 100mV steps<br>between options programmed at<br>manufacturing | 0.95 *<br>Vthresh | V <sub>THRESH</sub> | 1.05 *<br>V <sub>THRESH</sub> | V    |

| Off Mode to On Mode Hysteresis           | V <sub>Hys</sub>      | Rising Transition:<br>Off Mode to On Mode                                                                                                                       |                   | 500                 |                               | mV   |

# 2 Typical Performance Characteristics

$T = 25^{\circ}C$  (unless otherwise noted)

## **3 Description of Circuit**

The ZSPM4121 battery management load switch includes an internally generated threshold voltage, comparator with hysteresis, slew rate control for the load switch, a P-channel load switch, and an open-drain indicator pin. When the input battery voltage rises to 500mV above the threshold, the load switch turns on (the On Mode). When the input battery voltage falls to the threshold voltage or below, the load switch is off (the Off Mode), and the quiescent current draw on the battery is in the order of 100pA (typical). The ZSPM4121 threshold voltage is programmed at manufacturing to an option in the range of 1.2V to 4.2V with 100mV steps between options. The 500mV hysteresis between the Off Mode and the On Mode prevents intermittent operation. The ZSPM4121 also provides over-current protection.

# 4 Application Circuit

## 4.1. Typical Application Circuit

## 5 Pin Configuration and Package

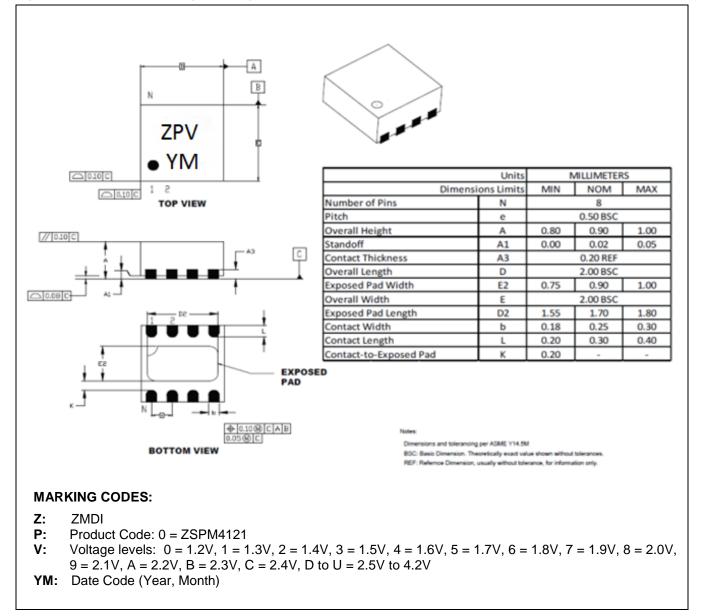

#### 5.1. Package Dimensions and Marking Diagram

Figure 5.1 ZSPM4121 Package Drawing

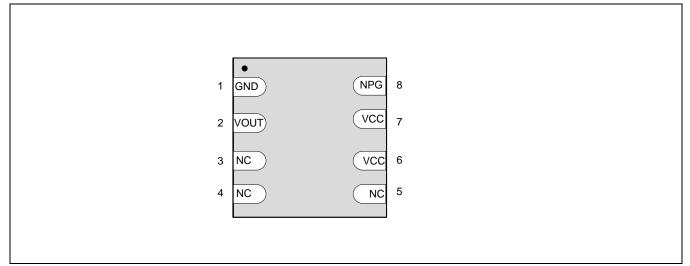

### 5.2. Pin Description for 8-Pin DFN (2x2 mm)

Figure 5.2 ZSPM4121 Pin Assignments (top view)

#### Table 5.1Pin Description, 8-Pin DFN (2x2)

| Pin # | Name | Function | Description                                              |  |

|-------|------|----------|----------------------------------------------------------|--|

| 1     | GND  | Ground   | GND                                                      |  |

| 2     | VOUT | Output   | Output to system load                                    |  |

| 3     | NC   |          | No connection (connect to GND or float)                  |  |

| 4     | NC   |          | No connection (connect to GND or float)                  |  |

| 5     | NC   |          | No connection (connect to GND or float)                  |  |

| 6     | VCC  | Supply   | Supply input (connect to pin 7 and VCC supply rail)      |  |

| 7     | VCC  | Supply   | Supply input (connect to pin 6 and VCC supply rail)      |  |

| 8     | NPG  | Output   | Open-drain N-channel output (low indicates "Power Good") |  |

## 6 Layout and Soldering Requirements

To maximize the efficiency of this package for applications on a single layer or multi-layer printed circuit board (PCB), certain guidelines must be followed when laying out this part on the PCB.

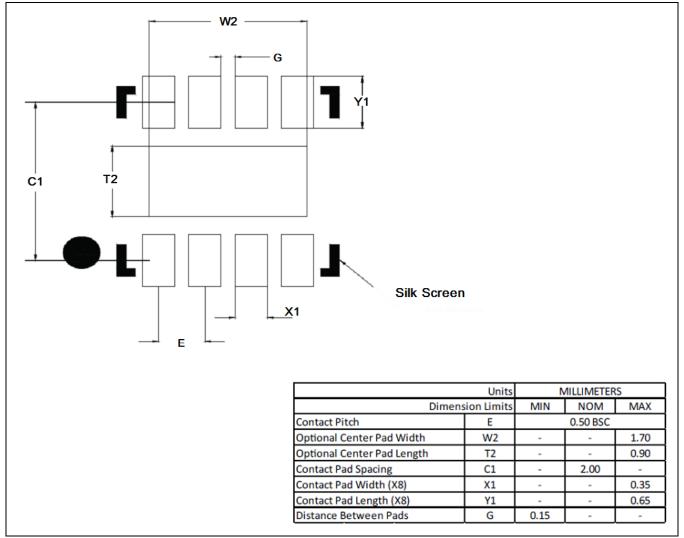

### 6.1. Recommended Landing Pattern for PCBs

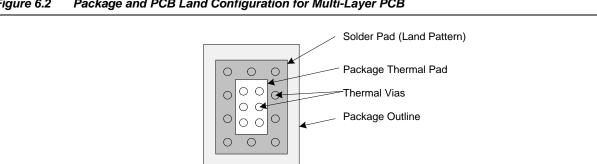

#### 6.2. Multi-Layer PCB Layout

The following are guidelines for mounting the exposed pad ZSPM4121 on a multi-Layer PCB with ground a plane. In a multi-layer board application, the thermal vias are the primary method of heat transfer from the package thermal pad to the internal ground plane. The efficiency of this method depends on several factors, including die area, number of thermal vias, and thickness of copper, etc.

Figure 6.2 Package and PCB Land Configuration for Multi-Layer PCB

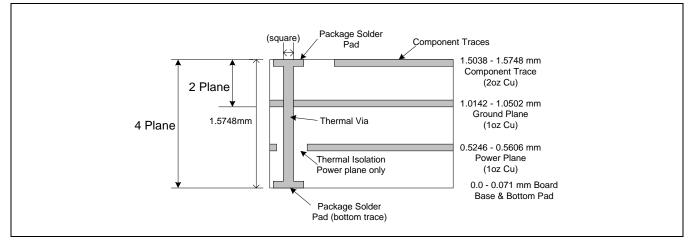

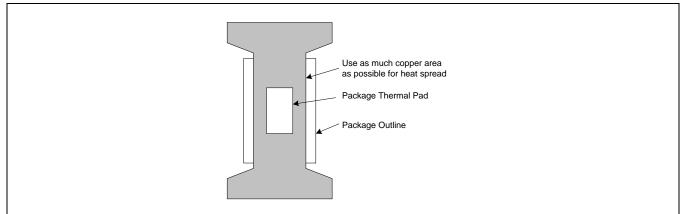

Figure 6.4 is a representation of how the heat can be conducted away from the die using an exposed pad package. Each application will have different requirements and limitations, and therefore the user should use sufficient copper to dissipate the power in the system. The output current rating of the linear regulators might need to be de-rated for higher ambient temperatures. The de-rated value will depend on the calculated worstcase power dissipation and the thermal management implementation in the application.

Figure 6.4 Conducting Heat Away from the Die using an Exposed Pad Package

### 6.3. Single-Layer PCB Layout

Layout recommendations for a single-layer PCB: Utilize as much copper area for power management as possible. In a single-layer board application, the thermal pad is attached to a heat spreader (copper areas) by using a low thermal impedance attachment method (solder paste or thermal conductive epoxy). In both of the methods mentioned above, it is advisable to use as much copper trace as possible to dissipate the heat.

**Important:** If the attachment method is NOT implemented correctly, the functionality of the product is NOT guaranteed. Power dissipation capability will be adversely affected if the device is incorrectly mounted onto the circuit board.

## 7 Ordering Information

| Ordering Code*          | Description                                                                | Package                    |

|-------------------------|----------------------------------------------------------------------------|----------------------------|

| ZSPM4121AI1 <i>W</i> 17 | ZSPM4121 Under-Voltage Load Switch—V <sub>THRESH</sub> factory set to 1.7V | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121AI1 <i>W</i> 21 | ZSPM4121 Under-Voltage Load Switch—V <sub>THRESH</sub> factory set to 2.1V | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121AI1 <i>W</i> 23 | ZSPM4121 Under-Voltage Load Switch—V <sub>THRESH</sub> factory set to 2.3V | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121AI1 <i>W</i> 24 | ZSPM4121 Under-Voltage Load Switch—V <sub>THRESH</sub> factory set to 2.4V | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121AI1W25          | ZSPM4121 Under-Voltage Load Switch—V <sub>THRESH</sub> factory set to 2.5V | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121AI1W26          | ZSPM4121 Under-Voltage Load Switch—V <sub>THRESH</sub> factory set to 2.6V | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121AI1 <i>W</i> 28 | ZSPM4121 Under-Voltage Load Switch—V <sub>THRESH</sub> factory set to 2.8V | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121AI1W30          | ZSPM4121 Under-Voltage Load Switch—V <sub>THRESH</sub> factory set to 3.0V | 8-pin DFN / 7" Reel (2500) |

| ZSPM4121KIT             | ZSPM4121 Evaluation Kit                                                    |                            |

\* For a 13" reel (3300 parts), replace the W in the ordering code with an R. Custom V<sub>THRESH</sub> values are also available: 1.2V to 4.2V (typical) in 100mV increments.

## 8 Related Documents

| Document                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------|

| ZSPM4121 Feature Sheet                                                                                               |

| ZSPM4121 Evaluation Kit Description                                                                                  |

| ZSPM4121 Application Note—Low Power<br>Battery Control and Voltage Regulator<br>Solutions for Remote Sensor Networks |

Visit IDT's website <u>www.IDT.com</u> or contact your nearest sales office for the latest version of these documents.

# 9 Glossary

| Term | Description                               |  |

|------|-------------------------------------------|--|

| PG   | Power Good (NPG = Power Good, active low) |  |

| RFID | Radio Frequency Identification            |  |

| SPM  | Smart Power Management                    |  |

# **10** Document Revision History

| Revision | Date             | Description                                                                                |

|----------|------------------|--------------------------------------------------------------------------------------------|

| 1.00     | April 30, 2012   | First release                                                                              |

| 1.01     | February 7, 2013 | Addition of "Electrostatic Discharge – Charged Device Model" specification in section 1.1. |

|          |                  | Update for block diagram.                                                                  |

|          |                  | Updates for V designation in marking codes in section 5.                                   |

|          |                  | Edits for clarity.                                                                         |

|          |                  | Update to IDT contact information.                                                         |

|          | January 29, 2016 | Changed to IDT branding.                                                                   |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.