# RENESAS

### ClockMatrix TDC

This document explains how to use the Input and Output Time-to-Digital Converters (TDCs) in <u>ClockMatrix</u> devices. It is intended to complement the <u>ClockMatrix TDC Application Note</u>.

## Contents

| 1. | Inpu | t TDC                                | 2  |

|----|------|--------------------------------------|----|

|    | 1.1  | Main Screen                          | 2  |

|    | 1.2  | CH2 Phase Measurement Mode           | 3  |

|    | 1.3  | Registers                            | 4  |

|    | 1.4  | Reading a Measurement                | 5  |

| 2. | Outp | out TDC                              | 6  |

|    | 2.1  | Main Screen                          | 6  |

|    | 2.2  | Masters and Slaves                   | 6  |

|    | 2.3  | Combo Bus                            | 7  |

|    | 2.4  | Master Divider Frequency             | 7  |

|    | 2.5  | Global Sync Enable (GSE)             |    |

|    | 2.6  | Configuration                        | 8  |

|    | 2.7  | Visuals                              | 10 |

|    | 2.8  | Initial Alignment Time (Single Shot) |    |

|    | 2.9  | Phase Correction                     | 11 |

| 3. | Revi | sion History                         | 11 |

## 1. Input TDC

### 1.1 Main Screen

| 8A34001 / 8A34001P V8.0.0<br>Firmware: PR4.8.6<br>Display input and output labels 🔲 📑 |       | 50MHz                                    | Configure GPIOs Configure Output<br>Power Estimate Configure Input T<br>Configure PWM Scratch Registe |

|---------------------------------------------------------------------------------------|-------|------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Quick View                                                                            |       | SYS APLL<br>13.5GHz<br>System DPLL<br>XO | To DCOs Disable Unused Channe<br>Configure 800MHz                                                     |

| Enable Frequency                                                                      | 25MHz | Channel 0<br>DPLL Mode                   | Configure                                                                                             |

| С.K8 -                                                                                | 25MHz | Channel 1                                | Configure                                                                                             |

| Сске -                                                                                |       | DPLL Mode                                |                                                                                                       |

|                                                                                       |       | Channel 2<br>Phase Measurement           | Configure                                                                                             |

| 🖆 📃 🚰 сікз –                                                                          |       |                                          |                                                                                                       |

- Any channel can be used for Phase Measurement mode (i.e., to measure the phase between two different inputs).

- Outputs are still useable for Synthesizer or DCO (FCW) mode when in Phase Measurement mode.

### 1.2 CH2 Phase Measurement Mode

(

- Clk0 and CLK1 are used for Phase Measurement mode and must be the same frequency.

- Two types:

- Phase Status has a resolution of 50ps.

- Filter Status has a resolution of less than 1ps.

- Resolution is the step size.

- Filter Status is only activated when High Precision mode is enabled (see section 1.3).

- The "read" button gives the phase difference between CLK0 and CLK1.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Channel 2                                                                                      | 💼 🎦 Global Sync Enable                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Mode of Operation: Phase Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                |                                                     |

| Phase Measurement<br>Low precision (configure Input TDC to switch to high precis<br>REF: CLK0<br>PHASE_STATUS<br>PHASE_STATUS<br>Phase Measurement<br>Phase Status<br>Phase Status<br>Pha |                                                                                                | DCO.Omly<br>DCO.Omly<br>H35GHz<br>PCO<br>PCO<br>PCO |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Combo Mode - Slave                                                                             | Enable secondary combo source                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Clocks to Measure read<br>Reference Clock: CLK0<br>Feedback Clock: CLK1 ♥<br>Phase Status: Ops |                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                | ToD Synchronization<br>Enable:                      |

#### 1.3 Registers

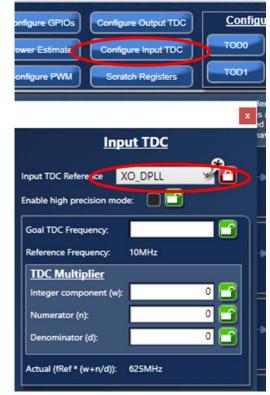

- Input TDC Reference source can use the XTAL or the XO\_DPLL (if available).

- The TDC source determines the accuracy.

- For small phase offsets using phase measurement such as 1ns or 1ps, XTAL or XO\_DPLL does not make a difference.

- For large phase offsets such as 1us or 1ms, XTAL or XO\_DPLL makes a difference

|              | XTAL     | XO DPLL  |

|--------------|----------|----------|

| Phase Offset | 50 ppm   | 5 ppm    |

| 1.00E-03     | 5.00E-08 | 5.00E-09 |

| 1.00E-06     | 5.00E-11 | 5.00E-12 |

| 1.00E-09     | 5.00E-14 | 5.00E-15 |

| 1.00E-12     | 5.00E-17 | 5.00E-18 |

- Enabling High Precision mode activates Loop Filter Status for increased resolution (50ps to < 1ps).</li>

- Resolution is the step size.

- If High Precision mode is OFF, TDC frequency is 625MHz by default.

- If High Precision mode is ON, TDC frequency is skewed such that it is not an integer multiple of the input frequency (for more information, see the *ClockMatrix TDC Application Note*).

- Enabling High Precision mode prevents DCO (FCW) access, but Synthesizer still available.

#### 1.4 Reading a Measurement

- Enabling High Precision mode activates Loop Filter Status for increased resolution (50ps to < 1ps).</li>

- Resolution is the step size.

- If High Precision mode is OFF, TDC frequency is 625MHz by default.

- If High Precision mode is ON, TDC frequency is skewed such that it is not an integer multiple of the input frequency (for more information, see the *ClockMatrix TDC Application Note*).

- Enabling High Precision mode prevents DCO (FCW) access, but Synthesizer still available.

|                                                      |                                                                        | Channel 2                                                                                                               | 🔲 🚰 Global Sync Enable                                                                                 |

|------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| ode of Operation:                                    | Phase Measurement                                                      |                                                                                                                         | ر <u>ا</u> ل                                                                                           |

| Phase Measurem<br>figh precision (confi<br>REF. CLK0 | nent<br>gure Input TDC to switch to low p<br>PHASE_STATUS<br>Decimator | PLITER_STATUS                                                                                                           | DCO Only<br>13.5GP<br>III 25GP<br>III 25GP<br>III 25GP<br>III 25GP<br>III 25GP<br>III 25GP<br>III 25GP |

|                                                      |                                                                        | Combo Mode - Slave                                                                                                      | Enable secondary combo source                                                                          |

|                                                      |                                                                        | Clocks to Measure<br>Reference Clock: CLK0<br>Feedback Clock: CLK1<br>Phase Satus: 1.05ms<br>Loop Filter Status: 1.06ms |                                                                                                        |

|                                                      |                                                                        |                                                                                                                         | ToD Synchronization<br>Enable:                                                                         |

## 2. Output TDC

#### 2.1 Main Screen

| /8A34001P V8.0.0<br>: PR4.8.8<br>nput and output labels 💿 💼 | TCXO/OCXO 49.152MHz                         | Power Estimate Configur      | e Input TDC TOD2<br>I Registers TOD1 TOD3                                                                                                           | EEPROMUMAY                                                                           |

|-------------------------------------------------------------|---------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| ok View                                                     | SYS APLL<br>13.4676GHz<br>System DPLL<br>xo | To DCOs Disable Unuse        | d Channels<br>DCO frequencies and output dividers that<br>outputs. To speed up entry of output freq<br>finder until you have entered all outputs, i | can provide the desired<br>encies, disable the solution<br>and then enable it again. |

| Frequency                                                   | CLK0 Channel 0<br>500MHz                    | Configure                    | 500MHz 00 10MHz •                                                                                                                                   | enable: C G<br>hood<br>LVOS 1.8V                                                     |

| сия                                                         | DPLL Mode<br>Combo: Syste                   | m DPLL                       | 500MHz at 500MHz                                                                                                                                    | enable: Desired:                                                                     |

| CLK1                                                        | <u>Channel 1</u><br>1000MHz<br>Synthesizer  | Configure                    | 1000MHz 02 10MHz                                                                                                                                    | enable: C G Desired:                                                                 |

|                                                             | Channel 2<br>750MHz                         | m DPLL Channel 0 Configure 0 | 1000MHz 03 20MHz •                                                                                                                                  | enable: Desired:                                                                     |

| сиз                                                         |                                             | m DPLL Channel 0             | 750MHz • C1 25MHz •                                                                                                                                 | enable: Desired:                                                                     |

| CLK11                                                       | <u>Channel 3</u>                            | Configure                    |                                                                                                                                                     | LVDS 1.8V                                                                            |

- Output TDCs enable output alignment of outputs from different channels.

- The example below aligns Q0, Q2, and Q4.

- Outputs from the same channel are obviously aligned and do not require a TDC: Q0 and Q1 or Q2 and Q3.

### 2.2 Masters and Slaves

- Master and slave satellites are assumed and are connected through the combo bus.

- Master normally has an input (Ch0):

- DPLL mode

- Satellite slaves (Ch1 and CH2) follow the master (Ch0):

- Synthesizer, DCO (FCW/PCW), or Phase Measurement mode

- Any stimulus on the master is propagated to the slaves through the combo mode.

- Combo mode passes only frequency (change in phase).

- Combo mode does not pass edge information.

### 2.3 Combo Bus

- All three Channel Combo configs are shown above.

- Ch0 has one master: sysDPLL.

- Ch1 and Ch2 have two masters each: Ch0 and sysDPLL.

- Slaves always inherit the master of its master (since Ch0 has sysDPLL as its master, Ch1 and Ch2 must also have sysDPLL as their master as well as Ch0).

#### 2.4 Master Divider Frequency

| Channel 0                                                   | Global Sync Enable | Channel 1                                                                                             | 🔽 🎦 Global Sync Enable | Channel 2                     | Global Sync Enable |

|-------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------|------------------------|-------------------------------|--------------------|

|                                                             | <u>ل</u>           | × 🖻                                                                                                   | ų (L)                  |                               | d <b>u</b> h       |

| DCO Config for Channel 0                                    | SYS APLL           | DCO Config for Channel 1                                                                              | SYS APLL               | DCO Config for Channel 2      | SYS APLL           |

| Goal DCO Frequency: 500                                     | 13.4676GHz         | Goal DCO Frequency:                                                                                   | 13.4676GHz             | Goal DCO Frequency: 750       | 13.4676GHz         |

| Fractional Divider                                          | 500MHz             | Fractional Divider                                                                                    | 1000MHz                | Fractional Divider            | 750MHz             |

| Numerator (M): 32767500000000 5<br>Denominator (N): 65535 5 |                    | Numerator (M):         6553500000000         65535           Denominator (N):         65535         6 |                        | Numerator (M): 49151250000000 |                    |

| Actual DCO Frequency: 500MHz                                |                    | Actual DCO Frequency: 1000MHz                                                                         |                        | Denominator (N): 65535        |                    |

| Master Divider: 100                                         |                    | Master Divider: 200                                                                                   |                        | Master Divider: 150           |                    |

|                                                             |                    |                                                                                                       |                        |                               |                    |

- For alignment to occur, the output of the master divider must all be the same frequency for every channel involved:

- Ch0 MD frequency = 500MHz/100 = 5MHz

- Ch1 MD frequency = 1000MHz/200 = 5MHz

- Ch2 MD frequency = 750MHz/150 = 5MHz

- The higher the master divider frequency, the faster the alignment.

- The master divider frequency must be a common factor of each output frequency:

- 5MHz is a factor of Q0 = 10MHz, Q2 = 10MHz, and Q4 = 25MHz

### 2.5 Global Sync Enable (GSE)

| Channel 0<br>✓                                                     | 🖉 🙆 Global Sync Enable | Channel 1                                            | 🖉 🦳 Global Sync Enable | Channel 2                                           | 🖉 🦳 Global Sync Enable |

|--------------------------------------------------------------------|------------------------|------------------------------------------------------|------------------------|-----------------------------------------------------|------------------------|

| ×                                                                  | d <u>D</u> b           |                                                      | d Dh                   |                                                     | , Ch                   |

| DCO Config for Channel 0                                           | SYS APLL               | DCO Config for Channel 1                             | SYS APLL<br>13.4676GHz | DCO Config for Channel 2                            | SYS APLL<br>13.4676GHz |

| Goal DCO Frequency: 500 😭                                          | 13.4676GHz             | Goal DCO Frequency: 1000                             | (13.40/rbuHz)          | Goal DCO Frequency: 750                             |                        |

| Fractional Divider           Numerator (M):         32767500000000 | S00MHz                 | Fractional Divider Numerator (M): 6553500000000      | 1000MHz                | Fractional Divider Numerator (M): 49151250000000    | 750MHz                 |

| Denominator (N): 65535                                             |                        | Denominator (N): 65535                               |                        | Denominator (N): 65535                              |                        |

| Actual DCO Frequency: 500MHz<br>Master Divider: 100                |                        | Actual DCO Frequency: 1000MHz<br>Master Divider: 200 |                        | Actual DCO Frequency: 750MHz<br>Master Divider: 150 |                        |

|                                                                    |                        |                                                      |                        |                                                     |                        |

- GSE must be enabled for all channels involved.

- GSE performs the initial snap to align all outputs (coarse phase alignment).

## 2.6 Configuration

| T                                  | CXO/OCXO<br>12.8MHz | 49.1521       | 1                | Configure GP<br>Power Estima<br>Configure PV | ate Con      | igure Outp<br>figure Inpi<br>ratch Reg |                    | Configur<br>TOD0<br>TOD1 | TOD3      |                               | Configure Seria               |                       | vare Utility |

|------------------------------------|---------------------|---------------|------------------|----------------------------------------------|--------------|----------------------------------------|--------------------|--------------------------|-----------|-------------------------------|-------------------------------|-----------------------|--------------|

|                                    |                     |               |                  |                                              | Output       | TDC C                                  | onfig              |                          |           |                               |                               |                       |              |

| Enable Output T<br>Reference Clock |                     | L 🗸 🖸         | Fast Lock Enable | Delay:                                       | 0 🗂          | 500µs                                  | Fast Lock [        | ) isable Delay:          |           | 0 🚰 500µs                     |                               | read                  | 1            |

|                                    | Source              | <u>Target</u> | Mode             |                                              | Type         |                                        | <u>Align Reset</u> |                          |           | <u>Samples</u><br>(0 == 4096) | <u>Target Phase</u><br>Offset | Measurement<br>Status | Go           |

| Output TDC 0                       | DPLL0 ~             | DPLL0 ~       | alignment        | contin                                       | nuous Y      | keep                                   | accumulated        | Align                    | ment Mask | 0                             | •<br>•                        |                       |              |

| Output TDC 1                       | DPLL0 ~             | DPLL0 Y       | measurement      | _                                            |              |                                        |                    |                          | x nt Mask |                               |                               | 0                     | ] 🖬 🔂        |

| Output TDC 2                       | DPLLO Y             | DPLLO Y       | measurement      | ✓ sinc                                       |              | -                                      | Alignmen           | -                        | nt Mask   | 0                             | 0                             | 0                     | ] 🗆 🔁        |

| Output TDC 3                       |                     | DPLLO Y       | measurement      | Sinc                                         | DPLL0        |                                        | DPLL4<br>DPLL5     |                          | nt Mask   | 0                             |                               | 0                     | 1 🗆 🗃        |

| output for 5                       |                     |               | measurement      |                                              | DPLL2        | 2                                      | DPLL6              |                          |           | 2                             | <b></b>                       |                       |              |

|                                    |                     | Synthesize    | r                |                                              | DPLL3        |                                        | DPLL7              |                          |           |                               |                               |                       |              |

|                                    |                     | Combo: Sj     | ystem DPLL       | Channel 0                                    | Align Target | Mask                                   | 00000              | 110                      | 251       | H7 . N                        |                               | enable: 🔽 📑 D         | esired:      |

- Up to four different Output TDCs can be used individually.

- Output TDCs perform fine phase alignment.

- The Enable and Go buttons must be checked. Order is not important if saving to a TCS file. If connected to a device, the Go button must be last button clicked in entire box.

| nable Output T | DC: 🛛 🖸 |                       |                       |        | Output  | TDC C | onfig             |             |             |                               |                                      |                       |       |

|----------------|---------|-----------------------|-----------------------|--------|---------|-------|-------------------|-------------|-------------|-------------------------------|--------------------------------------|-----------------------|-------|

| eference Clock |         | LL 👻 🎦                | Fast Lock Enable Dela | iy:    | 0 📑     | 500µs | Fast Lock         | DisableDela | iy:         | 0 👩 500µs                     |                                      | read                  |       |

|                | Source  | <u>Target</u>         | Mode                  |        | Туре    |       | Align Reset       |             |             | <u>Samples</u><br>(0 == 4096) | <u>Target Phase</u><br><u>Offset</u> | Measurement<br>Status | Go    |

| Output TDC 0   | DPLLO ~ | DPLLO Y               | alignment 🛛 🖌         | contir | nuous 👻 |       | accumulate        | d 🗡 🗛       | gnment Mask | ۰<br>۲                        | 0                                    | 0                     | ] 🛛 🕻 |

| output TDC 1   | DPLLO ~ | DPLLO Y               | measurement Y         | sinc   |         |       |                   |             | x nt Mask   | 0                             | 0                                    | 0                     | ] 🗆 ( |

| utput TDC 2    | DPLLO Y | DPLLO Y               | measurement Y         | sind   |         |       | Alignmen<br>DPLL4 | nt Mask     | nt Mask     | ۰<br>۲                        | ہ<br>21                              | 0                     | ] 0(  |

| utput TDC 3    | DPLLO Y | DPLLO Y               | measurement ¥         | sind   |         |       |                   |             | nt Mask     | 0                             | 0                                    | 0                     |       |

|                |         | /bumHz<br>Synthesizer |                       | -(     | DPLL3 ( |       |                   |             |             |                               | > nQ3                                |                       |       |

- Reference clock: XO\_DPLL or XTAL. Select XO\_DPLL for better accuracy, if possible.

- Source: DPLL0 is the Source (master) in this example.

- Mode: choose Alignment ode to align all slaves.

- When Alignment mode is chosen, Target is ignored and Alignment Mask selects the slaves.

- Measurement mode is for measuring the phase between the Source and Target.

- Type: Select continuous for continuous alignment instead of a single alignment.

- Samples: 0 selects 4096 samples.

Note: More samples means more averaging.

#### 2.7 Visuals

| System DPLL<br>○                    | Configure |

|-------------------------------------|-----------|

| Channel 0<br>500MHz<br>DPLL Mode    | Configure |

| Combo: System DPLL                  |           |

| Channel 1<br>1000MHz<br>Synthesizer | Configure |

| Combo: System DPLL                  | Channel 0 |

| Channel 2<br>750MHz                 | Configure |

| Synthesizer                         |           |

| Combo: System DPLL                  | Channel 0 |

- 0\* indicates the Source for Output TDC 0.

- 0 indicates the Alignment Mask Slaves for Output TDC 0.

### 2.8 Initial Alignment Time (Single Shot)

$Time_{Output \ TDCAlign} = \frac{N_{samples}N_{slaves}}{\min(10kHz, MDF)}$

The equation calculates the initial alignment time (single shot mode):

- Subsequent alignments (continuous mode) are not included

- Nsamples is the number of samples used for averaging

- MDF is the Master Divider Frequency

- N<sub>slaves</sub> is the number of slaves or satellites being used

- Global Sync Enable (GSE) is assumed to be enabled

- GSE performs initial coarse phase adjustment (large output jumps)

- Output TDC performs fine phase adjustment (small output jumps)

- Output TDC Status Register will report when the alignment is done, but that time may be 2x the above time if samples have an average above the threshold of 50ps

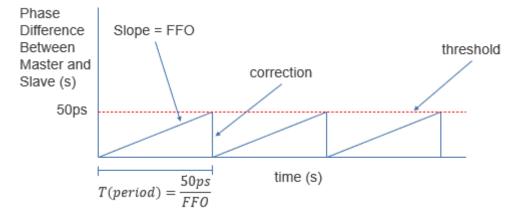

#### 2.9 Phase Correction

- TDC mechanism only adjusts the phase of the satellite channel when it drifts by more than 50ps.

- The 50ps threshold is fixed

- Truncation error when DCO frequencies are different can be up to 0.0032ppt, which would mean a correction every 4.3 hours. In reality the truncation error can be smaller depending on actual DCO frequencies.

- The correction happens at a maximum speed of 244ppm or 244 us/s.

### 3. Revision History

| Revision | Date         | Description      |

|----------|--------------|------------------|

| 1.00     | Nov 23, 2022 | Initial release. |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.