# IDT<sup>®</sup> 89HPES24NT6AG2 PCI Express<sup>®</sup> Switch

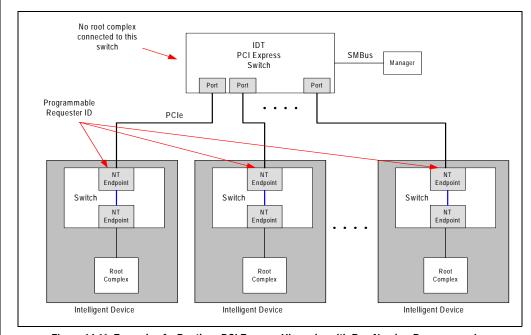

# **User Manual**

January 2013

6024 Silver Creek Valley Road, San Jose, California 95138

Telephone: (800) 345-7015 • (408) 284-8200 • FAX: (408) 284-2775

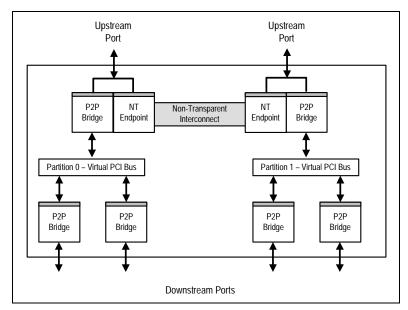

Printed in U.S.A.

©2013 Integrated Device Technology, Inc.

# GENERAL DISCLAIMER

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

# CODE DISCLAIMER

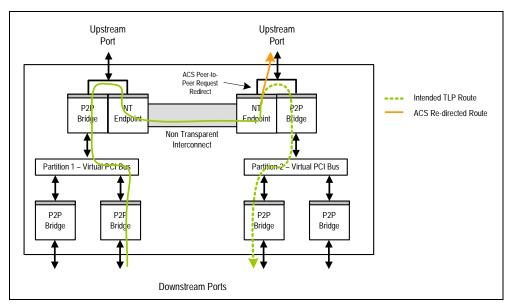

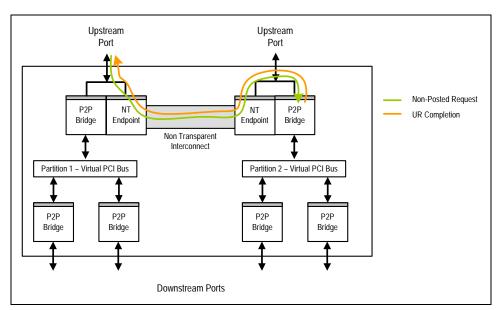

Code examples provided by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of the code examples below is completely at your own risk. IDT MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND CONCERNING THE NONINFRINGEMENT, QUALITY, SAFETY OR SUITABILITY OF THE CODE, EITHER EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. FURTHER, IDT MAKES NO REPRESENTATIONS OR WARRANTIES AS TO THE TRUTH, ACCURACY OR COMPLETENESS OF ANY STATEMENTS, INFORMATION OR MATERIALS CONCERNING CODE EXAMPLES CONTAINED IN ANY IDT PUBLICATION OR PUBLIC DISCLOSURE OR THAT IS CONTAINED ON ANY IDT INTERNET SITE. IN NO EVENT WILL IDT BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, INCIDENTAL, INDIRECT, PUNITIVE OR SPECIAL DAMAGES, HOWEVER THEY MAY ARISE, AND EVEN IF IDT HAS BEEN PREVIOUSLY ADVISED ABOUT THE POSSIBILITY OF SUCH DAMAGES. The code examples also may be subject to United States export control laws and may be subject to the export or import laws of other countries and it is your responsibility to comply with any applicable laws or regulations.

# LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- 1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

IDT, the IDT logo, and Integrated Device Technology are trademarks or registered trademarks of Integrated Device Technology, Inc.

# **About This Manual**

# **Notes**

# **Overview**

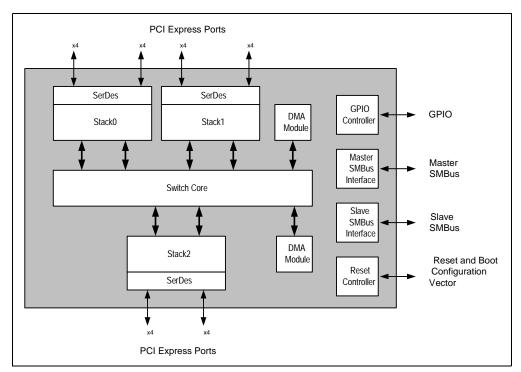

This user manual includes hardware and software information on the 89HPES24NT6AG2, a member of IDT's PRECISE™ family of PCI Express® switching solutions offering the next-generation I/O interconnect standard.

# **Finding Additional Information**

Information not included in this manual such as mechanicals, package pin-outs, and electrical characteristics can be found in the data sheet for this device, which is available from the IDT website **(www.idt.com)** as well as through your local IDT sales representative.

# **Content Summary**

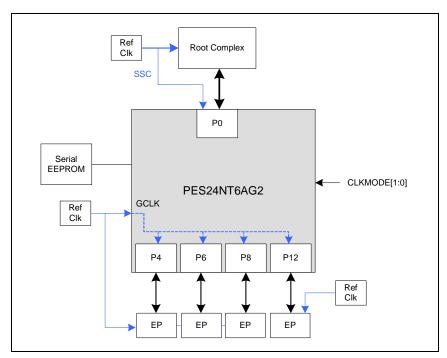

**Chapter 1**, "PES24NT6AG2 Device Overview," provides an introduction to the performance capabilities of the 89HPES24NT6AG2 and a high level architectural overview of the device.

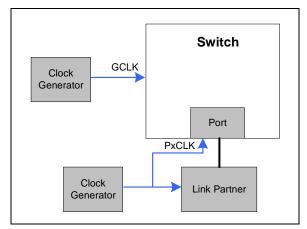

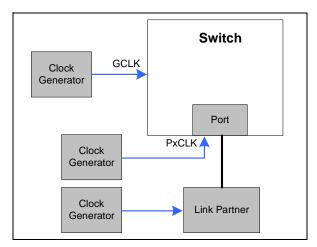

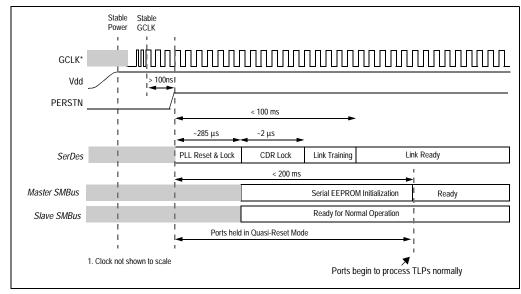

Chapter 2, "Clocking," provides a description of the PES24NT6AG2 clocking architecture.

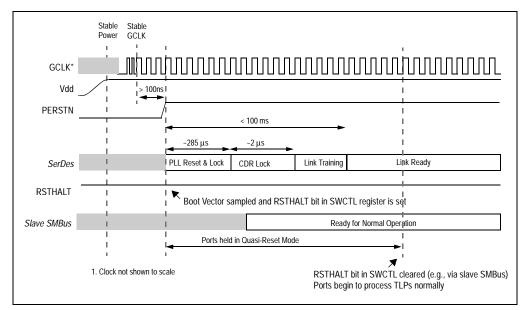

**Chapter 3**, "Reset and Initialization," describes the PES24NT6AG2 reset operations and initialization procedure.

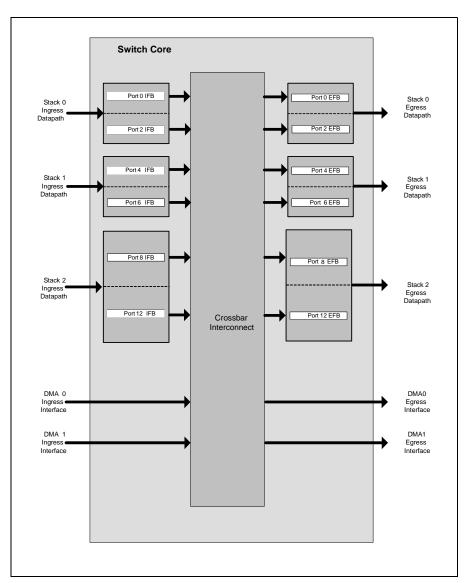

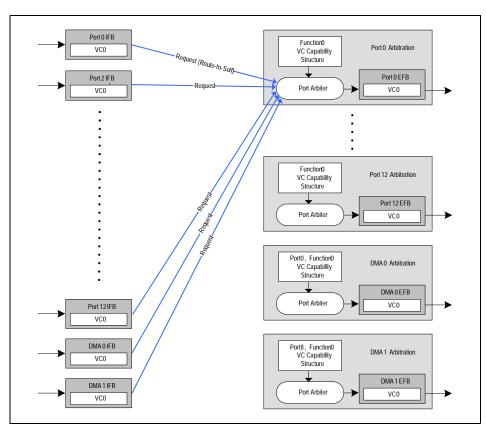

Chapter 4, "Switch Core," provides a description of the PES24NT6AG2 switch core.

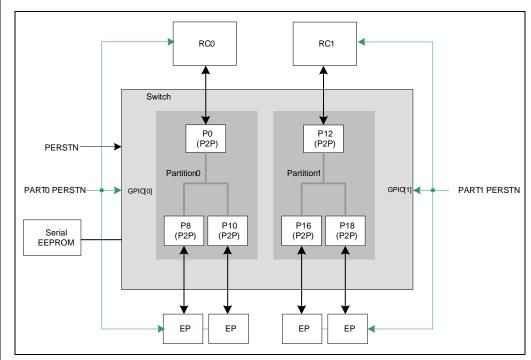

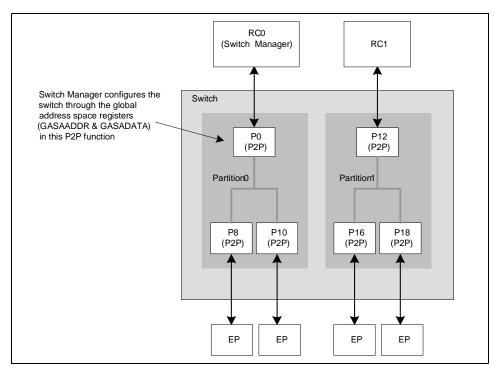

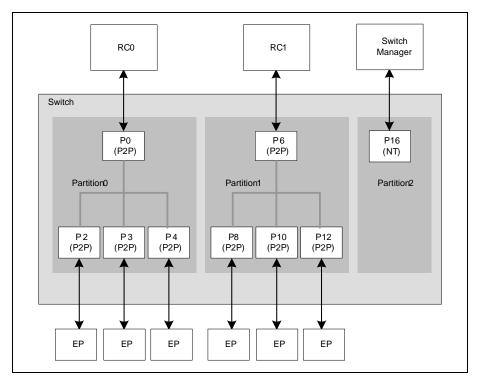

**Chapter 5**, "Switch Partitions," describes how the PES24NT6AG2 supports up to 6 active switch partitions.

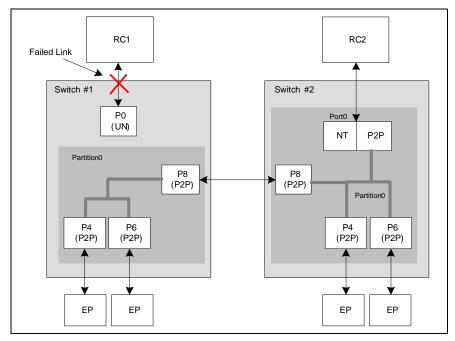

**Chapter 6**, "Failover," provides a description of the flexible failover mechanism that allows the construction of highly-available systems.

**Chapter 7, "Link Operation,"** describes the operation of the link feature including polarity inversion, link width negotiation, and lane reversal.

**Chapter 8**, "SerDes," describes basic functionality and controllability associated with the Serialiazer-Deserializer (SerDes) block in PES24NT6AG2 ports.

**Chapter 9, "Power Management,"** describes the power management capability structure located in the configuration space of each PCI-to-PCI bridge in the PES24NT6AG2.

**Chapter 10**, "**Transparent Operation**," describes the device-specific architectural features for the transparent switch associated with each PES24NT6AG2 partition (i.e., the PCI-to-PCI bridge functions and their interaction in the switch).

**Chapter 11**, "Hot-Plug and Hot-Swap," describes the behavior of the hot-plug and hot-swap features in the PES24NT6AG2.

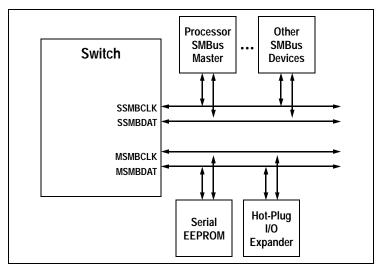

**Chapter 12, "SMBus Interfaces,"** describes the operation of the 2 SMBus interfaces on the PES24NT6AG2.

**Chapter 13**, "General Purpose I/O," describes how the 9 General Purpose I/O (GPIO) pins may be individually configured as general purpose inputs, general purpose outputs, or alternate functions.

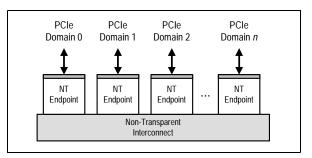

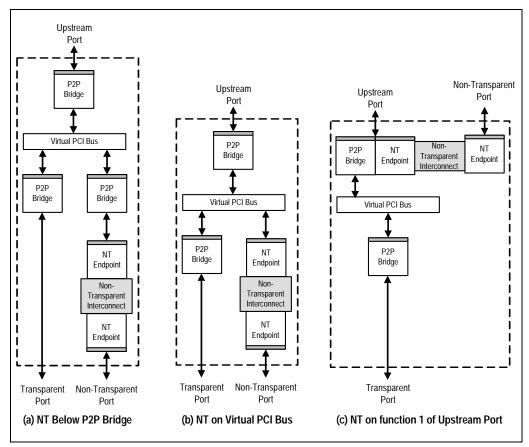

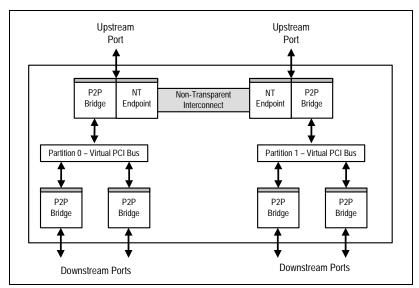

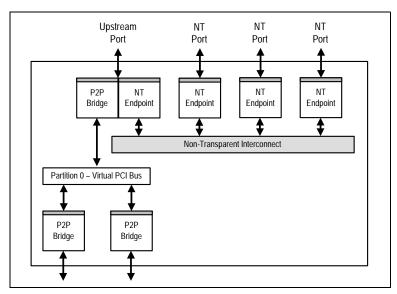

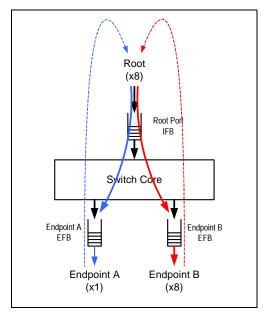

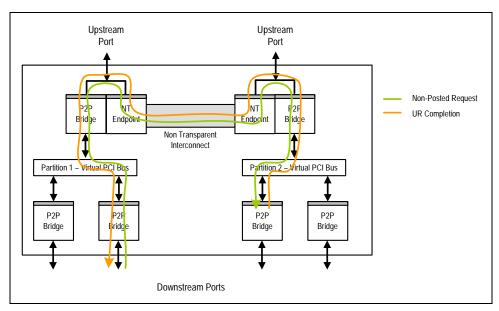

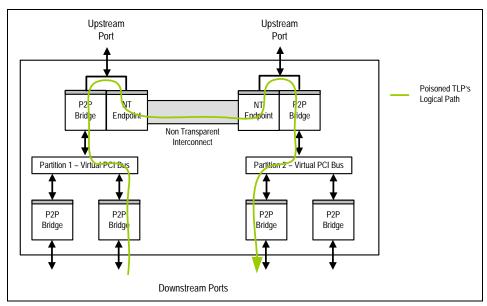

**Chapter 14, "Non-Transparent Operation,"** describes how a non-transparent bridge in the PES24NT6AG2 allows two roots or PCI Express trees (i.e., hierarchies) to be interconnected with one or more shared address windows between them.

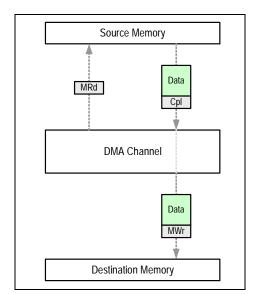

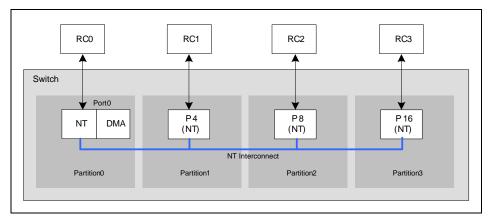

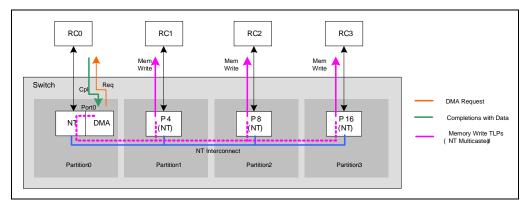

**Chapter 15, "DMA Controller,"** describes how the PES24NT6AG2 supports two direct memory access controller (DMA) functions.

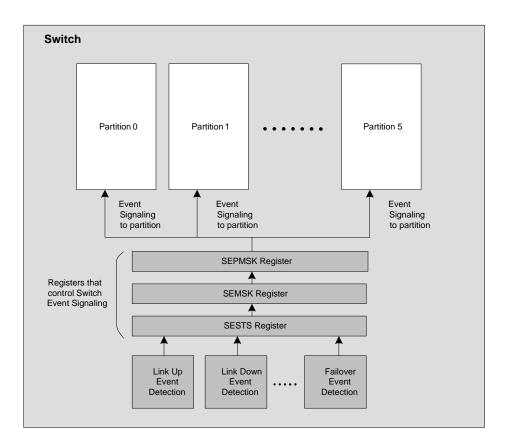

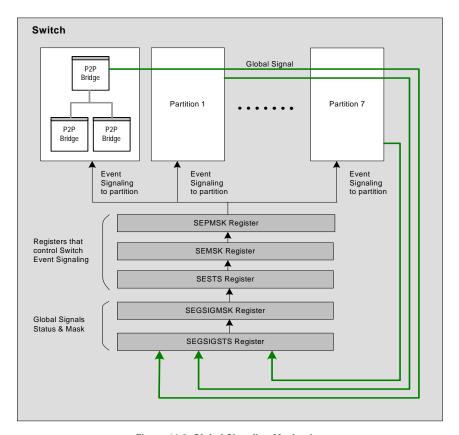

**Chapter 16, "Switch Events,"** describes mechanisms provided by the PES24NT6AG2 to facilitate communication between roots associated with different partitions as well as for communication between these roots and a management agent.

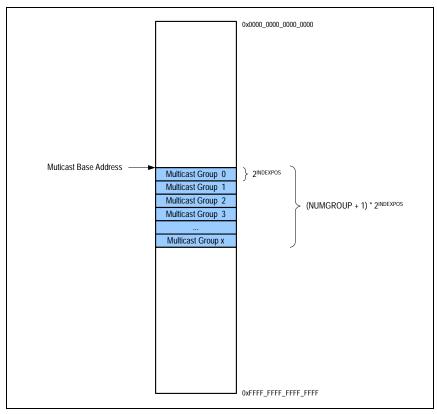

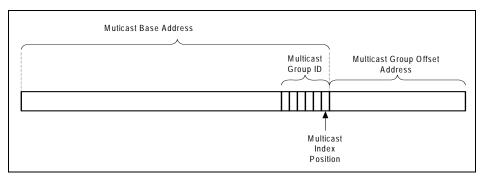

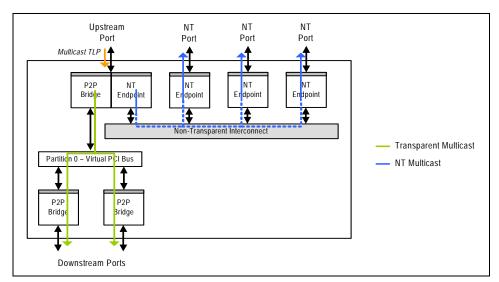

**Chapter 17**, "Multicast," describes how the multicast capability enables a single TLP to be forwarded to multiple destinations.

**Chapter 18**, "Temperature Sensor," provides a description of the on-chip temperature sensor with three programmable temperature thresholds and a temperature history capability.

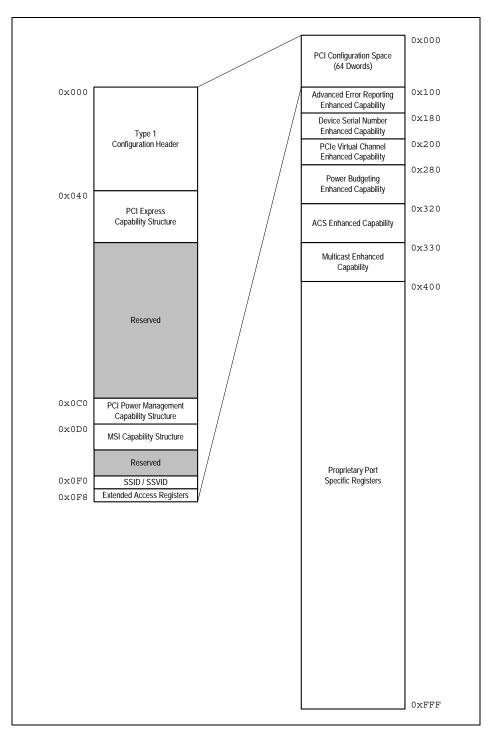

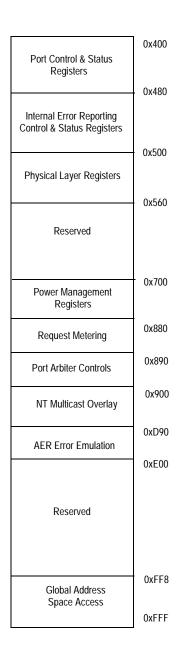

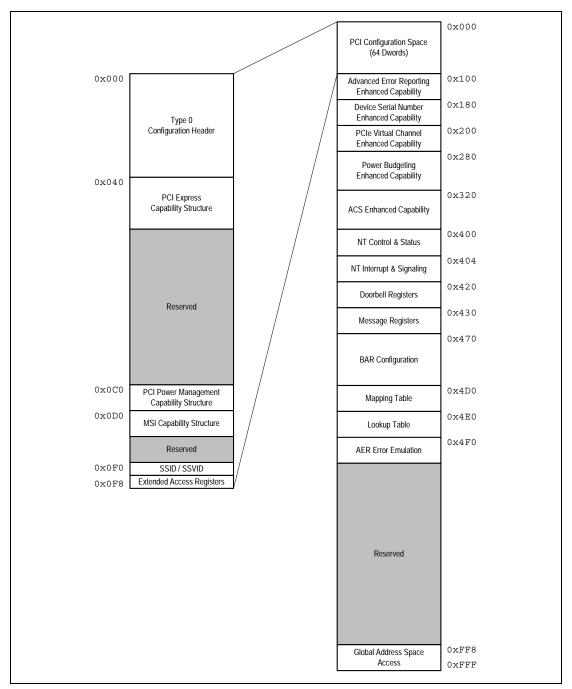

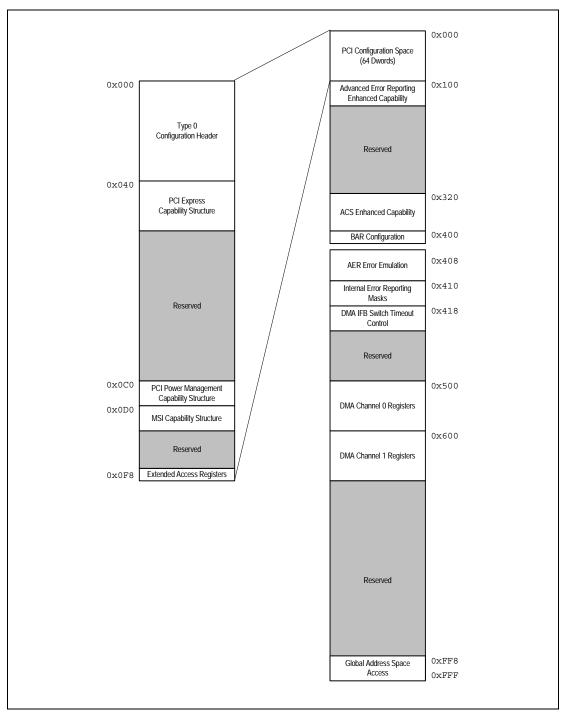

**Chapter 19**, "Register Organization," describes the organization of all the software visible registers in the PES24NT6AG2 and provides the address space for those registers.

Chapter 20, "PCI to PCI Bridge and Proprietary Port Specific Registers," lists the Type 1 configuration header registers in the PES24NT6AG2 and provides a description of each bit in those registers.

**Chapter 21**, "**Proprietary Registers**," lists the proprietary registers in the PES24NT6AG2 and provides a description of each bit in those registers.

**Chapter 22**, "NT Endpoint Registers," lists the NT Endpoint registers in the PES24NT6AG2 and provides a description of each bit in those registers.

**Chapter 23**, "DMA Registers," lists the DMA registers in the PES24NT6AG2 and provides a description of each bit in those registers.

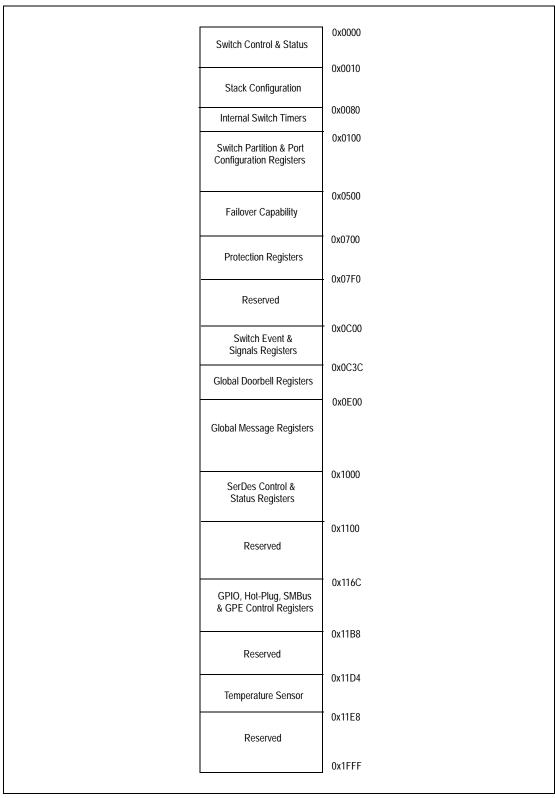

**Chapter 24, "Switch Control Registers,"** lists the switch control and status registers in the PES24NT6AG2 and provides a description of each bit in those registers.

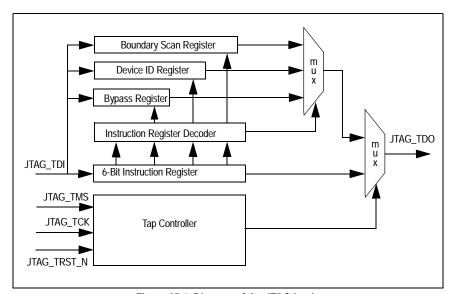

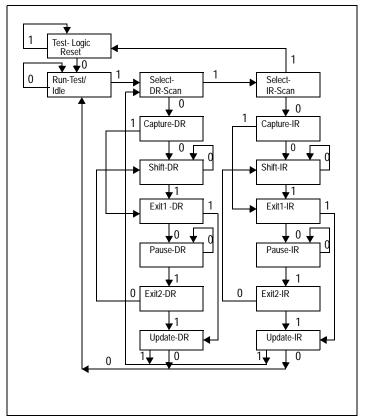

**Chapter 25**, "JTAG Boundary Scan," discusses an enhanced JTAG interface, including a system logic TAP controller, signal definitions, a test data register, an instruction register, and usage considerations.

**Chapter 26**, "Usage Models," describes possible configurations of the PES24NT6AG2 switch and presents some important system usage models.

# **Signal Nomenclature**

To avoid confusion when dealing with a mixture of "active-low" and "active-high" signals, the terms assertion and negation are used. The term assert or assertion is used to indicate that a signal is active or true, independent of whether that level is represented by a high or low voltage. The term negate or negation is used to indicate that a signal is inactive or false.

To define the active polarity of a signal, a suffix will be used. Signals ending with an 'N' should be interpreted as being active, or asserted, when at a logic zero (low) level. All other signals (including clocks, buses and select lines) will be interpreted as being active, or asserted when at a logic one (high) level.

To define buses, the most significant bit (MSB) will be on the left and least significant bit (LSB) will be on the right. No leading zeros will be included.

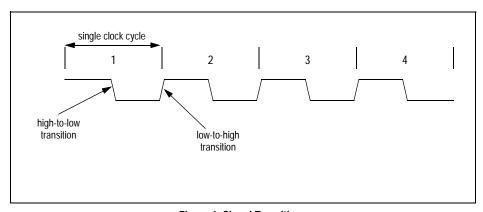

Throughout this manual, when describing signal transitions, the following terminology is used. Rising edge indicates a low-to-high (0 to 1) transition. Falling edge indicates a high-to-low (1 to 0) transition. These terms are illustrated in Figure 1.

Figure 1 Signal Transitions

# **Numeric Representations**

To represent numerical values, either decimal, binary, or hexadecimal formats will be used. The binary format is as follows: 0bDDD, where "D" represents either 0 or 1; the hexadecimal format is as follows: 0xDD, where "D" represents the hexadecimal digit(s); otherwise, it is decimal.

The compressed notation ABC[x|y|z]D refers to ABCxD, ABCyD, and ABCzD.

The compressed notation ABC[y:x]D refers to ABCxD, ABC(x+1)D, ABC(x+2)D,... ABCyD.

# **Data Units**

The following data unit terminology is used in this document.

| Term               | Words | Bytes | Bits |

|--------------------|-------|-------|------|

| Byte               | 1/2   | 1     | 8    |

| Word               | 1     | 2     | 16   |

| Doubleword (DWord) | 2     | 4     | 32   |

| Quadword (QWord)   | 4     | 8     | 64   |

Table 1 Data Unit Terminology

In quadwords, bit 63 is always the most significant bit and bit 0 is the least significant bit. In double-words, bit 31 is always the most significant bit and bit 0 is the least significant bit. In words, bit 15 is always the most significant bit and bit 0 is the least significant bit. In bytes, bit 7 is always the most significant bit and bit 0 is the least significant bit.

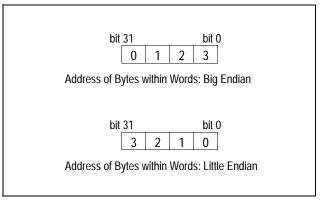

The ordering of bytes within words is referred to as either "big endian" or "little endian." Big endian systems label byte zero as the most significant (leftmost) byte of a word. Little endian systems label byte zero as the least significant (rightmost) byte of a word. See Figure 2.

Figure 2 Example of Byte Ordering for "Big Endian" or "Little Endian" System Definition

# **Register Terminology**

Software in the context of this register terminology refers to modifications made by PCI Express root configuration writes, writes to registers made through the slave SMBus interface, or serial EEPROM register initialization. See Table 2.

| Туре                 | Abbreviation | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware Initialized | HWINIT       | Register bits are initialized by firmware or hardware mechanisms such as pin strapping or serial EEPROM. (System firmware hardware initialization is only allowed for system integrated devices.) Bits are read-only after initialization and can only be reset (for write-once by firmware) with reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Read Only and Clear  | RC           | Software can read the register/bits with this attribute. Reading the value will automatically cause the register/bit to be reset to zero. Writing to a RC location has no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Read Clear and Write | RCW          | Software can read the register/bits with this attribute. Reading the value will automatically cause the register/bits to be reset to zero. Writes cause the register/bits to be modified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Reserved             | Reserved     | The value read from a reserved register/bit is undefined. Thus, software must deal correctly with fields that are reserved. On reads, software must use appropriate masks to extract the defined bits and not rely on reserved bits being any particular value. On writes, software must ensure that the values of reserved bit positions are preserved. That is, the values of reserved bit positions must first be read, merged with the new values for other bit positions and then written back.  In addition to reserved registers, some valid register fields have encodings marked as reserved. Such register fields must never be written with a value corresponding to an encoding marked as reserved. Violating this rule produces undefined operation in the device. |

| Read Only            | RO           | Software can only read registers/bits with this attribute. Contents are hardwired to a constant value or are status bits that may be set and cleared by hardware. Writing to a RO location has no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 2 Register Terminology (Part 1 of 2)

| Туре                            | Abbreviation | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read and Write                  | RW           | Software can both read and write bits with this attribute.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Read and Write Clear            | RW1C         | Software can read and write to registers/bits with this attribute. However, writing a value of zero to a bit with this attribute has no effect. A RW1C bit can only be set to a value of 1 by a hardware event. To clear a RW1C bit (i.e., change its value to zero) a value of one must be written to the location. An RW1C bit is never cleared by hardware.                                                                                                                                                                                                                                                                                                                      |

| Read and Write when<br>Unlocked |              | Software can read the register/bits with this attribute. Writing to register/bits with this attribute will only cause the value to be modified if the REGUNLOCK bit in the SWCTL register is set. When the REGUNLOCK bit is cleared, writes are ignored and the register/bits are effectively read-only.                                                                                                                                                                                                                                                                                                                                                                            |

| Sticky                          | Sticky       | Register/bits with this designation take on their initial value as a result of a switch fundamental reset or partition fundamental reset. Other resets have no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Switch Sticky                   | SWSticky     | Register/bits with this designation take on their default value as a result of a switch fundamental reset. Other resets have no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Modified Switch Sticky          | MSWSticky    | A MSWSticky register is a Switch Sticky register that in addition to taking on its default value as a result of a switch fundamental reset, it takes on its default value when the event(s) defined in the register description occur, unless the register has been written-to by software/firmware before the occurrence of the event. If the value of an MSWSticky register has been written by software/firmware, it preserves the value across all events until written again or until a switch fundamental reset is applied to the device. After a switch fundamental reset, the MSWSticky register will return to taking on the value as defined in the register description. |

Table 2 Register Terminology (Part 2 of 2)

# Use of Hypertext

In Chapter 19, Tables 19.2, 19.5, 19.6, 19.10, and 19.11 contain register names and page numbers highlighted in blue under the Register Definition column. In pdf files, users can jump from this source table directly to the registers by clicking on the register name in the source table. Each register name in the table is linked directly to the appropriate register in Chapters 20 through 24. To return to the source table after having jumped to the register section, click on the same register name (in blue) in the register section.

# **Reference Documents**

PCI Express Base Specification Revision 2.1., March 4, 2009, PCI-SIG.

PCI Local Bus Specification Revision 3.0., February 3, 2004, PCI-SIG.

PCI-to-PCI Bridge Architecture Specification Revision 1.2., June 9, 2003, PCI-SIG.

Address Translation Services Specification, March 8, 2007, PCI-SIG.

PCI Bus Power Management Interface Specification, Revision 1.2., March 3, 2004, PCI-SIG

SMBus Specification, Version 2.0, August 3, 2000, SBS Implementers Forum.

# **Revision History**

January 14, 2010: Initial publication of preliminary user manual.

**March 8, 2010**: Removed references to OUTDBELLCLR and OUTSBELLDBELLCLR registers in Chapter 14, Non-Transparent Switch Operation.

March 17, 2010: In Chapter 8, updated Tables 8.5, 8.6, 8.7, 8.10, and 8.11. In Chapter 13, deleted reference to multiple GPIOAFSEL registers; there is only one register. In Chapter 24, deleted "other" from ECRC Error name for bit 31 in the DMAC[1:0]ERRSTS register.

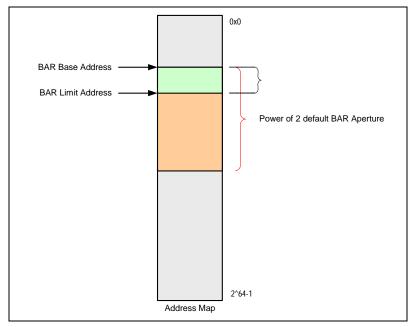

May 10, 2010: In Chapter 21, PCI Bridge Registers, the ACSCAP register offset address was corrected to 0x324. In Chapter 23, NT Endpoint Register, revised the Description for MODE field in BARSETUP0 register and LADDR field in BARLIMIT0 register.

May 21, 2010: In Chapter 23, NT Endpoint Registers, revised Description for INDEX field in LUTOFFSET register to read that if BAR4 is selected, the INDEX field must only be set to values 0 to 11 (instead of 12 to 23).

**June 21, 2010**: In Chapter 23, NT Endpoint Registers, revised Bit Field column in NTMTBLDATA register.

**June 30, 2010**: Removed several references to Port 16 and P16linkupn/activen except in Chapter 27 which refers to other IDT switch devices.

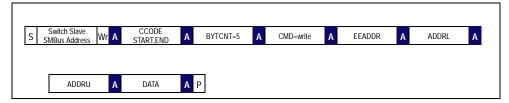

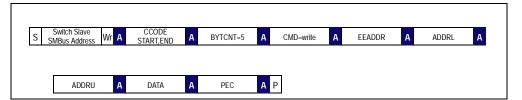

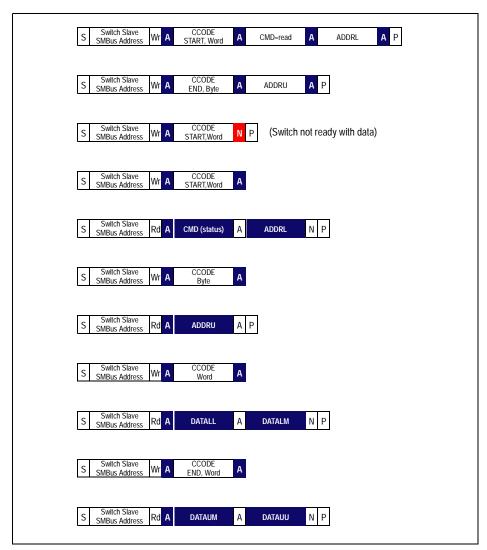

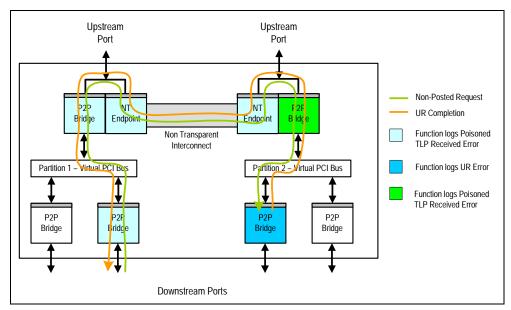

August 27, 2010: In Chapter 4, revised text in sections Internal Errors and Reporting of Port AER Errors as Internal Errors and updated Figures 4.7 and 4.8. In Chapter 5, revised text in Reset Mode Change Behavior. In Chapter 7, revised text in Link Width Negotiation in the Presence of Bad Lanes section and Crosslink section. In Chapter 11, corrected reference to DLLLASC in Hot Plug Events section. In Chapter 12, revised description for BYTECNT in Tables 12.19 and 12.21. In Chapter 14, added Note at end of section NT Mapping Table. In Chapter 15, deleted section DMA Channel Errors and revised text in Descriptor Prefetching, ECRC Errors, and Completion Timeout sections. In Chapter 16, revised text in section Port AER Errors. In Chapter 17, changed reference from NTMTC to NTMCC in NT Multicast TLP Routing section.

In Chapter 21, made the following changes: revised description for MAXLNKSPD bit in PCI Express Link Capabilities register (also applies to same bit in same register in Chapters 23 and 24), revised description for bits in PCI Express Slot Control register.

In Chapter 22, made the following changes: added text under section Physical Layer Control and Status Registers, revised description for bits in PCI Express Slot Control Initial Value register, deleted Port AER Status register, revised Port AER Mask register, added bit 10 to bit 9 as Reserved and revised description for ILSCC bit in Phy Link Configuration 0 register.

In Chapter 23, made the following changes: revised PCI Express Device Capabilities 2 and PCI Express Device Control 2 registers, revised Description for REG and EREG bits in ECFGADDR register, added bits 31:16 row in AER Correctable Error Status register, added text in Description of NXTPTR in SNUMCAP register, added text in Description of NXTPTR in PCIEVCECAP register, revised information for fields PARBC and PATBLOFF in VCR0CAP register, revised information for fields LPAT and PARBSEL in VCR0CTL register, revised Description for PATS in VCR0STS register, added text in Description of NXTPTR in MCCAPH register, changed default value for bits 30:29 from 0x1 to 0x3 in NTIERRORMSK0 register, changed bit 6 in the NTINTMSK register to Reserved, revised description for bits SIZE and MODE in Bar 0 Setup register, revised information in LADDR field in BARLIMIT0 register, revised text under register title for BAR 1 Limit Address and changed Default Value for Reserved and LADDR and Description for LADDR, revised text under register title for BARLIMIT3 and changed Default Value for Reserved and LADDR and Description for LADDR, revised text under register title for BARLIMIT5 and changed Default Value and Description for LADDR, revised description for INDEX in LUTOFFSET register.

In Chapter 24, made the following changes: revised bits 4 to 21 in PCIEDCAP2 register, revised bits 4 to 15 in PCIEDCTL2 register, revised bits 21 and 22 and added bits 24 and 25 in AERUES register, revised bit 22 and added bits 24 and 25 in AERUESV register, changed Default Value for CIE bit in AERCES register, changed Type and Default Value for

ECRCGC and ECRCCC bits in AERCTL register, changed bit 24 (HEC) to reserved in DMAIERRORMSK1 register, de-featured bits 0 and 6 through 9 in the DMAC[1:0]ERRSTS register, de-featured bits 0 and 6 through 7 and changed name of bit 31 to ECRCE in DMAC[1:0]ERRMSK register.

In Chapter 25, made the following changes: revised SESTS register, revised description for COUNT field in FCAP[3:0]TIMER register, added bits 20 and 21 and revised default value and/or description for bits 22 to 25 and changed name/value/description of bit 29 in SMBUSSTS register, removed default value for TEMP field in TMPSTS register.

**September 27, 2010**: In Chapter 22, changed bit 16 in the IERRORSTS0 register from ULD to Reserved.

**October 22, 2010**: In Chapter 15, added footnote to Table 15.7. In Chapter 25, re-arranged bits 24:28 in TMPCTL register.

December 21, 2010: In Chapter 2, revised header in Table 2.5 to read "Initial Port Clock Mode." In Chapter 5, added new footnote #1 in section Port Operating Mode Change. In Chapter 15, deleted reference to DATCT bit in Completion Timeout section. In Chapter 23, added text to SUBVID and SUBID registers. In Chapter 24, changed bit 20 (DATCT bit) in the DMAC[1:0]ERRSTS and DMAC[1:0]ERRMSK registers to Reserved and added text to SUBVID and SUBID registers. In Chapter 26, deleted PERSTN, GLK1, and SMODE from Table 26.1.

**March 11, 2011**: In Chapter 26, revised Usage Considerations section to remove reference to JTAG\_TCK being driven to a known value.

March 25, 2011: In Chapter 22, added PHYLSTATEO register with FLRET bit description.

May 20, 2011: In Chapter 1, added ZC silicon to Table 1.2.

**June 21, 2011**: In Chapter 5, section Reset Mode Change Behavior, changed fourth bullet to read "The port remains in a Reset state for at least 250 µs."

June 24, 2011: In Chapter 25, added bit BDISCARD to the Switch Control register.

July 15, 2011: In Chapter 1, revised section Switch Events and removed "and Signals" from the section title. In Chapter 5, revised the following sections: Downstream Switch Port, Port Operating Mode Change Latency, and System Notification of Partition Reconfiguration. In Chapter 8, revised section Programmable De-emphasis Adjustment. In Chapter 16, removed "and Signals" from title and revised section Global Signals and deleted Signals section. In Chapter 21, MCBLKALLH register, changed lower 32 to upper 32 in description of MCBLKALL bit. In Chapters 22 and 23, deleted references to SSIGNAL field. In Chapter 25, added section Internal Switch Timers with 4 new registers and deleted SSIGNAL register. Updated Figure 20.5 and Table 20.11, Switch Configuration and Status, in Chapter 20 to account for new registers.

July 27, 2011: In Chapter 22, added bits 7:0 (RCVD\_OVRD) in SERDESCFG register.

August 23, 2011: In Chapter 24, DMACxCFG register, changed 0x2 in DPREFETCH field to Reserved.

**September 12, 2011**: In Chapter 8, added additional reference in last paragraph of section Driver Voltage Level and Amplitude Boost.

October 24, 2011: In Chapter 22, added Port Control Register. In Chapter 20, added reference to Port Control register in Table 20.5.

**November 7, 2011**: In Chapter 2, section Local Port Clocked Mode, added recommendation to tie unused port clock pins to ground.

December 4, 2011: In Chapter 25, revised Description for AFSEL0 field in the GPIOAFSEL register.

January 11, 2012: Removed Hardware Error Containment chapter. Deleted references to SWFRST bit.

February 8, 2012: In Chapter 12, added footnote for RERR and WERR bits in Table 12.15.

February 23, 2012: Added paragraph after Table 12.14 to explain use of DWord addresses.

**March 14, 2012**: In the Overview section of Chapter 2, changed "single" to "two" differential global reference clock pairs.

# **IDT**

# **Notes**

May 1, 2012: In Chapter 2, Clocking, made text changes to state that unused port clock pins should be connected to Vss on the board. In Chapter 12, SMBus Interfaces, added new section Setting Up I2C Commands for Block Transactions.

**June 27, 2012**: In Chapter 12, changed BYTCNT=7 to BYTCNT=4 in Figure 12.14. In Chapter 24, changed type and default values for bits 16 and 20 in Switch Control register.

January 30, 2013: In Figure 12.12, changed No-ack to Ack between DATALM and DATAUM.

# **Table of Contents**

| Overview         1           Content Summary         1           Signal Nomenclature         2           Numeric Representations         3           Data Units         3           Register Terminology         4           Use of Hypertext         5           Reference Documents         5           Revision History         5           PES24NT6AG2 Device Overview           Overview           1-1           System Identification         1-1           Vendor ID         1-1           Device ID         1-1           Revision IDD         1-1           JTAG ID         1-2           SSID/SSVID         1-2           SSID/SSVID         1-2           Architectural Overview         1-2           Port Operating Modes         1-3           Switch Partitioning         1-6           Non-Transparent Operation         1-7           Dynamic Reconfiguration and Failover         1-15           Switch Events         1-16           Multicasting and Non-Transparent Multicasting         1-17           Clocking         2-2           Global Clocked Mode         2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | About This Manual                                   |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|

| Content Summary   1   Signal Nomenclature   2   Numeric Representations   3   3   Data Units   3   Register Terminology   4   4   4   5   5   Reference Documents   5   Reference Documents   5   Revision History   5   5   PES24NT6AG2 Device Overview   1-1   System Identification   1-1   Vendor ID   1-1   Device ID   1-1   Device ID   1-1   TAG ID | Overview                                            | 1   |

| Signal Nomenclature         2           Numeric Representations         3           Data Units         3           Register Terminology         4           Use of Hypertext         5           Reference Documents         5           Reference Documents         5           Revision History         5           PES24NT6AG2 Device Overview           Overview           1-1           System Identification         1-1           1-1           Vendor ID         1-1           1-1           Revision ID         1-1           1-1           Revision ID         1-1           1-1           SID/SSVID         1-2           Device Serial Number Enhanced Capability         1-2           2           Port Operating Modes         1-3           Swilch Partitioning         1-4           Architectural Overview         1-3           Swilch Events         1-16           Multicasting and Non-Transparent Multicasting         1-17 <t< td=""><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |     |

| Numeric Representations         3           Data Units         3           Register Terminology         4           Use of Hypertext         5           Reference Documents         5           Revision History         5           PES24NT6AG2 Device Overview           Overview           1-1           System Identification         1-1           Vendor ID         1-1           Device ID         1-1           Revision ID         1-1           JTAG ID         1-1           JTAG ID         1-2           SSID/SSVID         1-2           Device Serial Number Enhanced Capability         1-2           Architectural Overview         1-2           Port Operating Modes         1-3           Switch Partitioning         1-6           Non-Transparent Operation         1-7           DMA Operation         1-17           Dynamic Reconfiguration and Failover         1-16           Multicasting and Non-Transparent Multicasting         1-17           Clocking           Overview         2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | · · · · · · · · · · · · · · · · · · ·               |     |

| Data Units         3           Register Terminology         4           Use of Hypertext         5           Reference Documents         5           Revision History         5           PES24NT6AG2 Device Overview           Overview           Overview         1-1           System Identification         1-1           Vendor ID         1-1           Device ID         1-1           Revision ID         1-1           JTAG ID         1-2           SSID/SSVID         1-2           Device Serial Number Enhanced Capability         1-2           Architectural Overview         1-2           Port Operating Modes         1-3           Switch Partitioning         1-6           Non-Transparent Operation         1-1           DYnamic Reconfiguration and Failover         1-15           Switch Events         1-16           Multicasting and Non-Transparent Multicasting         1-17           Clocking         2-1           Overview         2-2           Global Clocked Mode         2-2           Local Port Clocking Modes         2-2           Global Clocked Mode         2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                                   |     |

| Register Terminology         4           Use of Hypertext         5           Reference Documents         5           Revision History         5           PES24NT6AG2 Device Overview           Overview           1-1           System Identification         1-1           Vendor ID         1-1           Device ID         1-1           Revision ID         1-1           JTAG ID         1-2           SSID/SSVID         1-2           Device Serial Number Enhanced Capability         1-2           Device Serial Number Enhanced Capability         1-2           Port Operating Modes         1-2           Port Operating Modes         1-2           Port Operating Modes         1-3           Switch Partitioning         1-6           Non-Transparent Operation         1-12           Dynamic Reconfiguration and Failover         1-13           Switch Events         1-16           Multicasting and Non-Transparent Multicasting         1-17           Clocking           Overv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <u>.</u>                                            |     |

| Use of Hypertext         5           Reference Documents         5           Revision History         5           PES24NT6AG2 Device Overview         1.1           Overview         1.1           System Identification         1.1           Vendor ID         1.1           Device ID         1.1           Revision ID         1.1           JTAG ID         1.2           SSID/SSVID         1.2           Device Serial Number Enhanced Capability         1.2           Architectural Overview         1.2           Port Operating Modes         1.3           Switch Partitioning         1.6           Non-Transparent Operation         1.7           DMA Operation         1.7           DMA Operation         1.7           Dynamic Reconfiguration and Failover         1.15           Switch Events         1.16           Multicasting and Non-Transparent Multicasting         1.17           Clocking           Overview         2.1           Port Clocking Modes         2.2           Global Clocked Mode         2.2           Local Port Clocked Mode         2.2           System Clocking Configuration Socional System Configuration Vec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     |     |

| Reference Documents         5           Revision History         5           PES24NT6AG2 Device Overview           Overview         1-1           System Identification         1-1           Vendor ID         1-1           Device ID         1-1           Revision ID         1-1           JTAG ID         1-2           SSID/SSVID         1-2           Device Serial Number Enhanced Capability         1-2           Architectural Overview         1-2           Port Operating Modes         1-3           Switch Partitioning         1-6           Non-Transparent Operation         1-7           DMA Operation         1-7           DMA Operation         1-12           Dynamic Reconfiguration and Failover         1-15           Switch Events         1-16           Multicasting and Non-Transparent Multicasting         1-17           Clocking           Overview         2-2           Global Clocked Mode         2-2           Local Port Clocked Mode         2-2           Local Port Clocking Mode Selection         2-3           System Clocking Configurations         2-7           Reset and Initia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                                   |     |

| Revision History         5           PES24NT6AG2 Device Overview         1-1           Overview         1-1           System Identification         1-1           Vendor ID         1-1           Device ID         1-1           Revision ID         1-1           JTAG ID         1-2           SSID/SSVID         1-2           Device Serial Number Enhanced Capability         1-2           Architectural Overview         1-2           Port Operating Modes         1-3           Switch Parlitioning         1-6           Non-Transparent Operation         1-7           DMA Operation         1-15           Dynamic Reconfiguration and Failover         1-15           Switch Events         1-16           Multicasting and Non-Transparent Multicasting         1-17           Clocking         0verview           Overview         2-2           Global Clocked Mode         2-2           Local Port Clocked Mode         2-2           Local Port Clocked Mode         2-3           System Clocking Configurations         2-5           System Clocking Configurations         2-7           Reset and Initialization         3-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     |     |

| PES24NT6AG2 Device Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |     |

| Overview         1-1           System Identification         1-1           Vendor ID         1-1           Device ID         1-1           Revision ID         1-1           JTAG ID         1-2           SSID/SSVID         1-2           Device Serial Number Enhanced Capability         1-2           Architectural Overview         1-2           Port Operating Modes         1-3           Switch Partitioning         1-6           Non-Transparent Operation         1-7           DMA Operation         1-12           Dynamic Reconfiguration and Failover         1-15           Switch Events         1-16           Multicasting and Non-Transparent Multicasting         1-17           Clocking         2-2           Global Clocked Mode         2-2           Local Port Clocking Modes         2-2           Global Clocked Mode         2-2           Local Port Clocked Mode         2-3           Support for Spread Spectrum Clocking (SSC)         2-4           Port Clocking Configurations         2-5           System Clocking Configurations         2-7           Reset and Initialization         3-1           Overview         3-2 <th>,</th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ,                                                   |     |

| System Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PES24NT6AG2 Device Overview                         |     |

| Vendor ID.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Overview                                            | 1-1 |

| Vendor ID.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |     |

| Device ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |     |

| Revision ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |     |

| JTAG ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |     |

| SSID/SSVID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |     |

| Device Serial Number Enhanced Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |     |

| Architectural Overview       1-2         Port Operating Modes       1-3         Switch Partitioning       1-6         Non-Transparent Operation       1-7         DMA Operation       1-17         Dynamic Reconfiguration and Failover       1-15         Switch Events       1-16         Multicasting and Non-Transparent Multicasting       1-17         Clocking         Overview       2-1         Port Clocking Modes       2-2         Global Clocked Mode       2-2         Local Port Clocked Mode       2-3         Support for Spread Spectrum Clocking (SSC)       2-4         Port Clocking Mode Selection       2-5         System Clocking Configurations       2-7         Reset and Initialization       3-1         Overview       3-2         Switch Fundamental Reset       3-2         Boot Configuration Vector       3-4         Stack Configuration Vector       3-4         Stack Configuration of a Stack       3-7         Dynamic Reconfiguration of a Stack via EEPROM / SMBus       3-7         Switch Modes       3-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |     |

| Port Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ·                                                   |     |

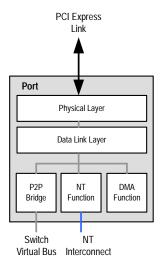

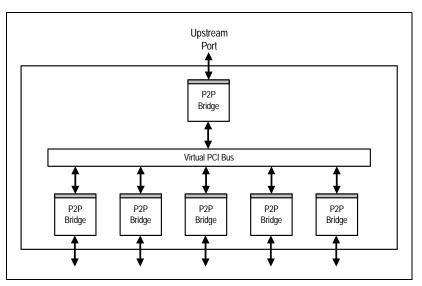

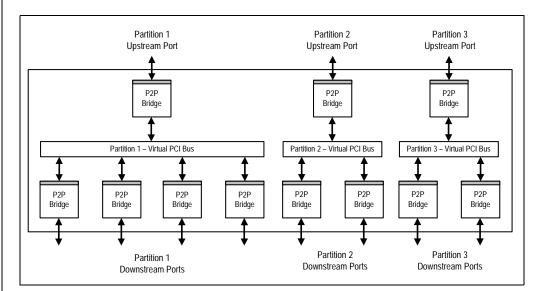

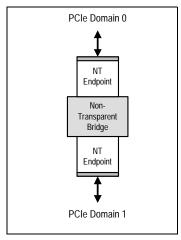

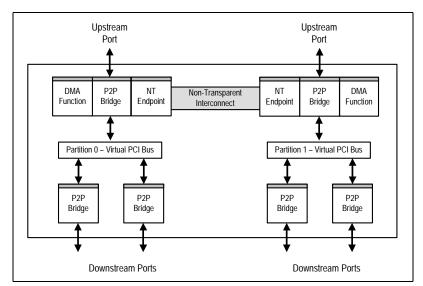

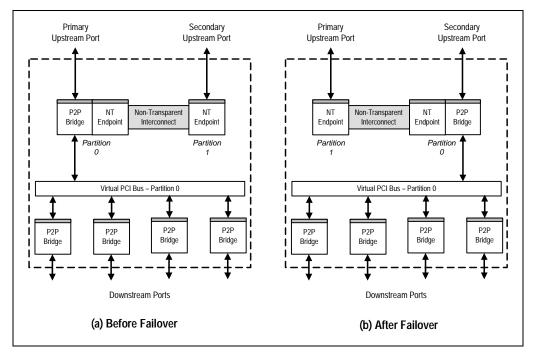

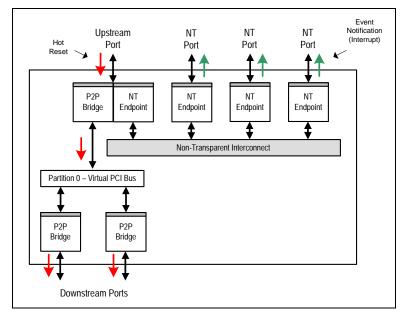

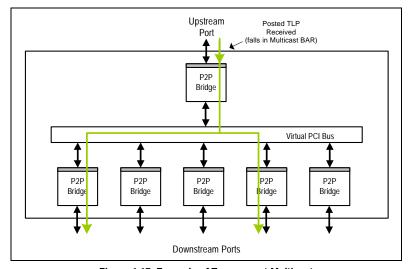

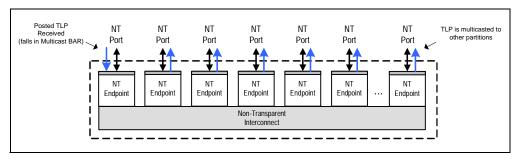

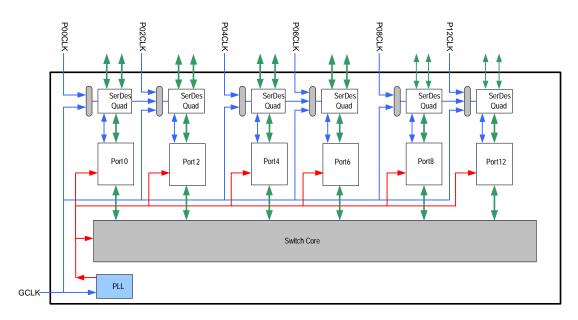

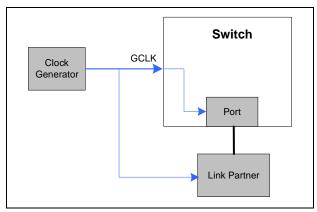

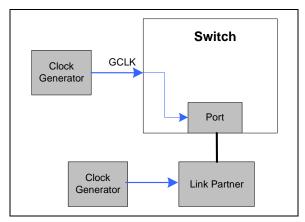

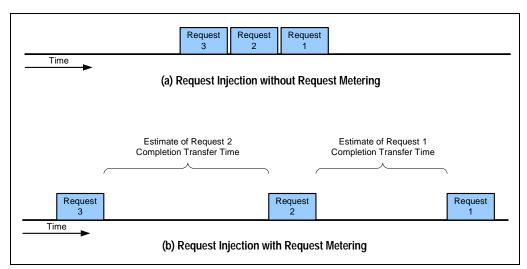

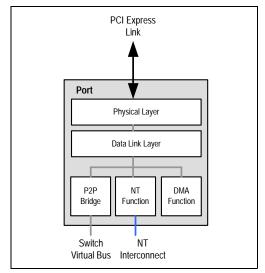

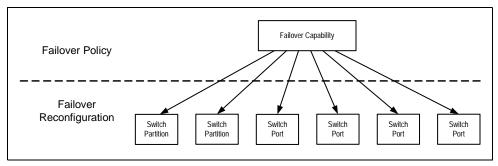

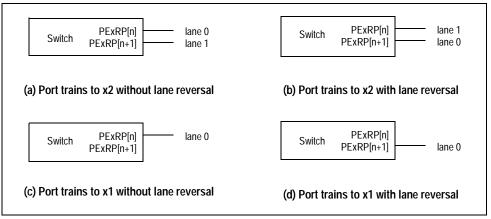

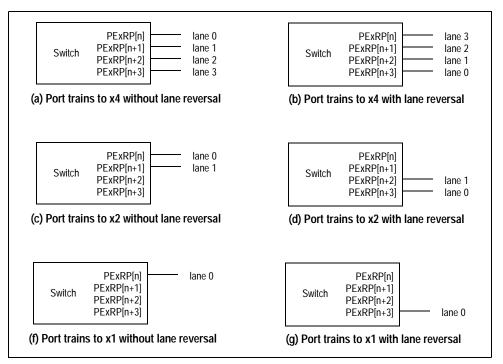

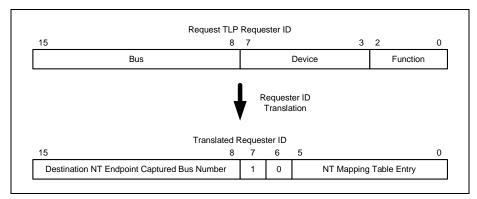

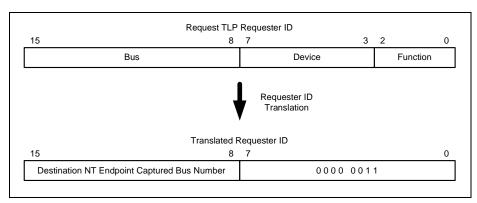

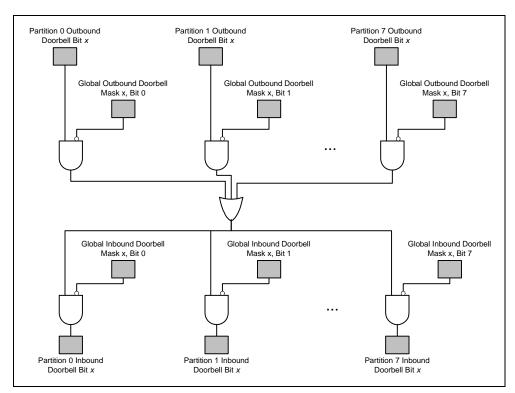

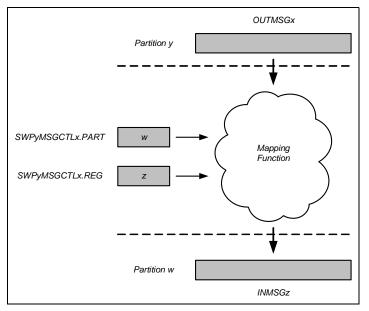

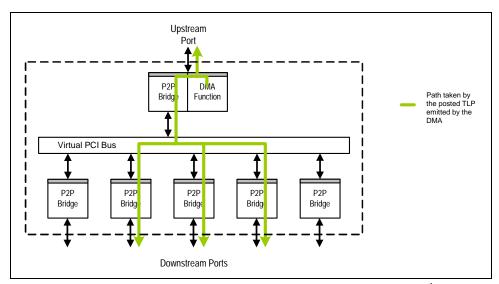

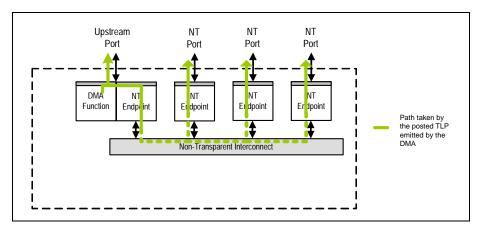

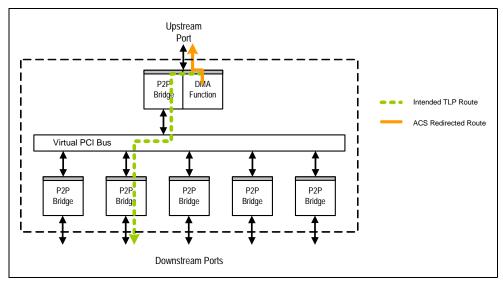

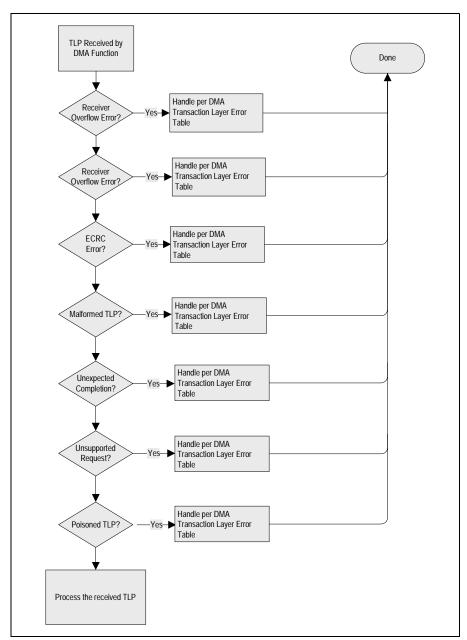

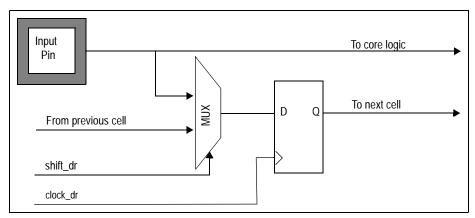

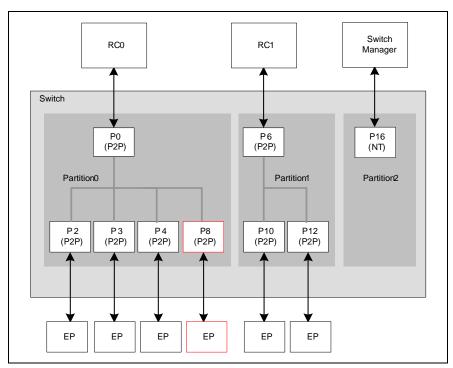

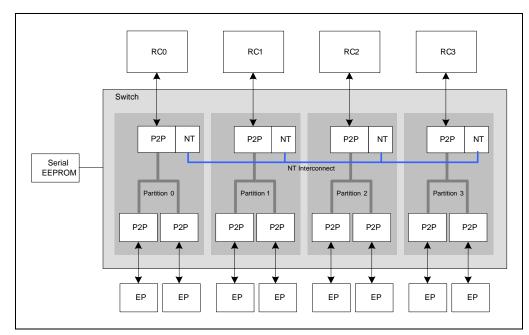

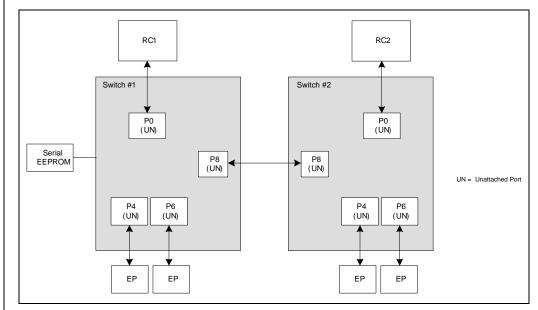

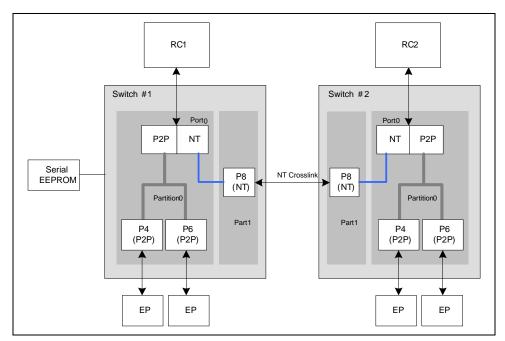

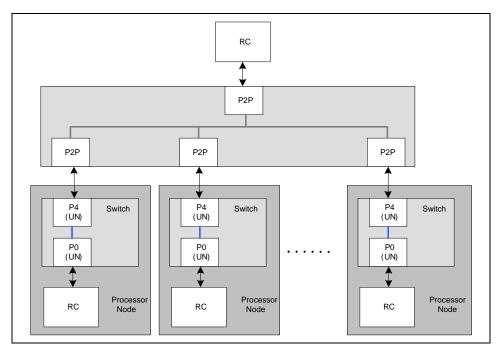

| Switch Partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |     |