# RENESAS

# IDT<sup>®</sup> Tsi382A PCIe<sup>®</sup>-to-PCI Bridge User Manual

April 17, 2014

© 2019 Renesas Electronics Corporation

#### GENERAL DISCLAIMER

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

#### CODE DISCLAIMER

Code examples provided by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of the code examples below is completely at your own risk. IDT MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND CONCERNING THE NONINFRINGEMENT, QUALITY, SAFETY OR SUITABILITY OF THE CODE, EITHER EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICU-LAR PURPOSE, OR NON-INFRINGEMENT. FURTHER, IDT MAKES NO REPRESENTATIONS OR WARRANTIES AS TO THE TRUTH, ACCURACY OR COMPLETENESS OF ANY STATEMENTS, INFORMATION OR MATERIALS CONCERNING CODE EXAMPLES CONTAINED IN ANY IDT PUBLICATION OR PUBLIC DISCLOSURE OR THAT IS CONTAINED ON ANY IDT INTERNET SITE. IN NO EVENT WILL IDT BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, INCIDENTAL, INDIRECT, PUNITIVE OR SPECIAL DAMAGES, HOWEVER THEY MAY ARISE, AND EVEN IF IDT HAS BEEN PREVIOUSLY ADVISED ABOUT THE POSSIBILITY OF SUCH DAMAGES. The code examples also may be subject to United States export control laws and may be subject to the export or import laws of other countries and it is your responsibility to comply with any applicable laws or regulations.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

IDT, the IDT logo, and Integrated Device Technology are trademarks or registered trademarks of Integrated Device Technology, Inc.

## Contents

| Ab | out tl            | his Document                            | 15 |

|----|-------------------|-----------------------------------------|----|

|    | Scop              | е                                       | 15 |

|    | ument Conventions |                                         |    |

|    | Revis             | sion History                            | 17 |

| 1. | Fur               | nctional Overview                       | 19 |

|    | 1.1               | Overview                                |    |

|    | 1.2               | Features                                |    |

|    |                   | 1.2.1 General Features.                 |    |

|    |                   | 1.2.2 PCIe Features                     |    |

|    |                   | 1.2.3 PCI Features                      |    |

|    | 1.3               | Device Architecture                     |    |

|    | 1.4               | Typical Applications                    |    |

| 2. | Sig               | nal Descriptions                        | 27 |

|    | 2.1               | Overview                                | 27 |

|    | 2.2               | PCIe Interface Signals                  | 28 |

|    | 2.3               | PCI Interface Signals                   | 29 |

|    | 2.4               | EEPROM Interface Signals                | 32 |

|    | 2.5               | GPIO Signals                            | 32 |

|    | 2.6               | JTAG Interface Signals                  | 32 |

|    | 2.7               | Power-up Signals                        | 34 |

|    | 2.8               | Power Supply Signals                    | 34 |

| 3. | Dat               | a Path                                  | 35 |

|    | 3.1               | Overview                                | 35 |

|    |                   | 3.1.1 Upstream Data Path                | 35 |

|    |                   | 3.1.2 Downstream Data Path              | 36 |

|    | 3.2               | Transaction Management                  | 37 |

|    |                   | 3.2.1 Upstream Transaction Management.  | 37 |

|    |                   | 3.2.2 Downstream Transaction Management | 38 |

|    | 3.3               | Buffer Structure                        | 38 |

|    |                   | 3.3.1 Upstream Non-posted Buffer        | 38 |

|    |                   | 3.3.2 Upstream Posted Buffer            | 39 |

|    |                   | 3.3.3 Downstream Non-posted Buffer      | 40 |

|    |                   | 3.3.4 Downstream Posted Buffer          | 40 |

|    | 3.4               | Flow Control                            | 40 |

|    | 3.5               | Prefetching Algorithm                   | 41 |

|    | 3.6               | Short Term Caching                      | 42 |

|    | 3.7               | Polarity Reversal                       | 42 |

| R | E | N | E | S | Δ | S |

|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |

| Λ |  |

|---|--|

| 4 |  |

| - |  |

| 4. | Add        | Iressin  | ıg                                             | 43 |

|----|------------|----------|------------------------------------------------|----|

|    | 4.1        | Overvie  | <br>2W                                         | 43 |

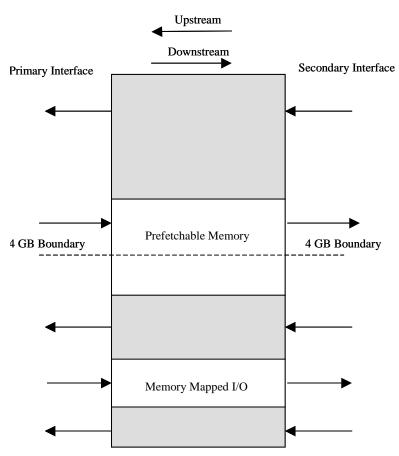

|    | 4.2        | Memor    | y-mapped I/O Space.                            | 43 |

|    | 4.3        | Prefetch | hable Space                                    | 45 |

|    | 4.4        |          | ree                                            |    |

|    | 4.5        | -        | ddressing                                      |    |

|    | 4.6        |          | ldressing                                      |    |

|    | 4.7        |          | Insparent Addressing                           |    |

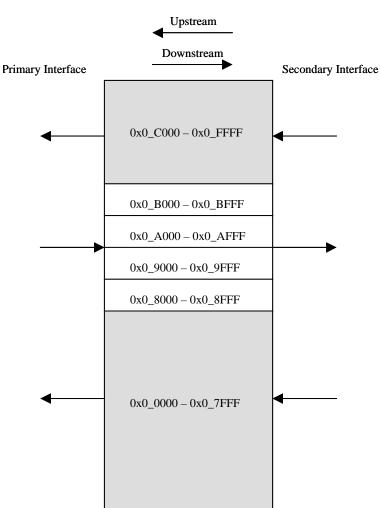

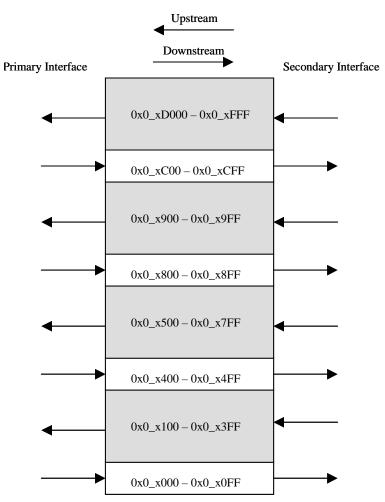

|    |            | 4.7.1    | PCIe to PCI Non-prefetchable Address Remapping |    |

|    |            | 4.7.2    | PCIe to PCI Prefetchable Address Remapping     |    |

|    |            | 4.7.3    | PCI to PCIe Address Remapping.                 |    |

|    | 4.8        |          | Mode                                           |    |

| 5. | Con        | figura   | tion Transactions                              | 55 |

| •  | 5.1        |          | 2W                                             |    |

|    | 5.1<br>5.2 |          | uration Transactions                           |    |

|    | 3.2        | 5.2.1    | Type 0 Configuration Transactions              |    |

|    |            |          |                                                |    |

|    |            | 5.2.2    | Type 1 Configuration Transactions              |    |

|    |            | 5.2.3    | Type 1 to Type 0 Conversion                    |    |

|    |            | 5.2.4    | Type 1 to Type 1 Forwarding                    |    |

|    | <b>5</b> 0 | 5.2.5    | Type 1 to Special Cycle Forwarding             |    |

|    | 5.3        |          | nhanced Configuration Mechanism                |    |

|    | 5.4        | Configu  | uration Retry Mechanisms                       | 59 |

| 6. | Bric       | lging .  |                                                | 61 |

|    | 6.1        | Overvie  | 2W                                             | 61 |

|    | 6.2        | Flow C   | ontrol Advertisements                          | 61 |

|    | 6.3        | Buffer S | Size and Management                            | 62 |

|    | 6.4        | Assignr  | nent of Requestor ID and Tag                   | 62 |

|    | 6.5        | -        | ding of PCIe to PCI                            |    |

|    |            | 6.5.1    | PCIe Memory Write Request.                     | 62 |

|    |            | 6.5.2    | PCIe Non-posted Requests                       |    |

|    | 6.6        | Forward  | ding of PCI to PCIe                            |    |

|    |            | 6.6.1    | PCI Memory Write Request.                      |    |

|    |            | 6.6.2    | PCI Non-posted Requests                        |    |

|    | 6.7        |          | ansaction Support                              |    |

|    | 6.8        |          | ransaction Support                             |    |

|    | 6.9        |          | e Transactions                                 |    |

|    | 015        | 6.9.1    | INTx Interrupt Signaling                       |    |

|    |            | 6.9.2    | Power Management                               |    |

|    |            | 6.9.3    | Locked Transaction                             |    |

|    |            | 6.9.4    | Slot Power Limit                               |    |

|    |            | 6.9.5    | Vendor-defined and Device ID                   |    |

|    | 6.10       |          | ction Ordering                                 |    |

|    | 6.11       |          | ve Access                                      |    |

|    | 0.11       | LACIUSI  | ve /100035                                     | 09 |

Contents

| 7.  | PCI  | I Arbitration                                    | 71  |

|-----|------|--------------------------------------------------|-----|

|     | 7.1  | Overview                                         |     |

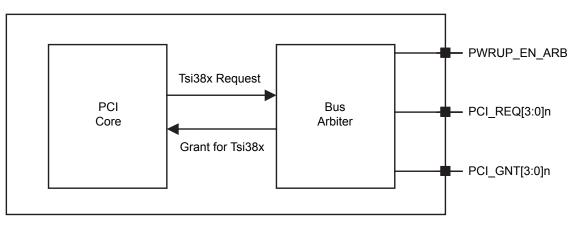

|     | 7.2  | Block Diagram                                    |     |

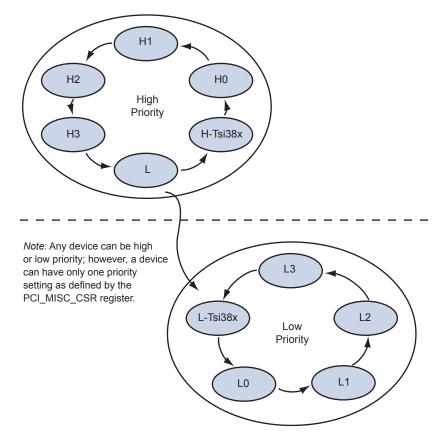

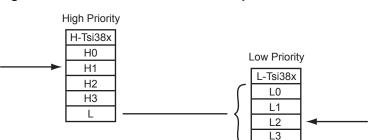

|     | 7.3  | PCI Arbitration Scheme                           |     |

| 0   | Into |                                                  | 75  |

| 8.  |      | errupt Handling                                  |     |

|     | 8.1  | Overview                                         |     |

|     | 8.2  | Interrupt Sources                                |     |

|     | 8.3  | Interrupt Routing                                |     |

|     | 8.4  | MSI Generation using GPIOs and Interrupts        |     |

| 9.  | Erro | or Handling                                      | 77  |

|     | 9.1  | Overview                                         |     |

|     | 9.2  | PCIe as Originating Interface                    |     |

|     |      | 9.2.1 Received Poisoned TLPs                     | 81  |

|     |      | 9.2.2 Received ECRC Errors                       |     |

|     |      | 9.2.3 PCI Uncorrectable Data Errors              |     |

|     |      | 9.2.4 PCI Uncorrectable Address/Attribute Errors | 84  |

|     |      | 9.2.5 Received Master-Abort on PCI Interface     | 85  |

|     |      | 9.2.6 Received Target-Abort On PCI Interface     |     |

|     | 9.3  | PCI as Originating Interface.                    | 87  |

|     |      | 9.3.1 Received PCI Errors                        |     |

|     |      | 9.3.2 Unsupported Request Completion Status.     | 91  |

|     |      | 9.3.3 Completer Abort Completion Status          | 91  |

|     | 9.4  | Timeout Errors                                   |     |

|     |      | 9.4.1 PCIe Completion Timeout Errors             | 92  |

|     |      | 9.4.2 PCI Delayed Transaction Timeout Errors     | 92  |

|     | 9.5  | Other Errors                                     | 92  |

|     | 9.6  | Error Handling Tables                            |     |

| 10. | Res  | set and Clocking                                 |     |

|     | 10.1 |                                                  |     |

|     |      | 10.1.1 PCIe Link Reset                           | 100 |

|     |      | 10.1.2 PCI Bus Reset                             |     |

|     | 10.2 |                                                  |     |

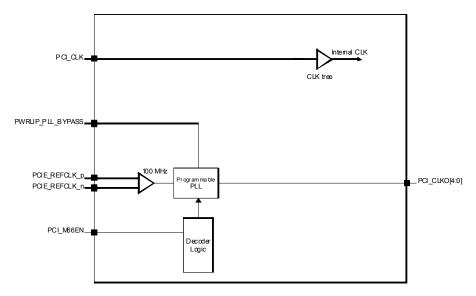

|     |      | 10.2.1 PCIe Clocking                             |     |

|     |      | 10.2.2 PCI Clocking                              |     |

|     | _    | -                                                |     |

| 11. |      | wer Management                                   |     |

|     | 11.1 |                                                  |     |

|     |      | 11.1.1 Features                                  |     |

|     |      | 11.1.2 Unsupported Features.                     |     |

|     | 11.2 |                                                  |     |

|     | 11.3 |                                                  |     |

|     |      | 11.3.1 ASPM                                      |     |

|     |      | 11.3.2 L0 State                                  | 107 |

| R | E | N | E | S | Δ | S |  |

|---|---|---|---|---|---|---|--|

|   |   |   |   |   |   |   |  |

| ٩ |  |  |

|---|--|--|

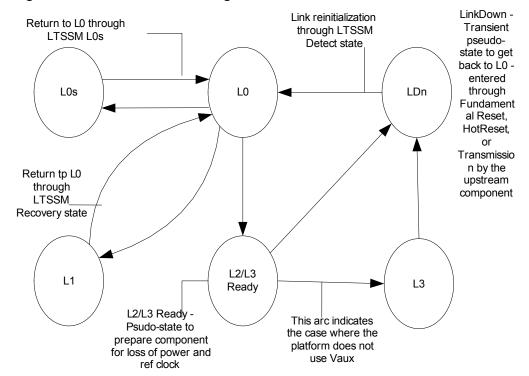

|     |      | 11.3.3   | LOs State                                            | . 107 |

|-----|------|----------|------------------------------------------------------|-------|

|     |      | 11.3.4   | L1 State                                             | . 107 |

|     |      | 11.3.5   | L2/L3 Ready                                          | . 107 |

|     |      | 11.3.6   | L3 State                                             | . 107 |

|     |      | 11.3.7   | LDn State                                            | . 107 |

|     |      | 11.3.8   | Link State Summary                                   | . 108 |

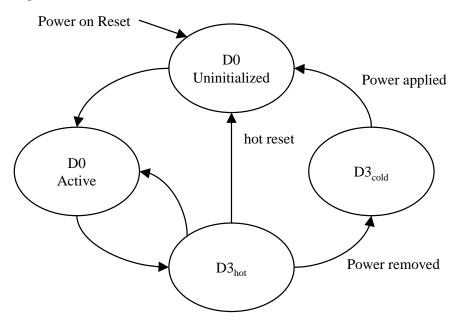

|     |      | 11.3.9   | Device Power States                                  | . 109 |

|     |      | 11.3.10  | D0 State                                             | . 109 |

|     |      | 11.3.11  | D3 <sub>Hot</sub> State                              | . 109 |

|     |      | 11.3.12  | D3 <sub>Cold</sub> State                             | . 109 |

|     |      | 11.3.13  | D State Transitions.                                 | . 110 |

|     |      | 11.3.14  | Power Management Event                               | . 110 |

|     |      | 11.3.15  | Power State Summary                                  | 111   |

|     |      |          | -                                                    |       |

| 12. | Seri |          | ROM                                                  |       |

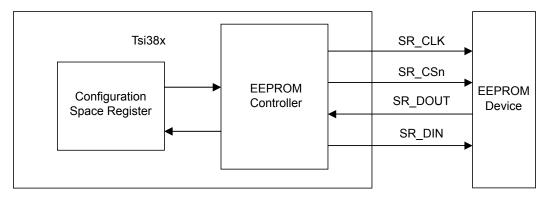

|     | 12.1 | Overviev | w                                                    | . 113 |

|     | 12.2 | •        | Diagram                                              |       |

|     | 12.3 |          | M Image                                              |       |

|     | 12.4 | Functior | nal Timing                                           | . 117 |

| 13  | ΙΤΔ  | G        |                                                      | 121   |

| 10. | 13.1 |          | w                                                    |       |

|     | 13.1 |          | wntroller Initialization                             |       |

|     |      |          |                                                      |       |

|     | 13.3 |          | on Register                                          |       |

|     | 13.4 | • •      | Register                                             |       |

|     | 13.5 |          | evice ID Register                                    |       |

|     | 13.6 | 13.6.1   | egister Access                                       |       |

|     |      |          | Register Access from JTAG                            |       |

|     |      | 13.6.2   | Write Access to Registers from the JTAG Interface    |       |

|     | 127  | 13.6.3   | Read Access to Registers from JTAG Interface         |       |

|     | 13.7 |          | ed Test Pins                                         |       |

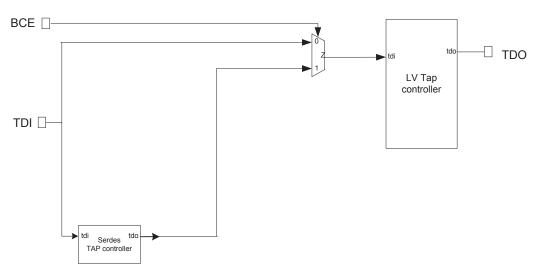

|     | 13.8 | Accessii | ng SerDes TAP Controller                             | . 125 |

| 14. | Reg  | ister D  | escriptions                                          | .127  |

|     | 14.1 | Overvie  | w                                                    | . 127 |

|     | 14.2 | PCI Con  | figuration Space                                     | . 128 |

|     | 14.3 | Register | Map                                                  | . 131 |

|     |      | 14.3.1   | PCI Identification Register                          | . 135 |

|     |      | 14.3.2   | PCI Control and Status Register                      | . 136 |

|     |      | 14.3.3   | PCI Class Register                                   | . 140 |

|     |      | 14.3.4   | PCI Miscellaneous 0 Register                         |       |

|     |      | 14.3.5   | PCI Base Address Register 0                          |       |

|     |      | 14.3.6   | PCI Bus Number Register                              |       |

|     |      | 14.3.7   | PCI Secondary Status and I/O Limit and Base Register |       |

|     |      | 14.3.8   | PCI Memory Base and Limit Register                   |       |

|     |      | 14.3.9   | PCI PFM Base and Limit Register                      |       |

|     |      |          | -                                                    |       |

|      | 14.3.10  | PCI PFM Base Upper 32 Address Register                           | . 148 |

|------|----------|------------------------------------------------------------------|-------|

|      | 14.3.11  | PCI PFM Limit Upper 32 Address Register                          | . 148 |

|      | 14.3.12  | PCI I/O Address Upper 16 Register.                               | . 149 |

|      | 14.3.13  | PCI Capability Pointer Register                                  | . 150 |

|      | 14.3.14  | PCI Bridge Control and Interrupt Register                        | . 151 |

|      | 14.3.15  | Secondary Retry Count Register                                   | . 157 |

|      | 14.3.16  | PCI Miscellaneous Control and Status Register                    | . 158 |

|      | 14.3.17  | PCI Miscellaneous Clock Straps Register                          | . 161 |

|      | 14.3.18  | Upstream Posted Write Threshold Register                         | . 162 |

|      | 14.3.19  | Completion Timeout Register                                      | . 163 |

|      | 14.3.20  | Clock Out Enable Function and Debug Register                     | . 164 |

|      | 14.3.21  | SERRDIS_OPQEN_DTC Register                                       | . 165 |

| 14.4 | Upstream | n Non-transparent Address Remapping Registers                    | . 166 |

|      | 14.4.1   | NTMA Control Register                                            | . 166 |

|      | 14.4.2   | NTMA Primary Upper Base Register                                 | . 167 |

|      | 14.4.3   | NTMA Secondary Lower Base Register                               | . 167 |

|      | 14.4.4   | NTMA Secondary Upper Base Register                               | . 168 |

|      | 14.4.5   | NTMA Secondary Lower Limit Register                              | . 168 |

|      | 14.4.6   | NTMA Secondary Upper Limit Register                              | . 169 |

| 14.5 | PCI Capa | ability Registers                                                | . 169 |

|      | 14.5.1   | SSID/SSVID Capability                                            | . 169 |

|      | 14.5.2   | SSID Capability Register                                         | . 170 |

|      | 14.5.3   | SSID ID Register                                                 | . 171 |

|      | 14.5.4   | MSI Capability and Message Control Register                      | . 172 |

|      | 14.5.5   | MSI Message Address Register                                     | . 174 |

|      | 14.5.6   | MSI Message Address Upper Register                               | . 175 |

|      | 14.5.7   | MSI Message Data Register                                        | . 175 |

|      | 14.5.8   | MSI Mask Register                                                | . 177 |

|      | 14.5.9   | MSI Pending Register                                             | . 178 |

|      | 14.5.10  | PCI Power Management Capability Register                         | . 179 |

|      | 14.5.11  | PCI Power Management Control and Status Register                 | . 181 |

|      | 14.5.12  | EEPROM Control Register                                          | . 183 |

|      | 14.5.13  | Secondary Bus Device Mask Register                               | . 184 |

|      | 14.5.14  | Short-term Caching Period Register                               | . 186 |

|      | 14.5.15  | Retry Timer Status Register                                      | . 187 |

|      | 14.5.16  | Prefetch Control Register                                        | . 188 |

| 14.6 | PCIe Caj | pability Registers                                               | . 189 |

|      | 14.6.1   | PCIe Capabilities Register                                       | . 190 |

|      | 14.6.2   | PCIe Device Capabilities Register                                | . 191 |

|      | 14.6.3   | PCIe Device Control and Status Register                          | . 193 |

|      | 14.6.4   | PCIe Link Capabilities Register                                  | . 196 |

|      | 14.6.5   | PCIe Link Control Register                                       | . 198 |

| 14.7 | Downstr  | eam Non-transparent Address Remapping Registers                  | . 200 |

|      | 14.7.1   | Secondary Bus Non-prefetchable Address Remap Control Register.   | . 200 |

|      | 14.7.2   | Secondary Bus Non-prefetchable Upper Base Address Remap Register | . 201 |

|      |          |                                                                  |       |

|      | 14.7.3   | Secondary Bus Prefetchable Address Remap Control Register      | 201 |

|------|----------|----------------------------------------------------------------|-----|

|      | 14.7.4   | Secondary Bus Prefetchable Upper Base Address Remap Register   | 202 |

|      | 14.7.5   | Primary Bus Non-prefetchable Upper Base Address Remap Register | 202 |

|      | 14.7.6   | Primary Bus Non-prefetchable Upper Limit Remap Register.       | 203 |

| 14.8 | Advance  | d Error Reporting Capability Registers                         | 204 |

|      | 14.8.1   | PCIe Advanced Error Reporting Capability Register              | 204 |

|      | 14.8.2   | PCIe Uncorrectable Error Status Register                       | 205 |

|      | 14.8.3   | PCIe Uncorrectable Error Mask Register                         | 206 |

|      | 14.8.4   | PCIe Uncorrectable Error Severity Register                     | 207 |

|      | 14.8.5   | PCIe Correctable Error Status Register                         | 208 |

|      | 14.8.6   | PCIe Correctable Error Mask Register                           | 209 |

|      | 14.8.7   | PCIe Advanced Error Capabilities and Control Register          | 210 |

|      | 14.8.8   | PCIe Header Log 1 Register                                     | 211 |

|      | 14.8.9   | PCIe Header Log 2 Register                                     | 211 |

|      | 14.8.10  | PCIe Header Log 3 Register                                     | 212 |

|      | 14.8.11  | PCIe Header Log 4 Register                                     | 212 |

|      | 14.8.12  | PCIe Secondary Uncorrectable Error Status Register             | 213 |

|      | 14.8.13  | PCIe Secondary Uncorrectable Error Mask Register               | 214 |

|      | 14.8.14  | PCIe Secondary Uncorrectable Error Severity Register           | 215 |

|      | 14.8.15  | PCIe Secondary Error Capabilities and Control Register         | 216 |

|      | 14.8.16  | PCIe Secondary Header Log 1 Register                           | 216 |

|      | 14.8.17  | PCIe Secondary Header Log 2 Register                           | 217 |

|      | 14.8.18  | PCIe Secondary Header Log 3 Register                           | 218 |

|      | 14.8.19  | PCIe Secondary Header Log 4 Register                           | 218 |

|      | 14.8.20  | Replay Latency Register                                        | 219 |

|      | 14.8.21  | ACK/NACK Update Latency Register                               | 220 |

|      | 14.8.22  | N_FTS Register                                                 |     |

|      | 14.8.23  | GPIO Control Register.                                         | 222 |

|      | 14.8.24  | GPIO Read Register.                                            | 223 |

|      | 14.8.25  | GPIO Write Register                                            | 224 |

|      | 14.8.26  | Interrupt MSI Control Register                                 | 225 |

| 14.9 | PCIe and | I SerDes Control and Status Registers                          | 225 |

|      | 14.9.1   | Base Offset Address Calculation                                | 226 |

|      | 14.9.2   | PCIe Per-Lane Transmit and Receive Registers                   | 227 |

|      | 14.9.3   | PCIe Transmit and Receive Status Register                      | 227 |

|      | 14.9.4   | PCIe Output Status and Transmit Override Register              | 228 |

|      | 14.9.5   | PCIe Receive and Output Override Register                      |     |

|      | 14.9.6   | PCIe Debug and Pattern Generator Control Register              |     |

|      | 14.9.7   | PCIe Pattern Matcher Control and Error Register                |     |

|      | 14.9.8   | PCIe SS Phase and Error Counter Control Register               |     |

|      | 14.9.9   | PCIe Scope Control and Frequency Integrator Register           |     |

|      | 14.9.10  | PCIe Clock Module Control and Status Registers.                |     |

|      | 14.9.11  | PCIe Control and Level Status Register                         |     |

|      | 14.9.12  | PCIe Control and Level Override Register                       |     |

|      |          | -                                                              |     |

| 15.  | Elec  | trical Characteristics 23                                 | 37  |

|------|-------|-----------------------------------------------------------|-----|

|      | 15.1  | Absolute Maximum Ratings                                  | 237 |

|      | 15.2  | Recommended Operating Conditions                          | 238 |

|      | 15.3  | Power Characteristics                                     | 238 |

|      | 15.4  | Power Supply Sequencing                                   | 239 |

|      | 15.5  | DC Operating Characteristics                              | 239 |

|      | 15.6  | AC Timing Specifications                                  | 240 |

|      |       | 15.6.1 PCI Interface AC Signal Timing 2                   | 240 |

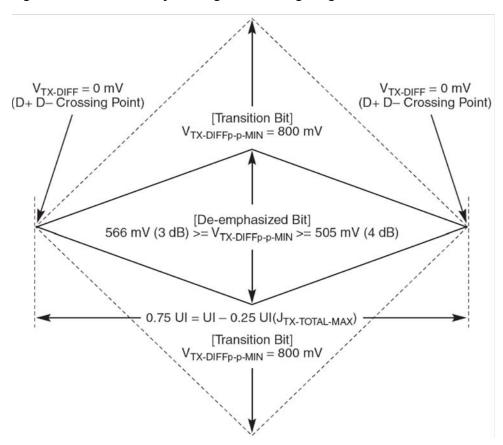

|      |       | 15.6.2 PCIe Differential Transmitter Output Specification | 242 |

|      |       | 15.6.3 PCIe Differential Receiver Input Specifications 2  | 246 |

|      |       | 15.6.4 Reference Clock                                    | 249 |

|      |       | 15.6.5 Boundary Scan Test Signal Timing 2                 | 250 |

|      |       | 15.6.6 Reset Timing                                       | 250 |

|      | 15.7  | AC Timing Waveforms                                       | 251 |

| 16.  | Pacl  | kaging                                                    | 55  |

|      | 16.1  | Mechanical Diagram                                        | 255 |

|      | 16.2  | Thermal Characteristics                                   |     |

|      | 16.3  | Moisture Sensitivity                                      | 258 |

| 17.  | Orde  | ering Information                                         | 59  |

|      | 17.1  | Part Numbers                                              | 259 |

|      | 17.2  | Part Numbering Information                                | 259 |

| Α.   | PCle  | e Programmable Transmit and Receive Equalization          | 61  |

|      | A.1   | Overview                                                  | 261 |

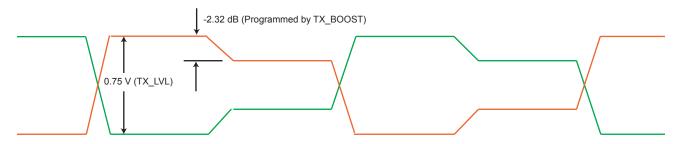

|      | A.2   | Transmit Drive Level and Equalization                     | 261 |

|      | A.3   | Receive Equalization                                      | 262 |

| Glo  | ssary | /                                                         | 63  |

| Inde | эх    |                                                           | 65  |

## **Figures**

| Figure 1:  | Tsi382A Block Diagram                                            |

|------------|------------------------------------------------------------------|

| Figure 2:  | Tsi382A Device Architecture                                      |

| Figure 3:  | Motherboard Application                                          |

| Figure 4:  | ExpressCard Application                                          |

| Figure 5:  | DVR Card Application                                             |

| Figure 6:  | Upstream Data Path                                               |

| Figure 7:  | Downstream Data Path                                             |

| Figure 8:  | Memory-mapped I/O Address Space                                  |

| Figure 9:  | 64-bit Prefetchable Memory Address Range                         |

| Figure 10: | I/O Address Space                                                |

| Figure 11: | ISA Mode I/O Addressing                                          |

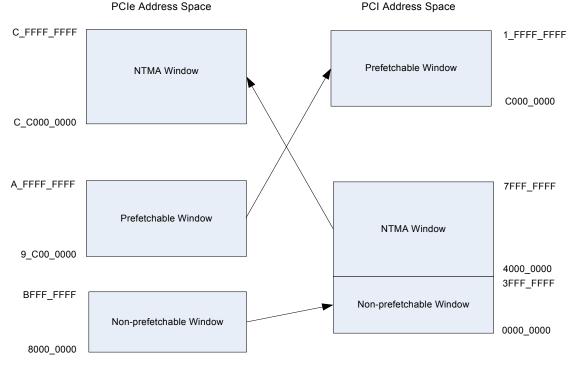

| Figure 12: | Memory Window Remapping Example                                  |

| Figure 13: | PCIe Configuration Address Format                                |

| Figure 14: | PCI Type 0 Configuration Address Format                          |

| Figure 15: | PCI Type 1 Configuration Address Format                          |

| Figure 16: | PCI Arbiter Block Diagram                                        |

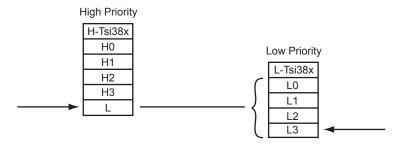

| Figure 17: | PCI Arbitration Priority                                         |

| Figure 18: | Arbitration Pointers – Example 1                                 |

| Figure 19: | Arbitration Pointers – Example 2                                 |

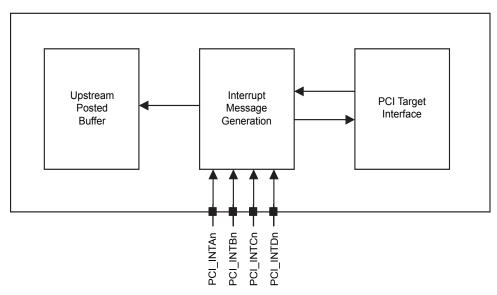

| Figure 20: | Interrupt Handling Diagram                                       |

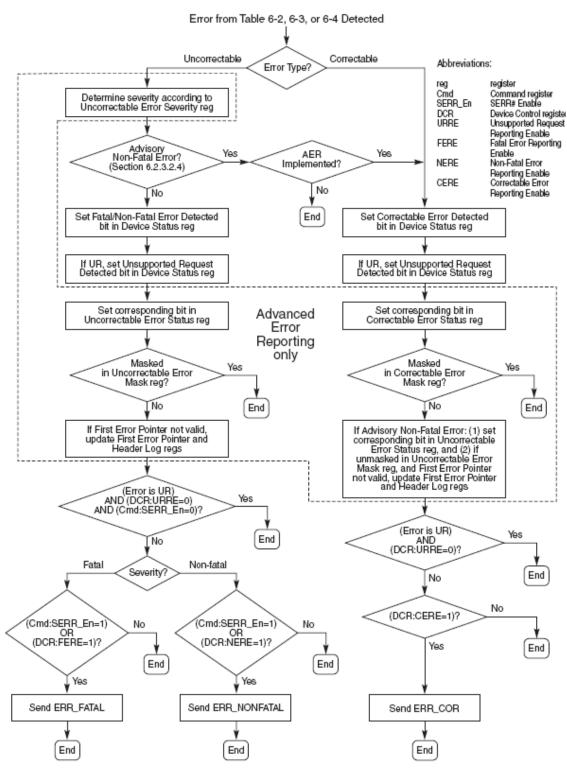

| Figure 21: | PCIe Flowchart of Device Error Signaling and Logging Operations  |

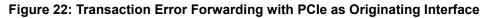

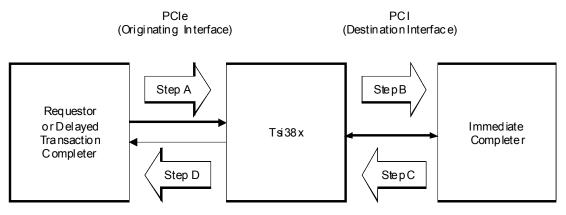

| Figure 22: | Transaction Error Forwarding with PCIe as Originating Interface  |

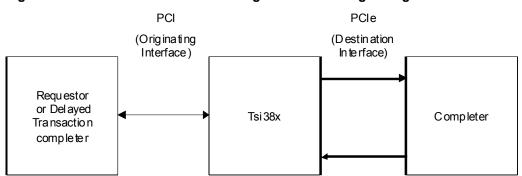

| Figure 23: | Transaction Error Forwarding with PCI as Originating Interface   |

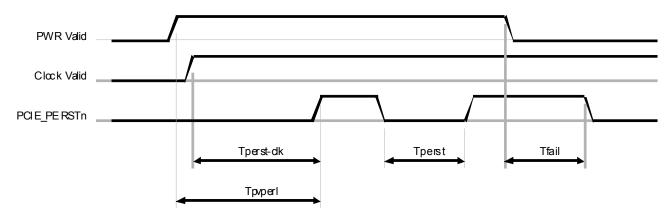

| Figure 24: | Reset Timing                                                     |

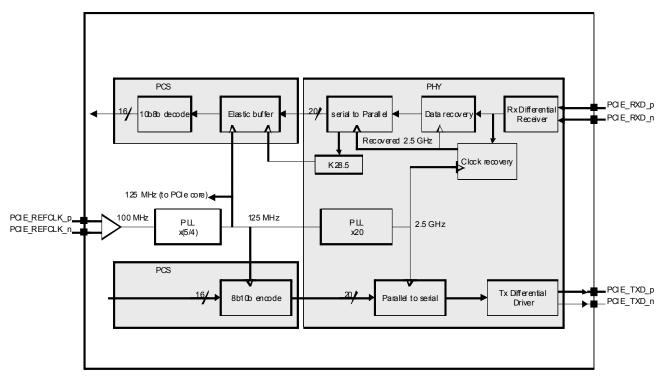

| Figure 25: | PCIe Clocking                                                    |

| Figure 26: | PCI Clocking                                                     |

| Figure 27: | PCIe Link Power Management States 108                            |

| Figure 28: | D State Transitions                                              |

| Figure 29: | EEPROM Interface                                                 |

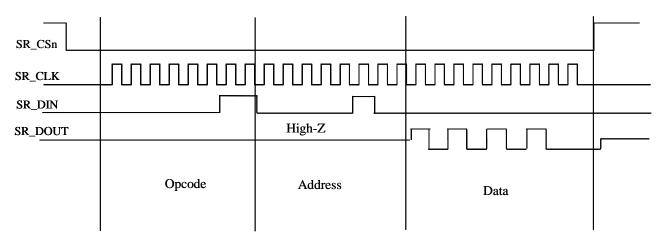

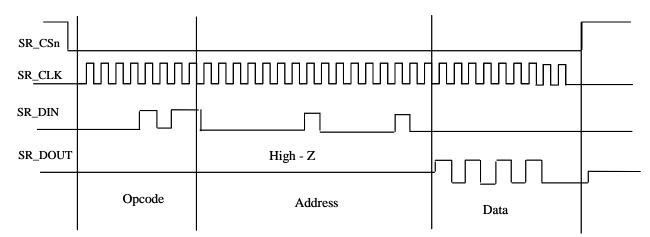

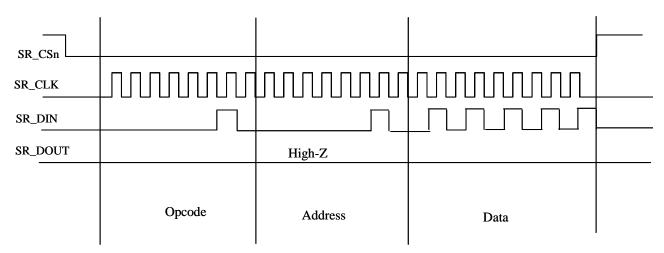

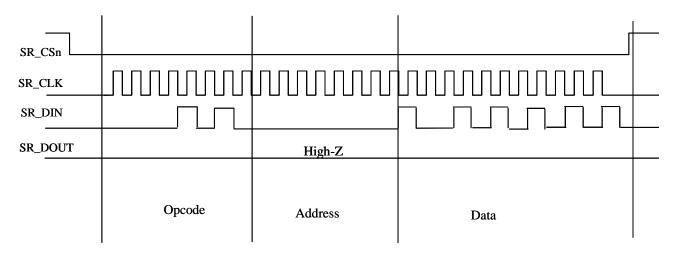

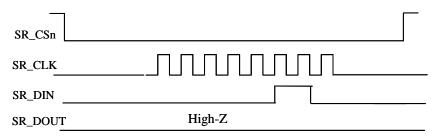

| Figure 30: | 9-bit EEPROM Read Timing                                         |

| Figure 31: | 16-bit EEPROM Read Timing                                        |

| Figure 32: | 9-bit EEPROM Write Timing                                        |

| Figure 33: | 16-bit EEPROM Write Timing                                       |

| Figure 34: | EEPROM WREN Instruction Timing 119                               |

| Figure 35: | EEPROM RDSR Instruction Timing 119                               |

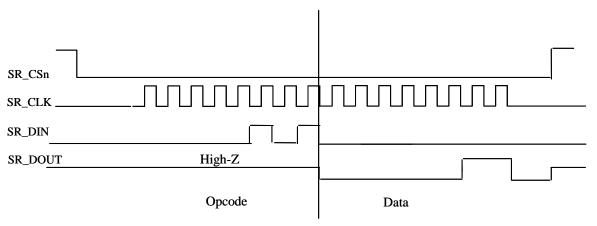

| Figure 36: | Read/Write Access from JTAG — Serial Data In 123                 |

| Figure 37: | Observe from JTAG — Serial Data Out                              |

| Figure 38: | PCIe SerDes Connections                                          |

| Figure 39: | Transmitter Eye Voltage and Timing Diagram                       |

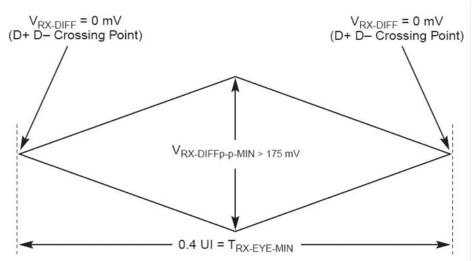

| Figure 40: | Minimum Receiver Eye Timing and Voltage Compliance Specification |

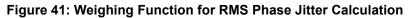

| Figure 41: | Weighing Function for RMS Phase Jitter Calculation               |

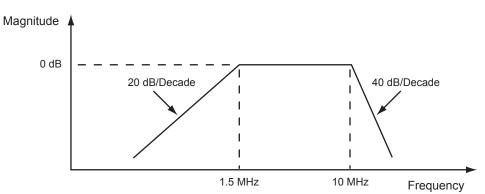

| Figure 42: | Input Timing Measurement Waveforms                               |

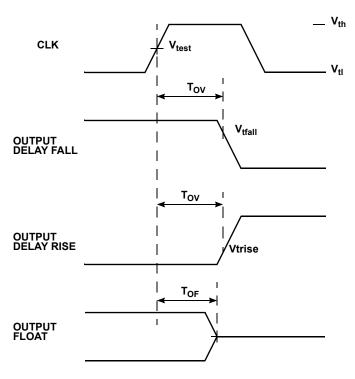

| Figure 43: | Output Timing Measurement Waveforms         | 252 |

|------------|---------------------------------------------|-----|

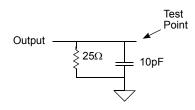

| Figure 44: | PCI TOV (max) Rising Edge AC Test Load      | 252 |

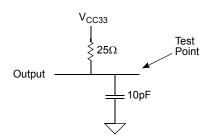

| Figure 45: | PCI TOV (max) Falling Edge AC Test Load     | 252 |

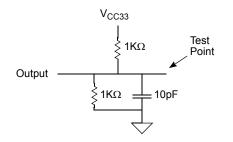

| Figure 46: | PCI TOV (min) AC Test Load 2                | 253 |

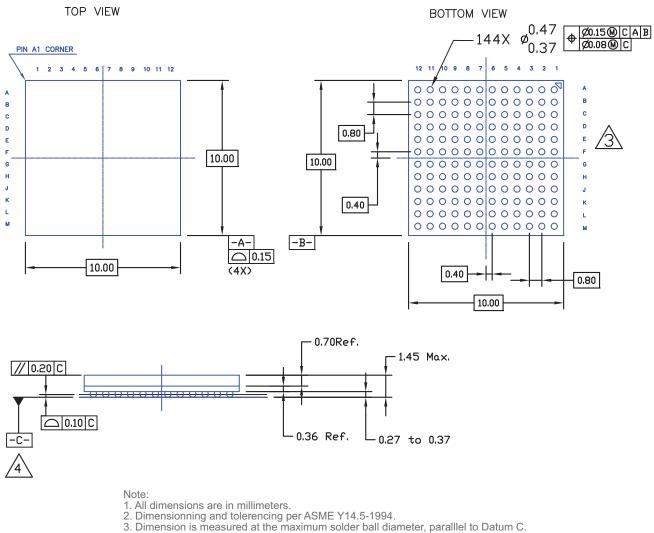

| Figure 47: | Mechanical Diagram – 144-pin 10x10mm BGA 2  | 255 |

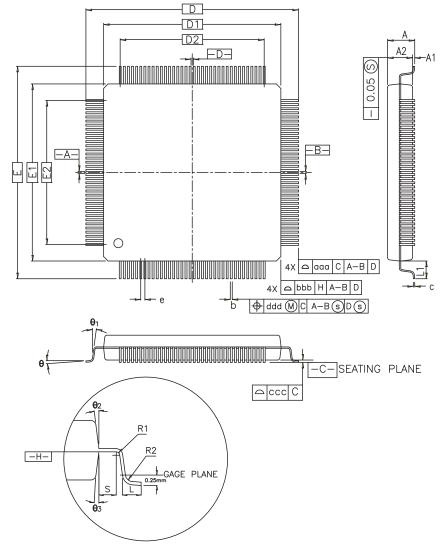

| Figure 48: | Mechanical Diagram – 176-pin 20x20mm LQFP 2 | 256 |

| Figure 49: | Drive Strength and Equalization Waveform    | 262 |

## RENESAS

## **Tables**

| Table 1:  | Pin Types                                                                        |

|-----------|----------------------------------------------------------------------------------|

| Table 2:  | PCIe Interface Signals                                                           |

| Table 3:  | PCI Interface Signals                                                            |

| Table 4:  | EEPROM Interface Signals                                                         |

| Table 5:  | GPIO Interface Signals                                                           |

| Table 6:  | JTAG Interface Signals                                                           |

| Table 7:  | Power-up Signals                                                                 |

| Table 8:  | Power Supply Signals                                                             |

| Table 9:  | Completion Buffer Allocation                                                     |

| Table 10: | Initial Credit Advertisement                                                     |

| Table 11: | PCI Transaction Support                                                          |

| Table 12: | PCIe Transaction Support                                                         |

| Table 13: | Transaction Ordering                                                             |

| Table 14: | Error Forwarding Requirements (Step A to Step B) for Received PCIe Errors        |

| Table 15: | Bridge Requirements for Transactions Requiring a Completion (Immediate Response) |

| Table 16: | Error Forwarding Requirements for Received PCI Errors                            |

| Table 17: | Error Forwarding Requirements for PCI Delayed Transaction                        |

| Table 18: | ECRC Errors                                                                      |

| Table 19: | Poisoned TLP Errors                                                              |

| Table 20: | Malformed TLP Errors                                                             |

| Table 21: | Link and Flow Control Errors                                                     |

| Table 22: | Uncorrectable Data/Address Errors                                                |

| Table 23: | Received Master/Target Abort Error                                               |

| Table 25: | Request Errors                                                                   |

| Table 24: | Completion Errors                                                                |

| Table 26: | Reset Summary                                                                    |

| Table 27: | Reset Timing                                                                     |

| Table 28: | PCI Clocking                                                                     |

| Table 29: | PCIe Link States                                                                 |

| Table 30: | Power Management State Summary 111                                               |

| Table 31: | EEPROM Image 116                                                                 |

| Table 32: | PCI Type 1 Configuration Header 128                                              |

| Table 33: | SSID Capability Registers                                                        |

| Table 34: | MSI Capability Registers                                                         |

| Table 35: | Power Management Capability Registers 129                                        |

| Table 36: | PCIe Capability Registers 129                                                    |

| Table 37: | Advanced Error Reporting Capability Registers 130                                |

| Table 38: | Register Map 131                                                                 |

| Table 39: | SerDes Per-lane and Clock Control and Status Register Map 226                    |

| Table 40: | TX_LVL Values                                                                    |

| Table 41: | Absolute Maximum Ratings – PCI                                                   |

| Table 42: | Absolute Maximum Ratings – PCIe                                                  |

| Table 43: | Recommended Operating Conditions                             | . 238 |

|-----------|--------------------------------------------------------------|-------|

| Table 44: | Power Characteristics.                                       | . 238 |

| Table 45: | DC Operating Characteristics                                 | . 239 |

| Table 46: | PCI Clock (PCI_CLK) Specification.                           | . 240 |

| Table 47: | AC Specifications for PCI Interface                          | . 241 |

| Table 48: | PCIe Differential Transmitter Output Specification           | . 242 |

| Table 49: | PCIe Differential Receiver Input Specifications              | . 246 |

| Table 50: | Reference Clock (PCIE_REFCLK_n/p) Electrical Characteristics | . 249 |

| Table 51: | Boundary Scan Test Signal Timings                            | . 250 |

| Table 52: | Reset Timing                                                 | . 250 |

| Table 53: | Thermal Characteristics                                      | . 257 |

| Table 54: | Junction to Ambient Characteristics                          | . 257 |

| Table 55: | Part Numbers                                                 | . 259 |

|           |                                                              |       |

## **About this Document**

This section discusses the following topics:

- "Scope"

- "Document Conventions"

- "Revision History"

## Scope

The *Tsi382A PCIe-to-PCI Bridge User Manual* discusses the features, capabilities, and configuration requirements for the Tsi382A.

## **Document Conventions**

This document uses the following conventions.

### **Non-differential Signal Notation**

Non-differential signals are either active-low or active-high. An active-low signal has an active state of logic 0 (or the lower voltage level), and is denoted by a lowercase "n". An active-high signal has an active state of logic 1 (or the higher voltage level), and is not denoted by a special character. The following table illustrates the non-differential signal naming convention.

| State       | Single-line signal | Multi-line signal |

|-------------|--------------------|-------------------|

| Active low  | NAMEn              | NAMEn[3]          |

| Active high | NAME               | NAME[3]           |

### **Differential Signal Notation**

Differential signals consist of pairs of complement positive and negative signals that are measured at the same time to determine a signal's active or inactive state (they are denoted by "\_p" and "\_n", respectively). The following table illustrates the differential signal naming convention.

| State    | Single-line signal       | Multi-line signal                |

|----------|--------------------------|----------------------------------|

| Inactive | NAME_p = 0<br>NAME_n = 1 | NAME_p[3] = 0<br>NAME_n[3] =1    |

| Active   | NAME_p = 1<br>NAME_n = 0 | NAME_p[3] is 1<br>NAME_n[3] is 0 |

## **Object Size Notation**

- A *byte* is an 8-bit object.

- A word is a 16-bit object.

- A doubleword (Dword) is a 32-bit object.

### **Numeric Notation**

- Hexadecimal numbers are denoted by the prefix Ox (for example, 0x04).

- Binary numbers are denoted by the prefix *0b* (for example, 0b010).

- Registers that have multiple iterations are denoted by  $\{x..y\}$  in their names; where x is first register and address, and y is the last register and address. For example, REG $\{0..1\}$  indicates there are two versions of the register at different addresses: REG0 and REG1.

### **Symbols**

This symbol indicates a basic design concept or information considered helpful.

This symbol indicates important configuration information or suggestions.

This symbol indicates procedures or operating levels that may result in misuse or damage to the device.

## **Document Status Information**

- Advance Contains information that is subject to change, and is available once prototypes are released to customers.

- Preliminary Contains information about a product that is near production-ready, and is revised as required.

- Formal Contains information about a final, customer-ready product, and is available once the product is released to production.

## **Revision History**

## April 17, 2014, Formal

- Corrected a typo in the second paragraph in "Overview"

- Updated the design recommendation for PCIE\_REFCLK\_n in Table 2

- Updated the description of PCI\_CLKO in Table 3

- Changed all references to PCI\_VIO to VIO\_PCI in Table 3

- Changed "Polarity Inversion" to "Polarity Reversal". This was an incorrect update in the previous manual.

- Updated the bit setting numbers in Table 9; however, no technical changes were made

- Changed the second paragraph in "PCI Non-posted Requests" to indicate the bridge enqueues up to eight requests

- Removed the second paragraph in "Block Diagram" because it is not applicable to the device

- The 00110 setting for the UPST\_PWR\_THRES bit in the "Upstream Posted Write Threshold Register" was correctly changed to 112 bytes in the previous manual; however, the change was not listed in its revision history.

- The bit description for ADD64 in the "MSI Capability and Message Control Register" was corrected to match the *PCI Express Base Specification (Revision 1.1)* in the previous manual; however, the change was not listed in its revision history.

- Removed BPCCE and B2B3S from the "PCI Power Management Control and Status Register" because the bits are not applicable to the device. This register space is now reserved.

## January 13, 2014, Formal

This version of the document was rebranded as IDT. The only technical change was to the maximum value of VIH\_PCI5V in Table 45. It was changed to  $VIO_PCI + 0.5$  from  $VDD_PCI + 0.5$ .

### May 2009, Formal

This is the first version of the Tsi382A User Manual.

## 1. Functional Overview

Topics discussed include the following:

- "Overview"

- "Features"

- "Device Architecture"

- "Typical Applications"

## 1.1 Overview

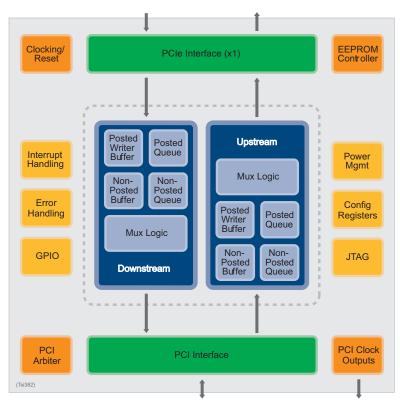

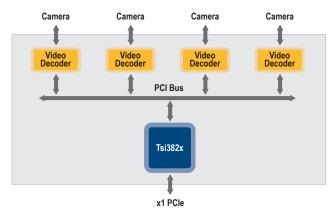

The IDT Tsi382A is a high-performance bus bridge that connects the PCI Express (PCIe) protocol to the PCI bus standard (see Figure 1).

The Tsi382A's PCIe Interface supports a x1 lane PCIe configuration. This enables the bridge to offer exceptional throughput performance of up to 2.5 Gbps per transmit and receive direction. The device's PCI Interface can operate up to 66 MHz. This interface offers designers extensive flexibility by supporting the following addressing modes: transparent, and non-transparent.

#### Figure 1: Tsi382A Block Diagram

## 1.2 Features

The Tsi382A's key features are listed in the following sub-sections.

### 1.2.1 General Features

- Forward bridge, PCIe to PCI

- Single store and forward for optimal latency performance

- Supports two modes of addressing:

- Transparent: For efficient, flow-through configurations

- Non-transparent: For address remapping of the PCIe and the PCI domains

- Compliant to the following specifications:

- PCI Express Base Specification (Revision 1.1)

- PCI Express-to-PCI/PCI-X Bridge Specification (Revision 1.0)

- PCI-to-PCI Bridge Specification (Revision 1.2)

- PCI Local Bus Specification (Revision 3.0)

- PCI Bus Power Management Interface Specification (Revision 1.2)

- 3.3V PCI I/Os with 5V tolerant I/Os

- Support for four external PCI bus masters through an integrated arbiter

- Support for external PCI bus arbiter

- Support for Masquerade mode (can overwrite vendor and device ID from EEPROM)

- JTAG IEEE 1149.1, 1149.6

- Support for D0, D3 hot, D3 cold power management states

- Support for Subsystem ID (SSID) and Subsystem Vendor ID (SSVID)

- Legacy mode support for subtractive decode

- Four GPIO pins that can be configured to generate MSIs

- Four interrupt pins that can be configured to generate MSIs

- Exclusive access using PCI\_LOCKn

- Packaging:

- 10 x 10 mm, 144-pin BGA

- 20 x 20 mm, 176-pin LQFP

### 1.2.2 PCIe Features

- 1 lane

- 128-byte maximum payload

- Advanced error reporting capability

- End-to-end CRC (ECRC) check and generation

- Up to four outstanding memory reads

- Four, 128-byte read completion buffers

- ASPM L0s link state power management

- Legacy interrupt signaling and MSI interrupts

## 1.2.3 PCI Features

- 32/64-bit addressing

- 32-bit data bus

- 5V tolerant

- Exclusive access using PCI\_LOCKn

- 25-, 33-, 50-, and 66-MHz operation

- Up to eight outstanding read requests

- 1-KB read completion buffer

- Clock outputs for four PCI devices

- Short-term caching support

## **1.3 Device Architecture**

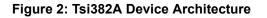

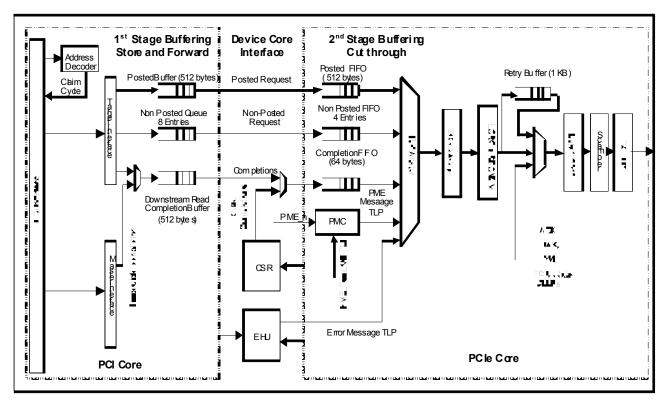

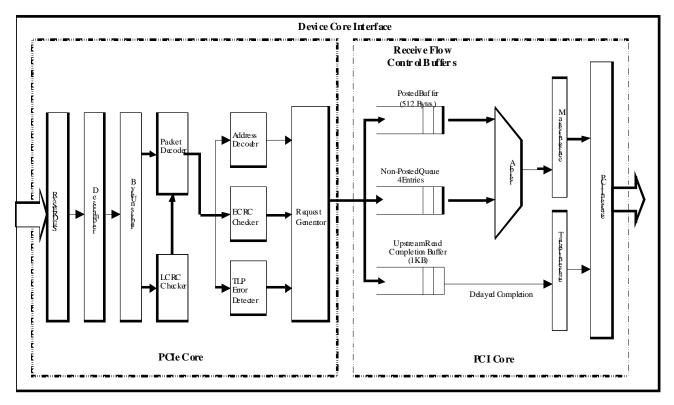

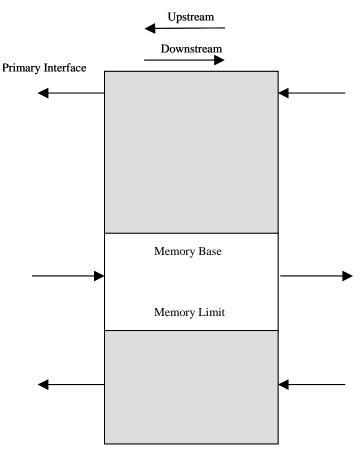

A high-level, architectural diagram of the Tsi382A is displayed in Figure 2. For more information about data flow through the device, see "Upstream Data Path" and "Downstream Data Path".

Packets received on the PCIe Interface are processed by the data link layer and transaction layer, if applicable. If a packet is destined for the transaction layer, its address is decoded and forwarded to the appropriate destination:

- Configuration register

- Downstream posted write buffer

- Downstream read request queue

- Downstream read completion buffer

PCI data that is destined for the PCIe fabric are subject to PCIe ordering rules. Data is pulled from the appropriate queue:

- Configuration register

- Upstream posted write buffer

- Upstream read request queue

- Upstream read completion buffer

PCI transactions that are decoded for the PCIe address space are forwarded to the appropriate queue:

- Upstream read request queue

- Upstream posted write buffer

Transactions destined for downstream devices on the PCI bus, are subject to PCI ordering rules. Data is pulled form the appropriate queue:

- Downstream posted write buffer

- Downstream read request queue

PCIe is a serialized protocol at the physical layer, and a packetized protocol at the data link layer. The PCIe lane operates at 2.5 Gb symbol rate, or at 2.0 Gb data rate; the difference is a result of the 8/10b coding process. The Tsi382A uses the following processes to ensure the accurate and timely delivery of data through the data link layer:

- Credit-based flow control Prevents data loss and congestion

- ACK/noACK protocol and End-to-End CRC (ECRC) Ensures reliable data delivery if bit errors occur

- Replay buffer Replays packets that are not acknowledged by the receiver (NAK)

In contrast, PCI is a parallel data interface at the physical layer. PCI is a non-packetized protocol. When a bus master starts a read or a write transaction, it indicates only the starting transaction address to the target, and not the size of the read or write. In the case of a PCI write, which is initiated on the PCI Interface and is destined for the root complex, the data is written into an upstream posted write buffer in the Tsi382A. The end of the write transaction is signaled by the master on the PCI bus. Once the write is completed the data can be forwarded to the PCIe Interface. If the posted write buffer is about to overflow, the Tsi382A indicates a retry/disconnect on the PCI bus. Once the posted write buffer empties, the Tsi382A can accept additional write transactions. The Tsi382A will split write transactions as required to meet PCIe constraints: to prevent a write crossing a 4-KB boundary; if byte enables are used throughout the transaction; or if the quantity of data exceeds the maximum payload size (see MAX\_SIZE in "PCIe Device Capabilities Register"). The upstream posted write buffer is managed as a simple FIFO.

A read initiated on the PCI bus that is decoded for an upstream target is handled as a delayed transaction by the Tsi382A. The bridge latches the read transaction and attempts to reserve buffer space in its upstream read completion buffer. If space is successfully reserved in the buffer, the Tsi382A initiates a read on the PCIe Interface. When the read data is returned from the root complex, it is stored in the upstream read completion buffer. PCI-initiated reads, however, do not define the amount of data to read. Once the master on the PCI bus retries the read transaction, the transaction is checked to determine if the read data is returned. If it has the read data, the Tsi382A responds as the target and transfers the read data to the PCI bus. Note the upstream read completion buffer becomes empty prior to the transaction completing, the Tsi382A disconnects from the PCI bus. When the read transaction is completed, the Tsi382A discards any prefetched data that is not used and frees up the buffer.

A write initiated on the PCIe Interface with the target on the downstream PCI bus is written into the downstream posted write buffer. The Tsi382A acts as the master for the transaction and arbitrates for the PCI bus and initiates the write transaction. The downstream posted write buffer is managed as a FIFO. There will always be space available in the buffer to accept packet data because of the flow control method used by the PCIe data link layer. If the downstream posted write buffer is about to overflow, the upstream device will be informed of this by its lack of credits and will not send any more write data to the Tsi382A.

A read initiated on the PCIe Interface with the target on the downstream PCI bus is written into the downstream read request queue. The downstream read request queue is managed with flow control credits to prevent overflowing. The Tsi382A latches the read transaction and attempts to reserve space in the downstream read completion buffer. If space is successfully reserved in the buffer, the Tsi382A acts as the master for the transaction and initiates a read transaction on the PCI bus. The read request queue is managed using a round-robin algorithm. Programmable address decoders instruct the Tsi382A which transactions on the PCI bus to forward upstream, and which transactions on the PCI link to forward downstream.

## 1.4 Typical Applications

This section illustrates some typical applications for the Tsi382A.

#### Figure 3: Motherboard Application

#### Figure 4: ExpressCard Application

### Figure 5: DVR Card Application

## 2. Signal Descriptions

Topics discussed include the following:

- "Overview"

- "PCIe Interface Signals"

- "PCI Interface Signals"

- "EEPROM Interface Signals"

- "GPIO Signals"

- "JTAG Interface Signals"

- "Power-up Signals"

- "Power Supply Signals"

## 2.1 Overview

Signals are classified according to the types defined in the following table.

#### Table 1: Pin Types

| Pin Type     | Definition                                                    |

|--------------|---------------------------------------------------------------|

| 3.3 OD       | 3.3V CMOS open-drain output                                   |

| 3.3 3-state  | 3.3V CMOS tri-state output                                    |

| 3.3 Bidir    | 3.3V CMOS bi-directional                                      |

| 3.3 Bidir PU | 3.3V CMOS bi-directional with 265K (+/- 45K) pull-up resistor |

| 3.3 Bidir OD | 3.3V CMOS bi-directional open-drain                           |

| 3.3 In       | 3.3V CMOS input                                               |

| 3.3 In PU    | 3.3V CMOS input with 265K (+/- 45K) pull-up resistor          |

| 3.3 Out      | 3.3V CMOS output                                              |

| PCI Bidir    | PCI bi-directional                                            |

| PCI Bidir OD | PCI bi-directional open-drain                                 |

| PCI In       | PCI input                                                     |

| PCI Out      | PCI output                                                    |

| PCI OD       | PCI output open-drain                                         |

### Table 1: Pin Types (Continued)

| Pin Type      | Definition               |

|---------------|--------------------------|

| PCIE Diff Out | PCIe differential output |

| PCIE Diff In  | PCIe differential input  |

## 2.2 PCIe Interface Signals

#### Table 2: PCle Interface Signals

| Name                           | Pin Type      | Description                                                                                                                             | Design Recommendation                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCIE_PERSTn                    | 3.3 In        | Master reset in:<br>0 = Tsi382A in reset<br>1 = Tsi382A in normal mode                                                                  | Direct connect to the PERST# signal.                                                                                                                                                                                                                                                                                                                                        |

| PCIE_TXD_n<br>PCIE_TXD_p       | PCIE Diff Out | Transmit Data. These differential pair<br>signals send PCIe 8b/10b encoded<br>symbols and an embedded clock to the<br>link partner.     | DC blocking capacitors must be placed<br>in the link between the transmitter and<br>the receiver. Place a 0603 or 0402<br>0.075uF to 0.1uF ceramic capacitor on<br>each TXD_n, TXD_p signal.                                                                                                                                                                                |

| PCIE_RXD_n<br>PCIE_RXD_p       | PCIE Diff In  | Receive Data. These differential pair<br>signals receive PCIe 8b/10b encoded<br>symbols and an embedded clock from<br>the link partner. | DC blocking capacitors must be placed<br>in the link between the transmitter and<br>the receiver; however, the DC blocking<br>capacitors are normally placed near the<br>transmitter. When designing an add-in<br>card, capacitors are not required on this<br>link. When designing a system board,<br>the DC blocking capacitors should be<br>placed near the transmitter. |

| PCIE_REFCLK_n<br>PCIE_REFCLK_p | PCIE Diff In  | Reference Clock. 100-MHz differential reference clock.                                                                                  | Refer to the <i>Tsi382A Board Design Guidelines</i> .                                                                                                                                                                                                                                                                                                                       |

| PCIE_REXT                      | Analog        | -                                                                                                                                       | This signal must be connected to VSS with a 191-ohm (1%) resistor.                                                                                                                                                                                                                                                                                                          |

## 2.3 PCI Interface Signals

## Table 3: PCI Interface Signals

| Name          | Pin Type  | Description                                                                                                                                                                                                                          | Design Recommendation                                                                                                                                                          |

|---------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI_AD[31:0]  | PCI Bidir | Address/Data Bus. These multiplexed signals provide a 32/64-bit address and 32-bit data bus.                                                                                                                                         | None.                                                                                                                                                                          |

| PCI_CBEn[3:0] | PCI Bidir | Command/Byte Enables. These<br>multiplexed signals indicate the current<br>transaction type.                                                                                                                                         | None.                                                                                                                                                                          |

| PCI_CLK       | PCI In    | PCI Input Clock. This signal provides<br>timing for the Tsi382A, either from an<br>external clock or from one of the<br>PCI_CLKO[4:0] signals (see<br>"Clocking").                                                                   | None.                                                                                                                                                                          |

| PCI_CLKO[4:0] | PCI Out   | PCI Output Clocks. These signals are<br>used for driving a device and driving<br>feedback to PCI_CLK (see "Clocking").                                                                                                               | Point-to-point connection to PCI device.<br>IDT recommends a 33 Ohm series<br>termination resistor. In Master clocking<br>mode, PCI_CLKO[4] should be<br>connected to PCI_CLK. |

| PCI_DEVSELn   | PCI Bidir | Device Select. A target device asserts<br>this signal when it decodes its address<br>on the bus. The master samples the<br>signal at the beginning of a transaction,<br>and the target rescinds it at the end of<br>the transaction. | Pull up (8.2K) to VIO_PCI.                                                                                                                                                     |

| PCI_FRAMEn    | PCI Bidir | Frame. The current initiator drives this signal to indicate the start and duration of a transaction, and the bus target samples it. The bus master rescinds the signal at the end of the transaction.                                | Pull up (8.2K) to VIO_PCI.                                                                                                                                                     |

## Table 3: PCI Interface Signals (Continued)

| Name          | Pin Type               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Design Recommendation                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI_GNTn[3:0] | PCI Bidir / PCI<br>Out | Bus Grant. The Tsi382A uses these<br>multifunction signals to grant access to<br>the PCI bus; however, they are used<br>differently depending on whether or not<br>the Tsi382A PCI arbiter is used. If the<br>arbiter is used, then PCI_GNTn[3:0] are<br>outputs used by the Tsi382A to grant<br>access to the bus (see "PCI<br>Arbitration").<br>If an external arbiter is used,<br>PCI_GNTn[0] is an input that is driven<br>by the arbiter to grant the Tsi382A<br>access to the bus. The remaining pins,<br>PCI_GNTn[3:1], remain as outputs.<br>The input/output mode is controlled by<br>the PWRUP_EN_ARB pin (see<br>"Power-up Signals"). | PCI_GNTn[3:0] outputs connect directly<br>to the PCI device's PCI_GNTn inputs.<br>Pull ups are not required on unused<br>outputs.                                                                                                                                                                                                                                                                  |

| PCI_INTDn     | PCI In                 | Interrupt D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pull-up (2.4K) to PCI_VIO.                                                                                                                                                                                                                                                                                                                                                                         |

| PCI_INTCn     | PCI In                 | Interrupt C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pull-up (2.4K) to PCI_VIO.                                                                                                                                                                                                                                                                                                                                                                         |

| PCI_INTBn     | PCI In                 | Interrupt B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pull-up (2.4K) to PCI_VIO.                                                                                                                                                                                                                                                                                                                                                                         |

| PCI_INTAn     | PCI In                 | Interrupt A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pull-up (2.4K) to PCI_VIO.                                                                                                                                                                                                                                                                                                                                                                         |

| PCI_IRDYn     | PCI Bidir              | Initiator Ready. The bus master asserts<br>this signal to indicate it is ready to<br>complete the current transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Pull-up (8.2K) to PCI_VIO.                                                                                                                                                                                                                                                                                                                                                                         |

| PCI_LOCKn     | PCI OD                 | Lock. This signal is used by the bus<br>master to lock the currently addressed<br>memory target during a series of<br>exclusive access transactions (see<br>"Exclusive Access").                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pull up (8.2K) to PCI_VIO.                                                                                                                                                                                                                                                                                                                                                                         |

| PCI_M66EN     | PCI In                 | 66-MHz Enable. This signal enables the<br>PCI Interface for 66-MHz operation.<br>0 = 33-MHz operation<br>1 = 66-MHz operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PCI_M66EN is used only in master<br>clocking mode.<br><u>Embedded designs</u><br>Tied to ground for 33-MHz operation;<br>otherwise, pull up to PCI_VIO.<br><u>Bused designs using PCI slots for add-</u><br><u>in cards</u><br>Place a 10K pull-up resistor (to<br>PCI_VIO) on PCI_M66EN and route the<br>signal from slot to slot.<br>In slave clocking mode, PCI_M66EN<br>can be tied to ground. |

### Table 3: PCI Interface Signals (Continued)

| Name          | Pin Type            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Design Recommendation                         |

|---------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| PCI_PAR       | PCI Bidir           | Parity. This signal carries even parity<br>across PCI_AD[31:0] and<br>PCI_CBEn[3:0]. The bus master<br>asserts this signal for the address and<br>write data phases. The bus target<br>asserts it for read data phases.                                                                                                                                                                                                                                                                                                                               | No pull-up or pull-down resistor is required. |

| PCI_PERRn     | PCI Bidir           | Parity Error. This signal indicates a<br>parity error occurred during the current<br>data phase. The bus target that<br>receives the data asserts this signal.                                                                                                                                                                                                                                                                                                                                                                                        | Pull up (8.2K) to PCI_VIO.                    |

| PCI_PMEn      | PCI In              | Power Management Event. This signal indicates a power management event occurred (see "Power Management").                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pull up (8.2K) to PCI_VIO.                    |

| PCI_REQn[3:0] | PCI In<br>PCI Bidir | Bus Request. These signals are used to<br>request access to the PCI bus. They are<br>used differently, however, depending on<br>whether or not the Tsi382A PCI arbiter<br>is used. If the PCI arbiter is used, then<br>PCI_REQn[3:0] are inputs used by<br>external masters to request access to<br>the bus.<br>If an external arbiter is used,<br>PCI_REQn[0] is an output used by the<br>Tsi382A to request access to the bus,<br>while PCI_REQn[3:1] should be pulled<br>high, as they are still inputs.<br>The input/output mode is controlled by | Pull up (8.2K) to PCI_VIO.                    |

|               |                     | the PWRUP_EN_ARB pin (see<br>"Power-up Signals").                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |

| PCI_RSTn      | PCI Out             | PCI reset: This signal resets all devices on the PC bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | No pull-up or pull-down resistor is required. |

| PCI_SERRn     | PCI Bidir OD        | System Error. This signal indicates an address or attribute phase parity error occurred.                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pull-up (8.2K) to PCI_VIO.                    |