# IDT<sub>®</sub> Tsi572 Serial RapidIO Switch

# **Hardware Manual**

May 18, 2012

© 2019 Renesas Electronics Corporation

#### GENERAL DISCLAIMER

Integrated Device Technology, Inc. (1DT<sup>-</sup>) reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance. IDT does not assume responsibility for use of any circuitry described herein other than the circuitry embodied in an IDT product. Disclosure of the information herein does not convey a license or any other right, by implication or otherwise, in any patent, trademark, or other intellectual property right of IDT. IDT products may contain errata which can affect product performance to a minor or immaterial degree. Current characterized errata will be made available upon request. Items identified herein as "reserved" or "undefined" are reserved for future definition. IDT does not assume responsibility for conflicts or incompatibilities arising from the future definition of such items. IDT products have not been designed, tested, or manufactured for use in, and thus are not warranted for, applications where the failure, malfunction, or any inaccuracy in the application carries a risk of death, serious bodily injury, or damage to tangible property. Code examples provided herein by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of such code examples shall be at the user's sole risk.

Copyright  $^{\odot}$  2012 Integrated Device Technology, Inc. All Rights Reserved.

The IDT logo is registered to Integrated Device Technology, Inc. IDT and CPS are trademarks of Integrated Device Technology, Inc.

# Contents

| 1. | Sigr        | nals and Package                     |  |  |  |  |

|----|-------------|--------------------------------------|--|--|--|--|

|    | 1.1         | Pinlist                              |  |  |  |  |

|    | 1.2         | Signals                              |  |  |  |  |

|    | 1.3         | Package Characteristics              |  |  |  |  |

|    | 1.4         | Thermal Characteristics              |  |  |  |  |

| 2. | Elec        | trical Characteristics               |  |  |  |  |

|    | 2.1         | Absolute Maximum Ratings             |  |  |  |  |

|    | 2.2         | Recommended Operating Conditions     |  |  |  |  |

|    | 2.3         | Power                                |  |  |  |  |

|    | 2.4         | Electrical Characteristics           |  |  |  |  |

| 3. | Lay         | Layout Guidelines                    |  |  |  |  |

|    | 3.1         | Overview                             |  |  |  |  |

|    | 3.2         | Impedance Requirements               |  |  |  |  |

|    | 3.3         | Tracking Topologies                  |  |  |  |  |

|    | 3.4         | Power Distribution                   |  |  |  |  |

|    | 3.5         | Decoupling Requirements              |  |  |  |  |

|    | 3.6         | Clocking and Reset                   |  |  |  |  |

|    | 3.7         | Modeling and Simulation              |  |  |  |  |

|    | 3.8         | Testing and Debugging Considerations |  |  |  |  |

|    | 3.9         | Reflow Profile                       |  |  |  |  |

| Α. | Cloc        | cking                                |  |  |  |  |

|    | A.1         | Line Rate Support                    |  |  |  |  |

|    | A.2         | P_CLK Programming                    |  |  |  |  |

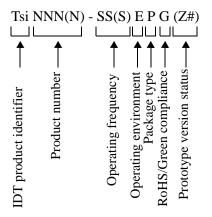

| В. | Ord         | ering Information                    |  |  |  |  |

|    | <b>B</b> .1 | Ordering Information                 |  |  |  |  |

|    | B.2         | Part Numbering Information           |  |  |  |  |

# **About this Document**

This section discusses general document information about the Tsi572. The following topics are described:

- "Scope" on page 5

- "Document Conventions" on page 5

- "Revision History" on page 6

# Scope

The *Tsi572 Hardware Manual* discusses electrical, physical, and board layout information for the Tsi572. It is intended for hardware engineers who are designing system interconnect applications with these devices.

# **Document Conventions**

This document uses a variety of conventions to establish consistency and to help you quickly locate information of interest. These conventions are briefly discussed in the following sections.

#### **Non-differential Signal Notation**

Non-differential signals are either active-low or active-high. An active-low signal has an active state of logic 0 (or the lower voltage level), and is denoted by a lowercase "b". An active-high signal has an active state of logic 1 (or the higher voltage level), and is not denoted by a special character. The following table illustrates the non-differential signal naming convention.

| State       | Single-line signal | Multi-line signal |

|-------------|--------------------|-------------------|

| Active low  | NAME_b             | NAMEn[3]          |

| Active high | NAME               | NAME[3]           |

#### **Differential Signal Notation**

Differential signals consist of pairs of complement positive and negative signals that are measured at the same time to determine a signal's active or inactive state (they are denoted by "\_p" and "\_n", respectively). The following table illustrates the differential signal naming convention.

| State    | Single-line signal       | Multi-line signal                |

|----------|--------------------------|----------------------------------|

| Inactive | NAME_p = 0<br>NAME_n = 1 | NAME_p[3] = 0<br>NAME_n[3] =1    |

| Active   | NAME_p = 1<br>NAME_n = 0 | NAME_p[3] is 1<br>NAME_n[3] is 0 |

#### **Symbols**

This symbol indicates a basic design concept or information considered helpful.

This symbol indicates important configuration information or suggestions.

This symbol indicates procedures or operating levels that may result in misuse or damage to the device.

# **Revision History**

#### May 18, 2012, Formal

- Updated the first paragraph in "Power Sequencing" on page 33

- Changed the SP\_IO\_SPEED setting in Table 21 for 125 MHz / 1.25 Baud rate to 1,1

#### November 18, 2010, Formal

• Added a note to Table 13

#### August 2009, Formal

This is the current release of the *Serial RapidIO Switch*. There have been no technical changes to the document; the formatting has been updated to reflect IDT.

#### June 2009, Formal

Changes have been implemented throughout the document.

Serial RapidIO Switch May 18, 2012

#### July 2008, Advance

The changes to this documents includes adding industrial variants of the device to "Ordering Information" on page 87.

#### June 2008, Advance

This was the first version of the Serial RapidIO Switch.

# 1. Signals and Package

This chapter describes the packaging (mechanical) features for the Tsi572. It includes the following information:

- "Pinlist" on page 9

- "Signals" on page 10

- "Package Characteristics" on page 24

- "Thermal Characteristics" on page 27

# 1.1 Pinlist

The pinlist and ballmap information for the Tsi572 are available by visiting www.idt.com. For more information, see the following documents:

- Tsi572 Pinlist

- Tsi572 Ballmap

9

10

# 1.2 Signals

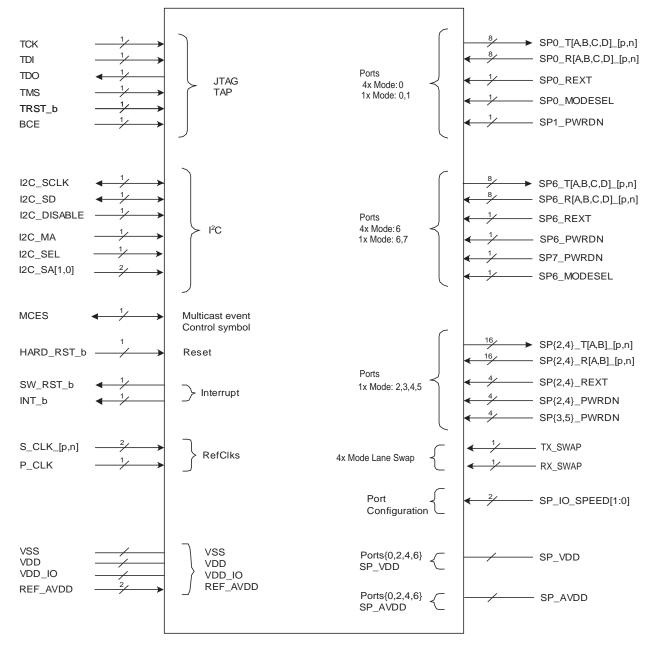

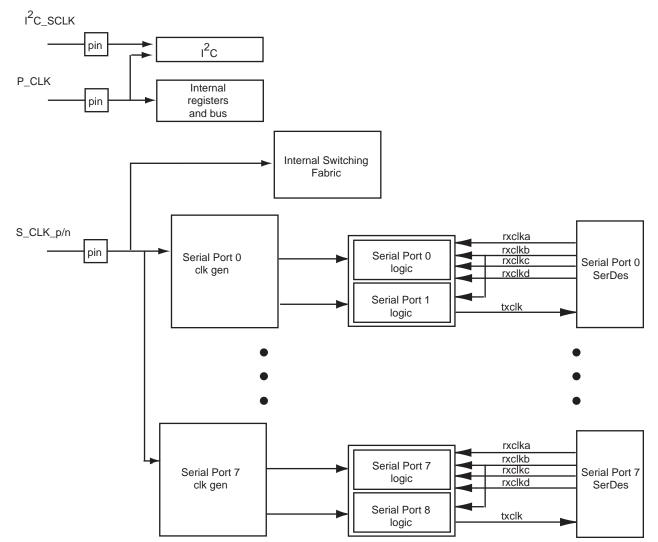

#### Figure 1: Signal Grouping

### 1.2.1 Conventions

The following conventions are used in the signal description table:

- Signals with the suffix "\_p" are the positive half of a differential pair.

- Signals with the suffix "\_n" are the negative half of a differential pair.

- Signals with the suffix "\_b" are active low.

Signals are classified according to the types defined in Table 1.

#### Table 1: Signal Types

| Pin Type    | Definition                                                                                   |

|-------------|----------------------------------------------------------------------------------------------|

| 1           | Input                                                                                        |

| 0           | Output                                                                                       |

| I/O         | Input/Output                                                                                 |

| OD          | Open Drain                                                                                   |

| SRIO        | Differential driver/receiver defined by RapidIO<br>Interconnect Specification (Revision 1.3) |

| PU          | Pulled Up internal to the Tsi572                                                             |

| PD          | Pulled Down internal to the Tsi572                                                           |

| LVTTL       | CMOS I/O with LVTTL thresholds                                                               |

| Hyst        | Hysteresis                                                                                   |

| Core Power  | Core supply                                                                                  |

| Core Ground | Ground for core logic                                                                        |

| I/O Power   | I/O supply                                                                                   |

| N/C         | No connect<br>These signals must be left unconnected.                                        |

## 1.2.2 Endian Ordering

This document follows the bit-numbering convention adopted by *RapidIO Interconnect Specification (Revision 1.3)*, where [0:7] is used to represent an 8 bit bus with bit 0 as the most-significant bit.

### 1.2.3 Port Numbering

The following table shows the mapping between port numbers and the physical ports. These port numbers are used within the destination ID lookup tables for ingress RapidIO ports and in numerous register configuration fields.

#### **Table 2: Port Numbering**

| Port Number | RapidIO Port        | Mode     |

|-------------|---------------------|----------|

| 0           | Serial Port 0 (SP0) | 1x or 4x |

| 1           | Serial Port 1 (SP1) | 1x       |

| 2           | Serial Port 2 (SP2) | 1x       |

| 3           | Serial Port 3 (SP3) | 1x       |

| 4           | Serial Port 4 (SP4) | 1x       |

| 5           | Serial Port 5 (SP5) | 1x       |

| 6           | Serial Port 6 (SP6) | 1x or 4x |

| 7           | Serial Port 7 (SP7) | 1x       |

## 1.2.4 Signal Grouping

The following table lists the signals by group and their recommended termination.

| Pin Name                                | Туре    | Description                                                                                                                                                | Recommended<br>Termination <sup>a</sup> |  |  |  |

|-----------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|

| Signal Port Numbering<br>n = 0, 2, 4, 6 |         |                                                                                                                                                            |                                         |  |  |  |

| Serial Port Transmit                    |         |                                                                                                                                                            |                                         |  |  |  |

| SP{n}_TA_p                              | O, SRIO | Port n Lane A Differential Non-inverting Transmit<br>Data output (4x mode)<br>Port n Lane A Differential Non-inverting Transmit<br>Data output (1x mode)   | No termination required.                |  |  |  |

| SP{n}_TA_n                              | O, SRIO | Port n Lane A Differential Inverting Transmit Data<br>output (4x mode)<br>Port n Lane A Differential Inverting Transmit Data<br>output (1x mode)           | No termination required.                |  |  |  |

| SP{n}_TB_p                              | O, SRIO | Port n Lane B Differential Non-inverting Transmit<br>Data output (4x mode)<br>Port n+1 Lane B Differential Non-inverting<br>Transmit Data output (1x mode) | No termination required.                |  |  |  |

| SP{n}_TB_n                              | O, SRIO | Port n Lane B Differential Inverting Transmit Data<br>output (4x mode)<br>Port n+1 Lane B Differential Inverting Transmit<br>Data output (1x mode)         | No termination required.                |  |  |  |

| SP[0,6]_TC_p                            | O, SRIO | Port n Lane C Differential Non-inverting Transmit<br>Data output (4x mode)                                                                                 | No termination required.                |  |  |  |

| SP[0,6]_TC_n                            | O, SRIO | Port n Lane C Differential Inverting Transmit Data output(4x mode)                                                                                         | No termination required.                |  |  |  |

| SP[0,6]_TD_p                            | O, SRIO | Port n Lane D Differential Non-inverting Transmit<br>Data output (4x mode)                                                                                 | No termination required.                |  |  |  |

| SP[0,6]TD_                              | O, SRIO | Port n Lane D Differential Inverting Transmit Data output (4x mode)                                                                                        | No termination required.                |  |  |  |

14

| Pin Name            | Туре    | Description                                                                                                                                            | Recommended<br>Termination <sup>a</sup>  |

|---------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Serial Port Receive |         |                                                                                                                                                        |                                          |

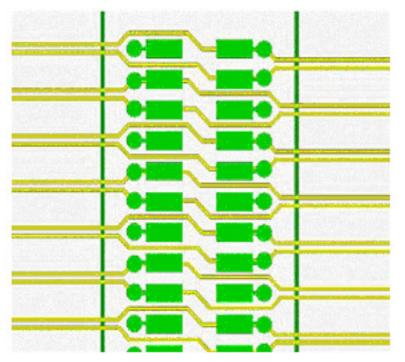

| SP{n}_RA_p          | I, SRIO | Port n Lane A Differential Non-inverting Receive<br>Data input (4x node)<br>Port n Lane A Differential Non-inverting Receive<br>Data input (1x mode)   | DC blocking capacitor of 0.1uF in series |

| SP{n}_RA_n          | I, SRIO | Port n Lane A Differential Inverting Receive Data<br>input (4x mode)<br>Port n Lane A Differential Inverting Receive Data<br>input (1x mode)           | DC blocking capacitor of 0.1uF in series |

| SP{n}_RB_p          | I, SRIO | Port n Lane B Differential Non-inverting Receive<br>Data input (4x mode)<br>Port n+1 Lane B Differential Non-inverting<br>Receive Data input (1x mode) | DC blocking capacitor of 0.1uF in series |

| SP{n}_RB_n          | I, SRIO | Port n Lane B Differential Inverting Receive Data<br>input (4x mode)<br>Port n+1 Lane B Differential Inverting Receive<br>Data input (1x mode)         | DC blocking capacitor of 0.1uF in series |

| SP[0,6]_RC_p        | I, SRIO | Port n Lane C Differential Non-inverting Receive Data input(4x mode)                                                                                   | DC blocking capacitor of 0.1uF in series |

| SP[0,6]_RC_n        | I, SRIO | Port n Lane C Differential Inverting Receive Data input (4x mode)                                                                                      | DC blocking capacitor of 0.1uF in series |

| SP[0,6]_RD_p        | I, SRIO | Port n Lane D Differential Non-inverting Receive<br>Data input(4x mode)                                                                                | DC blocking capacitor of 0.1uF in series |

| SP[0,6]_RD_n        | I, SRIO | Port n Lane D Differential Inverting Receive Data input (4x mode)                                                                                      | DC blocking capacitor of 0.1uF in series |

| Pin Name                  | Туре                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Recommended<br>Termination <sup>a</sup>                                                                                                                                                  |  |  |  |

|---------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Serial Port Configuration | Serial Port Configuration |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                          |  |  |  |

| SP{n}_REXT                | Analog                    | Used to connect a resistor to VSS to provide a reference current for the driver and equalization circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Must be connected to VSS<br>with a 191-ohm (1%)<br>resistor.                                                                                                                             |  |  |  |

| SP{n}_MODESEL             | I/O,<br>LVTTL,<br>PD      | Selects the serial port operating mode for ports<br>Oand 6<br>0 = Port 0 or 6 operating in 4x mode<br>1 = Ports n and n+1 operating in 1x mode<br>Note: Output capability of this pin is only used in<br>test mode.<br>Must remain stable for 10 P_CLK cycles after<br>HW_RST_b is de-asserted in order to be sampled<br>correctly.<br>This signal is ignored after reset.                                                                                                                                                                                                                                                                                              | Pin must be tied off<br>according to the required<br>configuration. Either a 10K<br>pull up to VDD_IO or a<br>10K pull-down to VSS_IO.<br>Internal pull-down may be<br>used for logic 0. |  |  |  |

| SP{n}_PWRDN               | I/O,<br>LVTTL,<br>PU      | Port n Transmit and Receive Power Down control<br>This signal controls the state of Port n and Port<br>n+1<br>The PWRDN controls the state of all four lanes<br>(A/B/C/D) of SERDES Macro.<br>0 = Port n Powered Up. Port n+1 controlled by<br>SP{n+1}_PWRDN.<br>1 = Port n Powered Down. Port n+1 Powered<br>Down.<br>Override SP{n}_PWRDN using PWDN_x1 field in<br>"SRIO MAC x Clock Selection Register" in the<br><i>Tsi572 User Manual</i> .<br>Output capability of this pin is only used in test<br>mode.<br>Must remain stable for 10 P_CLK cycles after<br>HW_RST_B is de-asserted in order to be sampled<br>correctly.<br>This signal is ignored after reset. | Pin must be tied off<br>according to the required<br>configuration. Either a 10K<br>pull up to VDD_IO or a<br>10K pull-down to VSS_IO.<br>Internal pull-up may be<br>used for logic 1.   |  |  |  |

| Pin Name      | Туре                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Recommended<br>Termination <sup>a</sup>                                                                                                                                                |

|---------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SP{n+1}_PWRDN | I/O,<br>LVTTL,<br>PU | Port n+1 Transmit and Receive Power Down<br>control<br>This signal controls the state of Port n+1. Note<br>that Port n+1 is never used when 4x mode is<br>selected for a Serial Rapid IO MAC, and it must<br>be powered down.<br>0 = Port n+1 Powered Up<br>1 = Port n+1 Powered Down<br>Override SP{n+1}_PWRDN using PWDN_x4 field<br>SRIO MAC x Clock Selection Register.<br>Output capability of this pin is only used in test<br>mode.<br>Must remain stable for 10 P_CLK cycles after<br>HW_RST_B is de-asserted in order to be sampled<br>correctly.<br>This signal is ignored after reset. | Pin must be tied off<br>according to the required<br>configuration. Either a 10K<br>pull up to VDD_IO or a<br>10K pull-down to VSS_IO.<br>Internal pull-up may be<br>used for logic 1. |

| Pin Name                 | Туре                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Recommended<br>Termination <sup>a</sup>                                                                                                                                                  |  |  |  |

|--------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Serial Port Speed Select | Serial Port Speed Select |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                          |  |  |  |

| SP_IO_SPEED[1]           | I/O,<br>LVTTL,<br>PU     | Serial Port Transmit and Receive operating<br>frequency select, bit 1. When combined with<br>SP_IO_SPEED[0], this pin selects the default<br>serial port frequency for all ports.<br>00 = 1.25 Gbit/s<br>01 = 2.5 Gbit/s<br>10 = 3.125 Gbit/s (default)<br>11 = Illegal<br>Selects the speed at which the ports operates<br>when reset is removed. This could be at either<br>HARD_RST_b being de-asserted or by the<br>completion of a self-reset.<br>These signals must remain stable for 10 P_CLK<br>cycles after HW_RST_b is de-asserted in order to<br>be sampled correctly.<br>These signals are ignored after reset and<br>software is able to over-ride the port frequency<br>setting in the SRIO MAC x Digital Loopback and<br>Clock Selection register.<br>The SP_IO_SPEED[1:0] setting is equal to the<br>IO_SPEED field in SRIO MAC x Clock Selection<br>Register.<br>Output capability of this pin is only used in test<br>mode. | Pin must be tied off<br>according to the required<br>configuration. Either a 10K<br>pull-up to VDD_IO or a<br>10K pull-down to VSS_IO.<br>Internal pull-down may be<br>used for logic 0. |  |  |  |

| SP_IO_SPEED[0]           | I/O,<br>LVTTL,<br>PD     | See SP_IO_SPEED[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Pin must be tied off<br>according to the required<br>configuration. Either a 10K<br>pull-up to VDD_IO or a<br>10K pull-down to VSS_IO.<br>Internal pull-up may be<br>used for logic 1.   |  |  |  |

18

| Pin Name                  | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Recommended<br>Termination <sup>a</sup>                                                                                                                                                                                                    |  |

|---------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Serial Port Lane Ordering | Select          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                            |  |

| SP_RX_SWAP                | I, LVTTL,<br>PD | Configures the order of 4x receive lanes on serial<br>ports [0,6]<br>0 = A, B, C, D<br>1 = D, C, B, A<br>This signal is ignored in 1X mode.<br>Must remain stable for 10 P_CLK cycles after<br>HARD_RST_b is de-asserted in order to be<br>sampled correctly.<br>This signal is ignored after reset.<br>Note: Ports that require the use of lane swapping<br>for ease of routing will only function as 4x mode<br>ports. The re-configuration of a swapped port to<br>dual 1x mode operation results in the inability to<br>connect to a 1x mode link partner. | No termination required.<br>Internal pull-down can be<br>used for logic 0. Pull up to<br>VDD_IO through 10K if<br>external pull-up is desired.<br>Pull down to VSS_IO<br>through a 10K resistor if an<br>external pull-down is<br>desired. |  |

| SP_TX_SWAP                | I, LVTTL,<br>PD | Configures the order of 4x transmit lanes on serial<br>ports [0,6].<br>0 = A, B, C, D<br>1 = D, C, B, A<br>Must remain stable for 10 P_CLK cycles after<br>HARD_RST_b is de-asserted in order to be<br>sampled correctly.<br>This signal is ignored after reset.<br>Note: Ports that require the use of lane swapping for<br>ease of routing only function as 4x mode ports. The<br>re-configuration of a swapped port to dual 1x mode<br>operation results in the inability to connect to a 1x<br>mode link partner.                                          | No termination required.<br>Internal pull-down can be<br>used for logic 0. Pull up to<br>VDD_IO through 10K if<br>external pull-up is desired.<br>Pull down to VSS_IO<br>through 10K resistor if an<br>external pull-down is<br>desired.   |  |

| Clock and Reset           |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                            |  |

| P_CLK                     | I,<br>LVTTL     | This clock is used for the register bus clock.<br>The nominal frequency of this input clock is<br>100 MHz. For more information on programming<br>the P_CLK operating frequency, refer to "P_CLK<br>Programming" on page 75.                                                                                                                                                                                                                                                                                                                                   | No termination required.                                                                                                                                                                                                                   |  |

#### Table 3: Signal Descriptions and Recommended Termination

| Pin Name   | Туре                    | Description                                                                                                                                                                | Recommended<br>Termination <sup>a</sup>                                    |

|------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

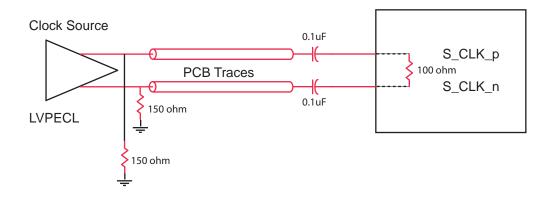

| S_CLK_p    | I,<br>CML               | Differential non-inverting reference clock. The<br>clock is used for following purposes: SERDES<br>reference clock, serial port system clock, ISF<br>clock and test clock. | AC coupling capacitor of 0.1uF required.                                   |

|            |                         | The maximum frequency of this input clock is 156.25 MHz.                                                                                                                   |                                                                            |

|            |                         | The clock frequency is defined in "Reference Clock, S_CLK_p/n" on page 35.                                                                                                 |                                                                            |

|            |                         | For more information on the S_CLK operating frequency, refer to "Line Rate Support" on page 71.                                                                            |                                                                            |

| S_CLK_n    | I,<br>CML               | Differential inverting reference clock. The clock is<br>used for following purposes: SerDes reference<br>clock, serial port system clock, ISF clock and test<br>clock.     | AC coupling capacitor of 0.1uF required.                                   |

|            |                         | The maximum frequency of this input clock is 156.25 MHz.                                                                                                                   |                                                                            |

|            |                         | The clock frequency is defined in "Reference Clock, S_CLK_p/n" on page 35.                                                                                                 |                                                                            |

|            |                         | For more information on the S_CLK operating frequency, refer to "Line Rate Support" on page 71.                                                                            |                                                                            |

| HARD_RST_b | I<br>LVTTL,             | Schmidt-triggered hard reset. Asynchronous active low reset for the entire device.                                                                                         | Connect to a power-up reset source.                                        |

|            | Hyst,<br>PU             | The Tsi572 does not contain a voltage detector to generate internal reset.                                                                                                 | Refer to "Reset<br>Requirements" on page 64                                |

| Interrupts |                         |                                                                                                                                                                            |                                                                            |

| INT_b      | O, OD,<br>LVTTL,<br>2mA | Interrupt signal (open drain output)                                                                                                                                       | External pull-up required.<br>Pull up to VDD_IO through<br>a 10K resistor. |

| Pin Name         | Туре                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Recommended<br>Termination <sup>a</sup>                                                                                                                                     |

|------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW_RST_b         | O, OD,<br>LVTTL,<br>2mA         | Software reset (open drain output): This signal is<br>asserted when a RapidIO port receives a valid<br>reset request on a RapidIO link. If self-reset is not<br>selected, this pin remains asserted until the reset<br>request is cleared from the status registers. If<br>self-reset is selected, this pin remains asserted<br>until the self reset is complete. If the Tsi572 is<br>reset from the HARD_RST_b pin, this pin is<br>de-asserted and remains de-asserted after<br>HARD_RST_b is released.<br>For more information, refer to "Resets" in the<br>Tsi572 User's Manual. | External pull-up required.<br>Pull up to VDD_IO through<br>a 10K resistor.                                                                                                  |

| Multicast        |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                             |

| MCES             | I/O,<br>LVTTL,<br>PD            | Multicast Event Symbol pin.<br>As an input, an edge (rising or falling) will trigger a<br>Multicast Event Control Symbol will be sent to all<br>ports;<br>As an output, this pin will toggle its value every<br>time an Multicast Event Control Symbol is<br>received by any port which is enabled for<br>Multicast even control symbols.<br>Must remain stable for 10 P_CLK cycles <i>before</i><br><i>and after</i> a transition.                                                                                                                                                 | No termination required.<br>This pin must not be driven<br>by an external source until<br>all power supply rails are<br>stable.                                             |

| l <sup>2</sup> C |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                             |

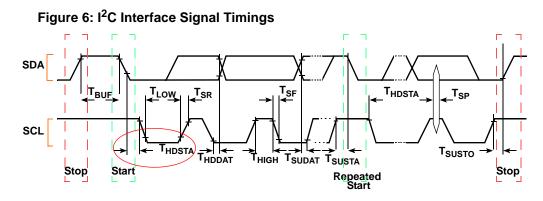

| I2C_SCLK         | I/O, OD,<br>LVTTL,<br>PU<br>8mA | $I^2C$ input/output clock, up to 100 kHz.<br>If an EEPROM is present on the $I^2C$ bus, this<br>clock signal must be connected to the clock input<br>of the serial EEPROM on the $I^2C$ bus. If an<br>EEPROM is not present, the recommended<br>terminations should be used.                                                                                                                                                                                                                                                                                                        | No termination required.<br>Internal pull-up may be<br>used for logic 1.<br>Pull up to VDD_IO through<br>a minimum 470 ohms<br>resistor if higher edge rate<br>is required. |

| I2C_SD           | I/O, OD,<br>LVTTL,<br>PU<br>8mA | I <sup>2</sup> C input and output data bus (bidirectional open drain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No termination required.<br>Internal pull-up may be<br>used for logic 1.<br>Pull up to VDD_IO through<br>a minimum 470 ohms<br>resistor if higher edge rate<br>required.    |

| Pin Name    | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Recommended<br>Termination <sup>a</sup>                                                                                                                                                                          |

|-------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I2C_DISABLE | I, LVTTL,<br>PD | Disable I <sup>2</sup> C register loading after reset. When<br>asserted, the Tsi572 does not attempt to load<br>register values from I <sup>2</sup> C.<br>0 = Enable I <sup>2</sup> C register loading<br>1 = Disable I <sup>2</sup> C register loading<br>Must remain stable for 10 P_CLK cycles after<br>HARD_RST_b is de-asserted in order to be<br>sampled correctly.<br>Note: This signal does not control the slave<br>accessibility of the interface.<br>This signal is ignored after reset. | No termination required.<br>Pull up to VDD_IO through<br>a 10K resistor if I <sup>2</sup> C<br>loading is not required.                                                                                          |

| I2C_MA      | I, CMOS,<br>PU  | <ul> <li>I<sup>2</sup>C Multibyte Address.</li> <li>When driven high, I<sup>2</sup>C module will expect<br/>multi-byte peripheral addressing; otherwise, when<br/>driven low, single-byte peripheral address is<br/>assumed.</li> <li>Must remain stable for 10 P_CLK cycles after<br/>HW_RST_b is de-asserted in order to be sampled<br/>correctly.</li> <li>This signal is ignored after reset.</li> </ul>                                                                                        | No termination required.<br>Internal pull-up may be<br>used for logic 1.<br>Pull up to VDD_IO through<br>10K resistor if an external<br>pull-up is desired. Pull<br>down to VSS_IO to<br>change the logic state. |

| I2C_SA[1,0] | I, CMOS,<br>PU  | I <sup>2</sup> C Slave Address pins.<br>The values on these two pins represent the<br>values for the lower 2 bits of the 7-bit address of<br>Tsi572 when acting as an I <sup>2</sup> C slave (see I <sup>2</sup> C Slave<br>Configuration register).<br>The values at these pins can be overridden by<br>software after reset.                                                                                                                                                                      | No termination required.<br>Internal pull-up may be<br>used for logic 1.<br>Pull up to VDD_IO through<br>10K resistor if an external<br>pull-up is desired. Pull<br>down to VSS_IO to<br>change the logic state. |

| Pin Name            | Туре                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Recommended<br>Termination <sup>a</sup>                                                                           |

|---------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| I2C_SEL             | I, CMOS,<br>PU      | <ul> <li>DS, I<sup>2</sup>C Pin Select. Together with the I2C_SA[1,0] pins, Tsi572 will determine the lower 2 bits of the 7-bit address of the EEPROM address it boots from.</li> <li>When asserted, the I2C_SA[1,0] values will also be used as the lower 2 bits of the EEPROM address.</li> <li>When de-asserted, the I2C_SA[1,0] pins will be ignored and the lower 2 bits of the EEPROM address are default to 00.</li> <li>The values of the lower 2 bits of the EEPROM address can be over-ridden by software after reset.</li> </ul> |                                                                                                                   |

| JTAG TAP Controller |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                   |

| тск                 | I, LVTTL,<br>PD     | IEEE 1149.1 Test Access Port Clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Pull up to VDD_IO through 10K resistor if not used.                                                               |

| TDI                 | I, LVTTL,<br>PU     | IEEE 1149.1 Test Access Port Serial Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pull up to VDD_IO through<br>a 10K resistor if the signal<br>is not used or a if higher<br>edge rate is required. |

| TDO                 | O,<br>LVTTL,<br>2mA | IEEE 1149.1 Test Access Port Serial Data Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | No connect if JTAG is not<br>used.<br>Pull up to VDD_IO through<br>a 10K resistor if used.                        |

| TMS                 | I, LVTTL,<br>PU     | IEEE 1149.1 Test Access Port Test Mode Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pull up to VDD_IO through a 10K resistor if not used.                                                             |

| TRST_b              | I, LVTTL,<br>PU     | IEEE 1149.1 Test Access Port TAP Reset Input<br>This input must be asserted during the assertion<br>of HARD-RST_b. Afterwards, it may be left in<br>either state.<br>Combine the HARD_RST_b and TRST_b signals<br>with an AND gate and use the output to drive the<br>TRST_b pin.                                                                                                                                                                                                                                                           | Tie to VSS_IO through a 10K resistor if not used.                                                                 |

| Pin Name       | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                    | Recommended<br>Termination <sup>a</sup>                                                     |  |

|----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| BCE            | I, LVTTL,<br>PU | Boundary Scan compatibility enabled pin. This<br>input is used to aid 1149.6 testing.<br>This signal also enables system level diagnostic<br>capability using features built into the SerDes. For<br>more information on this functionality, refer to the<br>Serial RapidIO Signal Analyzer documentation.<br>This signal must be tied to VDD_IO during normal<br>operation of the device, and during JTAG<br>accesses of the device registers | <ul><li>or The default setting is to be pulled-up.</li><li>Pulling the signal low</li></ul> |  |

| Power Supplies | -               |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |  |

| SP_AVDD        | -               | Port n and n+1: 3.3V supply for bias generator circuitry. This is required to be a low-noise supply.                                                                                                                                                                                                                                                                                                                                           | Refer to ""Decoupling<br>Requirements" on<br>page 57"                                       |  |

| REF_AVDD       | -               | Analog 1.2V for Reference Clock (S_CLK_p/n).<br>Clock distribution network power supply.                                                                                                                                                                                                                                                                                                                                                       | Refer to ""Decoupling<br>Requirements" on<br>page 57"                                       |  |

| Common Supply  |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |  |

| VDD_IO         | -               | Common 3.3V supply for LVTTL I/O                                                                                                                                                                                                                                                                                                                                                                                                               | Refer to ""Decoupling<br>Requirements" on<br>page 57"                                       |  |

| VSS            | -               | Common ground supply for digital logic                                                                                                                                                                                                                                                                                                                                                                                                         | Refer to ""Decoupling<br>Requirements" on<br>page 57"                                       |  |

| VDD            | -               | Common 1.2V supply for digital logic                                                                                                                                                                                                                                                                                                                                                                                                           | Refer to ""Decoupling<br>Requirements" on<br>page 57"                                       |  |

| SP_VDD         | -               | 1.2V supply for CDR, Tx/Rx, and digital logic for all RapidIO ports                                                                                                                                                                                                                                                                                                                                                                            | Refer to ""Decoupling<br>Requirements" on<br>page 57"                                       |  |

a. Signals for unused serial ports do not require termination and can be left as N/Cs.

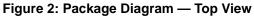

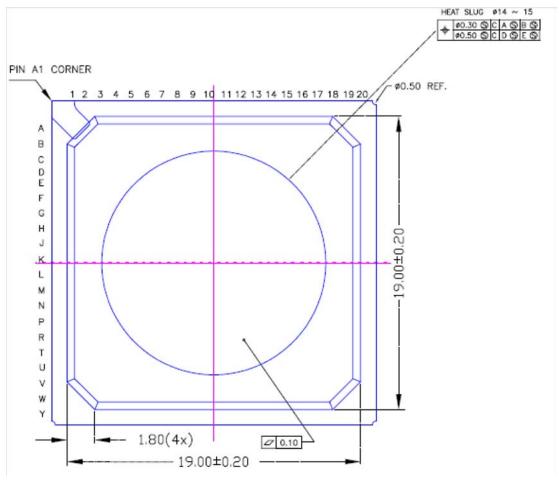

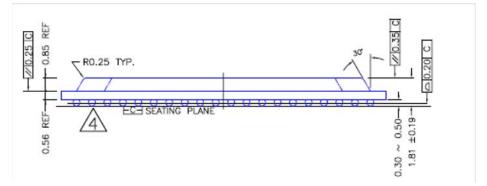

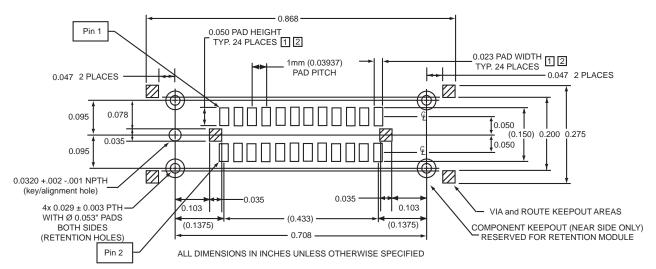

# **1.3 Package Characteristics**

The Tsi572's package characteristics are summarized in the following table. The following figures show the top, side, and bottom views of the Tsi572 package.

#### **Table 4: Package Characteristics**

| Feature                    | Description                       |

|----------------------------|-----------------------------------|

| Package Type               | Heat Slug Ball Grid Array (HSBGA) |

| Package Body Size          | 21 mm x 21 mm                     |

| JEDEC Specification        | 95-1 Section 14                   |

| Pitch                      | 1.00 mm                           |

| Ball pad size              | 500 um                            |

| Soldermask opening         | 400 um                            |

| Moisture Sensitivity Level | 3                                 |

# RENESAS

Figure 3: Package Diagram — Side View

21.00

Figure 4: Package Diagram — Bottom View

□ 0.20(4X)

Α

в

C

D

Ε

F G

н

J

к

L

М

N

Ρ

R

т

U

W

Y

RENESAS

# **1.4 Thermal Characteristics**

Heat generated by the packaged IC has to be removed from the package to ensure that the IC is maintained within its functional and maximum design temperature limits. If heat buildup becomes excessive, the IC temperature may exceed the temperature limits. A consequence of this is that the IC may fail to meet the performance specifications and the reliability objectives may be affected.

Failure mechanisms and failure rate of a device have an exponential dependence of the IC operating temperatures. Thus, the control of the package temperature, and by extension the Junction Temperature, is essential to ensure product reliability. The Tsi572 is specified safe for operation when the Junction Temperature is within the recommended limits.

Table 5 shows the simulated Theta jb and Theta jc thermal characteristics of the Tsi572 HSBGA package.

| Interface                    | Result      |

|------------------------------|-------------|

| Theta jb (junction to board) | 9.2 °C/watt |

| Theta jc (junction to case)  | 4.7 °C/watt |

#### **Table 5: Thermal Characteristics**

## 1.4.1 Junction-to-Ambient Thermal Characteristics (Theta ja)

The following table shows the simulated Theta ja thermal characteristic of the Tsi572 HSBGA package. The results in the table are based on a JEDEC Thermal Test Board configuration (JESD51-9) and do not factor in system level characteristics. As such, these values are for reference only.

The Theta ja thermal resistance characteristics of a package depend on multiple system level variables.

#### **Table 6: Simulated Junction to Ambient Characteristics**

|              | Theta ja at specified airflow (no Heat Sink) |              |              |  |

|--------------|----------------------------------------------|--------------|--------------|--|

| Package      | 0 m/s 1 m/s 2 m/s                            |              |              |  |

| Tsi572 HSBGA | 13.0 C/watt                                  | 12.0 °C/watt | 11.4 °C/watt |  |

RENESAS

#### 1.4.1.1 System-level Characteristics

In an application, the following system-level characteristics and environmental issues must be taken into account:

- Package mounting (vertical / horizontal)

- System airflow conditions (laminar / turbulent)

- Heat sink design and thermal characteristics

- Heat sink attachment method

- PWB size, layer count and conductor thickness

- Influence of the heat dissipating components assembled on the PWB (neighboring effects)

#### Example on Thermal Data Usage

Based on the Theta<sub>JA</sub> data and specified conditions, the following formula can be used to derive the junction temperature (Tj) of the Tsi572 with a 0m/s airflow:

•  $Tj = \hat{e}_{JA} * P + Tamb.$

Where: Tj is Junction Temperature, P is the Power consumption, Tamb is the Ambient Temperature

Assuming a power consumption (P) of 3 W and an ambient temperature (Tamb) of 70°C, the resulting junction temperature (Tj) would be 109°C.

# 2. Electrical Characteristics

This chapter provides the electrical characteristics for the Tsi572. It includes the following information:

- "Absolute Maximum Ratings" on page 29

- "Recommended Operating Conditions" on page 30

- "Power" on page 31

# 2.1 Absolute Maximum Ratings

Operating the device beyond the listed operating conditions is not recommended. Stressing the Tsi572 beyond the Absolute Maximum Rating can cause permanent damage.

Table 7 lists the absolute maximum ratings.

| Symbol                               | Parameter                                 | Min  | Мах    | Unit |

|--------------------------------------|-------------------------------------------|------|--------|------|

| T <sub>storage</sub>                 | Storage Temperature                       | -55  | 125    | °C   |

| V <sub>DD_IO</sub>                   | 3.3 V DC Supply Voltage                   | -0.5 | 4.6    | V    |

| SP_AVDD                              | 3.3 V Analog Supply Voltage               | -0.5 | 4.6    | V    |

| V <sub>DD,</sub> SP_VDD,<br>REF_AVDD | 1.2 V DC Supply Voltage                   | -0.3 | 1.7    | V    |

| $V_{I\_SP\{n\}-R\{A-D\}_{p,n\}}}$    | SERDES Port Receiver Input Voltage        | -0.3 | 3      | V    |

| $V_{O_SP\{n\}-T\{A-D\}_{p,n\}}}$     | SERDES Port VM Transmitter Output Voltage | -0.3 | 3      | V    |

| SP_AVDD                              | Transient di/dt                           | -    | 0.0917 | A/nS |

| SP_VDD                               | Transient di/dt                           | -    | 0.136  | A/nS |

#### **Table 7: Absolute Maximum Ratings**

#### **Table 7: Absolute Maximum Ratings**

| Symbol               | Parameter                                                                                                                           | Min  | Мах                     | Unit |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------|------|

| V <sub>O_LVTTL</sub> | LVTTL Output or I/O Voltage                                                                                                         | -0.5 | V <sub>DD_IO</sub> +0.5 | V    |

| V <sub>ESD_HBM</sub> | Maximum ESD Voltage Discharge Tolerance<br>for Human Body Model (HBM). [Test<br>Conditions per JEDEC standard -<br>JESD22-A114-B]   | -    | 2000                    | V    |

| V <sub>ESD_CDM</sub> | Maximum ESD Voltage Discharge Tolerance<br>for Charged Device Model (CDM). Test<br>Conditions per JEDEC standard -<br>JESD22-C101-A | -    | 500                     | V    |

# 2.2 Recommended Operating Conditions

Table 8 lists the recommended operating conditions.

Continued exposure of IDT's devices to the maximum limits of the specified junction temperature could affect the device reliability. Subjecting the devices to temperatures beyond the maximum/minimum limits could result in a permanent failure of the device.

| Symbol                               | Parameter                                  | Min  | Max  | Unit |

|--------------------------------------|--------------------------------------------|------|------|------|

| Тj                                   | Junction temperature                       | -40  | 125° | °C   |

| V <sub>DD_IO</sub>                   | 3.3 V DC Supply Voltage                    | 2.97 | 3.63 | V    |

| SP_AVDD                              | 3.3 V Analog Supply Voltage                | 2.97 | 3.63 | V    |

| V <sub>DD</sub> ,SP_VDD,<br>REF_AVDD | 1.2 V DC Supply Voltage                    | 1.14 | 1.29 | V    |

| I <sub>VDD_IO</sub>                  | 3.3 V IO Supply Current <sup>a</sup>       | -    | 15   | mA   |

| I <sub>SP_VDD</sub>                  | SerDes Digital Supply Current <sup>a</sup> | -    | 482  | mA   |

| I <sub>SP_AVDD</sub>                 | 3.3 V SerDes Supply Current <sup>a</sup>   | -    | 382  | mA   |

| I <sub>VDD</sub>                     | 1.2 V Core Supply Current <sup>a</sup>     | -    | 1176 | mA   |

| I <sub>REF_AVDD</sub>                | 1.2 V Ref Clock Supply Current             | -    | 12.5 | mA   |

#### **Table 8: Recommended Operating Conditions**

| Symbol               | Parameter                                                           | Min | Max | Unit             |

|----------------------|---------------------------------------------------------------------|-----|-----|------------------|

| V <sub>ripple1</sub> | Power Supply ripple for Voltage Supplies:<br>SP_VDD, VDD and VDD_IO | -   | 100 | mV <sub>pp</sub> |

| V <sub>ripple2</sub> | Power Supply ripple for Voltage Supplies:<br>SP{n}_AVDD, REF_AVDD   | -   | 50  | mV <sub>pp</sub> |

| I <sub>REXT</sub>    | External reference resistor current                                 | -   | 10  | uA               |

#### **Table 8: Recommended Operating Conditions**

a. The current values provided are maximum values and dependent on device configuration, such as port usage, traffic, etc.

# 2.3 Power

The following sections describe the Tsi572's power dissipation and power sequencing.

### 2.3.1 **Power Dissipation**

The Tsi572's power dissipation values are dependent on device configuration, such as line rate, port configuration, and traffic.

The following tables show the power in both 1x and 4x mode configurations in 125°C ambient temperature, typical process and voltage conditions.

| Line Rate                      | 1.25GBaud | 2.5GBaud | 3.125GBaud | Notes    |

|--------------------------------|-----------|----------|------------|----------|

| VDD_CORE                       | 0.67      | 1.00     | 1.15       | 2,9      |

| SP_VDD                         | 0.39      | 0.40     | 0.49       | 3        |

| SP_AVDD                        | 0.80      | 0.93     | 1.05       | 4        |

| VDD_IO                         | 0.01      | 0.01     | 0.01       | 5        |

|                                |           |          |            |          |

| Total Power Consumption<br>(W) | 1.88      | 2.33     | 2.70       | 1,6,7, 8 |

#### Notes

- 1. Voltage, temperature and process are all nominal

- 2. VDD\_CORE supplies the ISF and other internal digital logic

- 3. SP\_VDD supplies the digital portion of the Serial RapidIO SerDes

- 4. SPn\_AVDD supplies the analog portion of the Serial RapidIO SerDes

- 5. VDD\_IO supplies power for all non-Serial RapidIO I/O

- 6. Total power is independent of Serial RapidIO distance travelled due to Voltage Mode Driver technology used for Serial RapidIO I/O

- 7. Slight power variations must expected across different applications

- 8. Power is provided for fully utilized Serial RapidIO lanes

- 9. Core power reduces by approximately 10% under light traffic conditions

| Line Rate                      | 1.25GBaud | 2.5GBaud | 3.125GBaud | Notes    |

|--------------------------------|-----------|----------|------------|----------|

| VDD_CORE                       | 0.70      | 1.03     | 1.21       | 2,9      |

| SP_VDD                         | 0.40      | 0.37     | 0.45       | 3        |

| SP_AVDD                        | 0.77      | 0.85     | 0.96       | 4        |

| VDD_IO                         | 0.01      | 0.01     | 0.01       | 5        |

|                                |           |          |            |          |

| Total Power Consumption<br>(W) | 1.87      | 2.26     | 2.62       | 1,6,7, 8 |

#### Table 10: Power Consumption for Eight Links in 1x Mode

#### **Notes**

- 1. Voltage, temperature and process are all nominal

- 2. VDD\_CORE supplies the ISF and other internal digital logic

- 3. SP\_VDD supplies the digital portion of the Serial RapidIO SerDes

- 4. SPn\_AVDD supplies the analog portion of the Serial RapidIO SerDes

- 5. VDD\_IO supplies power for all non-Serial RapidIO I/O

- 6. Total power is independent of Serial RapidIO distance travelled due to Voltage Mode Driver technology used for Serial RapidIO I/O

- 7. Slight power variations must expected across different applications

- 8. Power is provided for fully utilized Serial RapidIO lanes

- 9. Core power reduces by approximately 10% under light traffic conditions

#### 2.3.2 Power Sequencing

Power-up option pins that are controlled by a logic device, in addition to all clocks, must not be driven until all power supply rails to the Tsi572 are stable. External devices also must not be permitted to sink current from, or source current to, the device because of the risk of triggering ESD protection or causing a latch-up condition.

The Tsi572 must have the supplies powered-up in the following order:

- VDD (1.2 V) must be powered up first

- SP\_VDD (1.2 V) and REF\_AVDD (1.2 V) should power up at approximately the same time as VDD

- Delays between the powering up of VDD, SP\_VDD, and REF\_AVDD are acceptable.

- No more than 50ms after VDD is at a valid level, VDD\_IO (3.3 V) should be powered up to a valid level

- VDD\_IO (3.3V) must not power up before VDD (1.2 V)

- SP\_AVDD (3.3V) should power up at approximately the same time as VDD\_IO

- Delays between powering up VDD\_IO and SP\_AVDD are acceptable

- SP\_AVDD must not power up before SP\_VDD

It is recommended that there is no more than 50ms between ramping of the 1.2 V and 3.3 V supplies. The power supply ramp rates must be kept between 10 V/s and 1x10E6 V/s to minimize power current spikes during power up.

If it is necessary to sequence the power supplies in a different order than that recommended above, the following precaution must be taken:

• Any power-up option pins must be current limited with 10 K ohms to VDD\_IO or VSS\_IO as required to set the desired logic level.

#### 2.3.2.1 Power-down

Power down is the reverse sequence of power up:

- VDD\_IO (3.3V) and SP\_AVDD

- VDD (1.2V), SP\_VDD and REF\_AVDD power-down at the same time

- Or all rails falling simultaneously

Integrated Device Technology www.idt.com

# 2.4 Electrical Characteristics

This section describes the AC and DC signal characteristics for the Tsi572.

# 2.4.1 SerDes Receiver (SP{n}\_RD\_p/n)

Table 11 lists the electrical characteristics for the SerDes Receiver in the Tsi572.

Serial RapidIO signals may be presented to the receiver differential inputs while the switch is in an un-powered state only if a return current path (VSS) is present between the Tsi572 and the source of the signal. For example, this situation can occur if the Tsi572 is located on an AMC card that has been inserted into an active uTCA chassis and the slot power has been left in the off state.

#### **Table 11: SerDes Receiver Electrical Characteristics**

| Symbol                           | Parameter                              | Min | Тур | Max  | Unit | Notes                                                                 |

|----------------------------------|----------------------------------------|-----|-----|------|------|-----------------------------------------------------------------------|

| Z <sub>DI</sub>                  | RX Differential Input impedance        | 90  | 100 | 110  | Ohm  | -                                                                     |

| V <sub>DIFFI</sub>               | RX Differential Input<br>Voltage       | 170 | -   | 1600 | mV   | -                                                                     |

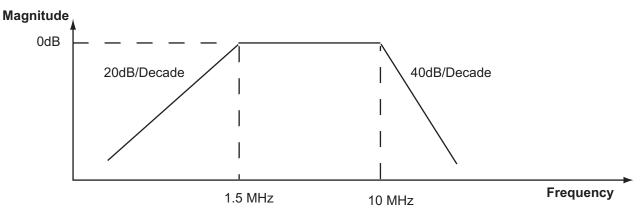

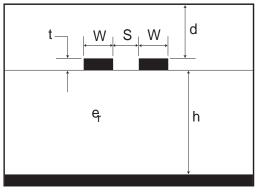

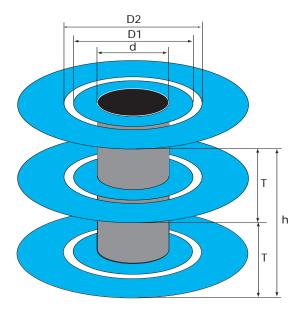

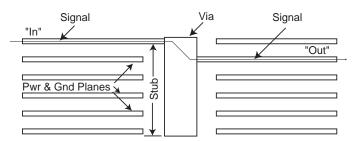

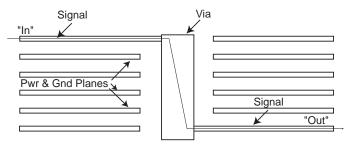

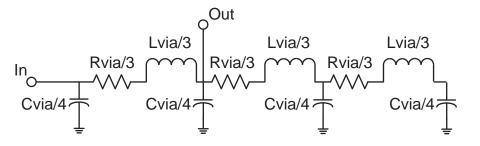

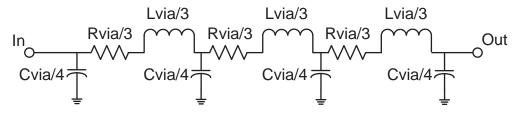

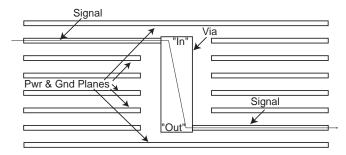

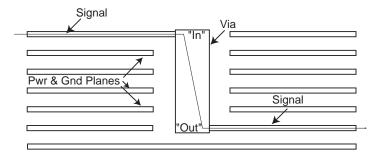

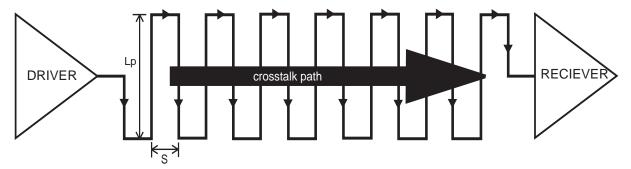

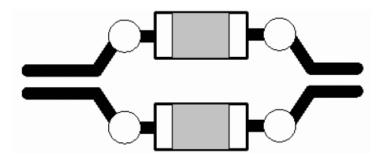

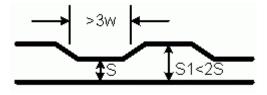

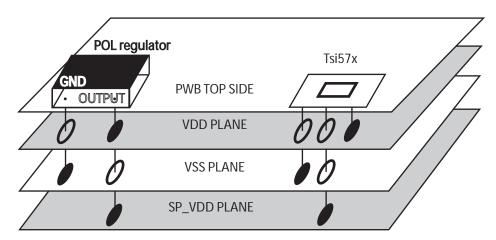

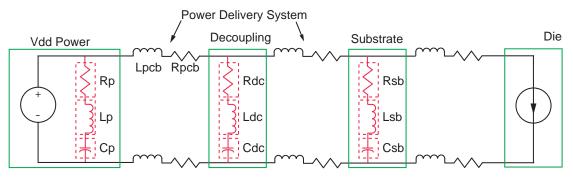

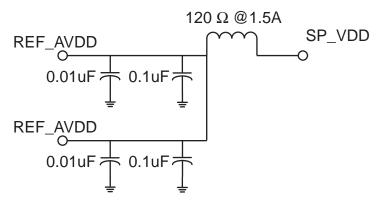

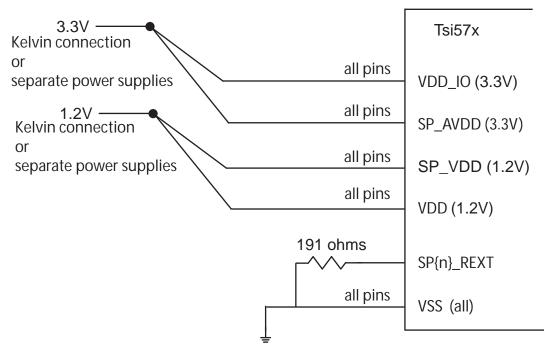

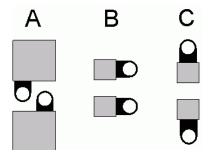

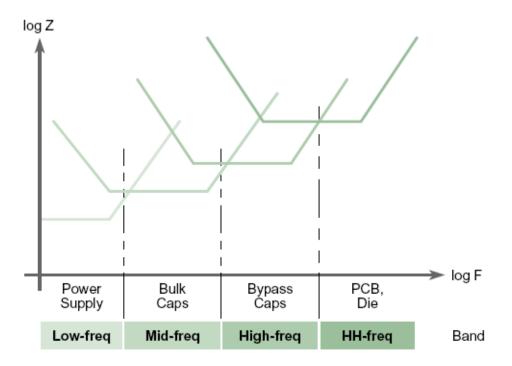

| L <sub>CR</sub>                  | RX Common Mode<br>Return Loss          | -   | -   | 6    | dB   | Over a range 100MHz to 0.8* Baud<br>Frequency                         |