## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

## Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## RENESAS

## USER'S MANUAL

# μPD78098 SUB-SERIES

## **8-BIT SINGLE-CHIP MICROCOMPUTER**

μPD78094 μPD78095 μPD78096 μPD78098A μPD78P098A

Document No. IEU-1381A (O. D. No. IEU-854A) Date Published March 1995 P Printed in Japan

© NEC Corporation 1993

## 1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to Vob or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

## **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

FIP is a trademark of NEC Corporation. IEBus and Inter Equipment Bus are trademarks of NEC Corporation. MS-DOS and Windows are trademarks of Microsoft Corporation. PC/AT and PC DOS are trademarks of IBM Corporation. HP9000 Series 300 and HP-UX are trademarks of Hewlett-Packard Company. SPARCstation is a trademark of SPARC International, Inc. Sun OS is a trademark of Sun Microsystems, Inc.

## Major Revisions in This Edition (1/2)

| Page       | Contents                                                                            |

|------------|-------------------------------------------------------------------------------------|

| Throughout | μPD78P098 was erased from Corresponding Products                                    |

|            | μPD78098A, 78P098A were added to Corresponding Products                             |

|            | $\mu$ PD78094, 78095, 78096: Under development $\rightarrow$ Development completed  |

| P. 24      | The recommended connecting method of unused pins P130/ANO0 and P131/ANO1 was        |

|            | changed                                                                             |

| P. 21, 79  | Cautions for use of pins P130/ANO0 and P131/ ANO1 were added                        |

| P. 80      | 4.3 Port Function Control Registers was revised                                     |

| P. 81      | Table 4-3 Port Mode Register and Output Latch Settings when Using Dual Function     |

|            | was added                                                                           |

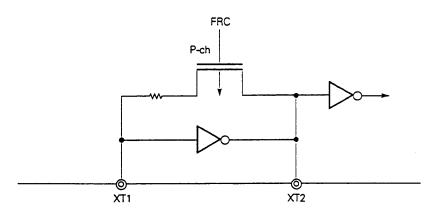

| P. 92      | Fig. 5-3 Subsystem Clock Feedback Resistor was added                                |

| P. 94      | Cautions were added to Fig. 5-5 Oscillation Mode Selection Register Format          |

| P. 105     | Cautions were added to 5.6.2 System clock and CPU clock switching procedure         |

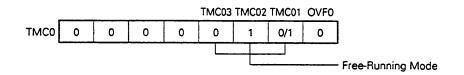

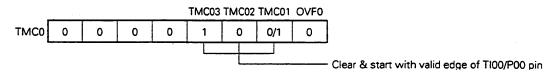

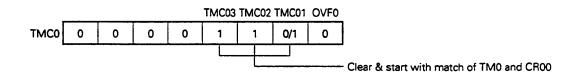

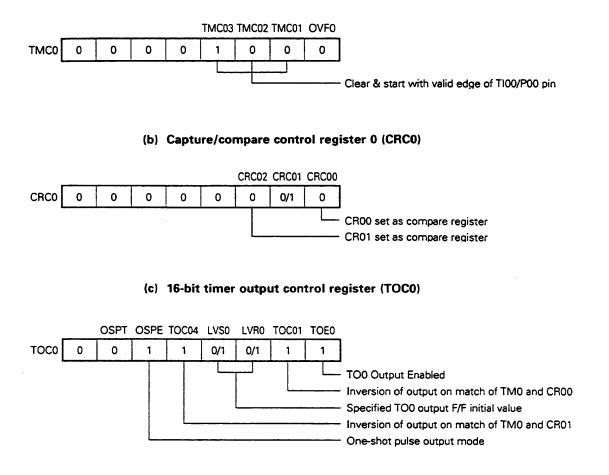

| P. 116     | Cautions were added to 6.3 (2) 16-bit timer mode control register                   |

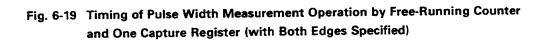

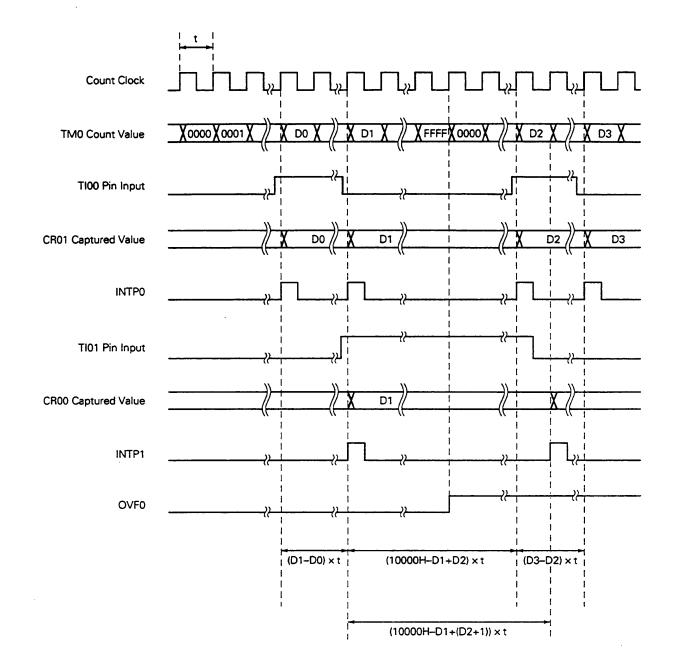

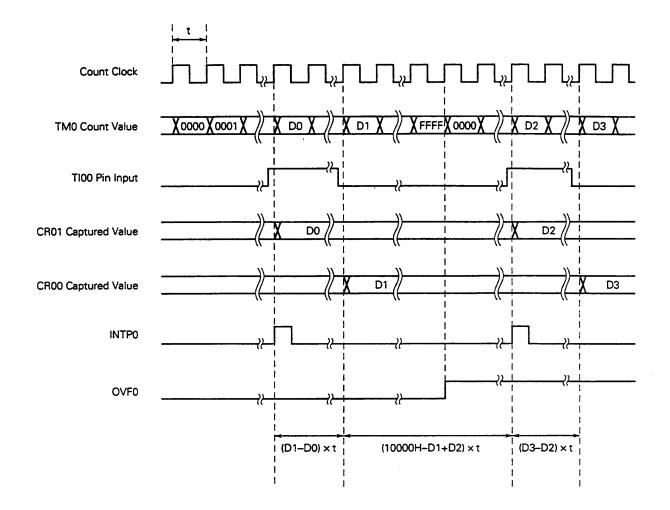

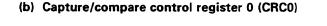

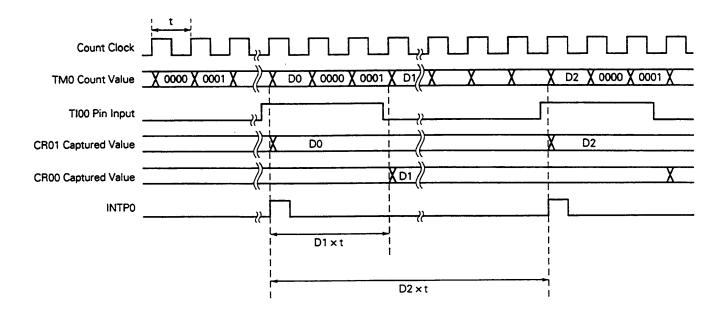

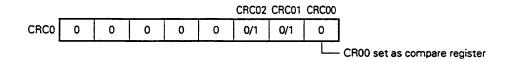

| P. 134     | 6.4.4 (3) Pulse width measurement with free-running counter and two capture         |

|            | registers was revised and cautions were added                                       |

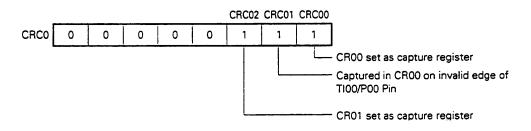

| P. 136     | 6.4.4 (4) Pulse width measurement by means of restart was revised and cautions were |

|            | added                                                                               |

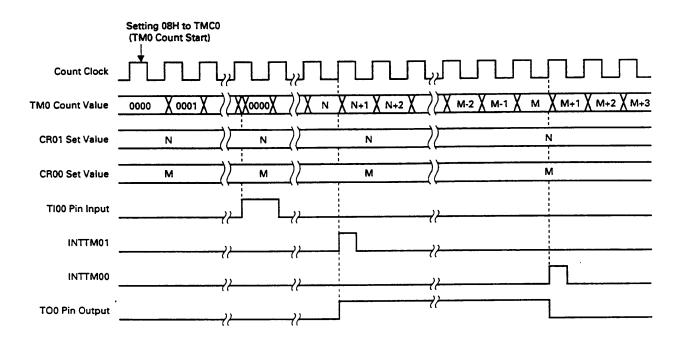

| P. 141     | 6.4.7 (1) One-shot pulse output using software trigger was revised                  |

| P. 143     | Fig. 6-32 Timing of One-Shot Pulse Output Operation Using Software Trigger was      |

|            | changed                                                                             |

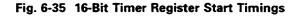

| P. 145     | Fig. 6-34 Timing of One-Shot Pulse Output Operation Using External Trigger (with    |

|            | Rising Edge Specified) was changed                                                  |

| P. 164     | Table 7-7 8-Bit Timer/Event Counter 2 Interval Time was added                       |

| P. 170     | Table 7-10 Square-Wave Output Ranges when 2-Channel 8-Bit Timer/Event Counters      |

| . <u></u>  | (TM1 and TM2) are Used as 16-Bit Timer/Event Counter was added                      |

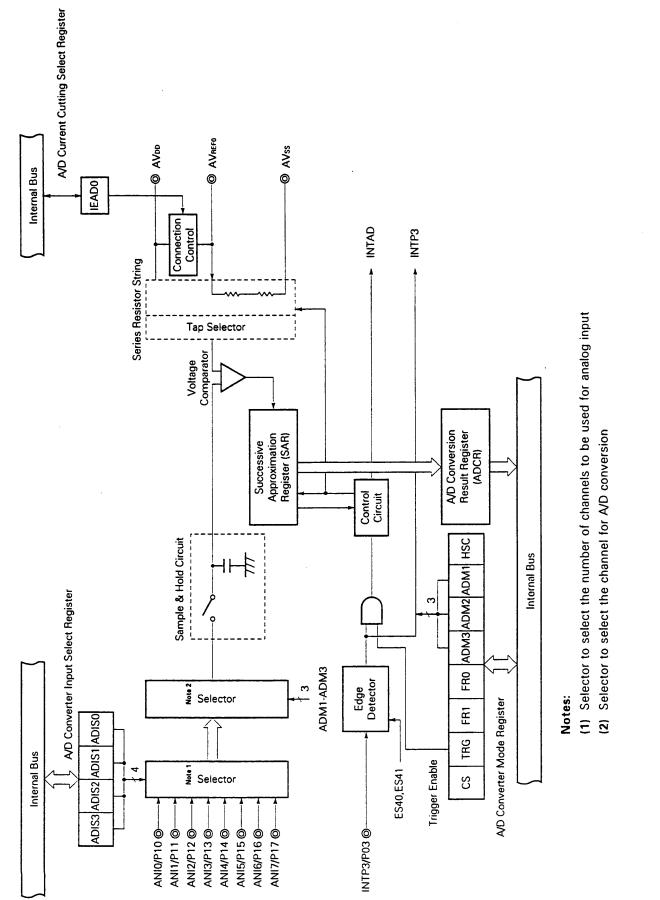

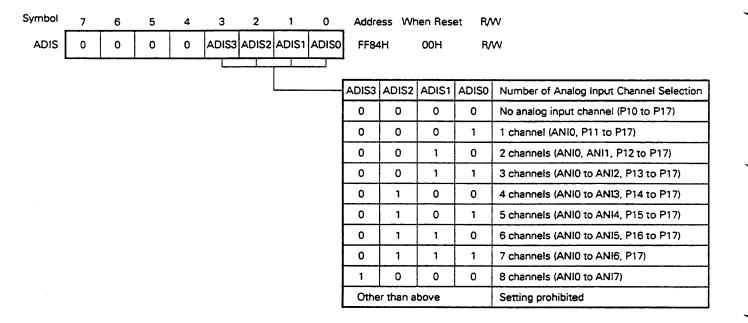

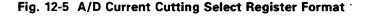

| P. 196     | Fig. 12-1 A/D Converter Block Diagram was changed                                   |

| P. 199     | Fig. 12-2 A/D Converter Mode Register Format was changed                            |

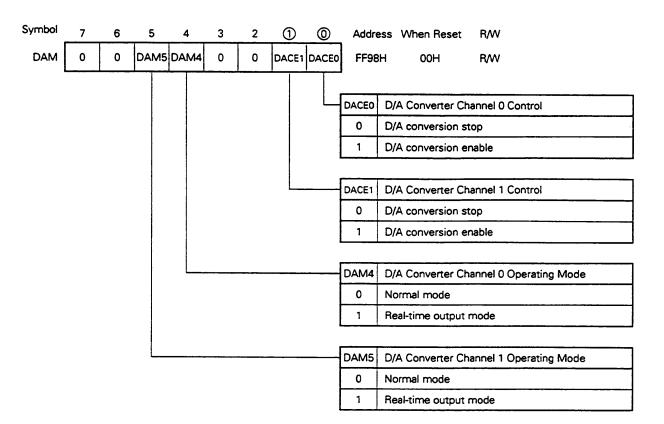

| P. 213     | Cautions were added to 13.1 D/A Converter Functions                                 |

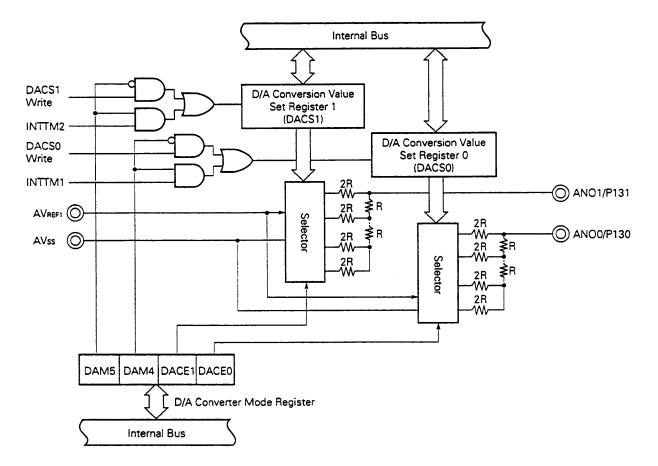

| P. 214     | Fig. 13-1 D/A Converter Block Diagram was changed                                   |

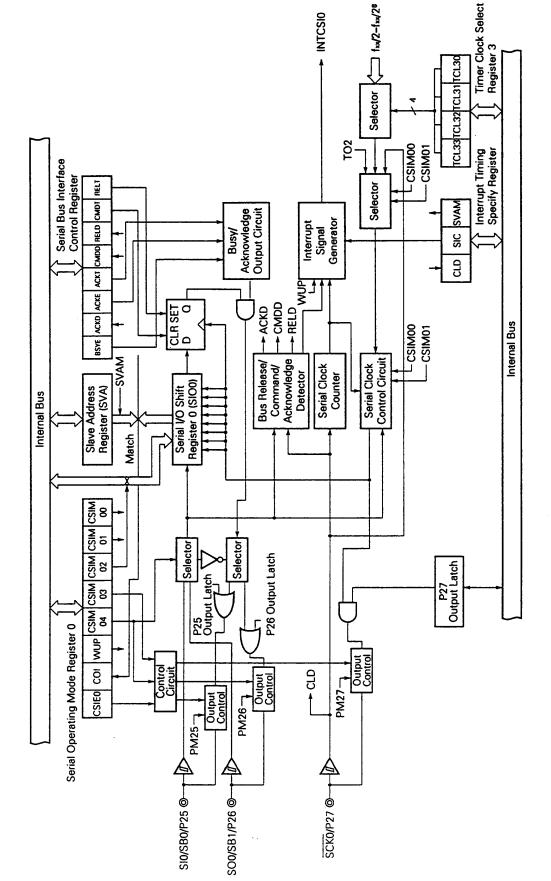

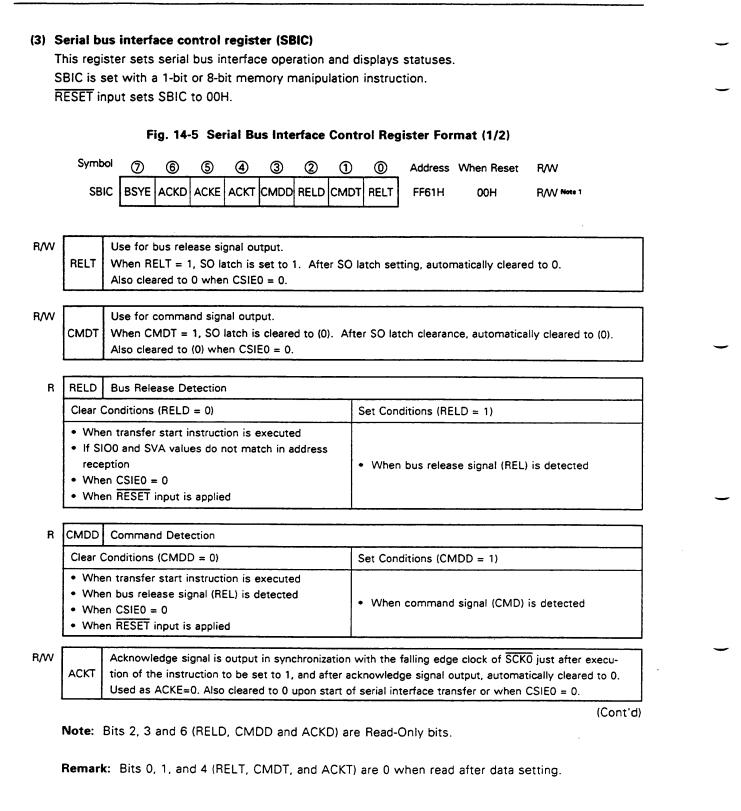

| P. 226     | Fig. 14-4 Serial Operating Mode Register 0 Format was changed                       |

| Page        | Contents                                                                             |

|-------------|--------------------------------------------------------------------------------------|

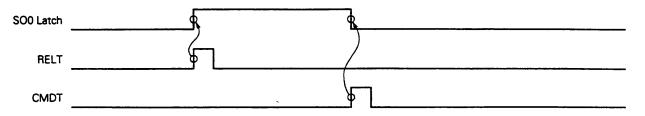

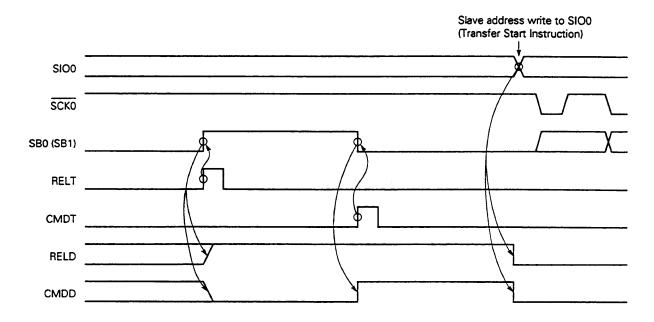

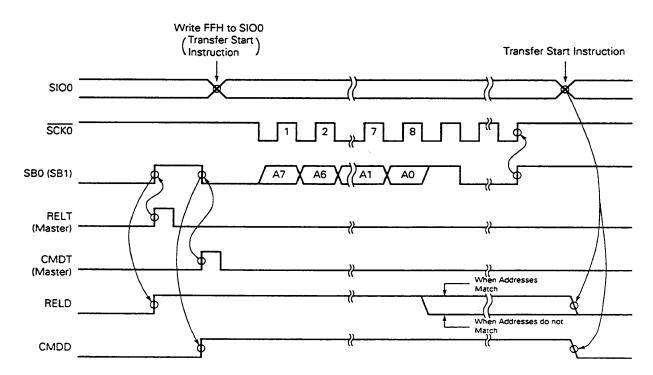

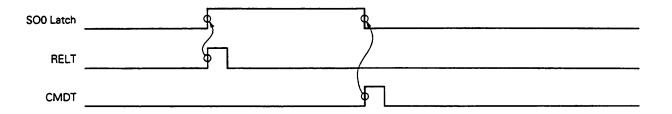

| P. 250      | Fig. 14-21 RELT, CMDT, RELD and CMDD Operations (Slave) was revised                  |

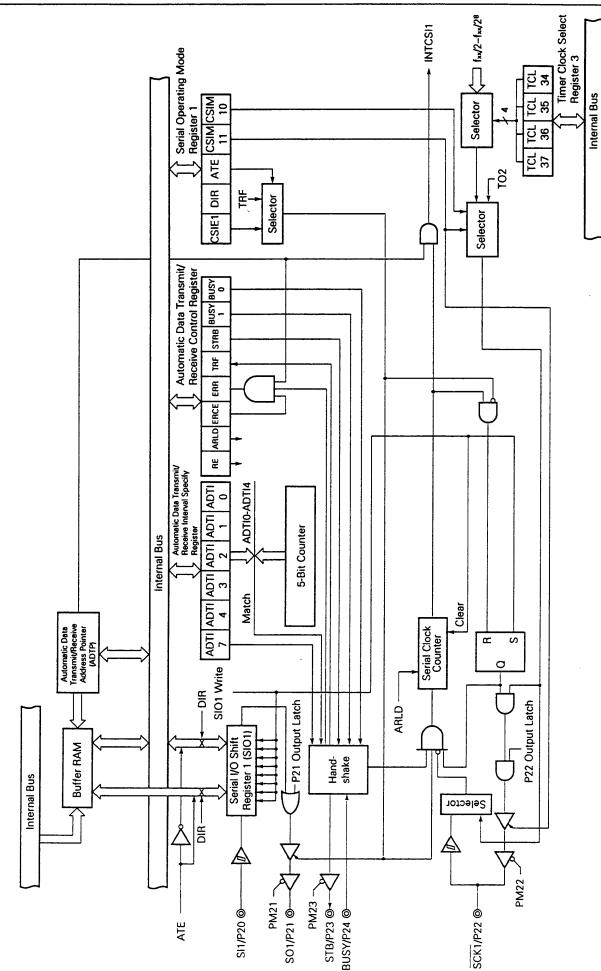

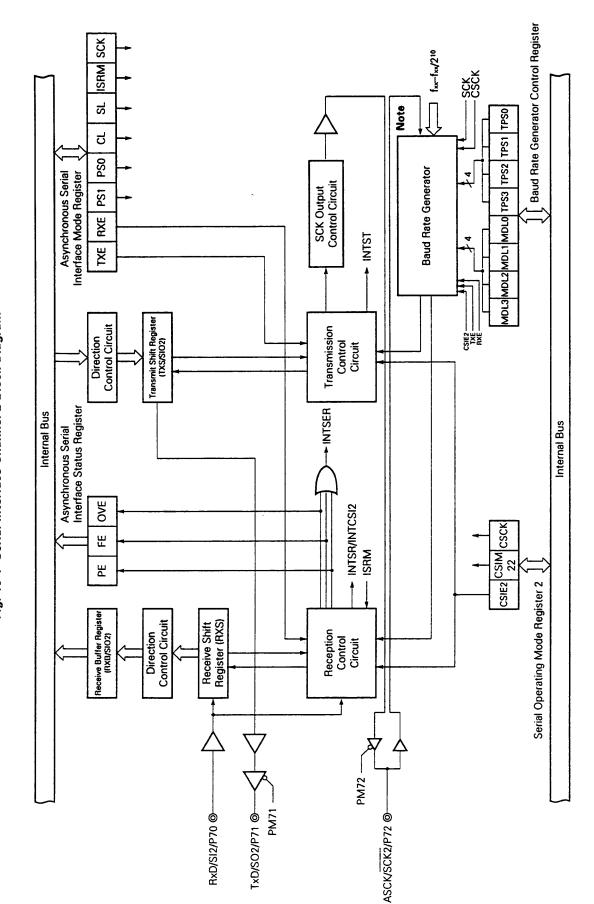

| P. 273      | Fig. 15-1 Serial Interface Channel 1 Block Diagram was revised                       |

| P. 277      | Fig. 15-3 Serial Operation Mode Register 1 Format was changed and Notes were erased  |

| P. 279      | Fig. 15-5 Automatic Data Transmit/Receive Interval Specify Register Format was       |

|             | revised and Notes were erased                                                        |

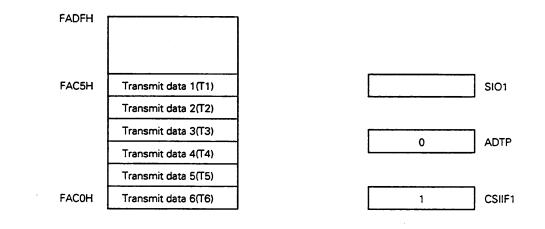

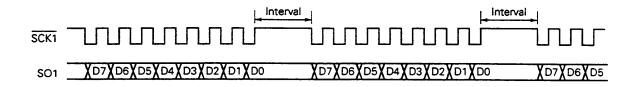

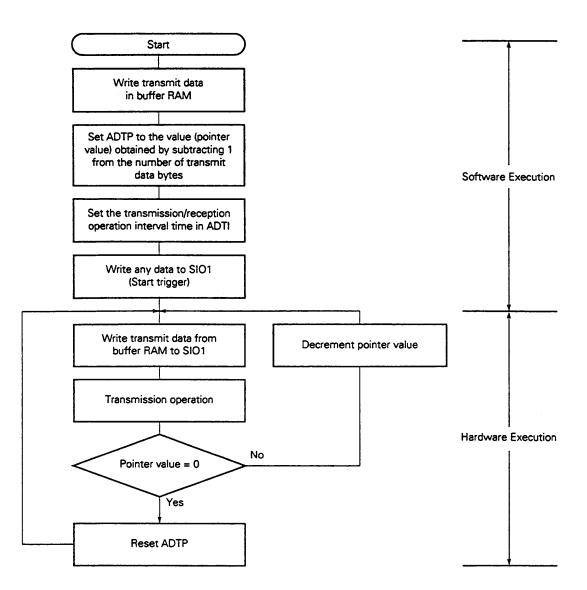

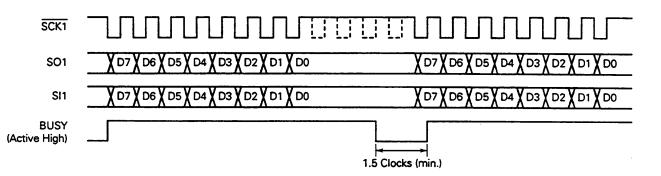

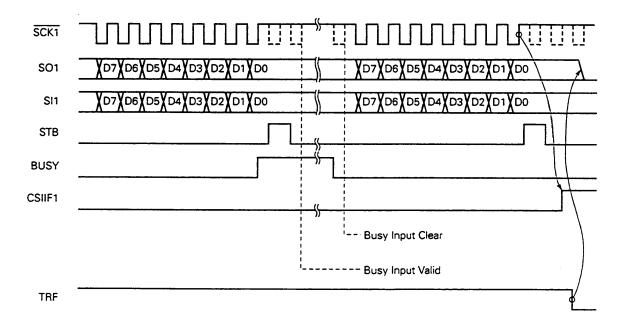

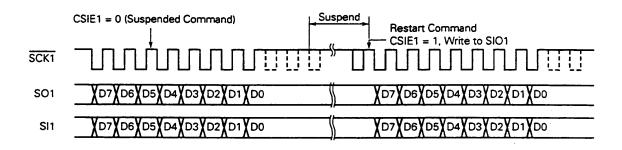

| P. 308      | 15.4.3 (3) (h) Automatic data transmit/receive interval was revised                  |

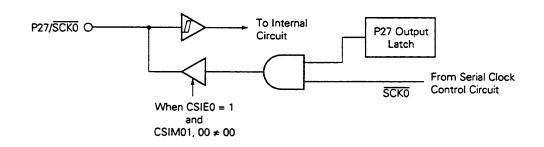

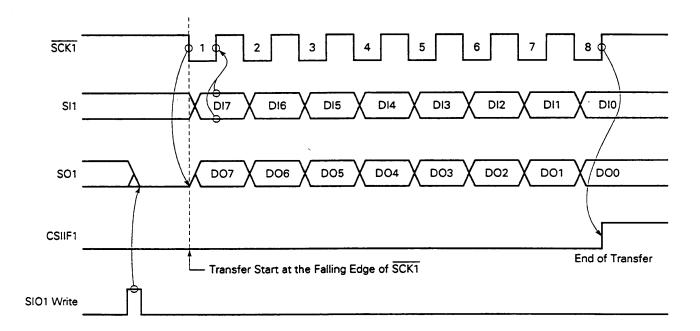

| P. 313      | Fig. 16-1 Serial Interface Channel 2 Block Diagram was revised                       |

| P. 319      | Table 16-2 Serial Interface Channel 2 Operating Mode Settings was revised            |

| P. 347      | CHAPTER 18 INTERRUPT FUNCTIONS AND TEST FUNCTIONS was changed                        |

| P. 401      | Fig. 20-13 IEBus Controller Mode Register Format was revised                         |

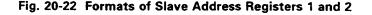

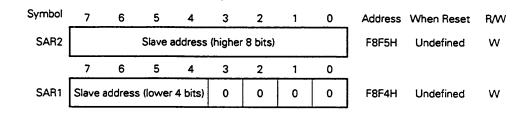

| P. 414      | Fig. 20-23 Formats of Multiaddress Calling Destination Address Registers 1 and 2 was |

|             | changed                                                                              |

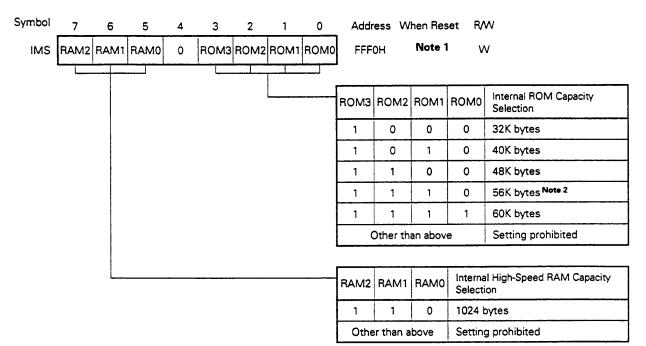

| P. 435      | 23.2 Internal Expansion RAM Size Switching Register was added                        |

| P. 436      | Cautions were added to 23.3 PROM Programming                                         |

| -           | 24.3 Instruction Codes and 24.4 Operation List were erased                           |

| P. 461, 462 | APPENDIX A DEVELOPMENT TOOLS was revised                                             |

|             | IE-78098-R-EM, DF78098: Under development $\rightarrow$ Development completed        |

| P. 467, 468 | APPENDIX B EMBEDDED SOFTWARE was revised                                             |

| -           | APPENDIX C INSTRUCTION INDEX (In Alphabetical Order) was erased                      |

| P. 475      | APPENDIX D REVISION HISTORY was added                                                |

The mark  $\star$  shows revised points.

#### PREFACE

Readers

This manual has been prepared for user engineers who want to understand the functions of the  $\mu$ PD78098 sub-series and design and develop its application systems and programs.

The  $\mu$ PD78P098AKK-T in the  $\mu$ PD78098 sub-series does not provide reliability that satisfies mass production of your application system. Use this model for experiment or function evaluation only.

Purpose This manual is intended for the users to understand the functions described in the Organization below.

**Organization** The  $\mu$ PD78098 sub-series manuals are separated into two manuals; this manual and Instruction manual (common to 78K/0 series).

| 1.000000.00 |                                                                                                                 | 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 - 200 |

|-------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|             |                                                                                                                 |                                                                                                                 |

|             |                                                                                                                 |                                                                                                                 |

| <u>u</u> PD | 78098 sub                                                                                                       | -series                                                                                                         |

|             |                                                                                                                 |                                                                                                                 |

|             |                                                                                                                 |                                                                                                                 |

| 1           | Jser's mar                                                                                                      | Initia                                                                                                          |

|             | 7361 3 Midi                                                                                                     | uai                                                                                                             |

|             | 10 Y 10 Y 10 Y                                                                                                  |                                                                                                                 |

|             | 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - |                                                                                                                 |

- Pin functions

- Internal block function

- Interrupt

- Other on-chip peripheral functions

- CPU function

- Instruction set

- Instruction description

#### How to Read This Manual

Before reading this manual, you must have general knowledge of electric, logic circuits, and microcomputer.

- When you want to understand the functions in general:

- $\rightarrow$  Read this manual in the order of the contents.

- □ How to interpret the register format:

- → For the circled bit number, the bit name is defined as a reserved word in RA78K/0, and in CC78K/0, already defined in the header file named sfrbit.h.

□ When you know the names of registers and want to check the details of these registers:

→ Refer to APPENDIX C REGISTER INDEX.

$\Box$  When you want to know the details of the  $\mu$ PD78098 sub-series instruction functions:

$\rightarrow$  Refer to the separate volume 78K/0 SERIES USER'S MANUAL-INSTRUCTION (IEU-1372).

| Legend | Data representation weight | : | High digits on the left and low digits on the right |

|--------|----------------------------|---|-----------------------------------------------------|

|        | Active low representations | : | 🚃 (top bar over pin or signal name)                 |

|        | Note                       | : | Description of "Note" in the text.                  |

|        | Caution                    | : | Information requiring particular attention          |

|        | Remark                     | : | Additional explanatory material                     |

|        | Numeral representations    | : | Binaryxxxx or xxxxB                                 |

|        |                            |   | Decimalxxxx                                         |

|        |                            |   | HexadecimalxxxxH                                    |

## **RELATED DOCUMENTS**

## • Documents related to devices

| Part number<br>Document name | μPD78094    | μPD78095                               | µPD78096 | μPD78098A | μPD78P098A      |

|------------------------------|-------------|----------------------------------------|----------|-----------|-----------------|

| Preliminary Product          |             | ······································ | _        |           | To be published |

| Information                  |             | soon                                   |          |           |                 |

| Data Sheet Pla               |             |                                        | nned     |           | Planned         |

| User's Manual                | This manual |                                        |          |           |                 |

| User's Manual Instruction    |             |                                        |          |           |                 |

## • Documents related to development tools

| Document name                                                | Document number      |          |

|--------------------------------------------------------------|----------------------|----------|

| RA78K Series Assembler Package                               | Operation            | EEU-1399 |

| User's Manual                                                | Language             | EEU-1404 |

| RA78K Series Structured Assembler Preprocessor User's Manual | £ ,                  | EEU-1402 |

| CC78K Series C Compiler                                      | Operation            | EEU-1280 |

| User's Manual                                                | Language             | EEU-1284 |

| CC78K Series Library Source File User's Manual               | *                    | -        |

| PG-1500 PROM Programmer User's Manual                        | EEU-1335             |          |

| PG-1500 Controller User's Manual                             | EEU-1291             |          |

| IE-78000-R User's Manual                                     |                      | EEU-1398 |

| IE-78000-R-BK User's Manual                                  | EEU-1427             |          |

| IE-78098-R-EM User's Manual                                  | To be published soon |          |

| SD78K/0 Screen Debugger                                      | Introduction         | EEU-1414 |

| User's Manual                                                | Reference            | EEU-1413 |

• Documents related to embedded software

| Document name                                                                            | Document number         |          |

|------------------------------------------------------------------------------------------|-------------------------|----------|

|                                                                                          | Basic                   | -        |

| 78K/0 Series Real-Time OS                                                                | Install                 | -        |

| User's Manual                                                                            | Debugger                | -        |

|                                                                                          | Technical               | -        |

| Fuzzy Inference Development Support System Brochure                                      | -                       |          |

| Fuzzy Knowledge Data Creation Tool User's Manual                                         | EEU-1438                |          |

| 78K/0, 78K/II, 87AD Series<br>Fuzzy Inference Development Support System Translator User | 's Manual               | EEU-1444 |

| 78K/0 Series Fuzzy Inference Development Support System Fu<br>User's Manual              | -                       |          |

| 78K/0 Series Fuzzy Inference Development Support System Fu<br>User's Manual              | izzy Inference Debugger | EEU-1458 |

## • Other documents

| Document name                                                 | Document number |

|---------------------------------------------------------------|-----------------|

| Package Manual                                                | IEI-1213        |

| Semiconductor Device Mounting Technology Manual               | IEI-1207        |

| Quality Grade of NEC Semiconductor Devices                    | IEI-1209        |

| Reliability and Quality Control of NEC Semiconductor Devices  | IEI-1203        |

| Electrostatic Discharge (ESD) Test                            | IEI-1201        |

| Guide to Quality Assurance of Semiconductor Devices           | MEI-1202        |

| Guide to Microcomputer-Related Products - Other Manufacturers | -               |

Caution: The contents of the above documents are subject to change without notice. Be sure to use the latest edition for designing.

## CONTENTS

| <ul> <li>Applications</li> <li>Ordering Information</li> <li>Quality Grade</li> <li>Pin Configuration (Top View)</li> <li>78K/0 Series Development</li> <li>78K/0 Series Development</li> <li>Block Diagram</li> <li>Block Diagram</li> <li>Outline of Function</li> </ul> PTER 2 PIN FUNCTION PTER 2 PIN FUNCTION 2.1 Pin Function List 2.1.1 Normal operating mode pins 2.1.2 PROM programming mode pins (µPD78P098A only) 2.2 Description of Pin Functions 2.2.1 P00 to P07 (Port 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | APTE | R 1 0                      | UTLINE                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------|------------------------------------------------------------|

| 3       Ordering Information         4       Quality Grade         5       Pin Configuration (Top View)         6       78K/0 Series Development         7       Block Diagram         8       Outline of Function         9       PIN FUNCTION         2.1       Pin Function List         2.1.1       Normal operating mode pins         2.1.2       PROM programming mode pins (#PD78P098A only)         2.2       PIO to PO7 (Port 0)         2.2.1       PO0 to PO7 (Port 0)         2.2.2       P10 to P17 (Port 1)         2.2.3       P20 to P27 (Port 2)         2.4       P30 to P37 (Port 3)         2.2.5       P40 to P47 (Port 4)         2.2.6       P50 to P57 (Port 5)         2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 12)         2.2.9       P120 to P127 (Port 12)         2.2.10       P130 and P131 (Port 13)         2.2.11       AVest         2.2.12       AVest         2.2.13       AVest         2.2.14       AVest         2.2.15       RESET         2.2.16       X1 and X2         2.2.13       K2         2.2.                                                                        | 1.1  | Featur                     | 'es                                                        |

| 4       Quality Grade         5       Pin Configuration (Top View)         16       78K/0 Series Development         17       Block Diagram         18       Outline of Function         PTER 2 PIN FUNCTION         21       Pin Function List         2.1.1       Normal operating mode pins         2.1.2       PROM programming mode pins (µPD78P098A only)         2.2       PROM programming mode pins (µPD78P098A only)         2.2       Pto to P07 (Port 0)         2.2.1       P00 to P07 (Port 1)         2.2.3       P20 to P17 (Port 1)         2.2.4       P30 to P37 (Port 3)         2.2.5       P40 to P47 (Port 4)         2.2.6       P50 to P57 (Port 5)         2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P127 (Port 12)         2.10       P130 and P131 (Port 13)         2.2.11       AVREF1         2.2.12       AVreF1         2.2.13       AVoc         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       X11 and XT2         2.2.18       Voc         2.2.19       Vss         <                                                                       | 1.2  | Applic                     | ations                                                     |

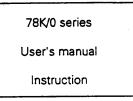

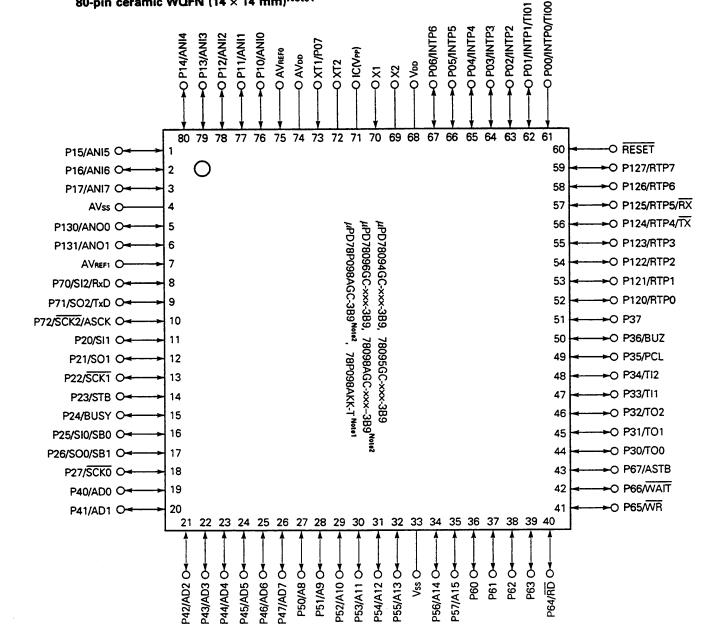

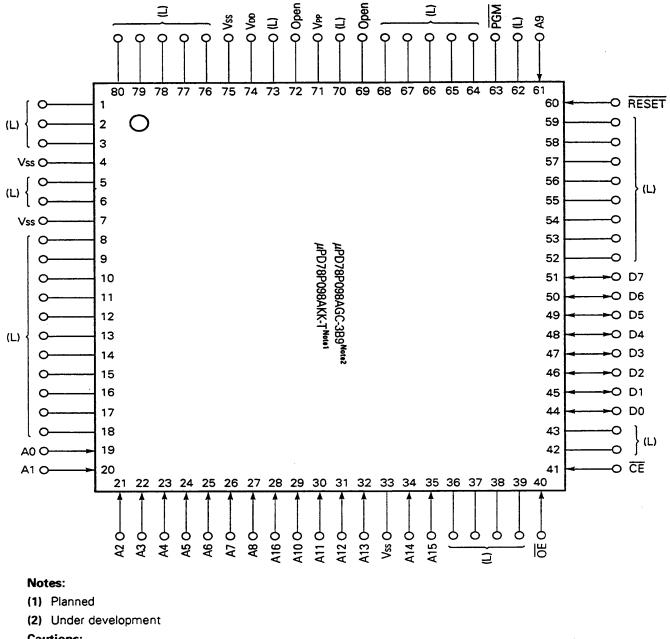

| 1.5       Pin Configuration (Top View)         1.6       78K/0 Series Development         1.7       Block Diagram         1.8       Outline of Function         1.8       Outline of Function         2.1       Normal operating mode pins         2.1.1       Normal operating mode pins         2.1.2       PROM programming mode pins (#PD78P098A only)         2.2       Description of Pin Functions         2.1.2       P10 to P07 (Port 0)         2.2.2       P10 to P17 (Port 1)         2.2.3       P20 to P27 (Port 2)         2.4       P30 to P37 (Port 3)         2.5       P40 to P47 (Port 4)         2.6       P50 to P57 (Port 5)         2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 7)         2.9       P120 to P127 (Port 12)         2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.12       AVREF1         2.2.13       RESET         2.2.14       AVes         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and X2         2.2.18       Vop         2.2.19       Vss <tr< th=""><th>1.3</th><th>Orderi</th><th>ng Information</th></tr<> | 1.3  | Orderi                     | ng Information                                             |

| 1.6       78K/0 Series Development         1.7       Block Diagram         1.8       Outline of Function         1.8       Outline of Function         2.1       Normal operating mode pins         2.1.1       Normal operating mode pins (µPD78P098A only)         2.2       Description of Pin Functions         2.1.2       PROM programming mode pins (µPD78P098A only)         2.2       Description of Pin Functions         2.2.1       P00 to P07 (Port 0)         2.2.2       P10 to P17 (Port 1)         2.3       P20 to P27 (Port 2)         2.4       P30 to P37 (Port 3)         2.5       P40 to P47 (Port 4)         2.6       P50 to P57 (Port 5)         2.7       P60 to P67 (Port 6)         2.8       P70 to P72 (Port 7)         2.9       P120 to P127 (Port 12)         2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.12       AVREF1         2.2.13       RESET         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Voo         2.2.19       Vss                                                      | 1.4  | Qualit                     | y Grade                                                    |

| 1.7       Block Diagram         1.8       Outline of Function         PTER 2       PIN FUNCTION         2.1       Pin Function List         2.1.1       Normal operating mode pins         2.1.2       PROM programming mode pins (µPD78P098A only)         2.2       Pescription of Pin Functions         2.1.1       P00 to P07 (Port 0)         2.2.2       P10 to P17 (Port 1)         2.2.3       P20 to P27 (Port 2)         2.2.4       P30 to P37 (Port 3)         2.2.5       P40 to P47 (Port 4)         2.2.6       P50 to P57 (Port 5)         2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 7)         2.2.9       P120 to P127 (Port 12)         2.2.10       P130 and P131 (Port 13)         2.2.11       AV#refo         2.2.12       AV#refo         2.2.13       AVbo         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vop         2.2.19       Vss         2.2.20       V#p (µPD78P098A only)                                                                                                                   | 1.5  | Pin Co                     | nfiguration (Top View)                                     |

| 8       Outline of Function         PTER 2       PIN FUNCTION         2.1       Pin Function List         2.1.1       Normal operating mode pins         2.1.2       PROM programming mode pins (µPD78P098A only)         P2       Description of Pin Functions         2.2.1       P00 to P07 (Port 0)         2.2.2       P10 to P17 (Port 1)         2.2.3       P20 to P27 (Port 2)         2.4       P30 to P37 (Port 3)         2.2.5       P40 to P47 (Port 4)         2.2.6       P50 to P57 (Port 5)         2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 7)         2.2.9       P120 to P127 (Port 12)         2.2.10       P130 and P131 (Port 13)         2.2.11       AVmero         2.2.12       AVeref         2.2.13       AVoc         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Voc         2.2.19       Vss         2.2.20       VFP (µPD78P098A only)                                                                                                                                                          | 1.6  | <b>78K</b> /0              | Series Development                                         |

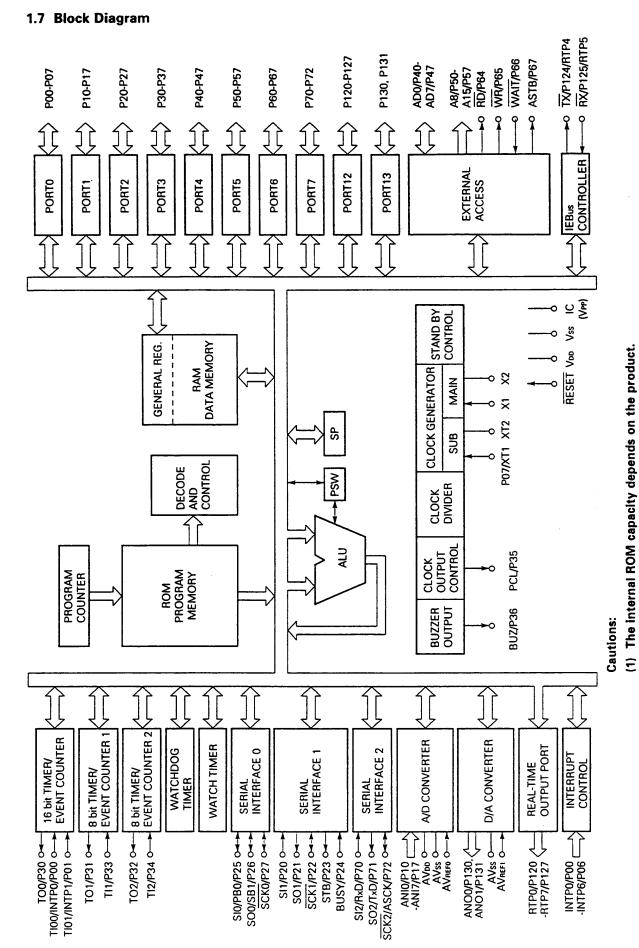

| PTER 2       PIN FUNCTION         2.1       Pin Function List         2.1.1       Normal operating mode pins         2.1.2       PROM programming mode pins (µPD78P098A only)         2.2       PBOM programming mode pins (µPD78P098A only)         2.2       PBO to P07 (Port 0)         2.2.2       P10 to P17 (Port 1)         2.2.3       P20 to P27 (Port 2)         2.4       P30 to P37 (Port 3)         2.5       P40 to P47 (Port 4)         2.6       P50 to P57 (Port 5)         2.7       P60 to P67 (Port 6)         2.8       P70 to P72 (Port 7)         2.9       P120 to P127 (Port 12)         2.10       P130 and P131 (Port 13)         2.11       AVREF0         2.2.12       AVREF1         2.2.13       AV00         2.2.14       AVSS         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vop         2.2.19       Vss         2.2.10       Vep (µPD78P098A only)                                                                                                                                                                                             | 1.7  | Block                      | Diagram                                                    |

| 2.1       Pin Function List         2.1.1       Normal operating mode pins         2.1.2       PROM programming mode pins (µPD78P098A only)         2.2       PBob to P07 (Port 0)         2.2.1       P00 to P07 (Port 0)         2.2.2       P10 to P17 (Port 1)         2.2.3       P20 to P27 (Port 2)         2.4       P30 to P37 (Port 3)         2.2.5       P40 to P47 (Port 4)         2.2.6       P50 to P57 (Port 5)         2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 7)         2.9       P120 to P127 (Port 12)         2.2.9       P120 to P127 (Port 13)         2.2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.12       AVREF1         2.2.13       AVoo         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vpo         2.2.19       Vss         2.2.19       Vss         2.2.20       VPF (µPD78P098A only)                                                                                                                                                                     | 1.8  | Outlin                     | e of Function                                              |

| 2.1.1       Normal operating mode pins         2.1.2       PROM programming mode pins (μPD78P098A only)         2.2.1       P00 to P07 (Port 0)         2.2.2       P10 to P17 (Port 1)         2.2.3       P20 to P27 (Port 2)         2.4       P30 to P37 (Port 3)         2.5       P40 to P47 (Port 4)         2.6       P50 to P57 (Port 5)         2.7       P60 to P67 (Port 6)         2.8       P70 to P127 (Port 12)         2.9       P120 to P127 (Port 12)         2.10       P130 and P131 (Port 13)         2.11       AVREF0         2.213       AVbo         2.214       AVss         2.215       RESET         2.216       X1 and X2         2.217       XT1 and XT2         2.219       Vss         2.219       Vss         2.219       Vss         2.211       XVpD                                                                                                                                                                                                                                                                                                                                                           |      | R 2 PI                     | N FUNCTION                                                 |

| 2.1.2       PROM programming mode pins (μPD78P098A only) <b>Description of Pin Functions</b> 2.2.1       P00 to P07 (Port 0)         2.2.2       P10 to P17 (Port 1)         2.2.3       P20 to P27 (Port 2)         2.2.4       P30 to P37 (Port 3)         2.2.5       P40 to P47 (Port 4)         2.2.6       P50 to P57 (Port 5)         2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 7)         2.9       P120 to P127 (Port 12)         2.10       P130 and P131 (Port 13)         2.2.11       AVREF1         2.2.13       AVop         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vpc         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss                                                                                                                                                                                                                                                                                                                                                            | 2.1  | Pin Fu                     | nction List                                                |

| 2.2       Description of Pin Functions         2.2.1       P00 to P07 (Port 0)         2.2.2       P10 to P17 (Port 1)         2.2.3       P20 to P27 (Port 2)         2.2.4       P30 to P37 (Port 3)         2.2.5       P40 to P47 (Port 4)         2.2.6       P50 to P57 (Port 5)         2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 7)         2.2.9       P120 to P127 (Port 12)         2.2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.13       AVoc         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vco         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.20       Vep (µPD78P098A oniy)                                                                                                                                                                                                                                                                                |      | 2.1.1                      | Normal operating mode pins                                 |

| 2.2       Description of Pin Functions         2.2.1       P00 to P07 (Port 0)         2.2.2       P10 to P17 (Port 1)         2.2.3       P20 to P27 (Port 2)         2.2.4       P30 to P37 (Port 3)         2.2.5       P40 to P47 (Port 4)         2.2.6       P50 to P57 (Port 5)         2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 7)         2.2.9       P120 to P127 (Port 12)         2.2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.13       AVoc         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vco         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.20       Vep (µPD78P098A oniy)                                                                                                                                                                                                                                                                                |      | 2.1.2                      | PROM programming mode pins (µPD78P098A only)               |

| 2.2.2       P10 to P17 (Port 1)         2.2.3       P20 to P27 (Port 2)         2.2.4       P30 to P37 (Port 3)         2.2.5       P40 to P47 (Port 4)         2.2.6       P50 to P57 (Port 5)         2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 7)         2.2.9       P120 to P127 (Port 12)         2.2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.12       AVREF1         2.2.13       AVDD         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       VDD         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.20       VrP (µPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                    | 2.2  | Descri                     |                                                            |

| 2.2.2       P10 to P17 (Port 1)         2.2.3       P20 to P27 (Port 2)         2.2.4       P30 to P37 (Port 3)         2.2.5       P40 to P47 (Port 4)         2.2.6       P50 to P57 (Port 5)         2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 7)         2.2.9       P120 to P127 (Port 12)         2.2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.12       AVREF1         2.2.13       AVDD         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       VDD         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.20       VrP (µPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                    |      |                            | P00 to P07 (Port 0)                                        |

| 2.2.3       P20 to P27 (Port 2)         2.2.4       P30 to P37 (Port 3)         2.2.5       P40 to P47 (Port 4)         2.2.6       P50 to P57 (Port 5)         2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 7)         2.2.9       P120 to P127 (Port 12)         2.2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.12       AVREF1         2.2.13       AVD0         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vpp         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.20       VeP (µPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                            | P10 to P17 (Port 1)                                        |

| 2.2.4       P30 to P37 (Port 3)         2.2.5       P40 to P47 (Port 4)         2.2.6       P50 to P57 (Port 5)         2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 7)         2.9       P120 to P127 (Port 12)         2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.12       AVREF1         2.2.13       AVoo         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Voo         2.2.19       Vss         2.2.19       Vss         2.2.20       VeP (µPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |                            |                                                            |

| 2.2.5       P40 to P47 (Port 4)         2.2.6       P50 to P57 (Port 5)         2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 7)         2.2.9       P120 to P127 (Port 12)         2.2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.12       AVREF1         2.2.13       AVDD         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       VDD         2.2.19       Vss         2.2.19       Vss         2.2.20       VPP (µPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                            | •                                                          |

| 2.2.6       P50 to P57 (Port 5)         2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 7)         2.9       P120 to P127 (Port 12)         2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.12       AVREF1         2.2.13       AVDD         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vpp         Vpc       (µPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |                            |                                                            |

| 2.2.7       P60 to P67 (Port 6)         2.2.8       P70 to P72 (Port 7)         2.2.9       P120 to P127 (Port 12)         2.2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.12       AVREF1         2.2.13       AVDD         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vop         2.2.19       Vss         2.2.19       Vss         2.2.20       Vep (µPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                            |                                                            |

| 2.2.8       P70 to P72 (Port 7)         2.2.9       P120 to P127 (Port 12)         2.2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.12       AVREF1         2.2.13       AVod         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vod         2.2.19       Vss         2.2.19       Vss         2.2.19       Vss         2.2.20       VPP (µPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |                            |                                                            |

| 2.2.9       P120 to P127 (Port 12)         2.2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.12       AVREF1         2.2.13       AVDD         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vod         2.2.19       Vss         2.2.19       Vss         2.2.20       Vep (μPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                            |                                                            |

| 2.2.10       P130 and P131 (Port 13)         2.2.11       AVREF0         2.2.12       AVREF1         2.2.13       AVDD         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vod         2.2.19       Vss         2.2.19       Vss         2.2.20       Vep (μPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                            |                                                            |

| 2.2.11       AVREF0         2.2.12       AVREF1         2.2.13       AVDD         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vod         2.2.19       Vss         2.2.19       Vss         2.2.20       Vep (μPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |                            |                                                            |

| 2.2.12       AVREF1         2.2.13       AVDD         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       VDD         2.2.19       Vss         2.2.19       Vss         2.2.20       VPP (μPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                            |                                                            |

| 2.2.13       AVDD         2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vod         2.2.19       Vss         2.2.19       Vss         2.2.20       VPP (µPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                            |                                                            |

| 2.2.14       AVss         2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vop         2.2.19       Vss         2.2.20       Vep (μPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                            |                                                            |

| 2.2.15       RESET         2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vod         2.2.19       Vss         2.2.20       VPP (μPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                            |                                                            |

| 2.2.16       X1 and X2         2.2.17       XT1 and XT2         2.2.18       Vpp         2.2.19       Vss         2.2.20       Vpp (μPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |                            |                                                            |

| 2.2.17       XT1 and XT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                            |                                                            |

| 2.2.18 Vpd<br>2.2.19 Vss<br>2.2.20 Vpp (μPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                            |                                                            |

| 2.2.19 Vss<br>2.2.20 Vpp (μPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                            |                                                            |

| 2.2.20 VPP (μPD78P098A only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                            |                                                            |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                            |                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                            | •                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • •  |                            |                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.3  | 2.2.19<br>2.2.20<br>2.2.21 | Vss<br>Vpp (μPD78P098A only)<br>IC (Mask ROM version only) |

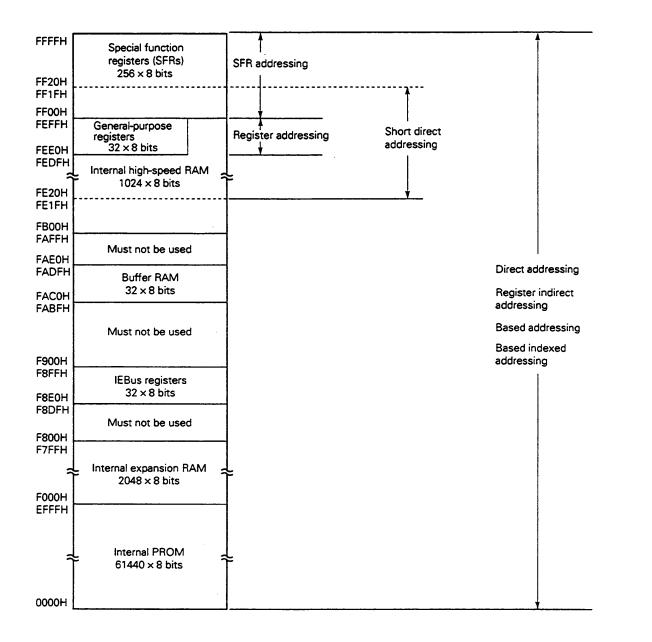

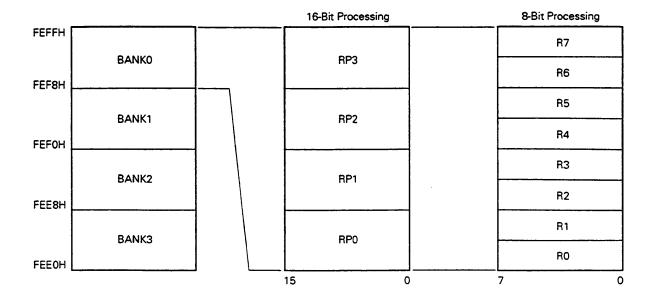

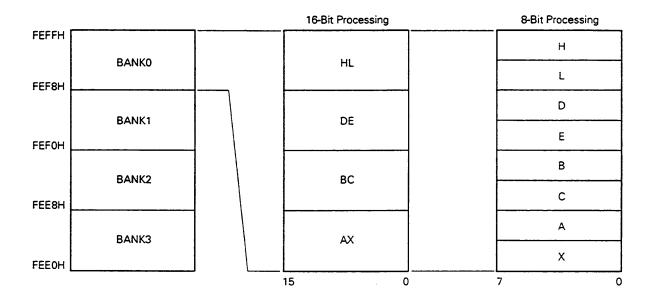

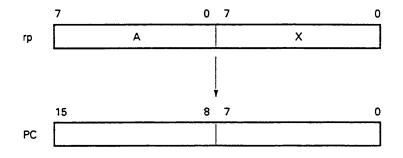

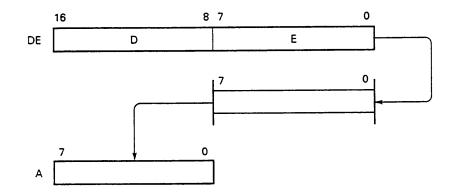

| 3.2    | Proces         | sor Registers                              | 39                   |

|--------|----------------|--------------------------------------------|----------------------|

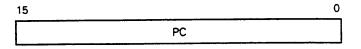

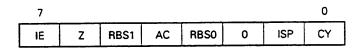

|        | 3.2.1          | Control registers                          | 39                   |

|        | 3.2.2          | General registers                          | 41                   |

|        | 3.2.3          | Special function register (SFR)            | 43                   |

|        | 3.2.4          | IEBus registers                            | 47                   |

| 3.3    | Instruc        | tion Address Addressing                    | 49                   |

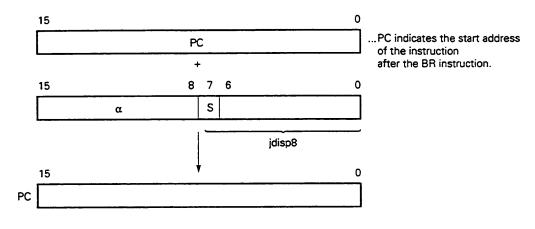

|        | 3.3.1          | Relative addressing                        | 49                   |

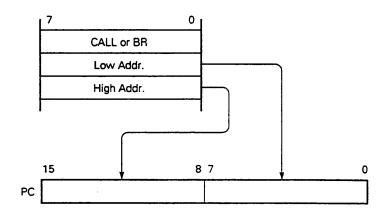

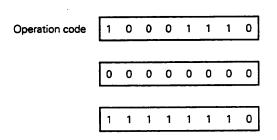

|        | 3.3.2          | Immediate addressing                       | 50                   |

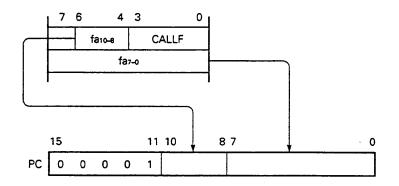

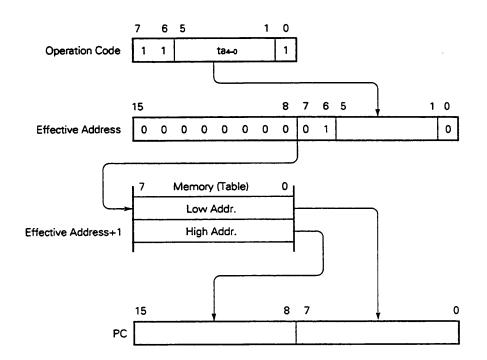

|        | 3.3.3          | Table indirect addressing                  | 51                   |

|        | 3.3.4          | Register addressing                        | 52                   |

| 3.4    | Opera          | nd Address Addressing                      | 53                   |

|        | 3.4.1          | Implied addressing                         | 53                   |

|        | 3.4.2          | Register addressing                        | 54                   |

|        | 3.4.3          | Direct addressing                          | 55                   |

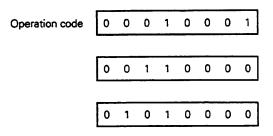

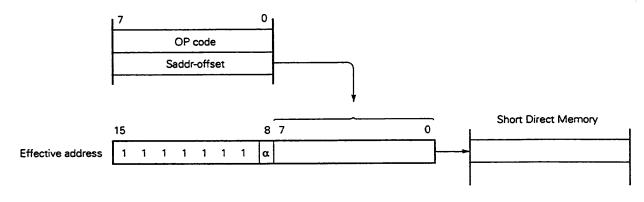

|        | 3.4.4          | Short direct addressing                    | 56                   |

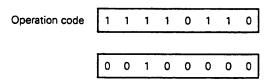

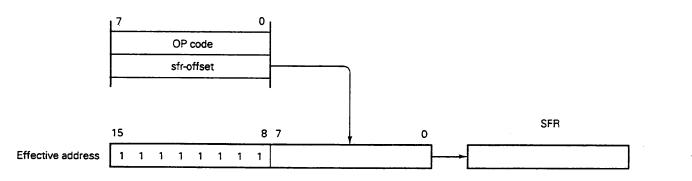

|        | 3.4.5          | Special function register (SFR) addressing | 58                   |

|        | 3.4.6          | Register indirect addressing               | 59                   |

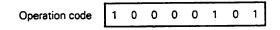

|        | 3.4.7          | Based addressing                           | 60                   |

|        | 3.4.8          | Based indexed addressing                   | 61                   |

|        | 3.4.9          | Stack addressing                           | 61                   |

|        |                |                                            |                      |

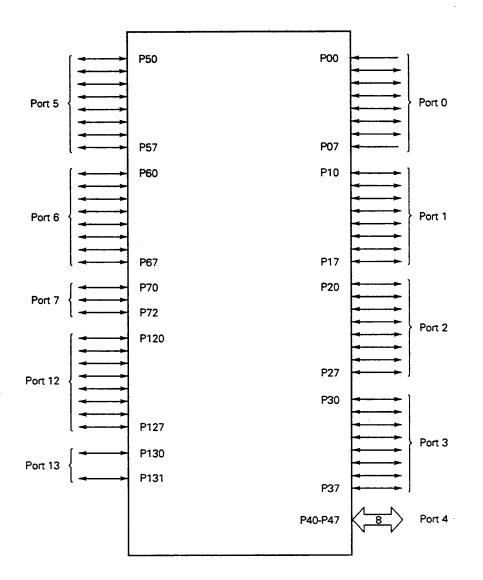

|        |                | DRT FUNCTIONS                              | 63                   |

| 4.1    |                | unctions                                   | 63                   |

| 4.2    |                | onfiguration                               | <b>66</b>            |

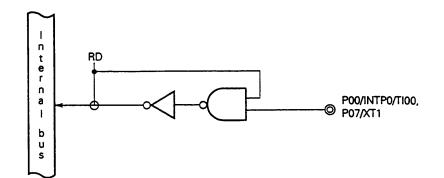

|        | 4.2.1<br>4.2.2 | Port 0                                     | 66<br>60             |

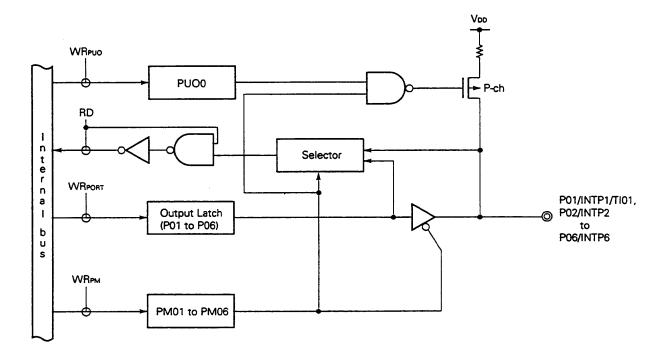

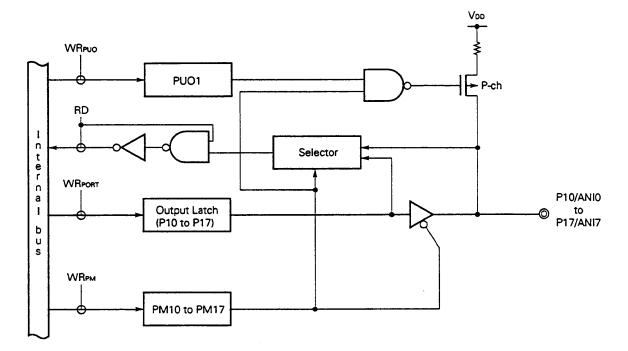

|        | 4.2.2          | Port 1<br>Port 2                           | 68<br>69             |

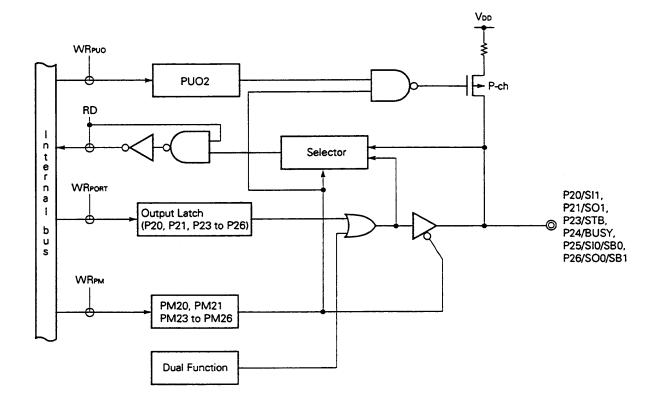

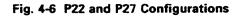

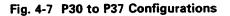

|        | 4.2.3          | Port 3                                     | 69<br>71             |

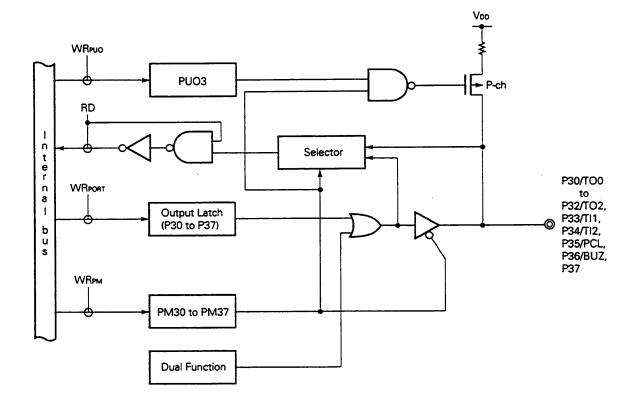

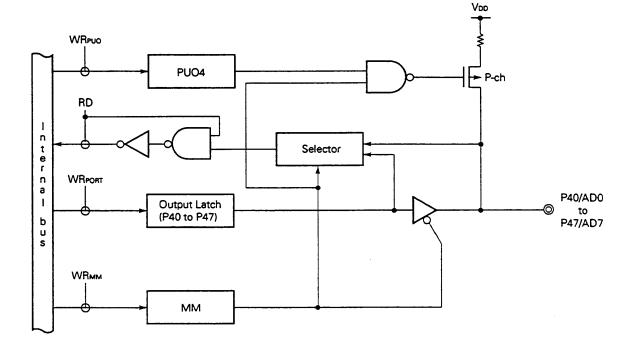

|        | 4.2.5          | Port 4                                     | 72                   |

|        | 4.2.6          | Port 5                                     | 72                   |

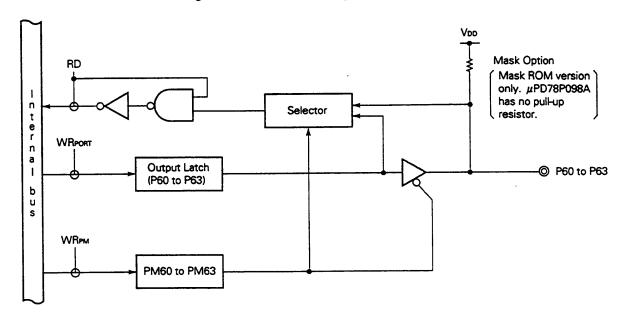

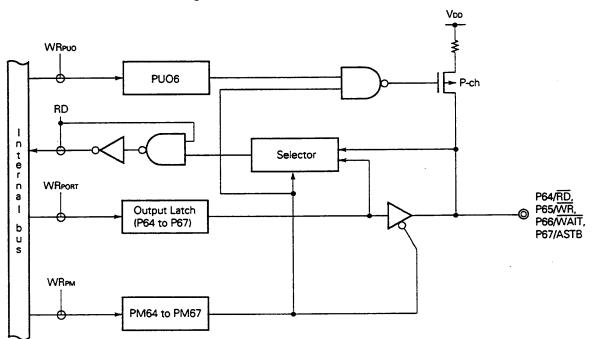

|        | 4.2.7          | Port 6                                     | 73                   |

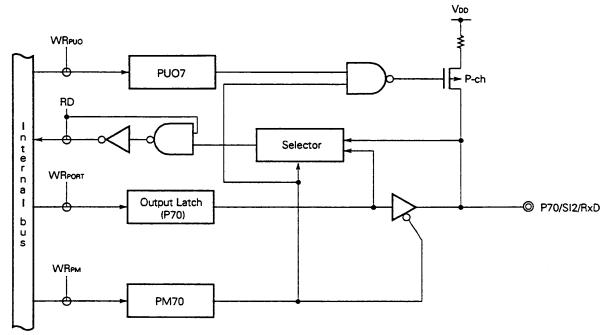

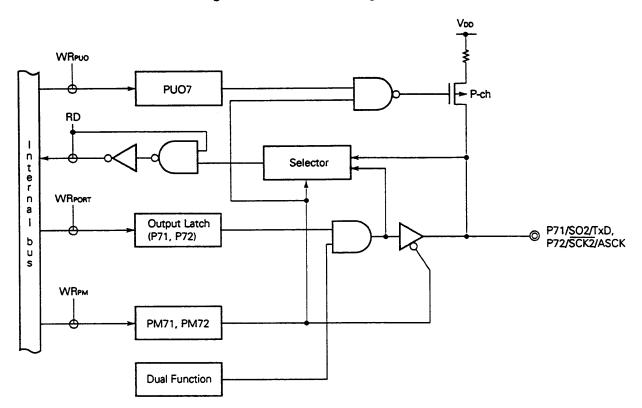

|        | 4.2.8          | Port 7                                     | 7 <del>4</del><br>76 |

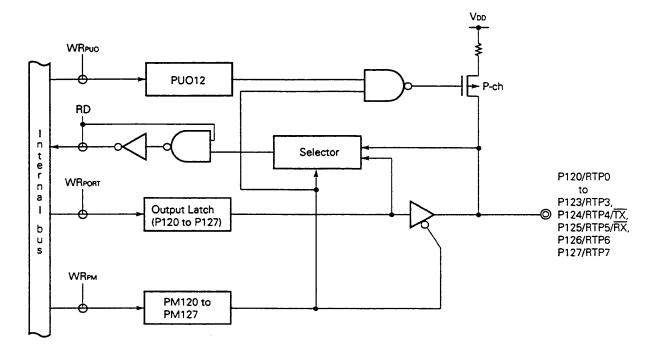

|        | 4.2.9          | Port 12                                    | 78                   |

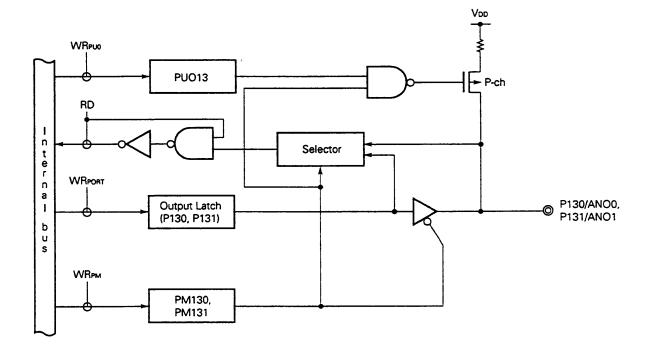

|        | 4.2.10         | Port 13                                    | 79                   |

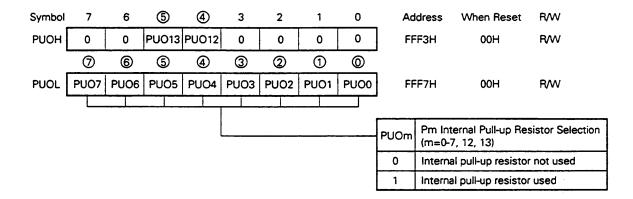

| 4.3    | Port F         | unction Control Registers                  | 80                   |

| 4.4    |                | unction Operations                         | 86                   |

|        | 4.4.1          | Writing to input/output port               | 86                   |

|        | 4.4.2          | Reading from input/output port             | 86                   |

|        | 4.4.3          | Operations on input/output port            | 87                   |

| 4.5    | Select         | ion of Mask Option                         | 87                   |

|        |                |                                            |                      |

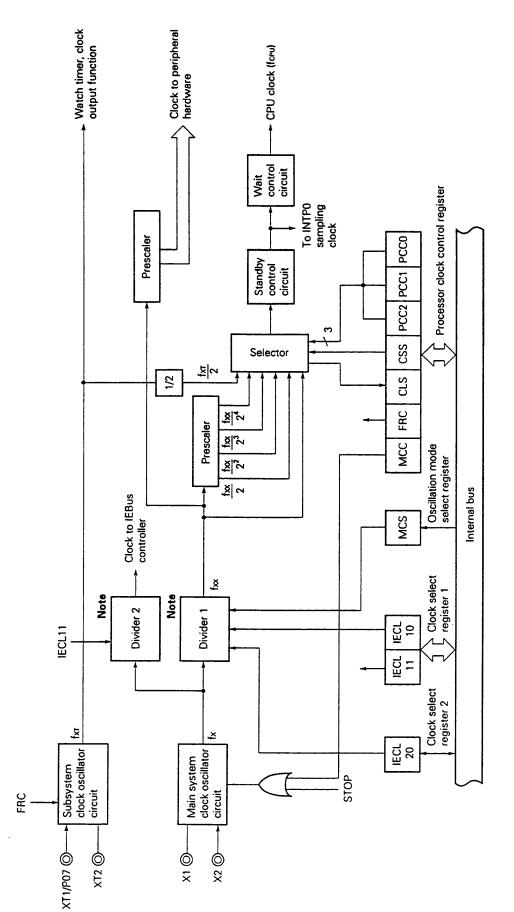

| СНАРТЕ | R 5 CI         | OCK GENERATOR                              | 89                   |

| 5.1    |                | Generator Functions                        | 89                   |

| 5.2    |                | Generator Configuration                    | 89                   |

| 5.3    | Clock          | Generator Control Register                 | 92                   |

| 5.4    |                | n Clock Oscillator                         | 97                   |

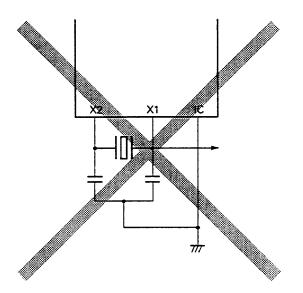

|        | 5.4.1          | Main system clock oscillator               | 97                   |

|        | 5.4.2          | Subsystem clock oscillator                 | 97                   |

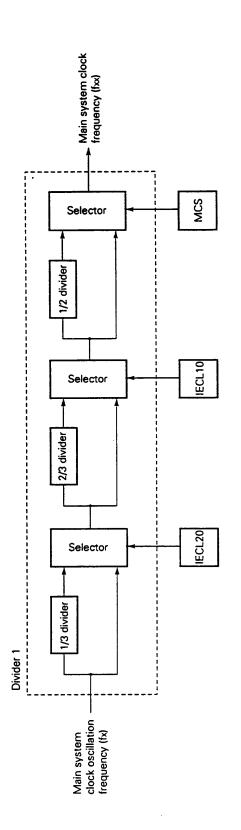

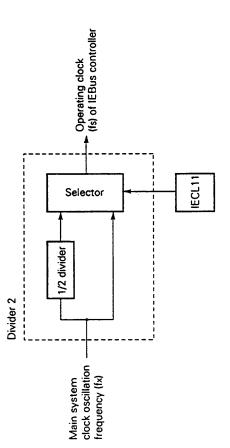

|        | 5.4.3                            | Divider                                                                                                |    |

|--------|----------------------------------|--------------------------------------------------------------------------------------------------------|----|

|        | 5.4.4                            | When no subsystem clocks are used                                                                      |    |

| 5.5    | •••••                            | Generator Operations                                                                                   |    |

|        | 5.5.1                            | Main system clock operations                                                                           |    |

|        | 5.5.2                            | Subsystem clock operations                                                                             |    |

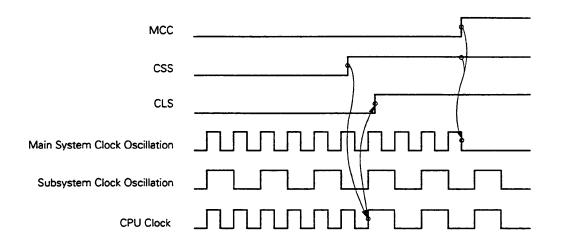

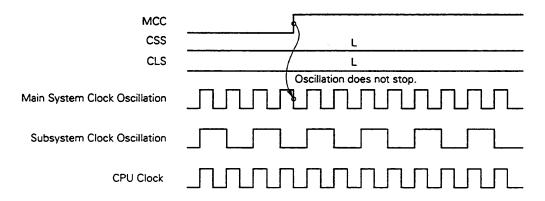

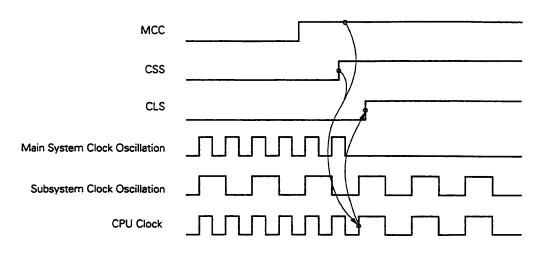

| 5.6    |                                  | ing System Clock and CPU Clock Settings                                                                |    |

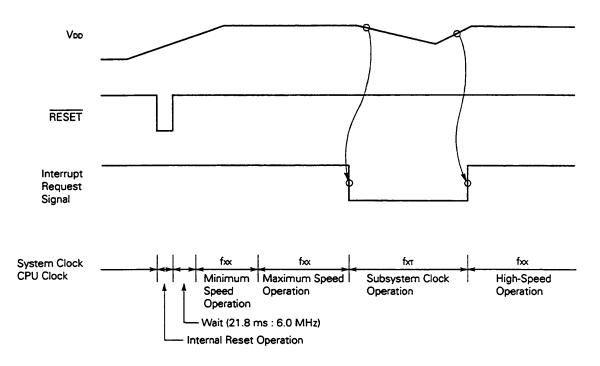

|        | 5.6.1                            | Time required for switchover between system clock and CPU clock                                        |    |

|        | 5.6.2                            | System clock and CPU clock switching procedure                                                         |    |

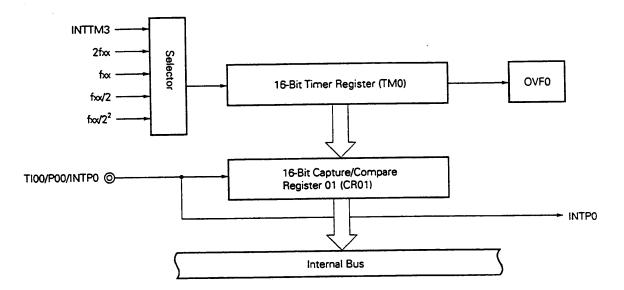

| СНАРТЕ |                                  | S-BIT TIMER/EVENT COUNTER                                                                              |    |

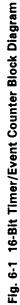

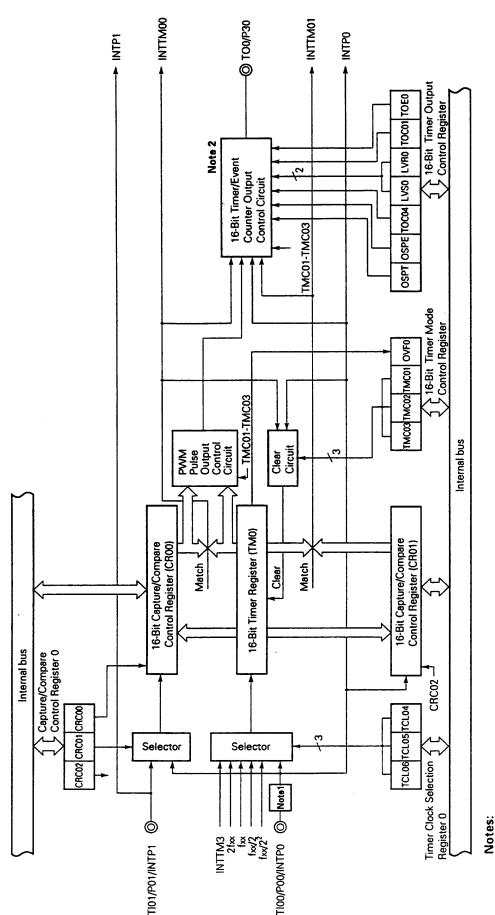

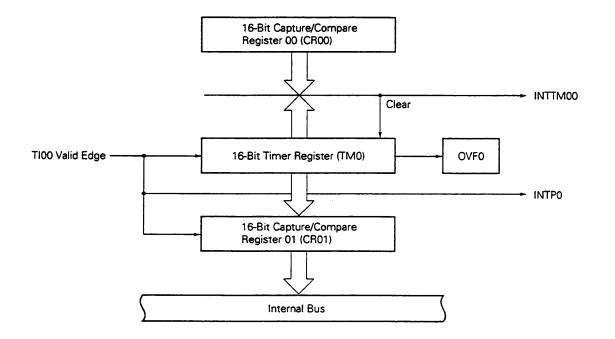

| 6.1    | 16-Bit                           | Timer/Event Counter Functions                                                                          |    |

| 6.2    |                                  | Timer/Event Counter Configuration                                                                      |    |