# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

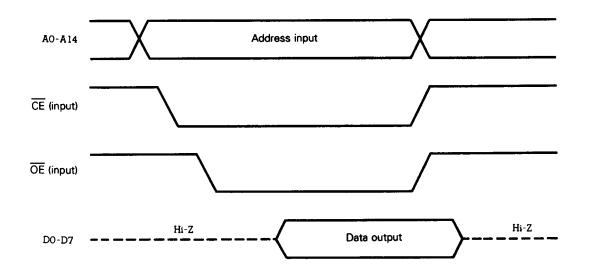

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# USER'S MANUAL

# $\mu$ PD78234 SUBSERIES

# **8-BIT SINGLE CHIP MICROCOMPUTER**

HARDWARE

μPD78233 μPD78234 μPD78237 μPD78238 μPD78238 μPD78234 (A) μPD78238 (A)

Document No. IEU-1290H (O. D. No. IEU-718H) Date Published January 1995 P Printed in Japan

#### GENERAL NOTES ON CMOS DEVICES

#### **(1)** STATIC ELECTRICITY (ALL MOS DEVICES)

# Exercise care so that MOS devices are not adversely influenced by static electricity while being handled.

The insulation of the gates of the MOS device may be destroyed by a strong static charge. Therefore, when transporting or storing the MOS device, use a conductive tray, magazine case, or conductive buffer materials, or the metal case NEC uses for packaging and shipment, and use grounding when assembling the MOS device system. Do not leave the MOS device on a plastic plate and do not touch the pins of the device.

Handle boards on which MOS devices are mounted similarly.

#### **(2)** PROCESSING OF UNUSED PINS (CMOS DEVICES ONLY)

#### Fix the input level of CMOS devices.

Unlike bipolar or NMOS devices, if a CMOS device is operated with nothing connected to its input pin, intermediate level input may be generated due to noise, and an inrush current may flow through the device, causing the device to malfunction. Therefore, fix the input level of the device by using a pull-down or pull-up resistor. If there is a possibility that an unused pin serves as an output pin (whose timing is not specified), each pin should be connected to VDD or GND through a resistor.

Refer to "Processing of Unused Pins" in the documents of each devices.

#### **③** STATUS BEFORE INITIALIZATION (ALL MOS DEVICES)

#### The initial status of MOS devices is undefined upon power application.

Since the characteristics of an MOS device are determined by the quantity Since the characteristics of an MOS device are determined by the quantity of injection at the molecular level, the initial status of the device is not controlled during the production process. The output status of pins, I/O setting, and register contents upon power application are not guaranteed. However, the items defined for reset operation and mode setting are subject to guarantee after the respective operations have been executed.

When using a device with a reset function, be sure to reset the device after power application.

EWS-4800 Series, EWS-UX/V, QTOP are trademarks of NEC Corporation. MS-DOS and Windows are trademarks of Microsoft Corporation. IBM DOS, PC/AT, and PC DOS are trademarks of IBM Corporation. SPARC station is a trademark of SPARC International, Inc. Sun OS is a trademark of Sun Microsystems, Inc. HP9000 Series 300 and HP-UX are trademarks of Hewlett-Packard.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

The devices listed in this document are not suitable for use in aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. If customers intend to use NEC devices for above applications or they intend to use "Standard" quality grade NEC devices for applications not intended by NEC, please contact our sales people in advance.

Application examples recommended by NEC Corporation

Standard: Computer, Office equipment, Communication equipment, Test and Measurement equipment, Machine tools, Industrial robots, Audio and Visual equipment, Other consumer products, etc.

Special: Automotive and Transportation equipment, Traffic control systems, Antidisaster systems, Anticrime systems, etc.

## **Contents Updated in This Edition**

| Page                 | Contents                                                                                                                                                                                                      |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P. 364               | Fig. 12-1 Clock-Synchronized Serial Interface Configuration has been modified.                                                                                                                                |

| P. 524               | Some part of the description of (5) A/D Converter in 16.4.3 Notes<br>on using STOP mode in CHAPTER 6 STANDBY FUNCTIONS has<br>been deleted.<br>An example of Processing of Analog Input Pin has been deleted. |

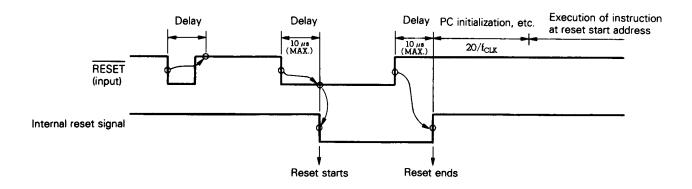

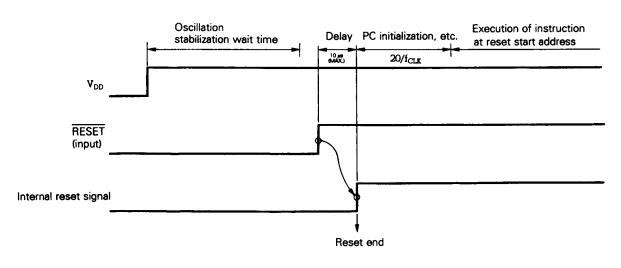

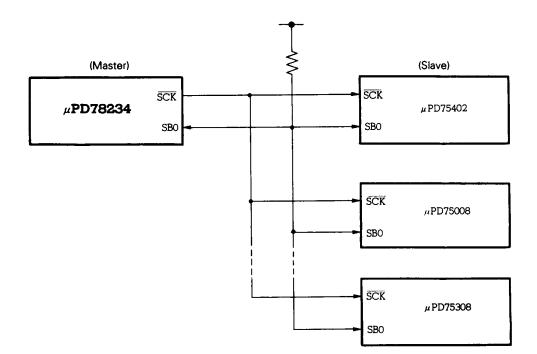

| P. 527, 528          | Some explanation has been added to Fig. 17-1 Accepting RESET<br>Signal and Fig. 17-2 Reset Operation on Power Application in<br>CHAPTER 17 RESET FUNCTION.                                                    |

| P. 574-577<br>P. 577 | <ul> <li>APPENDIX B DEVELOPMENT TOOL</li> <li>Descriptions concerning 3.5" 2HC has been added to the supply media and part number for IBM PC/AT.</li> <li>B.2.4 OS for IBM PC has been added.</li> </ul>      |

The mark  $\star$  shows major revised points.

#### INTRODUCTION

| Target reader |                                                                                                  | ers who understand the functions of $\mu$ PD78234 pplication systems of the microcomputers.                         |

|---------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Objectives    | This manual describes the function tions of $\mu$ PD78234 sub-series.                            | as of the internal hardware devices and instruc-                                                                    |

| Outline       |                                                                                                  | D78234 sub-series: the hardware Manual (this<br>I (which can be commonly used with the 78K/II<br>these manuals are: |

|               | Hardware<br>Pin functions<br>Internal block functions<br>Interrupt<br>Other internal peripherals | Instruction<br>CPU functions<br>Addressing<br>Instruction set                                                       |

The important information in using the products described in this manual are provided in the form of "Caution" in appropriate places in each Chapter of this manual. This information is repeated at the end of the Chapter. Be sure to read it before using the products.

#### How to read this manual

Readers of this manual must have general knowledge on electric engineering, logic circuits, and microcomputers.

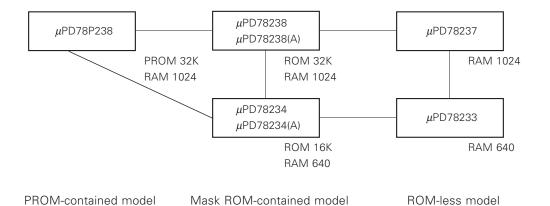

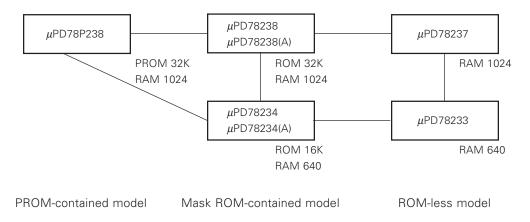

This manual describes the functions for  $\mu$ PD78233, 78234, 78237, 78238, 78P238, 78234(A), and 78238(A). The relations among these products are shown in the next figure.

Typical circuit examples described in this manual are designed for "Standard" quality standard products for general electronics devices. When using the circuits for applications requiring "Special" quality standard, the quality standard for each component and circuit actually used must be confirmed before using.

- When there are no functional differences among the products μPD78234 is described as the representative product.

- When there are functional differences

The functions of an individual product are described.

However, if the functional difference is whether ROM is provided or not, μPD78233 is described as the representative ROM-less model.

For the detailed description of a register whose name is known, refer to **APPENDIX D REGISTER INDEX**.

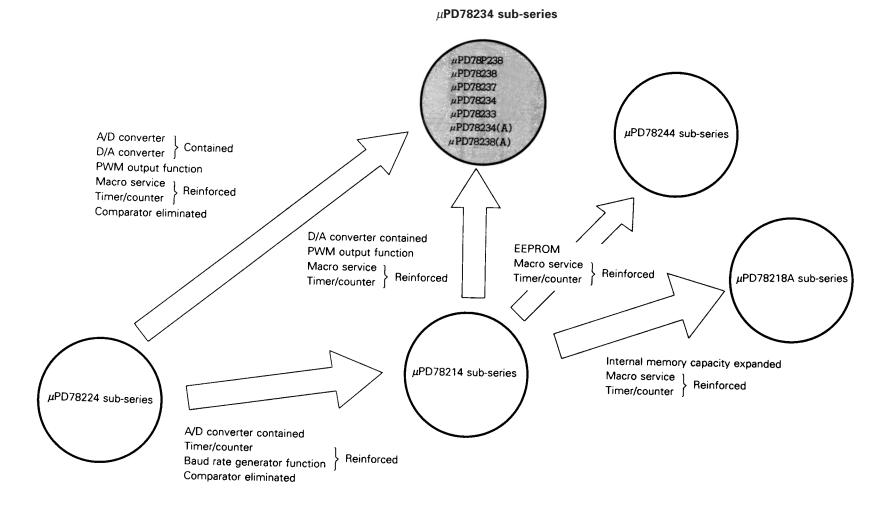

For the differences between  $\mu$ PD78234 and the other models in the 78K/II series, first refer to **APPENDIX A 78K/II SERIES PRODUCT LIST** to learn what kinds of differences exist, and then refer to **APPENDIX E GENERAL INDEX** for details.

For the detailed description of a function whose name is known, refer to **APPENDIX E GENERAL INDEX**.

If  $\mu$ PD78234 does not operate correctly, while the microcomputer or its software is being debugged, refer to the end of each chapter where notes on each function are presented.

To understand the functions of  $\mu \text{PD78234}$  sub-series read the manual according to the CONTENTS.

For a detailed description on instruction functions, refer to the **78K/II SERIES USER'S MANUAL, INSTRUCTIONS (IEU-1311)** separately available.

Refer to the data sheet provided with this manual as an appendix for the electrical characteristics of the  $\mu$ PD78234 sub-series.

Refer to the application note provided with this manual as an appendix for application examples of each function of the  $\mu$ PD78234 sub-series.

| Legend | Data significance     | : Data on the left has higher significance, while data on the right has lower significance |

|--------|-----------------------|--------------------------------------------------------------------------------------------|

|        | Active low signal     | : $\overline{x}\overline{x}\overline{x}$ (top bar on pin name or signal name)              |

|        | *                     | : Footnote                                                                                 |

|        | Caution               | : Information calling for your particular attention                                        |

|        | Remarks               | : Supplemental information                                                                 |

|        | Number representation | : Binary: xxxx or xxxxB                                                                    |

|        |                       | Decimal: xxxx                                                                              |

|        |                       | Hexadecimal: xxxxH                                                                         |

#### **Related documents**

Refer to the following documents as well as this manual.

|                  | Product                          | μPD78233<br>μPD78234 | μPD78P238   | μPD78234(A)<br>μPD78238(A) |

|------------------|----------------------------------|----------------------|-------------|----------------------------|

| Document         |                                  | μPD78237<br>μPD78238 |             |                            |

| Data sheet       |                                  | IC-2476              | IC-2607     | IC-2984                    |

| User's manual    | Hardware                         |                      | This manual |                            |

| Oser's manual    | Instruction                      |                      | IEU-1311    |                            |

|                  | Application                      |                      | IEA-1280    |                            |

| Application note | Floating point operation program |                      | IEA-1273    |                            |

#### - Documents related to $\mu$ PD78234 sub-series

#### • Serial bus interface (SBI) user's manual

#### • Documents related to development tools

| Document                                                   |                  | Document no. |

|------------------------------------------------------------|------------------|--------------|

|                                                            | Hardware         | EEU-1327     |

| IE-78230-R in-circuit emulator user's manual               | Software         | EEU-1296     |

| IE-78230-R-A in-circuit emulator user's manual             |                  | EEU-1392     |

| RA70K series secondar polyars uper's manual                | Language         | EEU-1404     |

| RA78K series assembler package user's manual               | Operation        | EEU-1399     |

| 78K series structured assembler preprocessor user's manual |                  | EEU-1402     |

| CC78K series C compiler user's manual                      | Language         | EEU-1284     |

|                                                            | Operation        | EEU-1280     |

| SD70K/II assaan dahuggas usas'a manual MC DOC basa         | Beginner's guide | EEU-1447     |

| SD78K/II screen debugger user's manual MS-DOS base         | Reference        | EEU-1413     |

### Documents related to software for embedded applications

| Document                                                                            |            | Document no. |

|-------------------------------------------------------------------------------------|------------|--------------|

| 78K/0, 78K/II, 87AD series fuzzy inference development support system user's manual | Translator | EEU-1444     |

#### Other related documents

| Document                                        | Document no. |

|-------------------------------------------------|--------------|

| Package manual                                  | IEI-1213     |

| Semiconductor device mounting technology manual | IEI-1207     |

| Quality grade on NEC semiconductor devices      | IEI-1209     |

| Static electricity discharge (ESD) test         | IEI-1201     |

Caution: Be sure to use the latest document for designing.

Register representation:

Confusing characters : 0 (zero), O (uppercase "O")

- : 1 (one), I (lowercase "L"),

- I (uppercase "I")

#### CONTENTS

| CHAPTE | R 1 0  | GENERAL                                                                                 |

|--------|--------|-----------------------------------------------------------------------------------------|

| 1.1    | Featu  | res                                                                                     |

| 1.2    | Order  | ing Information and Quality Grade                                                       |

|        | 1.2.1  | Ordering information                                                                    |

|        | 1.2.2  | Quality grade                                                                           |

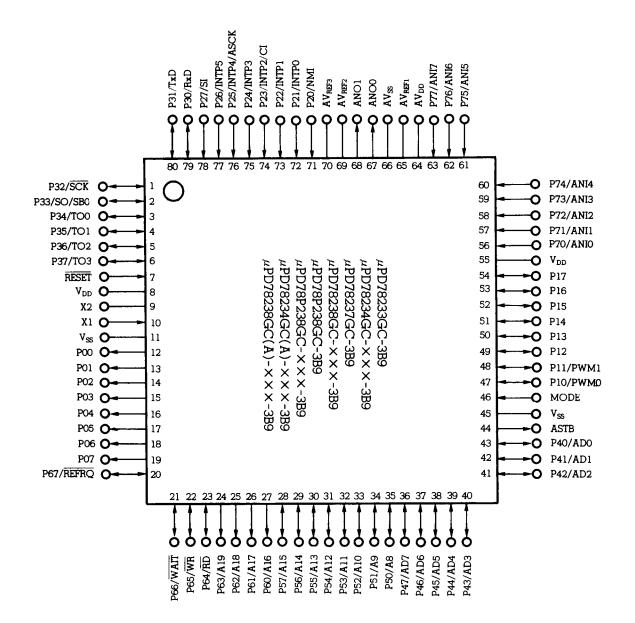

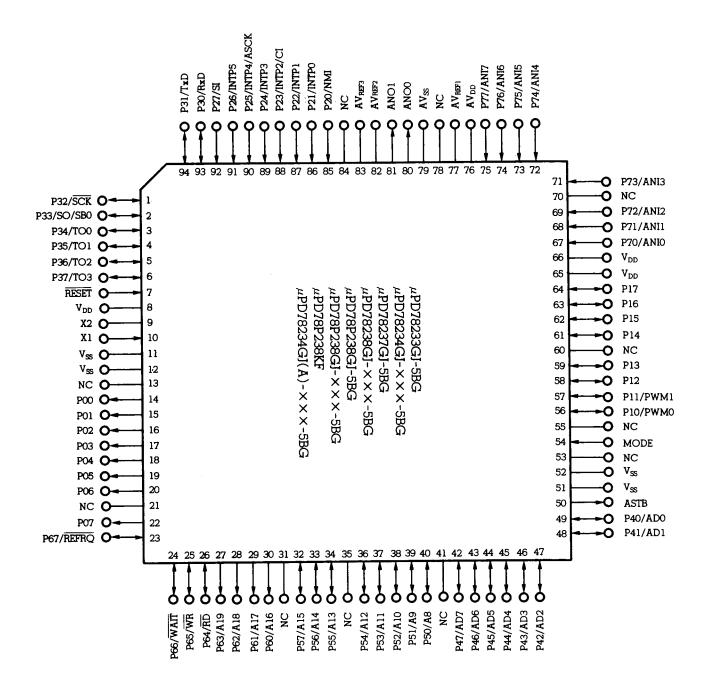

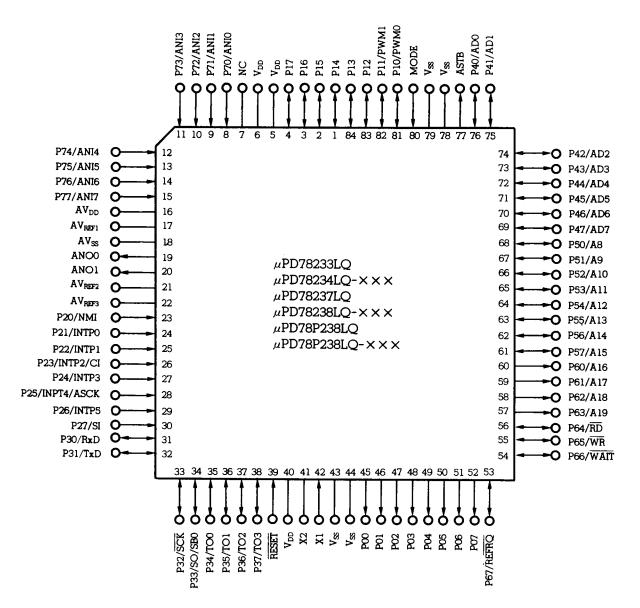

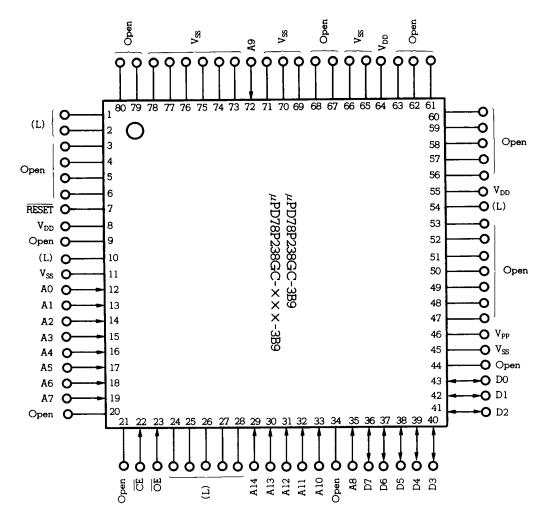

| 1.3    | Pin Co | onfiguration (Top View)                                                                 |

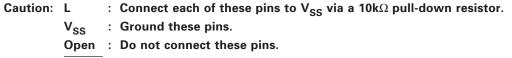

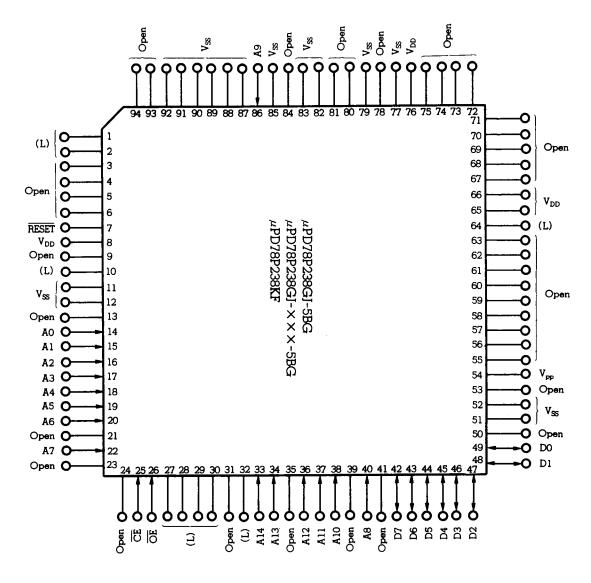

|        | 1.3.1  | Ordinary operation mode                                                                 |

|        | 1.3.2  | PROM programming mode                                                                   |

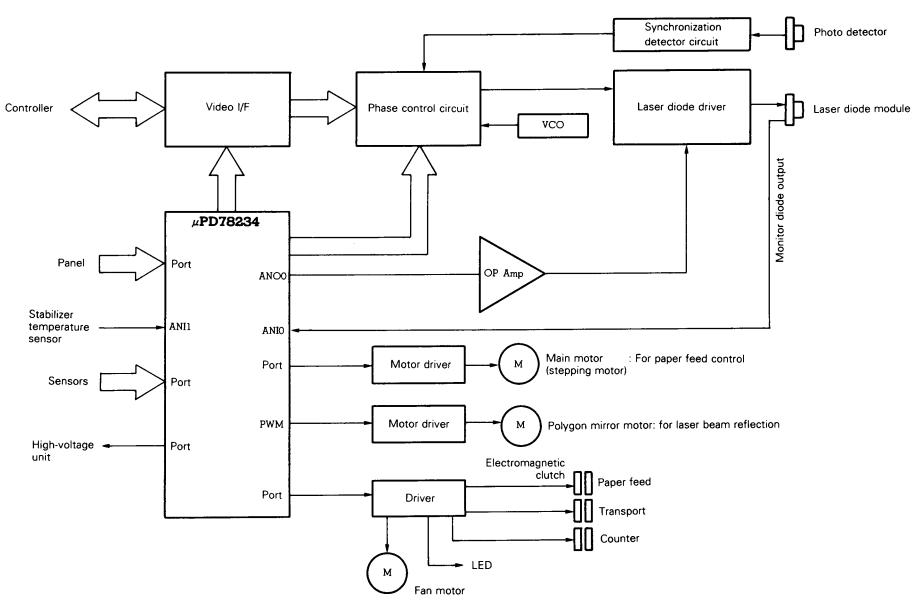

| 1.4    | Applic | cation System Configuration Example (LBP engine)                                        |

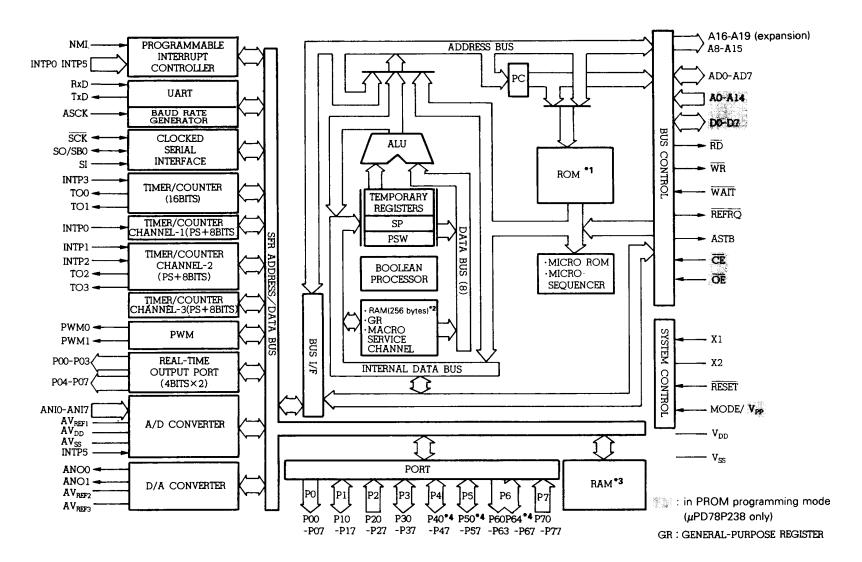

| 1.5    | Intern | al Block Diagram                                                                        |

| 1.6    | Specif | fications                                                                               |

| 1.7    | Differ | ences among $\mu$ PD78234 Sub-Series Products                                           |

|        | 1.7.1  | Functional differences                                                                  |

|        | 1.7.2  | Differences in package                                                                  |

|        | 1.7.3  | Differences between $\mu$ PD78234/ $\mu$ PD78238 and $\mu$ PD78234(A)/ $\mu$ PD78238(A) |

|        |        |                                                                                         |

| СНАРТЕ | R 2 P  | PIN FUNCTIONS                                                                           |

| 2.1    | Pin Fu | Inction List                                                                            |

|        | 2.1.1  | Ordinary operation mode                                                                 |

|        | 2.1.2  | PROM programming mode                                                                   |

| 2.2    | Pin Fu | inctions                                                                                |

|        | 2.2.1  | Ordinary operation mode                                                                 |

|        | 2.2.2  | PROM programming mode                                                                   |

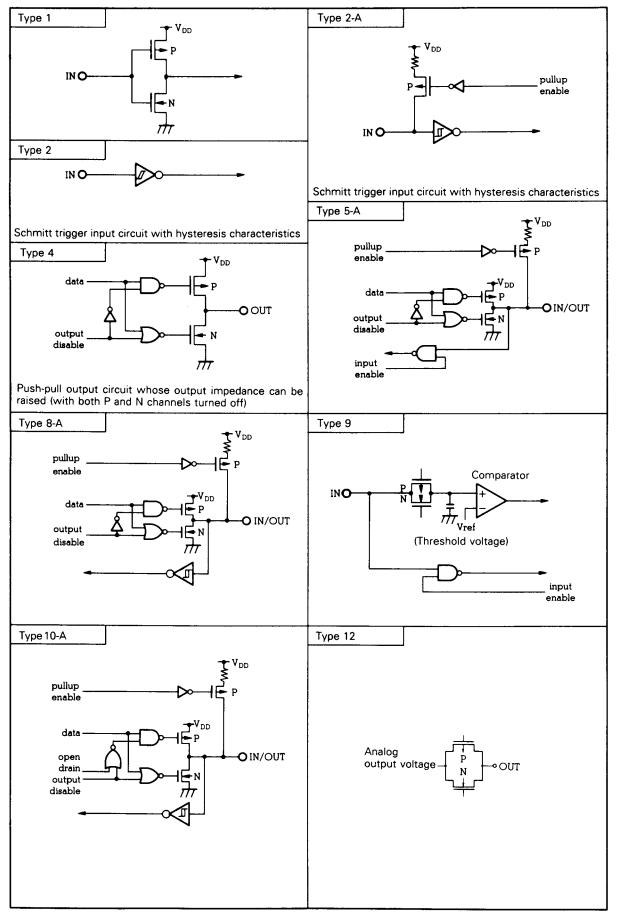

| 2.3    | I/O Ci | rcuits and Processing Unused Pins                                                       |

| 2.4    | Notes  |                                                                                         |

|        |        |                                                                                         |

| СНАРТЕ | R 3 0  | PU FUNCTION                                                                             |

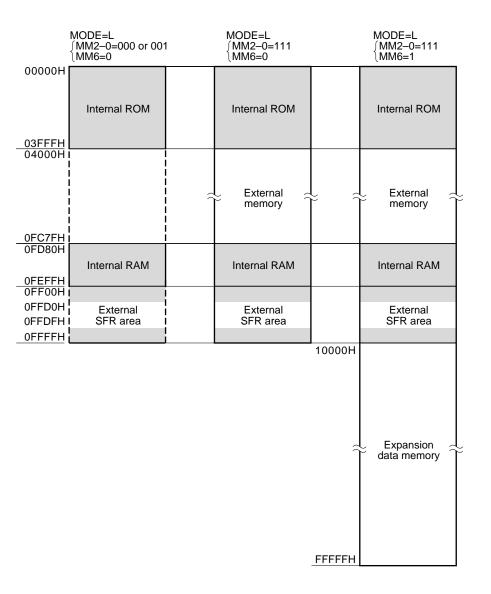

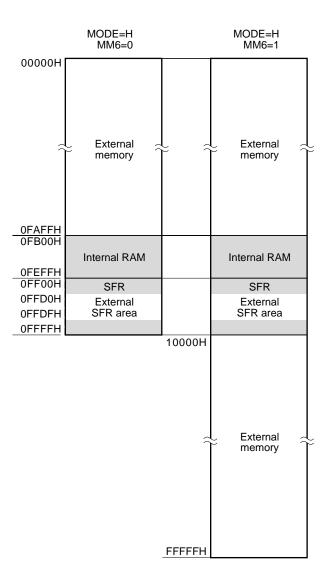

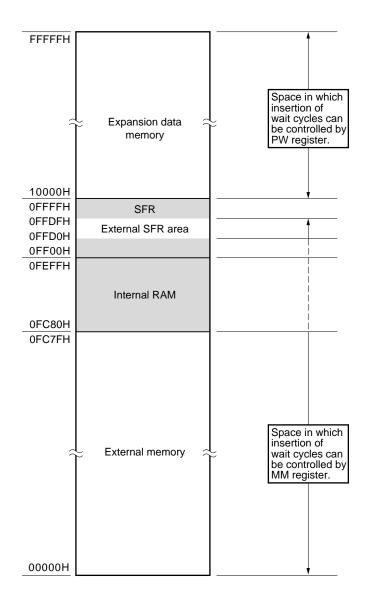

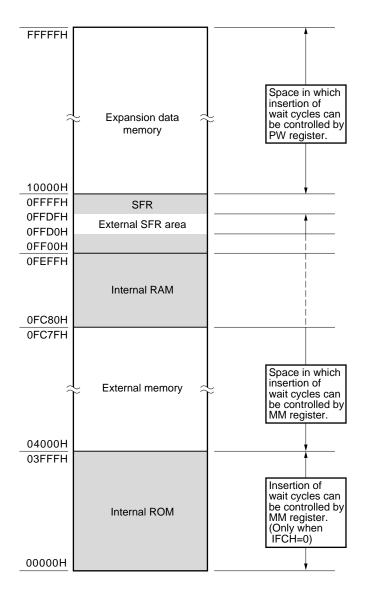

| 3.1    | Memo   | bry Space                                                                               |

|        | 3.1.1  | Internal program memory area                                                            |

|        | 3.1.2  | Internal RAM area                                                                       |

|        | 3.1.3  | Special function register (SFR) area                                                    |

|        | 3.1.4  | External SFR area                                                                       |

|        | 3.1.5  | External memory area                                                                    |

|        | 3.1.6  | External expansion data memory space                                                    |

|        | 3.1.7  | Memory mapping of $\mu$ PD78P238                                                        |

| 3.2    | Regist | ters                                                                                    |

|        | 3.2.1  | Program counter (PC)                                                                    |

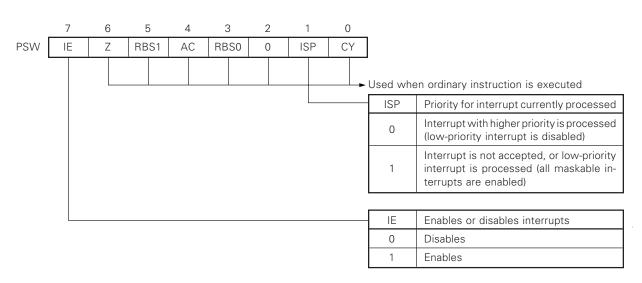

|        | 3.2.2  | Program status word (PSW)                                                               |

|        | 3.2.3  | Stack pointer (SP)                                                                      |

|        | 3.2.4  | General-purpose registers                                                               |

|        | 3.2.5  | Special function register (SFRs)                                                        |

| 3.3    | Notes  |                                                                                         |

| CHAPTE | R 4   | CLOCK GENERATOR CIRCUIT              | 59  |

|--------|-------|--------------------------------------|-----|

| 4.1    | Con   | figuration and Function              | 59  |

| 4.2    | Note  | e                                    | 61  |

|        | 4.2.1 | When external clock is input         | 61  |

|        | 4.2.2 | Crystal/ceramic oscillation          | 62  |

| СНАРТЕ | R 5   | PORT FUNCTIONS                       | 65  |

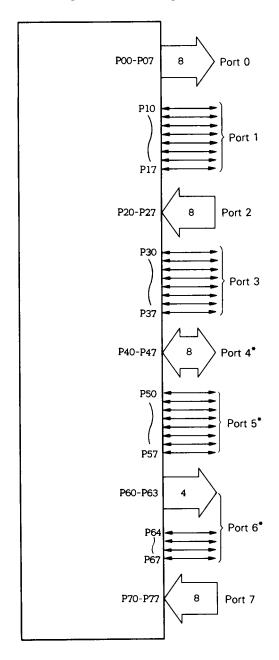

| 5.1    | Digi  | tal I/O Ports                        | 65  |

| 5.2    | Port  | : 0                                  | 67  |

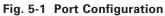

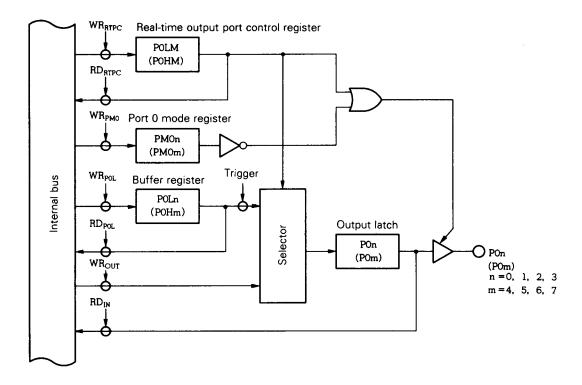

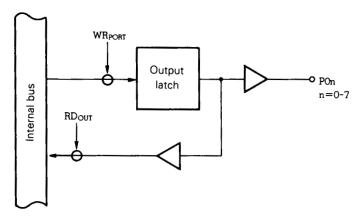

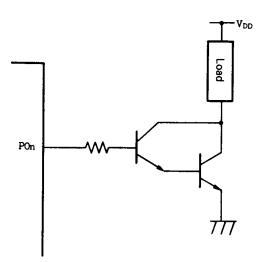

|        | 5.2.1 | Hardware configuration               | 67  |

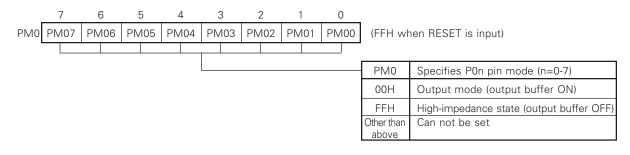

|        | 5.2.2 | Setting output mode and control mode | 68  |

|        | 5.2.3 | Operation state                      | 69  |

|        | 5.2.4 | Pull-up resistor                     | 69  |

|        | 5.2.5 | Driving transistor                   | 70  |

| 5.3    | Port  | : 1                                  | 71  |

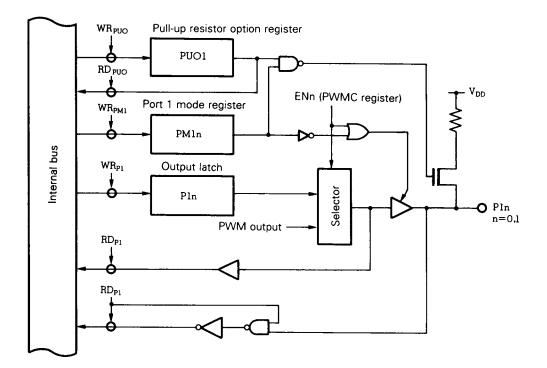

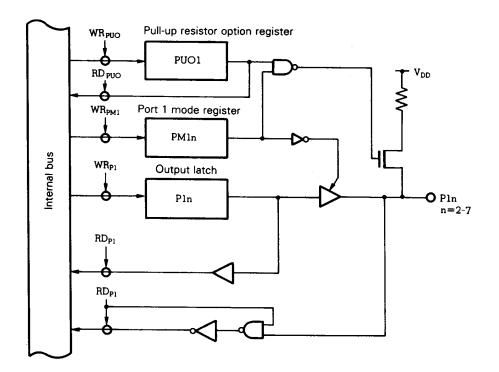

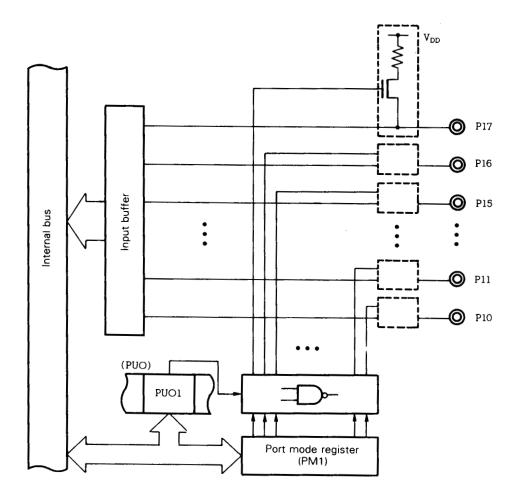

|        | 5.3.1 | Hardware configuration               | 71  |

|        | 5.3.2 | Setting I/O mode and control mode    | 73  |

|        | 5.3.3 | Operation state                      | 74  |

|        | 5.3.4 | Internal pull-up resistor            | 77  |

|        | 5.3.5 | Direct drive for LED                 | 79  |

| 5.4    | Port  | 2                                    | 80  |

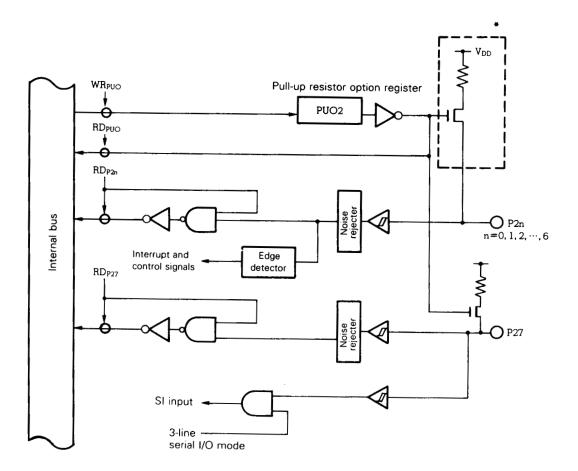

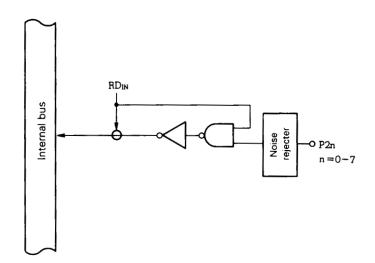

|        | 5.4.1 | Hardware configuration               | 82  |

|        | 5.4.2 | Setting I/O mode and control mode    | 83  |

|        | 5.4.3 | Operation state                      | 83  |

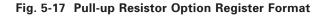

|        | 5.4.4 | Pull-up resistor                     | 84  |

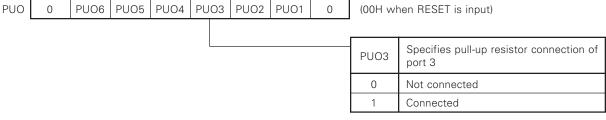

| 5.5    | Port  | : 3                                  | 86  |

|        | 5.5.1 | Hardware configuration               | 88  |

|        | 5.5.2 | Setting of I/O mode and control mode | 92  |

|        | 5.5.3 | Operation state                      | 94  |

|        | 5.5.4 | Internal pull-up resistor            | 97  |

| 5.6    | Port  | 4                                    | 99  |

|        | 5.6.1 | Hardware configuration               | 99  |

|        | 5.6.2 | Setting I/O mode and control mode    | 100 |

|        | 5.6.3 | Operation state                      | 100 |

|        | 5.6.4 | Internal pull-up resistor            | 102 |

|        | 5.6.5 | Direct drive for LED                 | 103 |

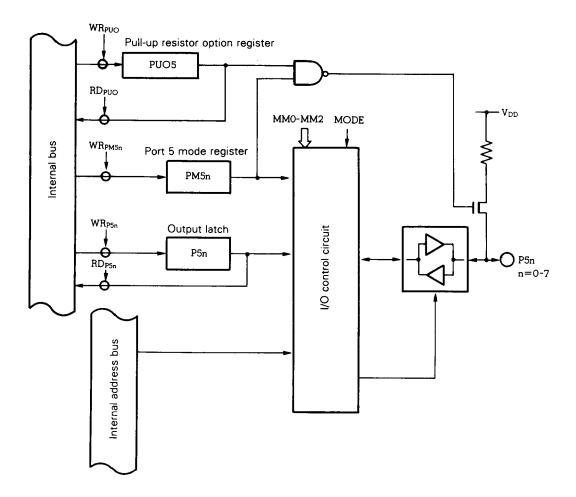

| 5.7    | Port  | 5                                    | 104 |

|        | 5.7.1 | Hardware configuration               | 104 |

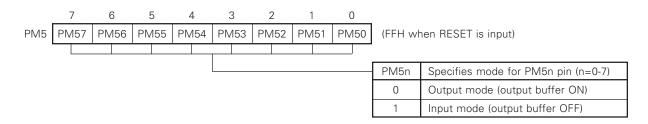

|        | 5.7.2 | Setting I/O mode and control mode    | 105 |

|        | 5.7.3 | Operation state                      | 106 |

|        | 5.7.4 | Internal pull-up resistor            | 108 |

|        | 5.7.5 | Direct drive for LED                 | 109 |

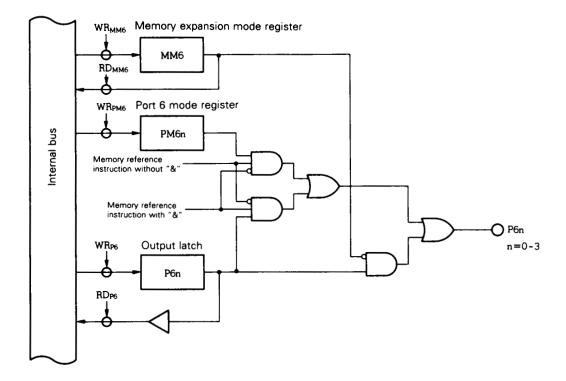

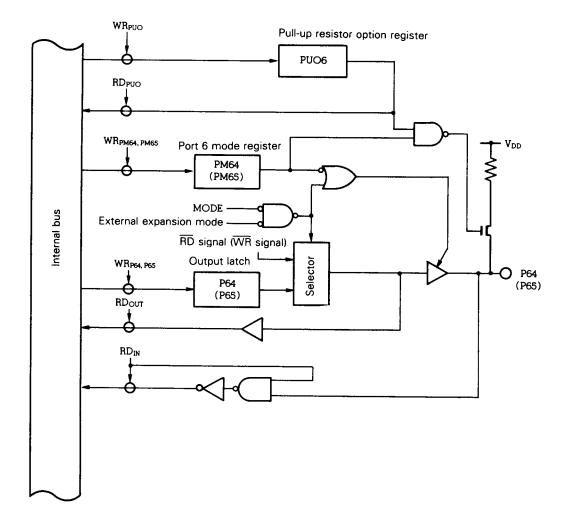

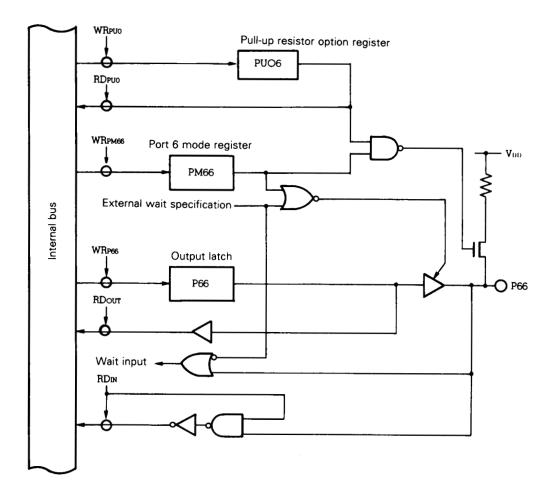

| 5.8    | Port  | 6                                    | 110 |

|        | 5.8.1 | Hardware configuration               | 111 |

|        | 5.8.2 | Setting I/O mode and control mode    | 115 |

|        | 5.8.3 | Operation state                      | 118 |

|        | 5.8.4 | Internal pull-up resistor            | 120 |

| 5.9    | Port 7  | ,                                                        | 121 |

|--------|---------|----------------------------------------------------------|-----|

|        | 5.9.1   | Hardware configuration                                   | 121 |

|        | 5.9.2   | Setting I/O mode and control mode                        | 121 |

|        | 5.9.3   | Operation state                                          | 122 |

|        | 5.9.4   | Internal pull-up resistor                                | 122 |

|        | 5.9.5   | Note                                                     | 122 |

| 5.10   | Note    |                                                          | 123 |

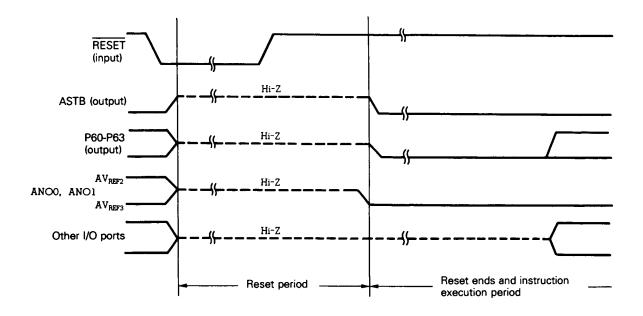

| СНАРТЕ | R6RE    | AL-TIME OUTPUT FUNCTION                                  | 125 |

| 6.1    |         | guration and Function                                    | 125 |

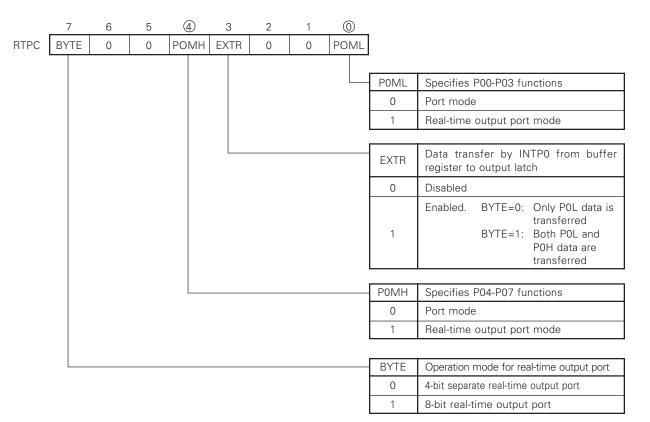

| 6.2    | Real-T  | Time Output Port Control Register (RTPC)                 | 127 |

| 6.3    | Acces   | sing Real-Time Output Port                               | 128 |

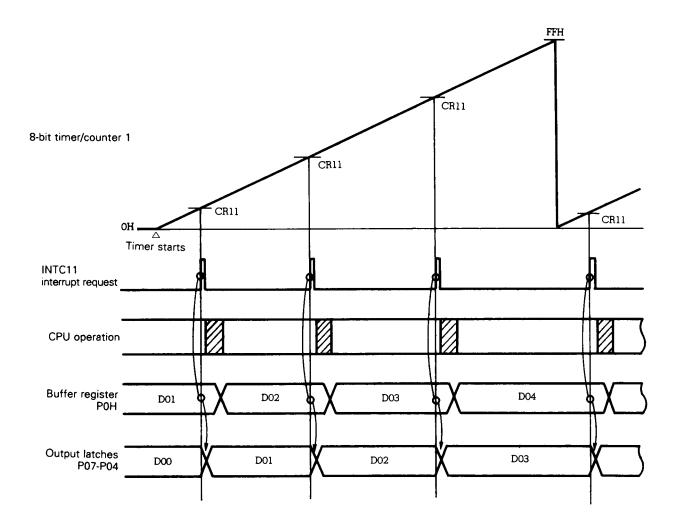

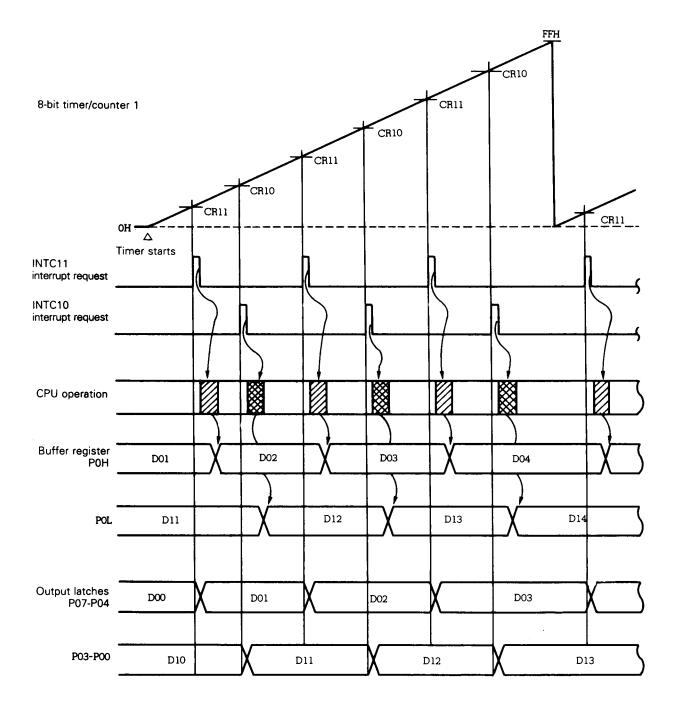

| 6.4    | Opera   | tion                                                     | 130 |

| 6.5    | Applic  | cation Example                                           | 133 |

| 6.6    | Note.   |                                                          | 136 |

|        |         |                                                          |     |

| СНАРТЕ | R7 T    | IMER/COUNTER UNITS                                       | 137 |

| 7.1    | 16-bit  | Timer/Counter                                            | 139 |

|        | 7.1.1   | Function                                                 | 139 |

|        | 7.1.2   | Configuration                                            | 140 |

|        | 7.1.3   | 16-bit timer/counter control registers                   | 143 |

|        | 7.1.4   | 16-bit timer0 (TM0) operation                            | 147 |

|        | 7.1.5   | Operations for compare registers and capture register    | 151 |

|        | 7.1.6   | Basic operation for output control circuits              | 154 |

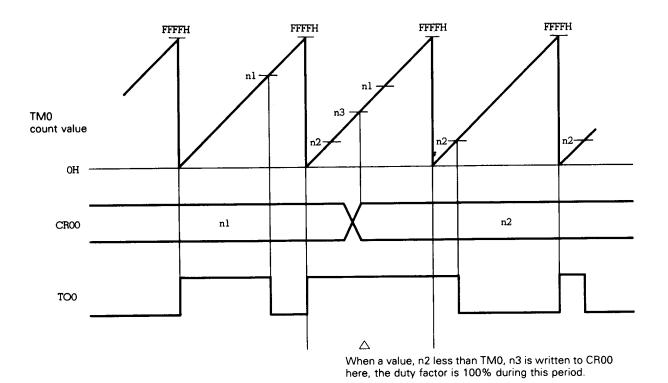

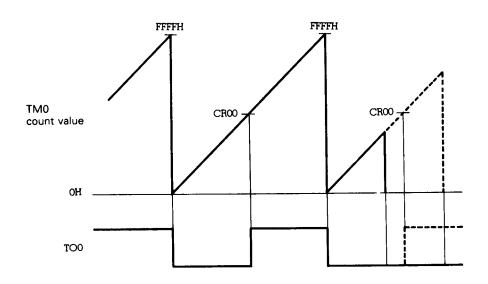

|        | 7.1.7   | PWM output                                               | 158 |

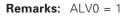

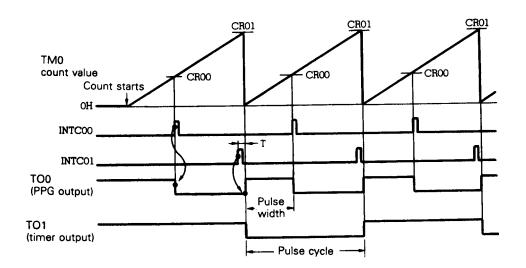

|        | 7.1.8   | PPG output                                               | 163 |

|        | 7.1.9   | Software-triggered one-shot pulse output                 | 170 |

|        | 7.1.10  | Application examples                                     | 171 |

| 7.2    | 8-bit 1 | Γimer/Counter 1                                          | 189 |

|        | 7.2.1   | Function                                                 | 189 |

|        | 7.2.2   | Configuration                                            | 190 |

|        | 7.2.3   | 8-bit timer/counter control registers                    | 193 |

|        | 7.2.4   | 8-bit timer 1 (TM1) operation                            | 196 |

|        | 7.2.5   | Compare register and capture/compare register operations | 200 |

|        | 7.2.6   | Application examples                                     | 205 |

| 7.3    |         | Γimer/Counter 2                                          | 214 |

|        | 7.3.1   | Function                                                 | 214 |

|        | 7.3.2   | Configuration                                            | 216 |

|        | 7.3.3   | 8-bit timer/counter 2 control registers                  | 219 |

|        | 7.3.4   | 8-bit timer 2 (TM2) operation                            | 223 |

|        | 7.3.5   | External event counter function                          | 227 |

|        | 7.3.6   | One-shot timer function                                  | 232 |

|        | 7.3.7   | Compare registers and capture register operations        | 233 |

|        | 7.3.8   | Basic operation for output control circuits              | 237 |

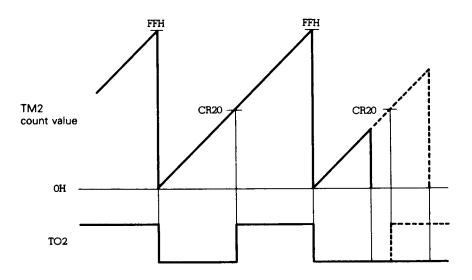

|        | 7.3.9   | PWM output                                               | 241 |

|        | 7.3.10  | PPG output                                               | 247 |

|        | 7.3.11  | Application examples                                     | 254 |

| 7.4    | 8-bit Timer/Counter 3                           | 278 |

|--------|-------------------------------------------------|-----|

|        | 7.4.1 Function                                  | 278 |

|        | 7.4.2 Configuration                             | 279 |

|        | 7.4.3 8-bit timer/counter 3 control registers   | 281 |

|        | 7.4.4 8-bit timer 3 (TM3) operation             | 283 |

|        | 7.4.5 Compare register operation                | 286 |

|        | 7.4.6 Application examples                      | 287 |

| 7.5    | Notes                                           | 289 |

|        | 7.5.1 Notes common to all timers/counters       | 289 |

|        | 7.5.2 Notes on 16-bit timer/counter             | 298 |

|        | 7.5.3 Notes on 8-bit timer/counter 2            | 299 |

|        | 7.5.4 Notes for using the in-circuit emulator   | 303 |

| СНАРТЕ |                                                 | 305 |

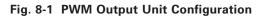

| 8.1    | PWM Output Unit Configuration                   | 305 |

| 8.2    | PWM Output Unit Control Registers               | 307 |

|        | 8.2.1 PWM control register (PWMC)               | 307 |

|        | 8.2.2 PWM modulo registers (PWM0 and PWM1)      | 308 |

| 8.3    | PWM Output Unit Operation                       | 309 |

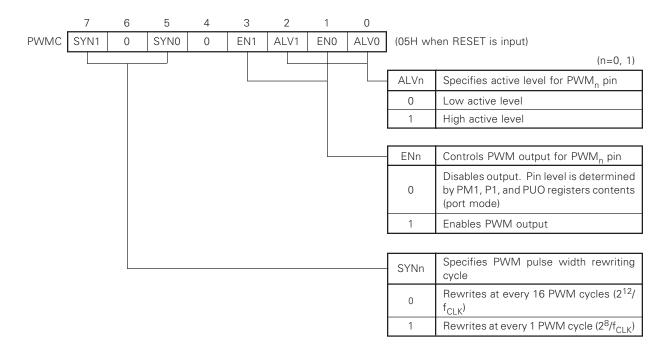

|        | 8.3.1 Basic PWM output operation                | 309 |

|        | 8.3.2 Enabling/disabling PWM pulse output       | 309 |

|        | 8.3.3 Specifying active level for PWM pulse     | 310 |

|        | 8.3.4 Specifying PWM pulse width changing cycle | 311 |

| 8.4    | Notes                                           | 312 |

| СНАРТЕ | R 9 A/D CONVERTER                               | 313 |

| 9.1    | Configuration                                   | 313 |

| 9.2    | A/D Converter Mode Register (ADM)               | 317 |

| 9.3    | Operation                                       | 319 |

|        | 9.3.1 Basic A/D converter operation             | 319 |

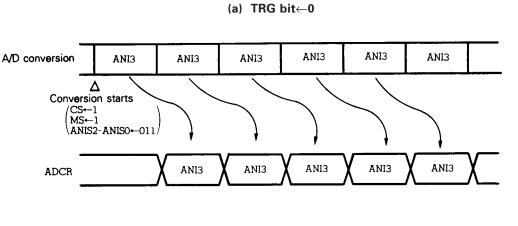

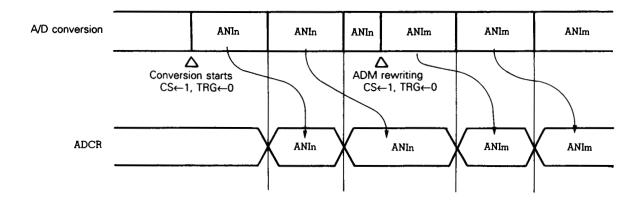

|        | 9.3.2 Select mode                               | 323 |

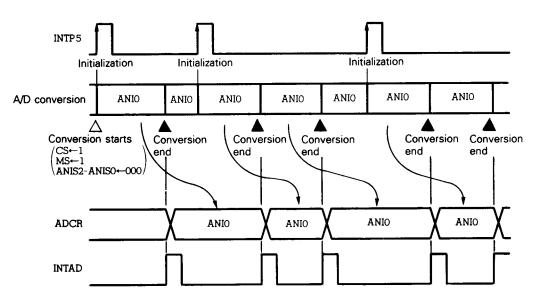

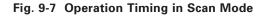

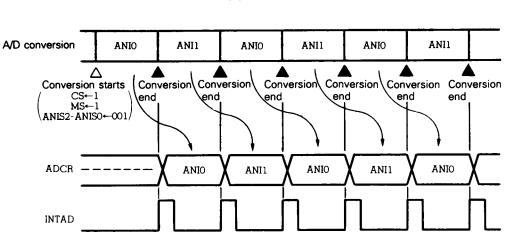

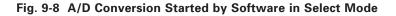

|        | 9.3.3 Scan mode                                 | 324 |

|        | 9.3.4 Starting A/D conversion by software       | 326 |

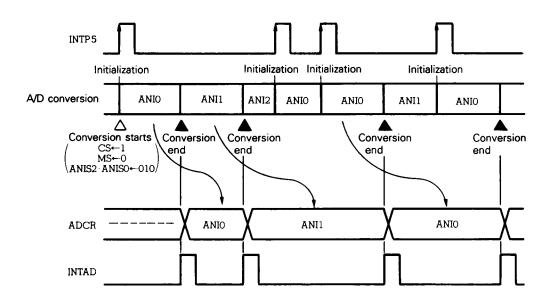

|        | 9.3.5 Starting A/D conversion by hardware       | 328 |

| 9.4    | External Interrupt for A/D Converter            | 332 |

| 9.5    | Notes                                           | 333 |

| СНАРТЕ | R 10 D/A CONVERTER                              | 337 |

|        | Configuration                                   | 337 |

| 10.2   | D/A Converter Operation                         | 339 |

| 10.3   | Notes                                           | 340 |

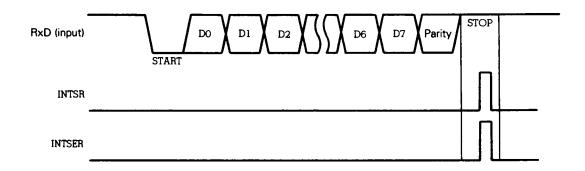

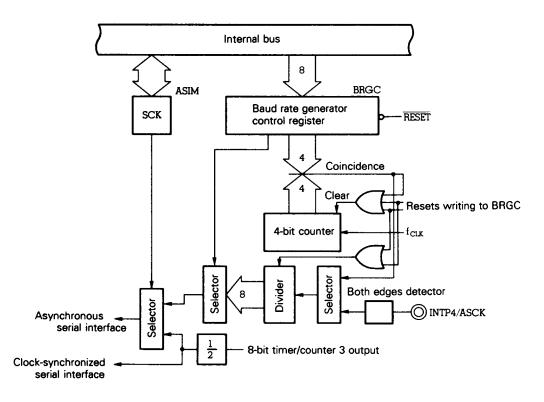

| СНАРТЕ | R 11 ASYNCHRONOUS SERIAL INTERFACE              | 341 |

| 11.1   | Configuration                                   | 341 |

| 11.2   | Asynchronous Serial Interface Control Registers | 344 |

| 11.3 | Asyncl                                          | nronous Serial Interface Operations                                |

|------|-------------------------------------------------|--------------------------------------------------------------------|

|      | 11.3.1                                          | Data format                                                        |

|      | 11.3.2                                          | Parity types and operations                                        |

|      | 11.3.3                                          | Transfer                                                           |

|      | 11.3.4                                          | Reception                                                          |

|      | 11.3.5                                          | Reception error                                                    |

| 11.4 | Baud F                                          | Rate Generator                                                     |

|      | 11.4.1                                          | Baud rate generator configuration                                  |

|      | 11.4.2                                          | Baud rate generator control register (BRGC)                        |

|      | 11.4.3                                          | Baud rate generator operations                                     |

| 11.5 | Baud F                                          | Rate Setting                                                       |

|      | 11.5.1                                          | Setting examples, when baud rate generator is used                 |

|      | 11.5.2                                          | Setting examples, when 8-bit timer/counter 3 is used               |

|      | 11.5.3                                          | Setting examples, when external baud rate input (ASCK) is used     |

| 11.6 | Notes                                           |                                                                    |

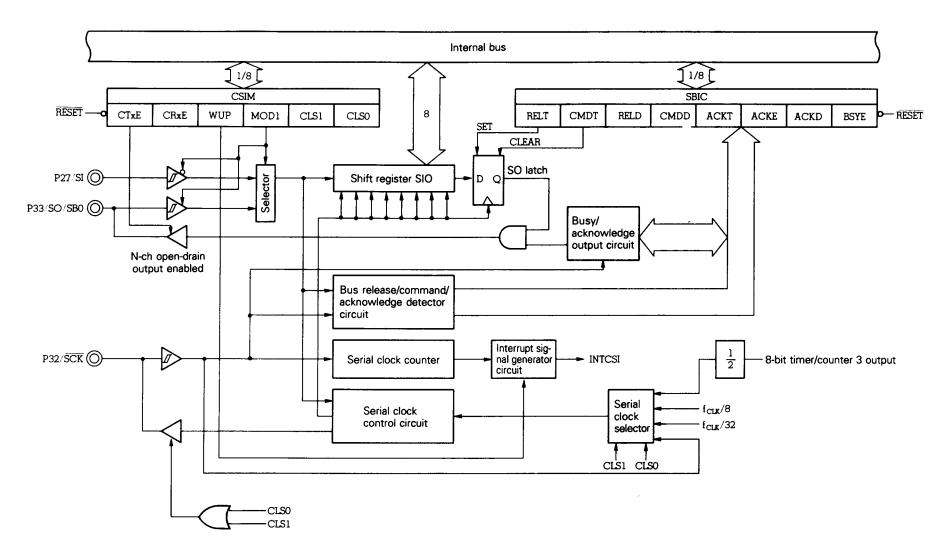

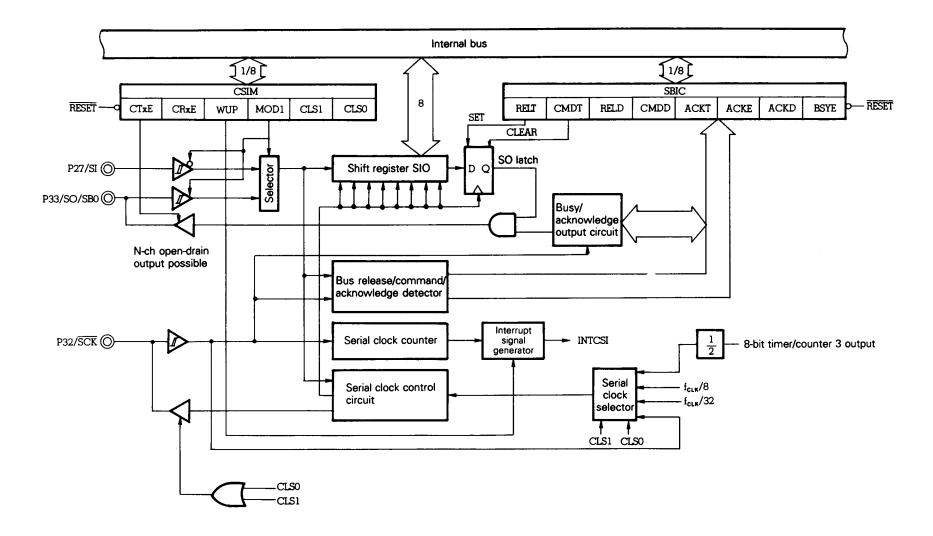

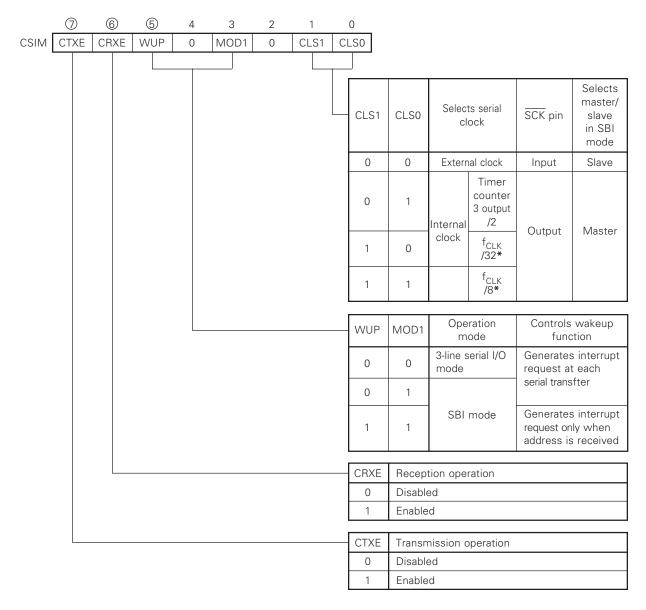

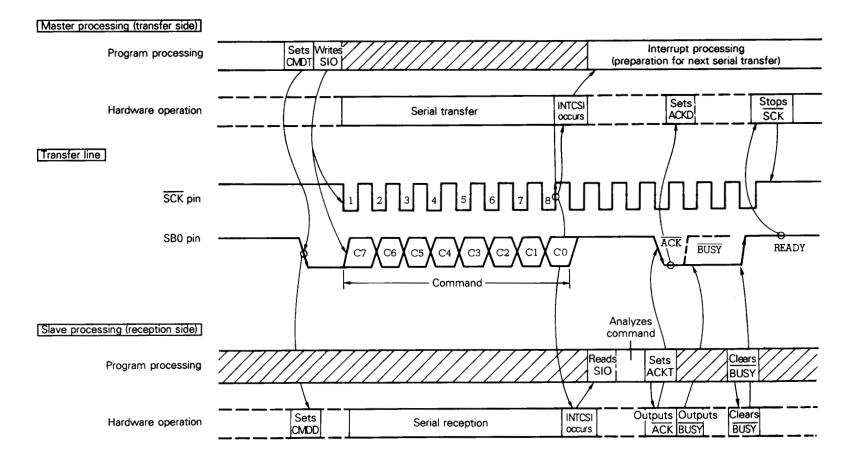

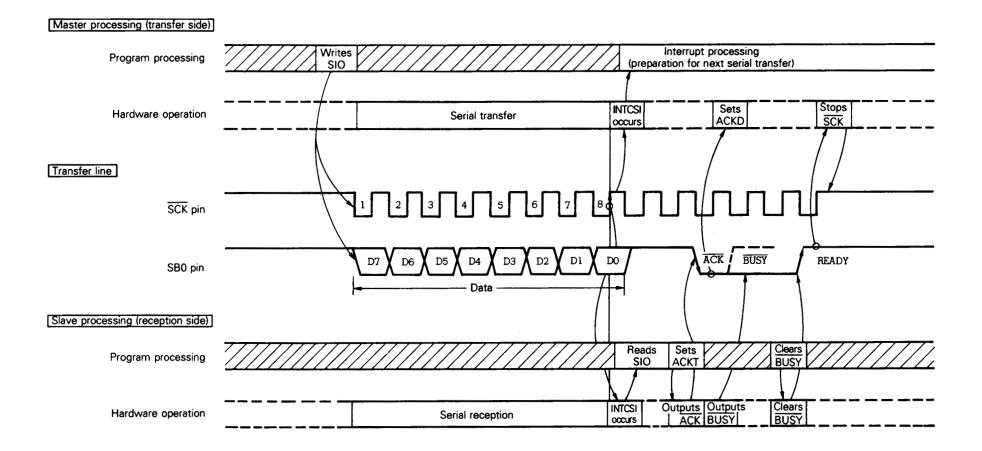

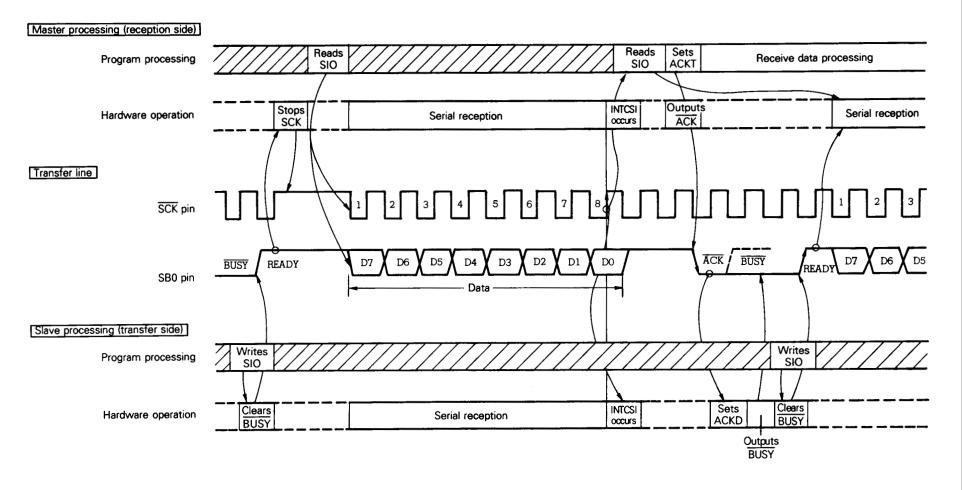

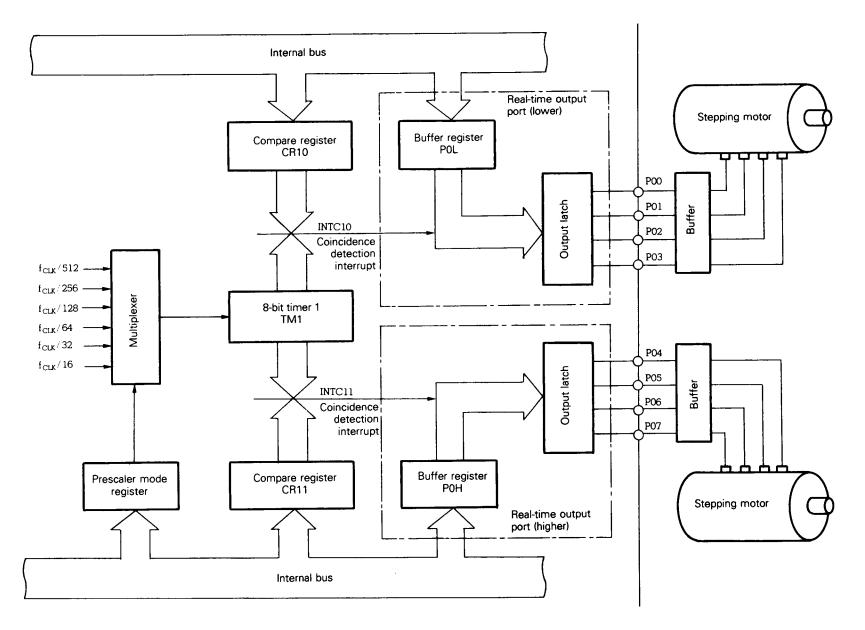

|      | P 12 C                                          | LOCK-SYNCHRONIZED SERIAL INTERFACE                                 |

|      |                                                 |                                                                    |

|      |                                                 | uration                                                            |

|      | -                                               | I Registers                                                        |

|      | 12.3.1                                          | Clock-synchronized serial interface mode register (CSIM)           |

|      | 12.3.2                                          | Serial bus interface control register (SBIC)                       |

| 12 4 |                                                 | Serial I/O Mode                                                    |

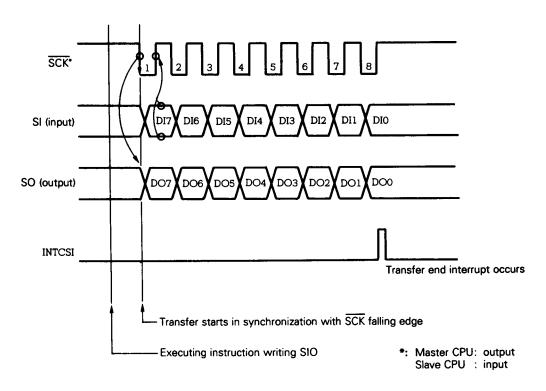

| 16.1 | 12.4.1                                          | Basic operation timing                                             |

|      | 12.4.2                                          | Operations when only transfer is enabled                           |

|      | 12.4.3                                          | Operation when only reception is enabled                           |

|      | 12.4.4                                          | Operations when both transfer and reception are enabled            |

|      | 12.4.5                                          | Corrective action, when serial clock is asynchronous with shifting |

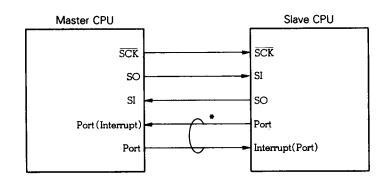

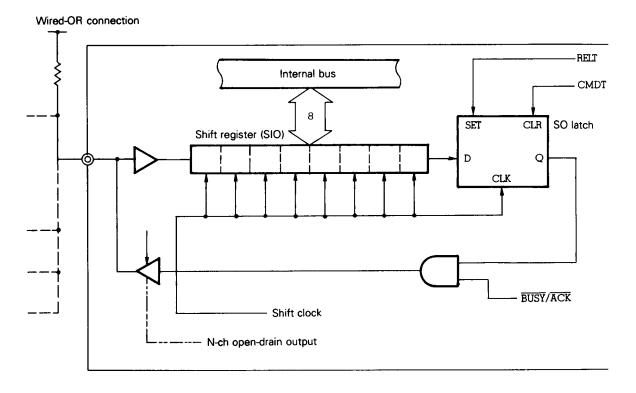

| 12.5 |                                                 | ode                                                                |

|      | 12.5.1                                          | Features of SBI                                                    |

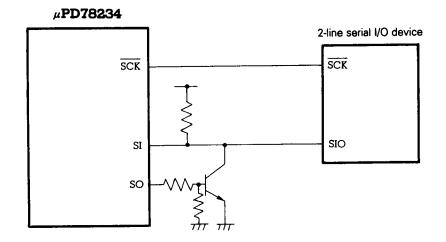

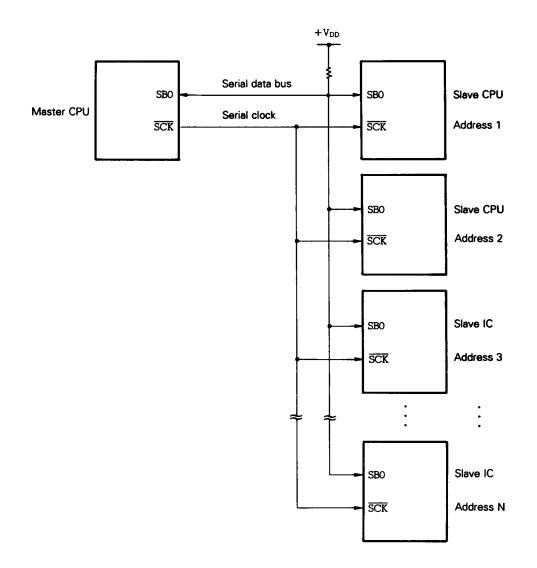

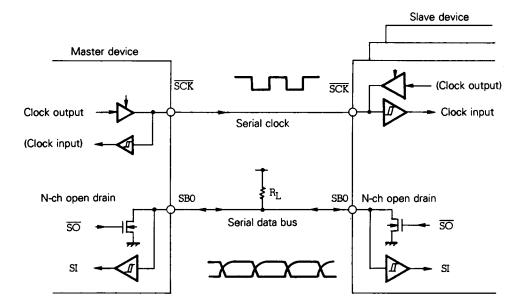

|      | 12.5.2                                          | Serial interface configuration                                     |

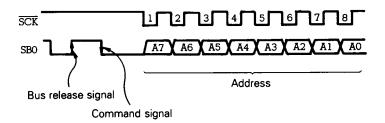

|      | 12.5.3                                          | Address coincidence detection                                      |

|      | 12.5.4                                          | SBI mode control registers                                         |

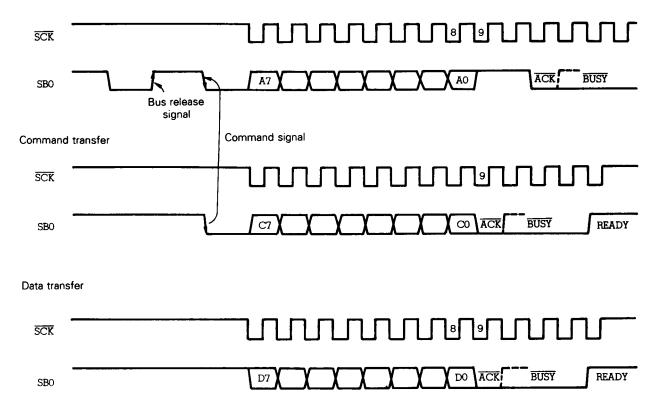

| 12.6 |                                                 | mmunication Operation and Signals                                  |

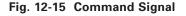

|      | 12.6.1                                          | Bus release signal (REL)                                           |

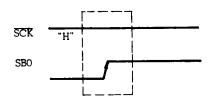

|      | 12.6.2                                          | Command signal (CMD)                                               |

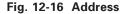

|      | 12.6.3                                          | Address                                                            |

|      | 12.6.4                                          | Command and data                                                   |

|      | 1005                                            | Acknowledge signal (ACK)                                           |

|      | 12.6.5                                          |                                                                    |

|      | 12.6.5<br>12.6.6                                | BUSY and READY signals                                             |

|      |                                                 | BUSY and READY signals                                             |

|      | 12.6.6                                          | Signals                                                            |

|      | 12.6.6<br>12.6.7                                | Signals<br>Communication operation                                 |

|      | 12.6.6<br>12.6.7<br>12.6.8<br>12.6.9            | Signals<br>Communication operation<br>Clearing BUSY                |

|      | 12.6.6<br>12.6.7<br>12.6.8<br>12.6.9<br>12.6.10 | Signals<br>Communication operation                                 |

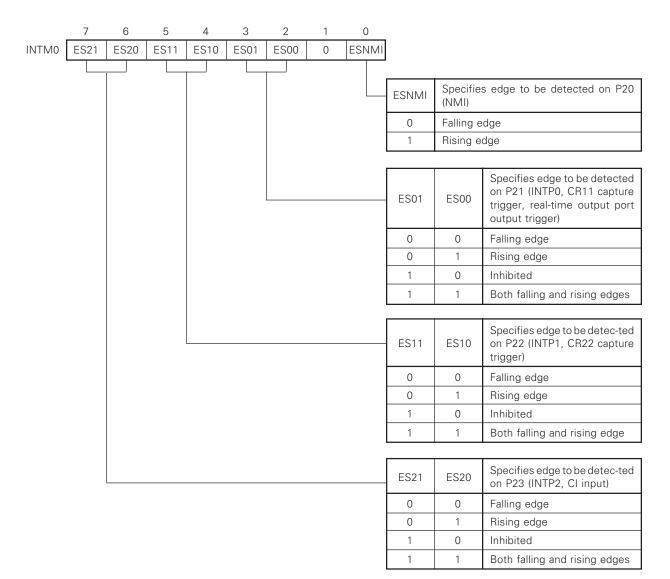

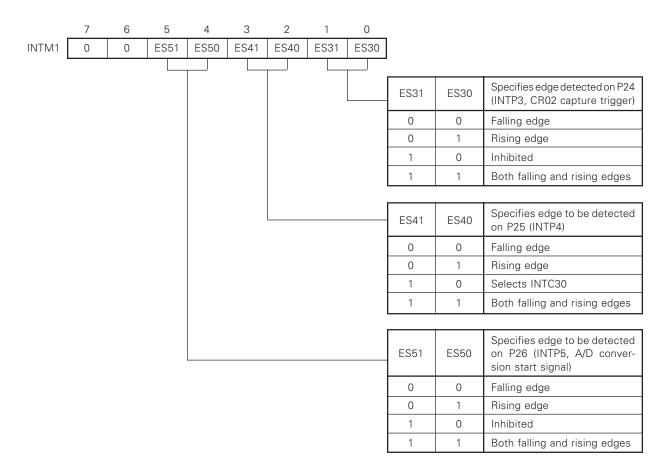

| СНАРТИ         | ER 13  | EDGE DETECTION FUNCTION                                      | 407               |

|----------------|--------|--------------------------------------------------------------|-------------------|

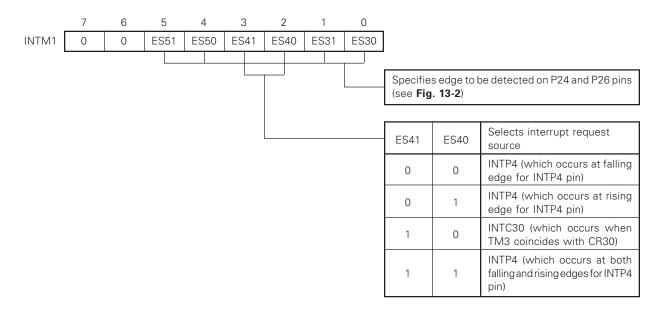

| 13.1           | Exter  | nal Interrupt Mode Registers (INTM0 and INTM1)               | 407               |

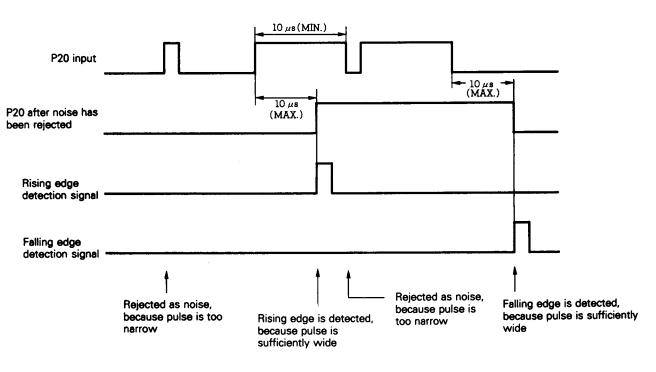

| 13.2           | Edge   | Detection on Pin P20                                         | 410               |

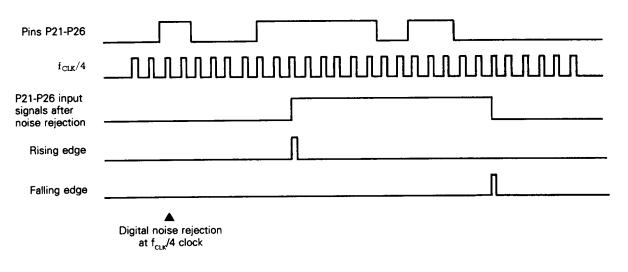

| 13.3           | Edge   | Detection on Pin P21 through P26                             | 411               |

| 13.4           | Notes  | -<br>-                                                       | 414               |

|                |        |                                                              |                   |

| СНАРТИ         | ER 14  | INTERRUPT FUNCTIONS                                          | 417               |

| 14.1           | Interr | upt Request Sources                                          | 418               |

|                | 14.1.1 | Software interrupt request                                   | 419               |

|                | 14.1.2 | Nonmaskable interrupt request                                | 419               |

|                | 14.1.3 | Maskable interrupt request                                   | 419               |

|                | 14.1.4 | Selecting interrupt source                                   | 420               |

| 14.2           | Interr | upt Processing Control Registers                             | 422               |

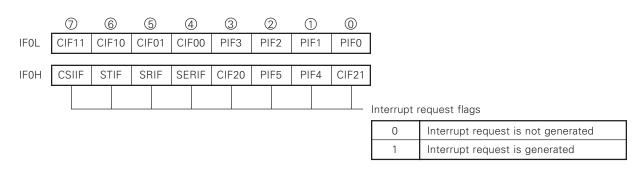

|                | 14.2.1 | Interrupt request flag register (IF0)                        | 423               |

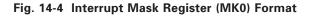

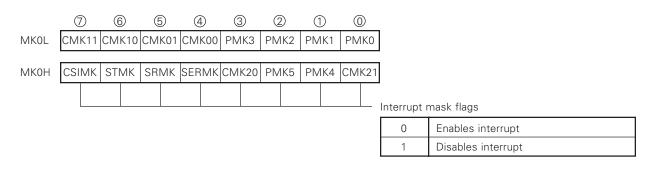

|                | 14.2.2 | Interrupt mask register (MK0)                                | 423               |

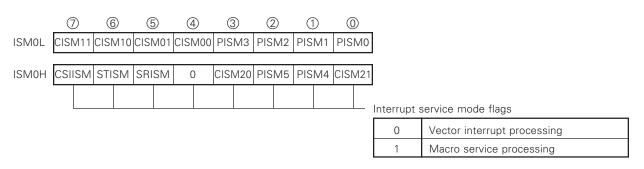

|                | 14.2.3 | Interrupt service mode register (ISM0)                       | 424               |

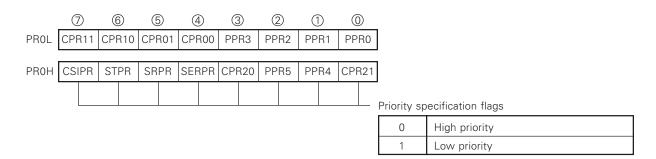

|                | 14.2.4 | Priority specification flag register (PR0)                   | 424               |

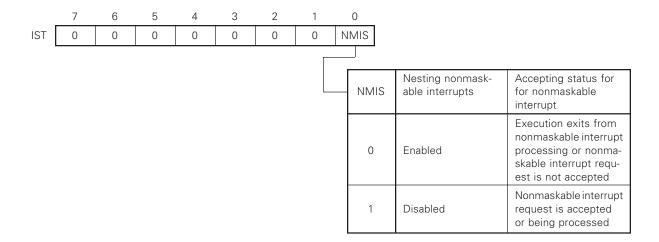

|                | 14.2.5 | Interrupt status register (IST)                              | 425               |

|                | 14.2.6 | Program status word (PSW)                                    | 426               |

| 14.3           | Interr | upt Processing                                               | 427               |

|                | 14.3.1 | Accepting software interrupt                                 | 427               |

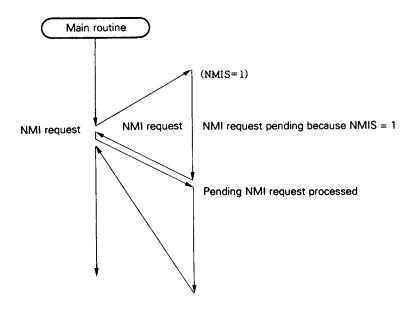

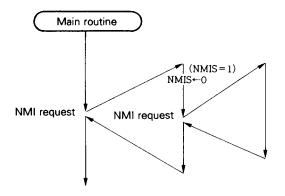

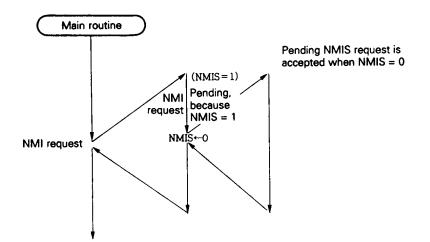

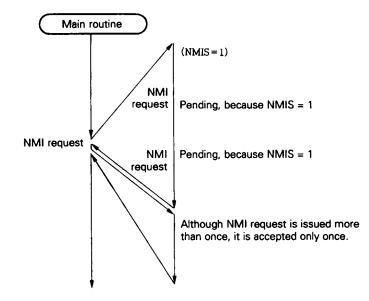

|                | 14.3.2 | Accepting nonmaskable interrupt                              | 427               |

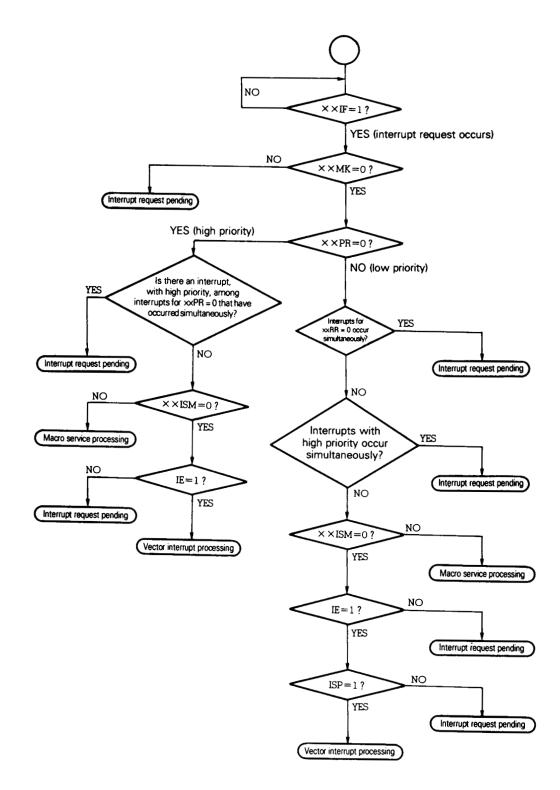

|                | 14.3.3 | Accepting maskable interrupt                                 | 431               |

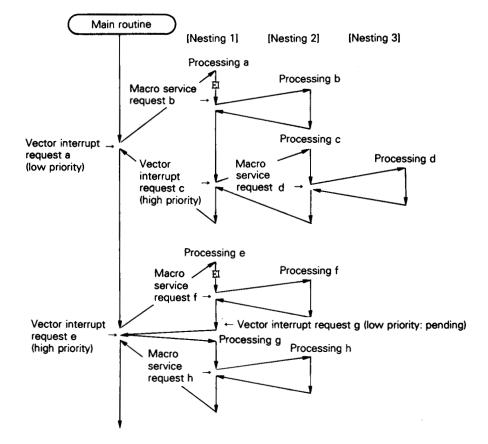

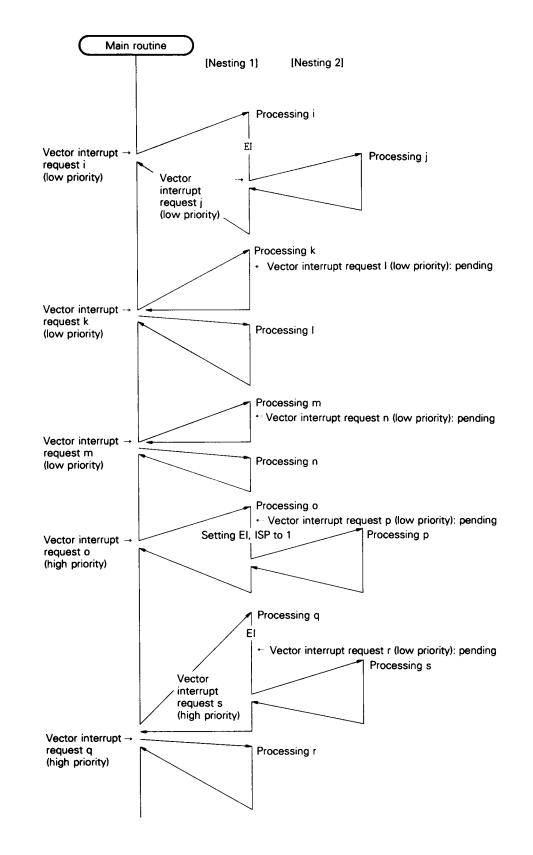

|                | 14.3.4 | Nested interrupt processing                                  | 433               |

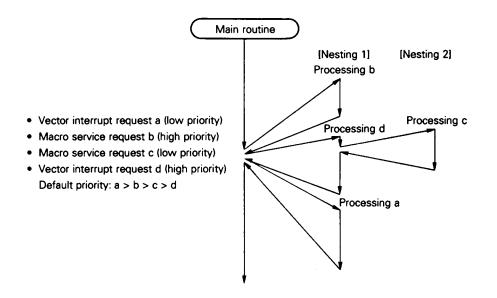

|                | 14.3.5 | Interrupt request and macro service pending                  | 436               |

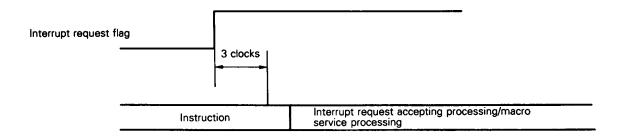

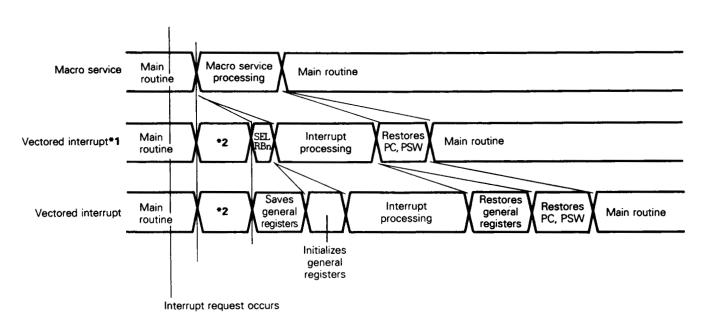

|                | 14.3.6 | Interrupt and macro service operation timing                 | 438               |

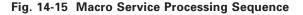

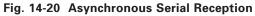

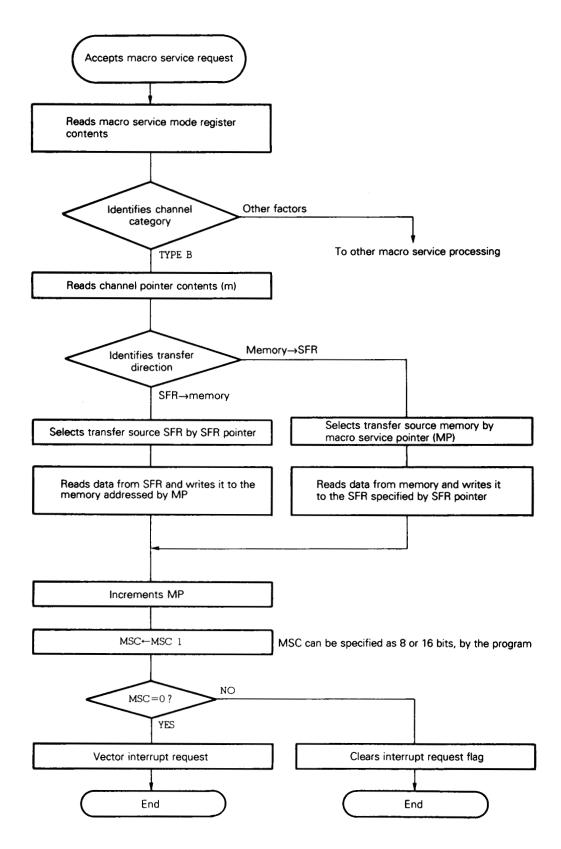

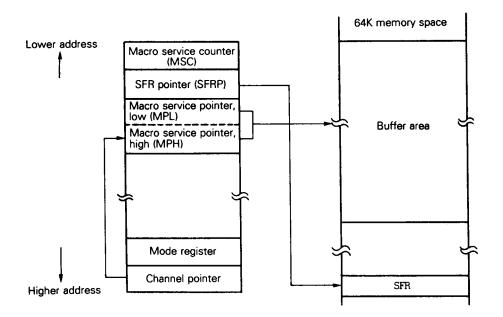

| 14.4           | Macro  | o Service Function                                           | 442               |

|                | 14.4.1 | Macro service outline                                        | 442               |

|                | 14.4.2 | Macro service types                                          | 443               |

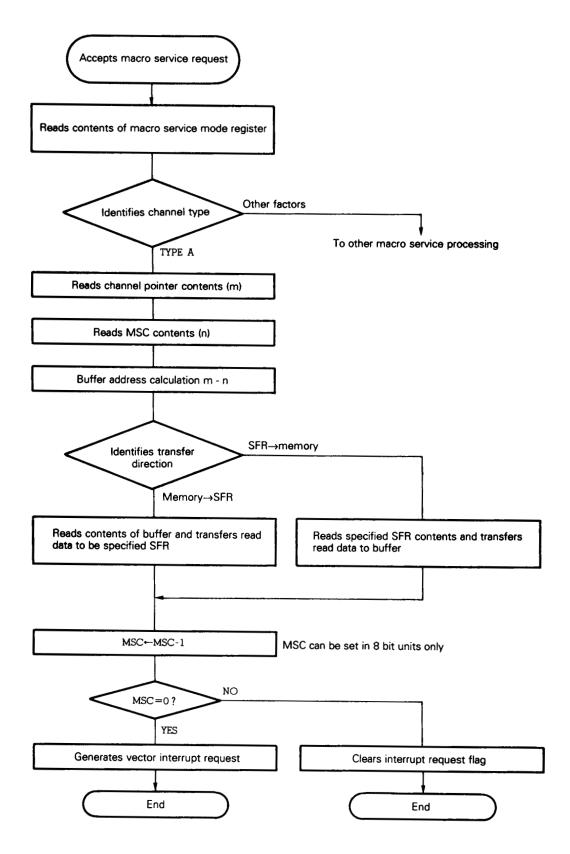

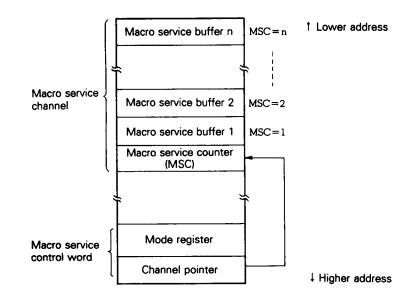

|                | 14.4.3 | Macro service basic operation                                | 445               |

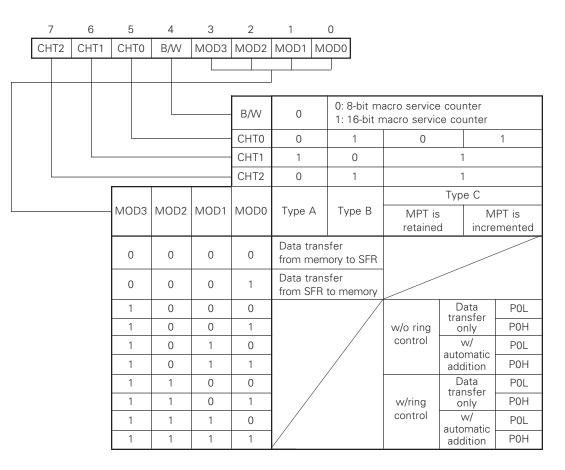

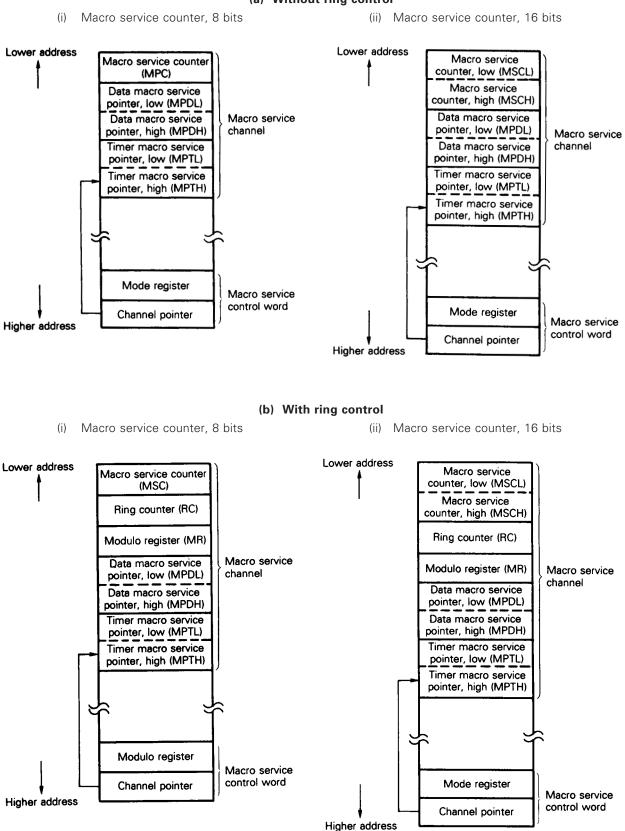

|                | 14.4.4 | Macro service control register                               | 446               |

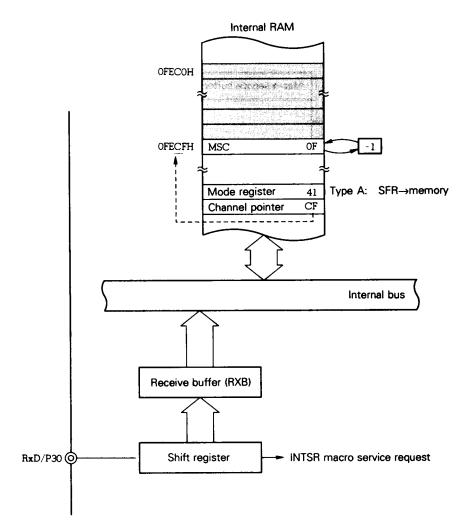

|                | 14.4.5 | Macro service type A                                         | 448               |

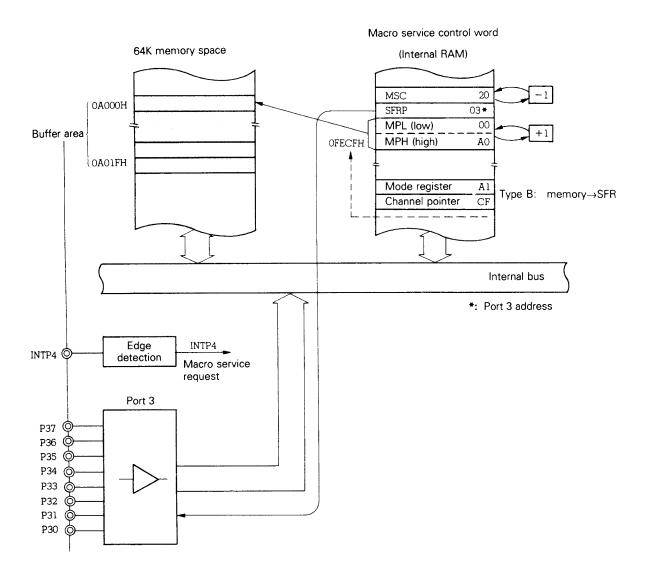

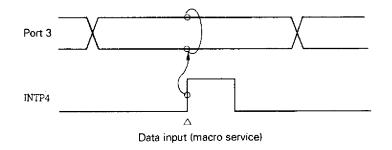

|                | 14.4.6 | Macro service type B                                         | 453               |

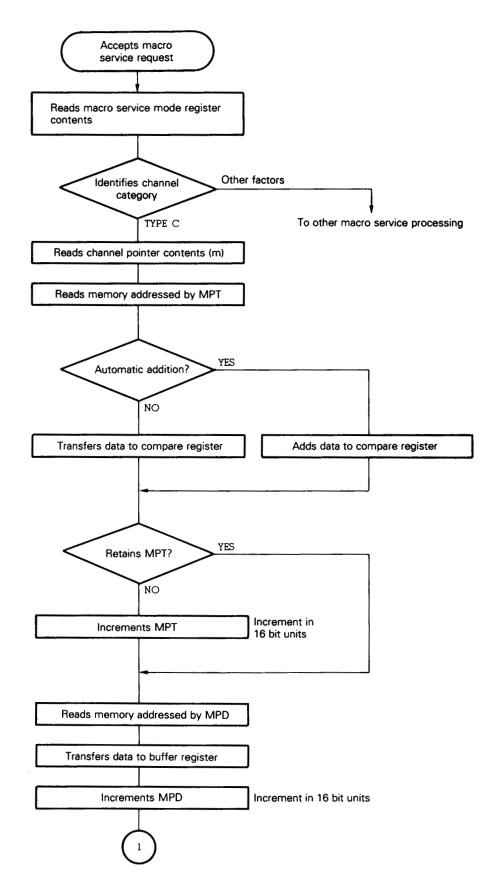

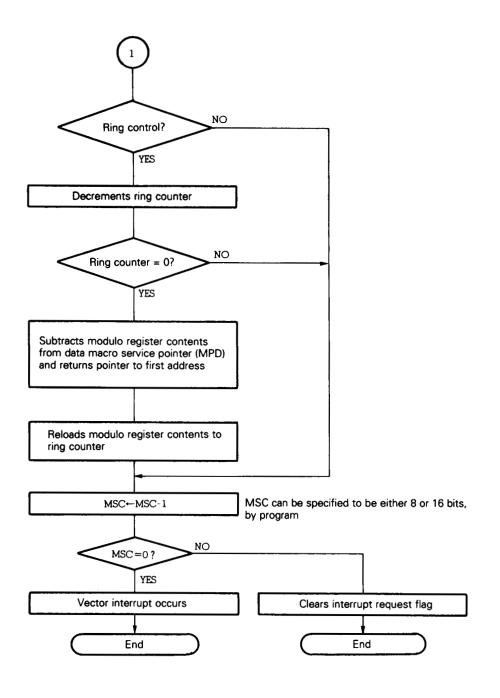

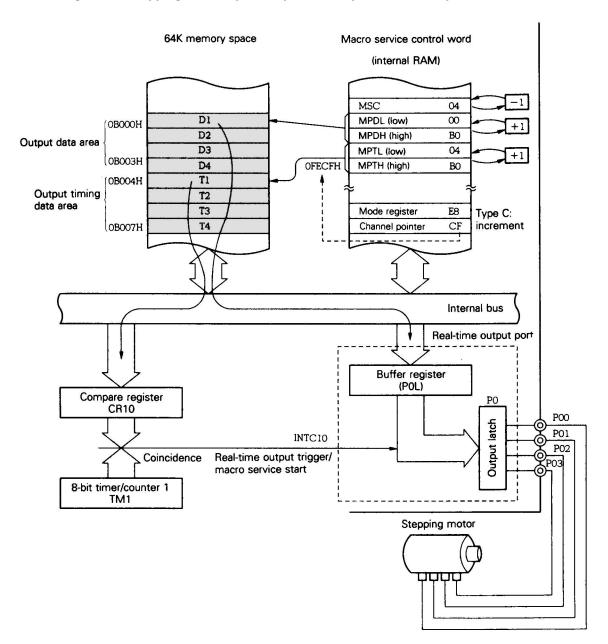

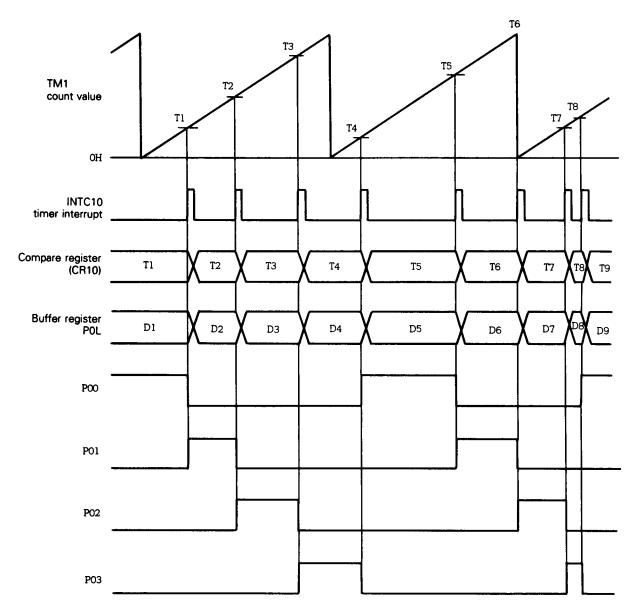

|                | 14.4.7 | Macro service type C                                         | 458               |

| 14.5           | Notes  | 5                                                            | 472               |

| CUADT          | D 15   |                                                              | 475               |

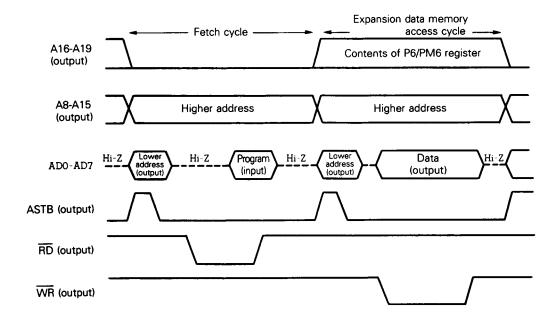

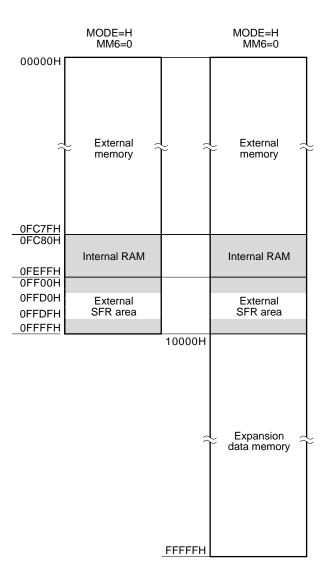

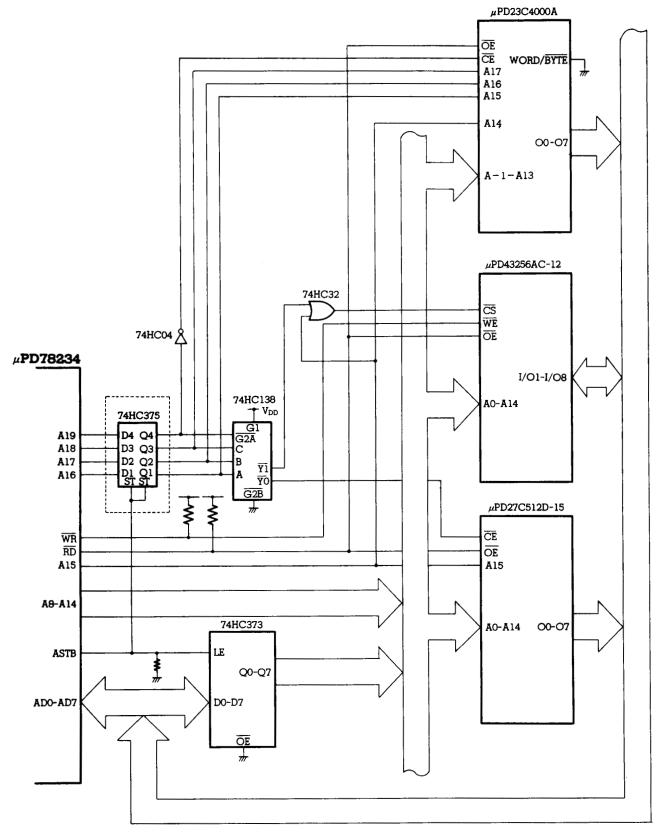

| CHAPTI<br>15 1 |        | LOCAL BUS INTERFACE FUNCTION                                 | 475<br>476        |

| 15.1           | 15.1.1 | OI Registers<br>Memory expansion mode register (MM)          | <b>470</b><br>476 |

|                | 15.1.1 |                                                              | 470               |

|                | 15.1.2 |                                                              | 477               |

| 15 2           |        |                                                              | 477<br><b>478</b> |

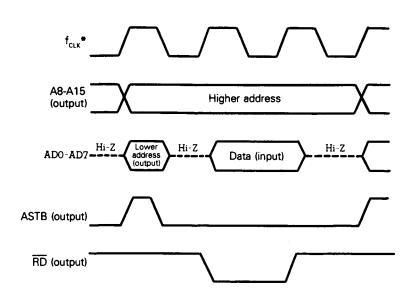

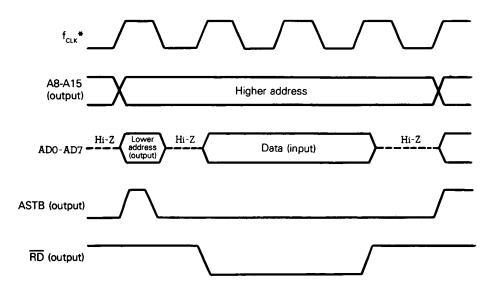

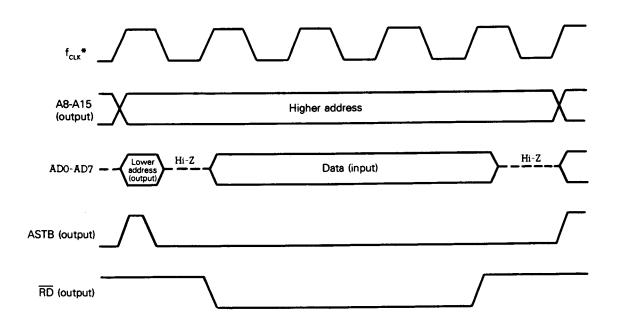

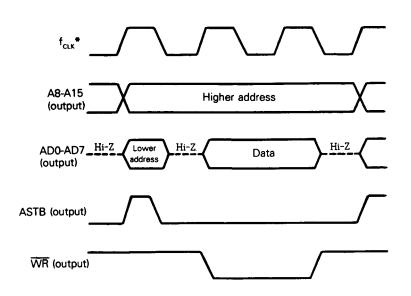

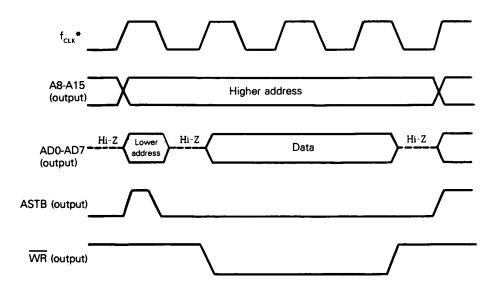

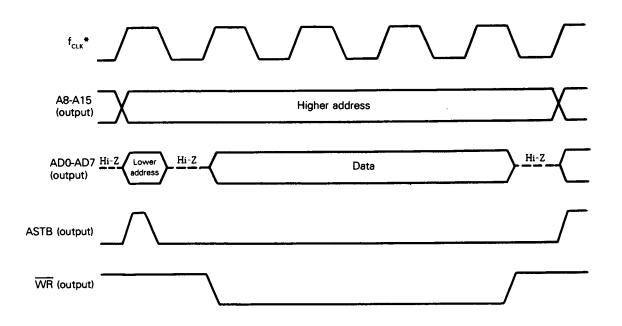

| 15.2           | 15.2.1 | bry Expansion Function<br>External memory expansion function | <b>478</b>        |

|                | 15.2.1 |                                                              | 478               |

|                | 15.2.2 |                                                              | 480<br>482        |

|                | 15.2.3 |                                                              | 482<br>482        |

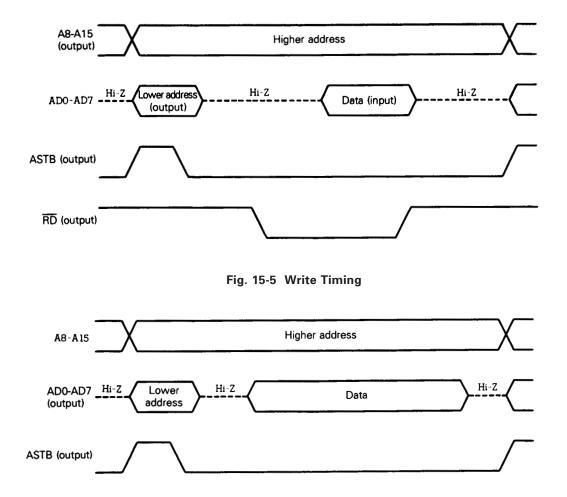

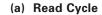

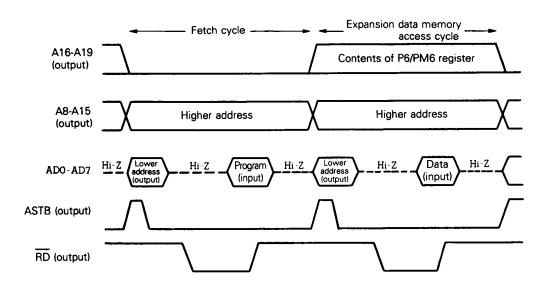

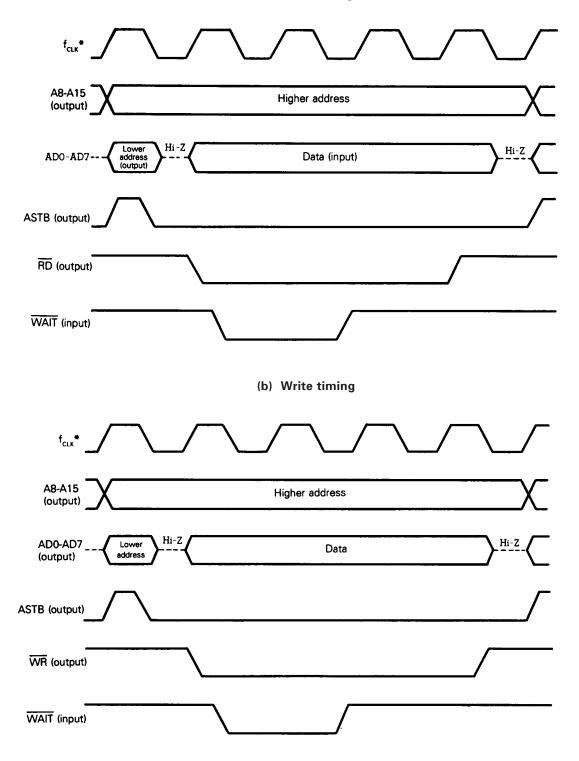

|                | 15.2.4 |                                                              | 488               |

|                | 10.2.0 |                                                              | -00               |

| 15.3   | Internal ROM High-Speed Fetch Function            | 490 |

|--------|---------------------------------------------------|-----|

|        | Wait Function                                     | 490 |

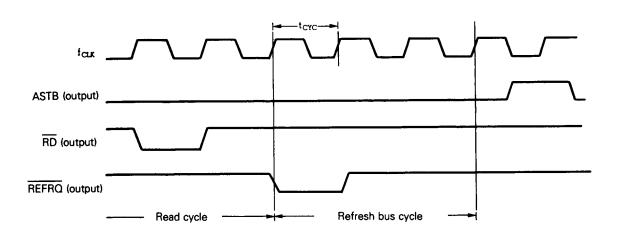

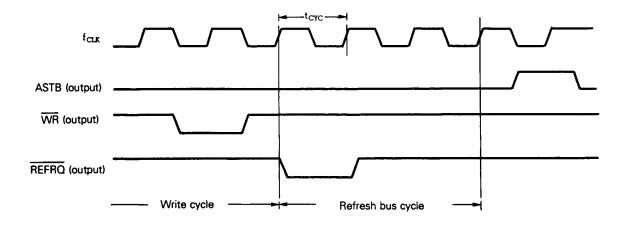

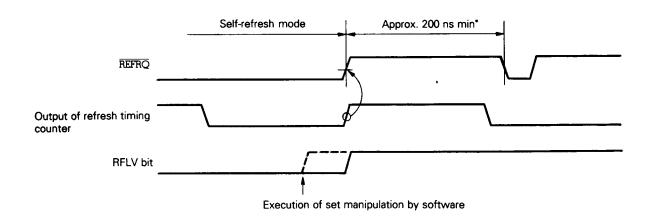

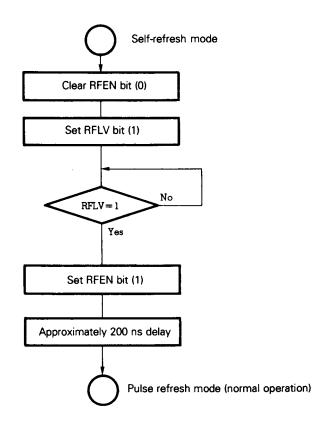

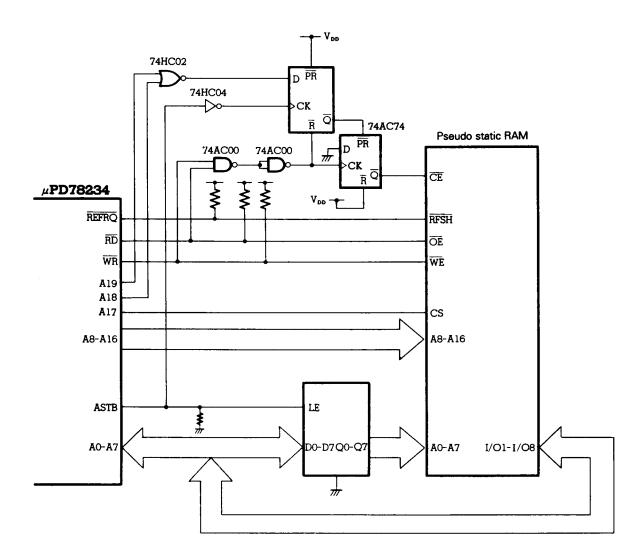

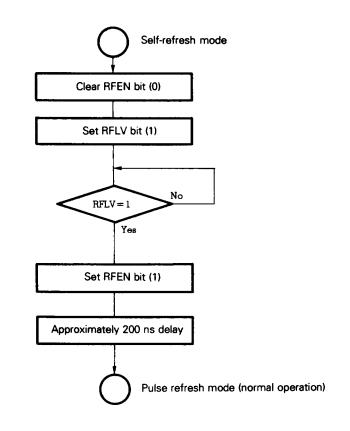

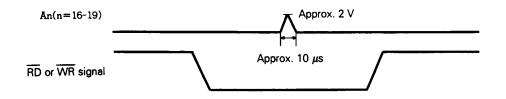

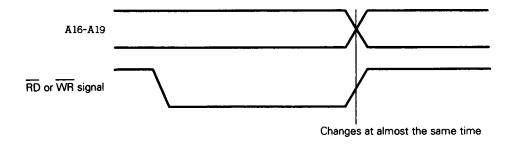

| 15.5   | Pseudo Static RAM Refresh Function                | 500 |

|        | 15.5.1 Function                                   | 500 |

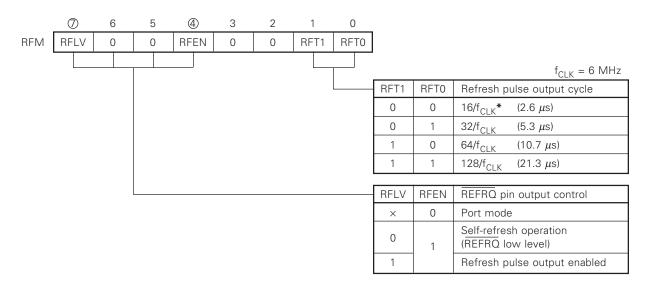

|        | 15.5.2 Refresh mode register (RFM)                | 501 |

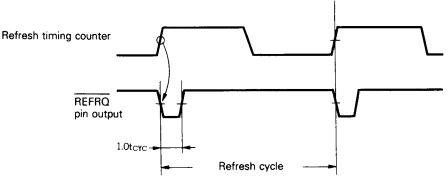

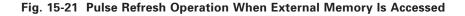

|        | 15.5.3 Operation                                  | 502 |

|        | 15.5.4 Example for connecting pseudo static RAM   | 506 |

| 15.6   | Note                                              | 507 |

| СНАРТЕ | R 16 STANDBY FUNCTIONS                            | 511 |

|        | Configuration and Functions                       | 511 |

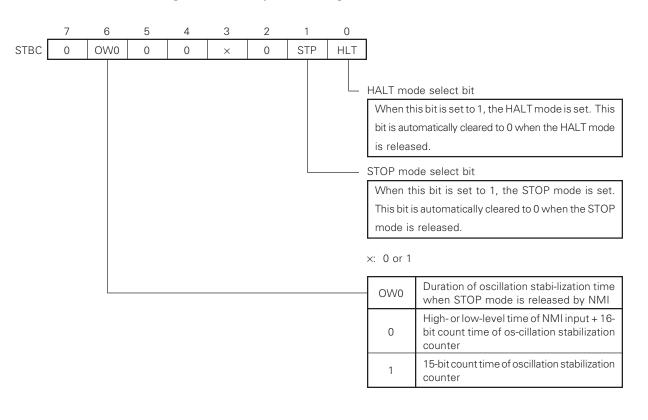

|        | Standby Control Register (STBC)                   | 513 |

|        | HALT Mode                                         | 514 |

|        | 16.3.1 Setting and operation of HALT mode         | 514 |

|        | 16.3.2 Releasing HALT mode                        | 515 |

| 16.4   | STOP Mode                                         | 518 |

|        | 16.4.1 Setting and operations of STOP mode        | 518 |

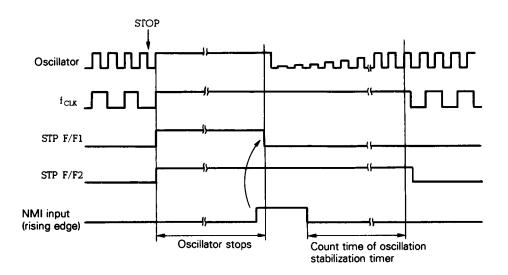

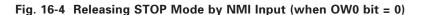

|        | 16.4.2 Releasing STOP mode                        | 519 |

|        | 16.4.3 Notes on using STOP mode                   | 522 |

| 16.5   | Notes                                             | 525 |

|        |                                                   |     |

| CHAPTE | R 17 RESET FUNCTION                               | 527 |

|        | Reset Function                                    | 527 |

| 17.2   | Note                                              | 532 |

| СНАРТЕ | R 18 APPLICATION EXAMPLES                         | 533 |

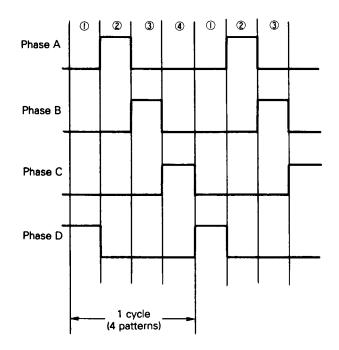

| 18.1   | Open-Loop Control of Stepping Motor               | 533 |

|        | Serial Communication with Several Devices         | 535 |

|        |                                                   |     |

| СНАРТЕ | R 19 PROGRAMMING $\mu$ PD78P238                   | 537 |

| 19.1   | Operation Mode                                    | 537 |

| 19.2   | Writing PROM                                      | 538 |

| 19.3   | PROM Reading Procedure                            | 540 |

| 19.4   | Note                                              | 541 |

|        |                                                   |     |

| CHAPTE |                                                   | 543 |

| 20.1   | Legend                                            | 543 |

|        | 20.1.1 Operand field                              | 543 |

|        | 20.1.2 Operation field                            | 545 |

| ~ ~ ~  | 20.1.3 Flag field                                 | 545 |

|        | Operation Lists                                   | 546 |

| 20.3   | Classification of Instructions by Addressing Mode | 557 |

| APPEND     | DIX A   | 78K/II SERIES PRODUCT LIST                      | 561        |

|------------|---------|-------------------------------------------------|------------|

| APPEND     | ых в п  | DEVELOPMENT TOOLS                               | 569        |

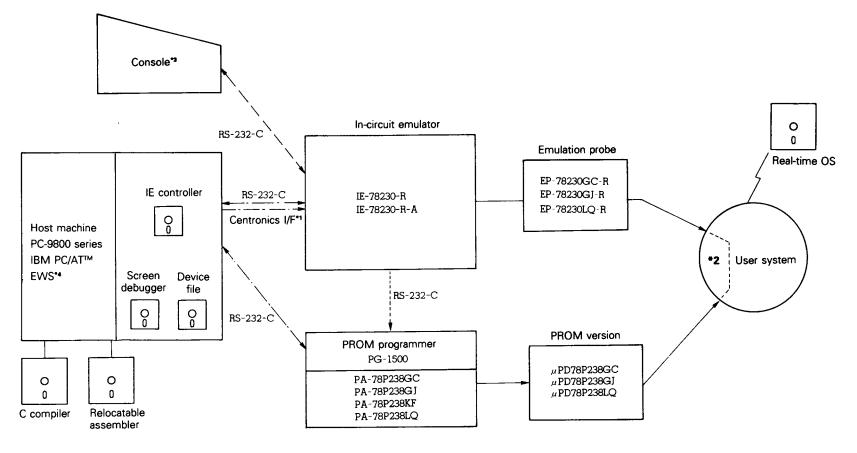

| B.1        |         | vare                                            | 571        |

| <b>B.2</b> | Softw   | are                                             | 573        |

|            | B.2.1   | Language processing software                    | 573        |

|            | B.2.2   | Software for in-circuit emulator                | 576        |

|            | B.2.3   | Software for PROM programmer                    | 577        |

|            | B.2.4   | OS for IBM PC                                   | 577        |

| B.3        | Upgra   | Inding Other In-Circuit Emulators to IE-78230-R | 578        |

|            | B.3.1   | Upgrading to IE-78230-R-A                       | 578        |

|            | B.3.2   | Upgrading system to IE-78230-R                  | 579        |

| APPEND     |         | SOFTWARE FOR EMBEDDED APPLICATIONS              | 581        |

| C.1        | Real-T  | Time OS                                         | 581        |

| C.2        | Fuzzy   | Inference Development Support System            | 582        |

| APPEND     |         | REGISTER INDEX                                  | 583        |

| D.1        |         | ter Index (Alphabetical order)                  | 583        |

|            |         |                                                 |            |

| APPEND     | DIX E I | NDEX                                            | 585        |

| E.1        | Alpha   | betical Glossary                                | 585        |

| E.2        | Symb    | ols                                             | <b>594</b> |

$\star$

# FIGURE (1/10)

| Fig. No. | Title                                               | Page |

|----------|-----------------------------------------------------|------|

| 2-1      | I/O Circuit List                                    |      |

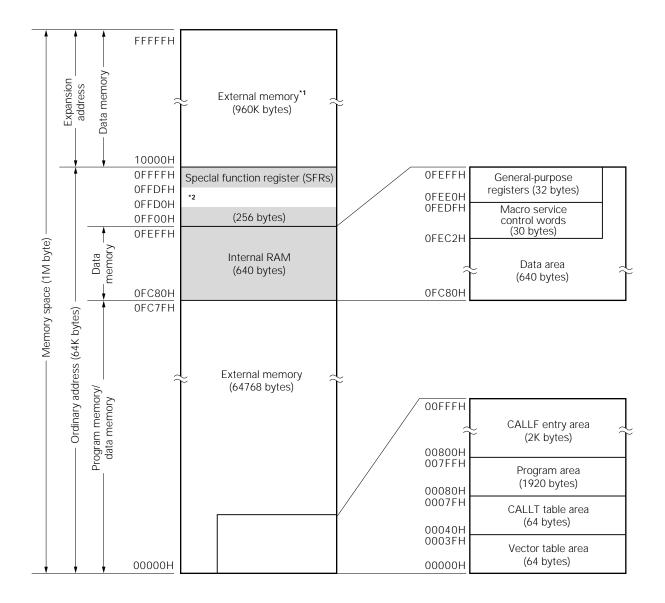

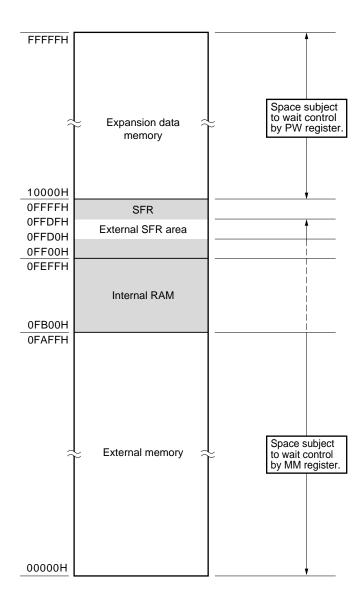

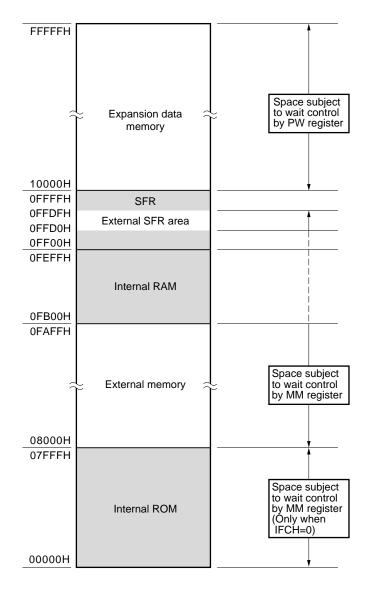

| 3-1      | μPD78233 Memory Map                                 |      |

| 3-2      | μPD78234 Memory Map                                 |      |

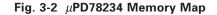

| 3-3      | μPD78237 Memory Map                                 |      |

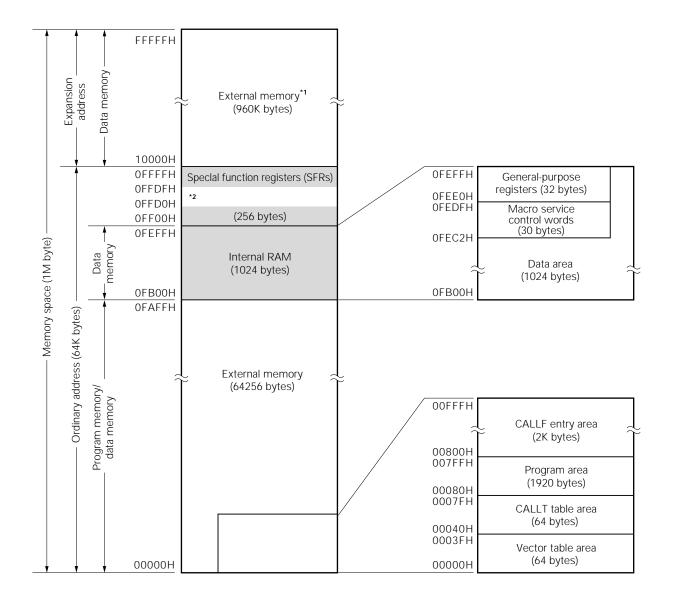

| 3-4      | μPD78238 Memory Map                                 |      |

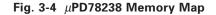

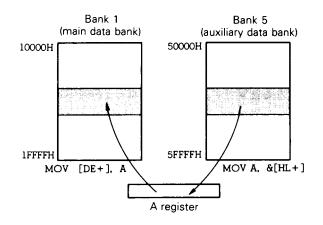

| 3-5      | Data Transfer between Banks                         |      |

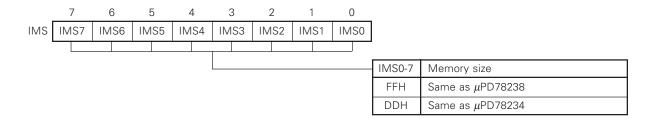

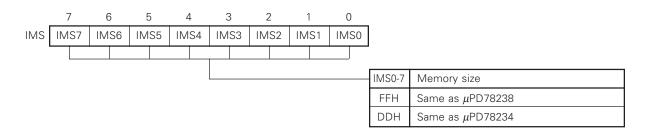

| 3-6      | Memory Size Select Register                         |      |

| 3-7      | Program Counter Configuration                       |      |

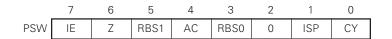

| 3-8      | Program Status Word Configuration                   |      |

| 3-9      | Stack Pointer Configuration                         |      |

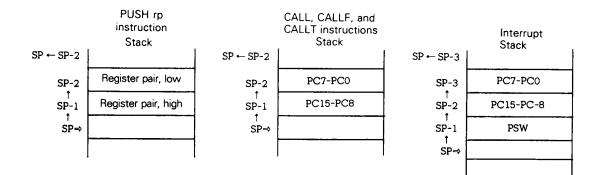

| 3-10     | Data Saved to Stack Area                            |      |

| 3-11     | Data Restored from Stack Area                       |      |

| 3-12     | General-Purpose Register Configuration              |      |

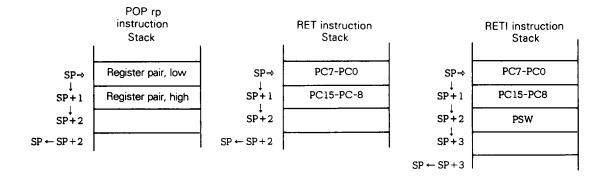

| 4-1      | Clock Generator Circuit Configuration               |      |

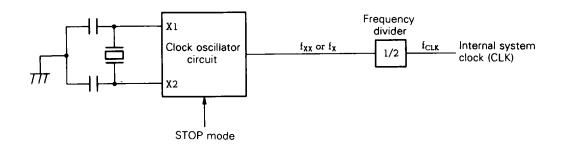

| 4-2      | External Circuit for Crystal Oscillator Circuit     |      |

| 4-3      | Extracting Signal when External Clock is Input      | 61   |

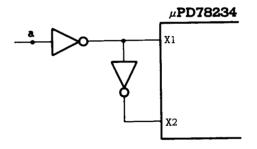

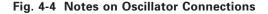

| 4-4      | Notes on Oscillator Connections                     |      |

| 4-5      | Incorrect Oscillator Connection Example             |      |

| 5-1      | Port Configuration                                  |      |

| 5-2      | Port 0 Configuration                                |      |

| 5-3      | Port 0 Mode Register Format                         |      |

| 5-4      | Port Specified in Output Mode                       |      |

| 5-5      | Transistor Driving Example                          |      |

| 5-6      | P10 and P11 (Port 1) Configuration                  |      |

| 5-7      | P12 through P17 Configuration (Port 1)              |      |

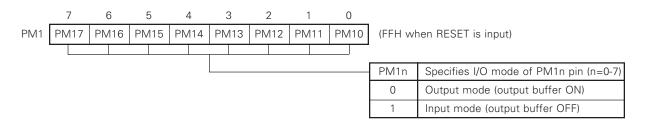

| 5-8      | Port 1 Mode Register Format                         |      |

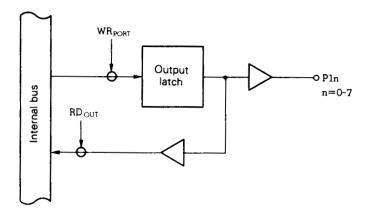

| 5-9      | Port Specified in Output Mode                       |      |

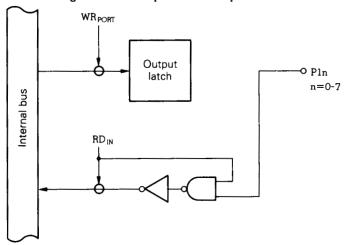

| 5-10     | Port Specified in Input Mode                        |      |

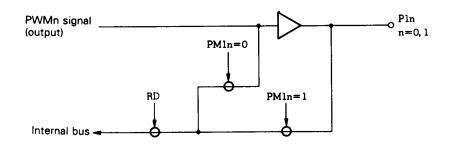

| 5-11     | To Output PWM Signal                                |      |

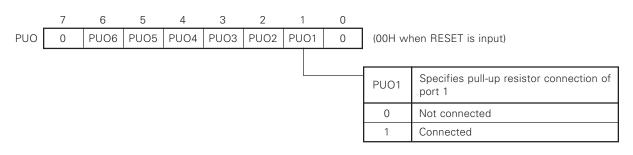

| 5-12     | Pull-up Resistor Option Register Format             |      |

| 5-13     | Specifying Pull-up Resistor Connection (Port 1)     |      |

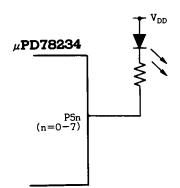

| 5-14     | LED Direct Drive                                    |      |

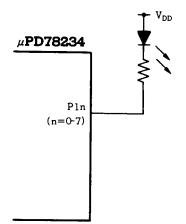

| 5-15     | Port 2 Configuration                                |      |

| 5-16     | Port Specified in Input Mode                        |      |

| 5-17     | Pull-up Resistor Option Register Format             |      |

| 5-18     | Specifying Connection for Pull-up Register (Port 2) |      |

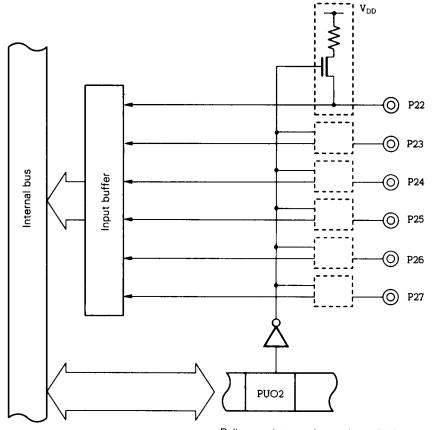

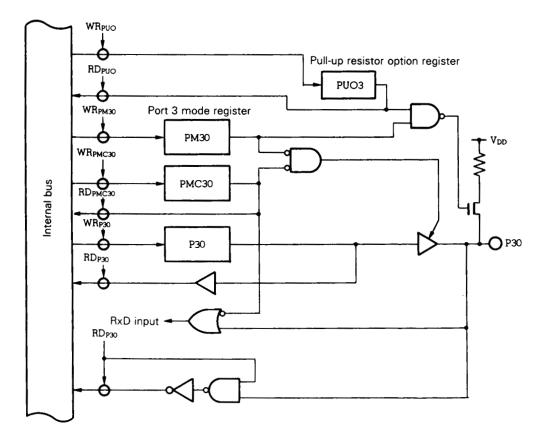

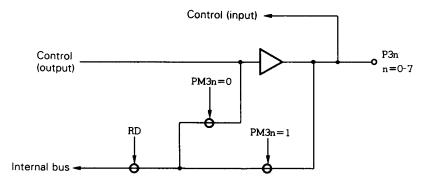

| 5-19     | P30 Configuration (Port 3)                          |      |

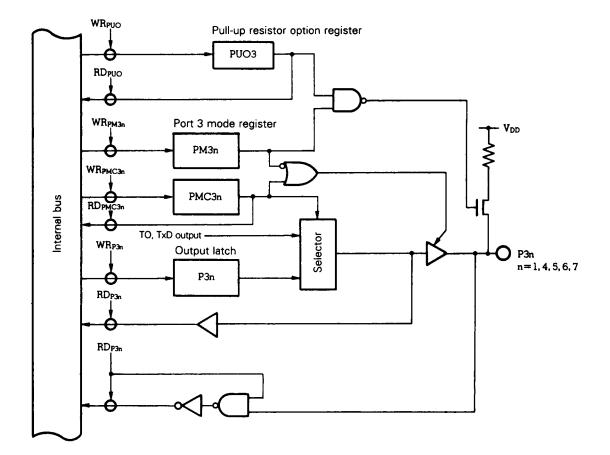

| 5-20     | Configuration for P31 and P34 through P37 (Port 3)  |      |

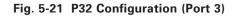

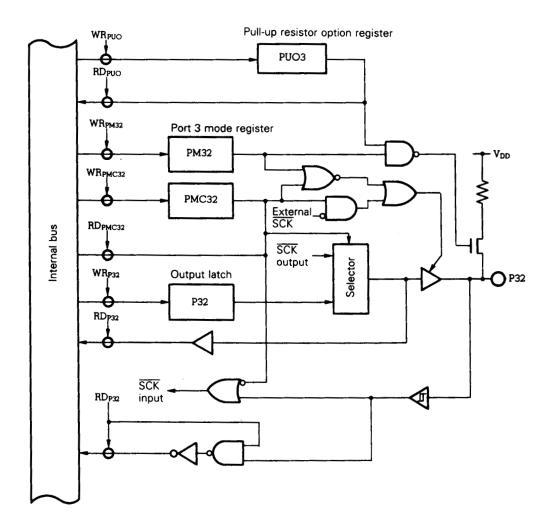

| 5-21     | P32 Configuration (Port 3)                          |      |

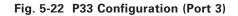

| 5-22     | P33 Configuration (Port 3)                          |      |

|          |                                                     |      |

# FIGURE (2/10)

| Fig. No. | Title                                                               | Page |

|----------|---------------------------------------------------------------------|------|

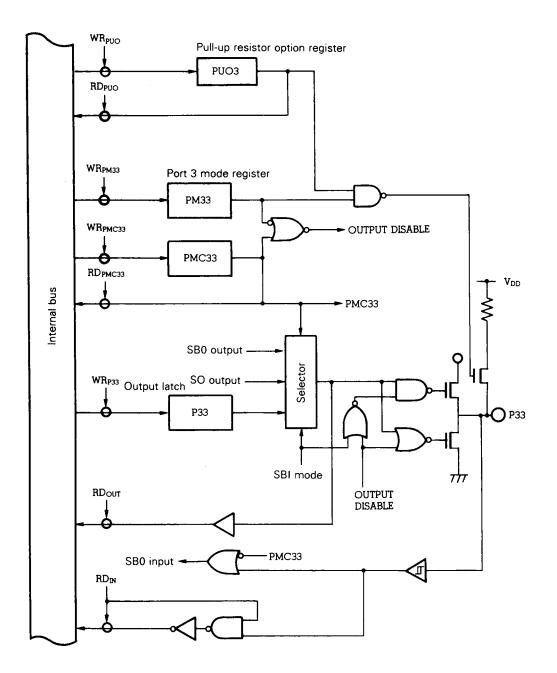

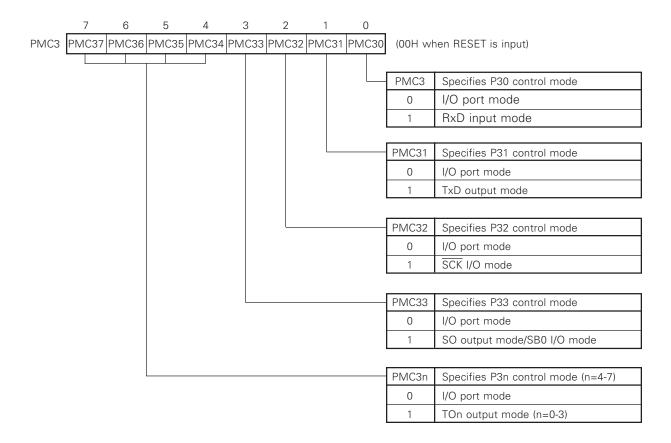

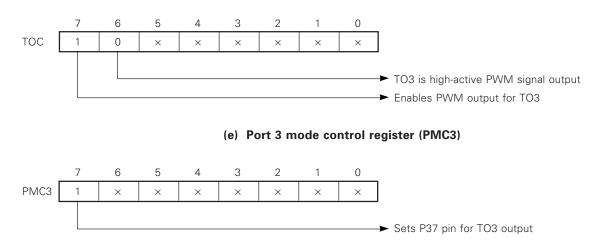

| 5-23     | Port 3 Mode Register Format                                         | 92   |

| 5-24     | Port 3 Mode Control Register (PMC3) Format                          | 93   |

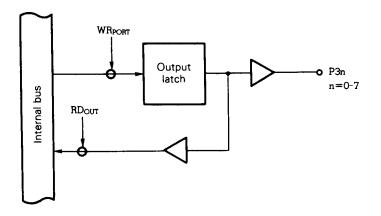

| 5-25     | Port Specified in Output Mode                                       | 94   |

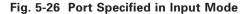

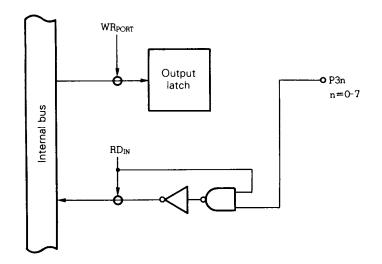

| 5-26     | Port Specified in Input Mode                                        | 95   |

| 5-27     | Port Specified in Control Mode                                      | 96   |

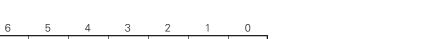

| 5-28     | Pull-up Resistor Option Register Format                             | 97   |

| 5-29     | Pull-up Resistor Connection (Port 3)                                | 98   |

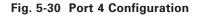

| 5-30     | Port 4 Configuration                                                | 99   |

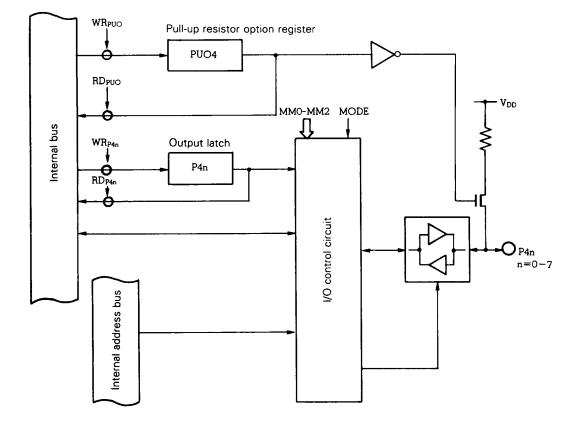

| 5-31     | Port Specified in Output Mode                                       | 100  |

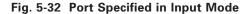

| 5-32     | Port Specified in Input Mode                                        | 101  |

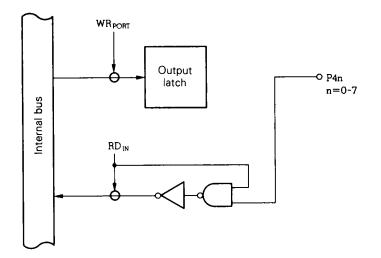

| 5-33     | Pull-up Resistor Option Resister Format                             | 102  |

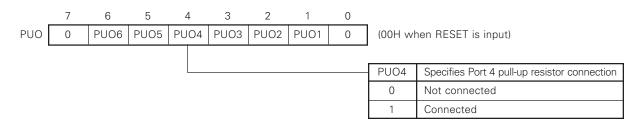

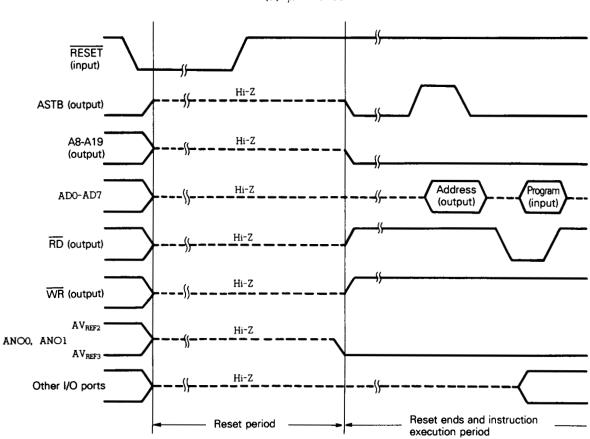

| 5-34     | Pull-up Resistor Connection (Port 4)                                | 103  |

| 5-35     | Direct Drive for LED                                                | 103  |

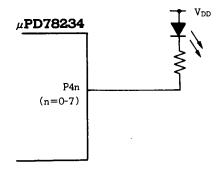

| 5-36     | Port 5 Configuration                                                | 104  |

| 5-37     | Port 5 Mode Register Format                                         | 105  |

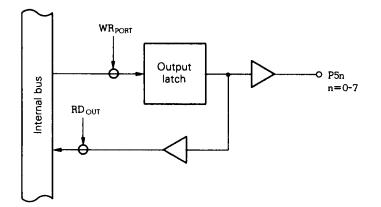

| 5-38     | Port Specified in Output Mode                                       | 106  |

| 5-39     | Port Specified in Input Mode                                        | 107  |

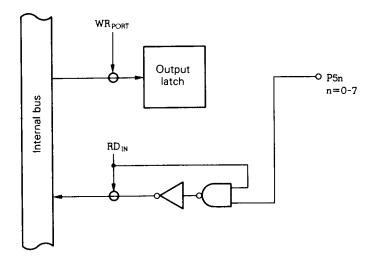

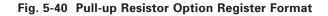

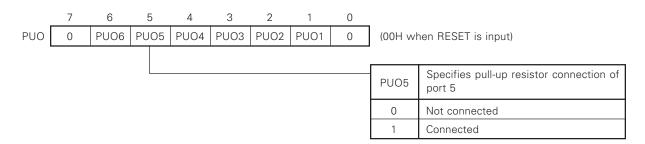

| 5-40     | Pull-up Resistor Option Register Format                             | 108  |

| 5-41     | Pull-up Resistor Connection (Port 5)                                | 109  |

| 5-42     | Direct Drive for LED                                                | 109  |

| 5-43     | P60-P63 Configuration (Port 6)                                      | 111  |

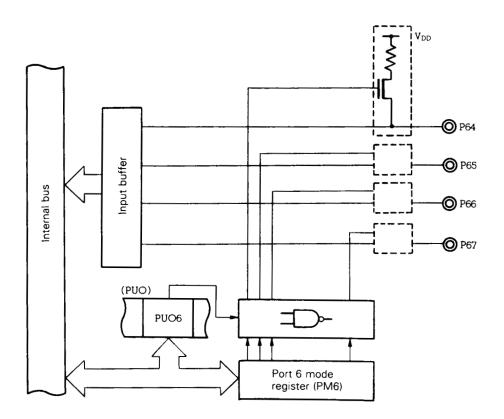

| 5-44     | P64 and P65 Configuration (Port 6)                                  | 112  |

| 5-45     | P66 Configuration (Port 6)                                          | 113  |

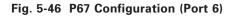

| 5-46     | P67 Configuration (Port 6)                                          | 114  |

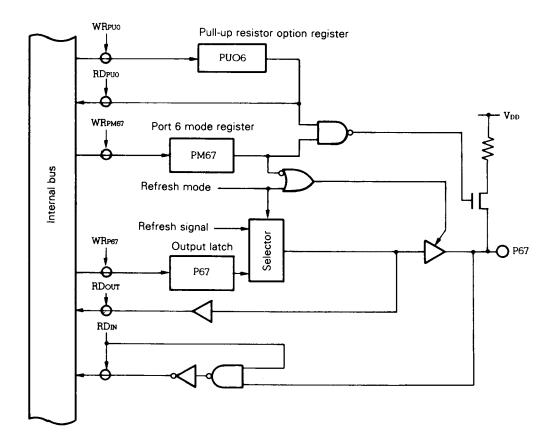

| 5-47     | Port 6 Mode Register Format                                         | 117  |

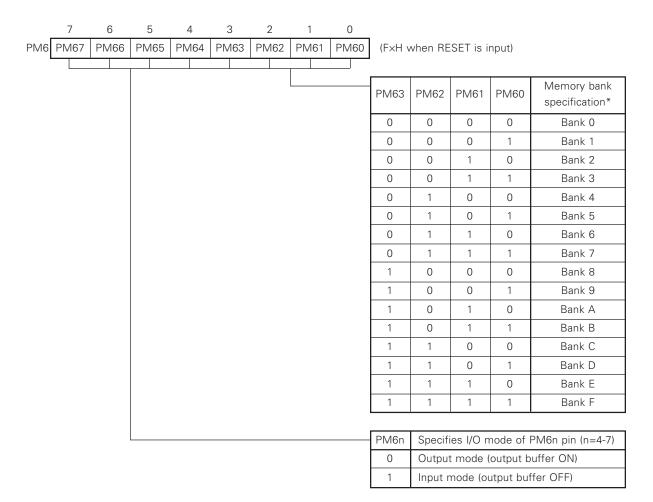

| 5-48     | Port Specified in Output Mode                                       | 118  |

| 5-49     | Port Specified in Input Mode                                        | 119  |

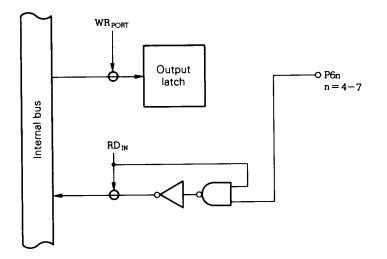

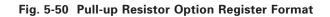

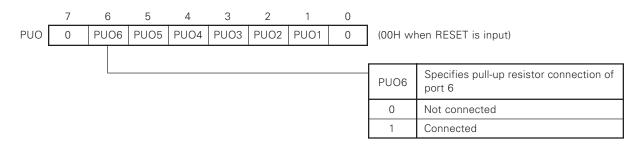

| 5-50     | Pull-up Resistor Option Register Format                             | 120  |

| 5-51     | Pull-up Resistor Connection (Port 6)                                | 120  |

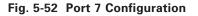

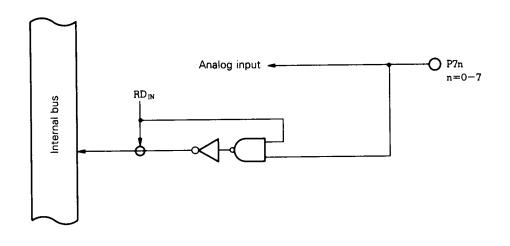

| 5-52     | Port 7 Configuration                                                | 121  |

| 5-53     | Port Specified in Input Mode                                        | 122  |

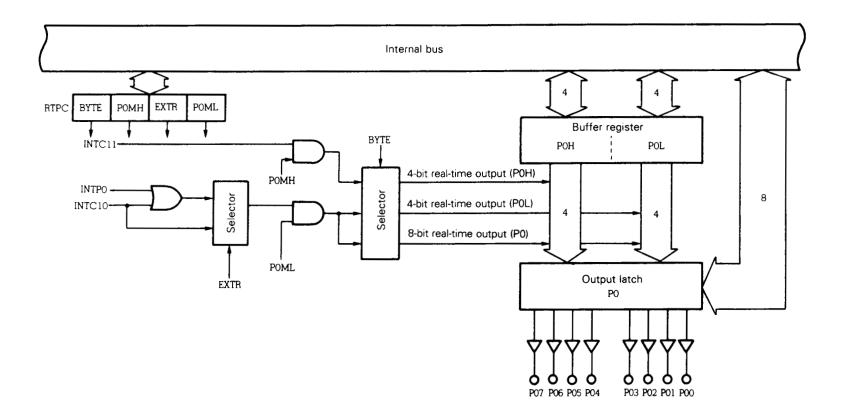

| 6-1      | Configuration of Real-Time Output Port                              | 126  |

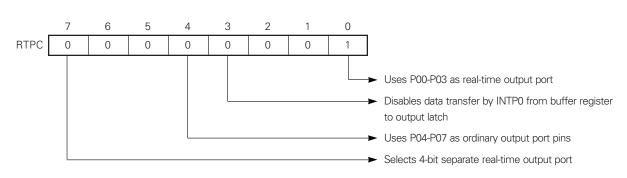

| 6-2      | Real-Time Output Port Control Register Format                       | 127  |

| 6-3      | Buffer Registers (P0H and P0L) Configuration                        | 128  |

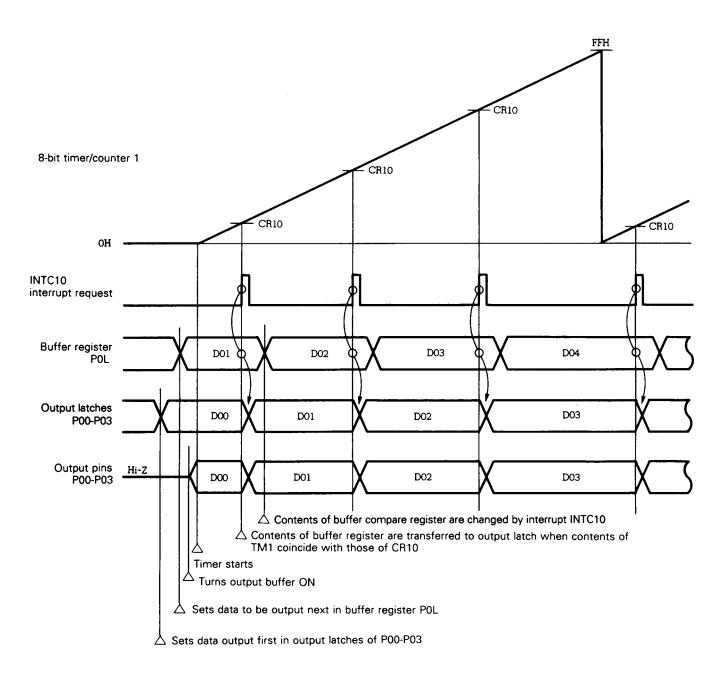

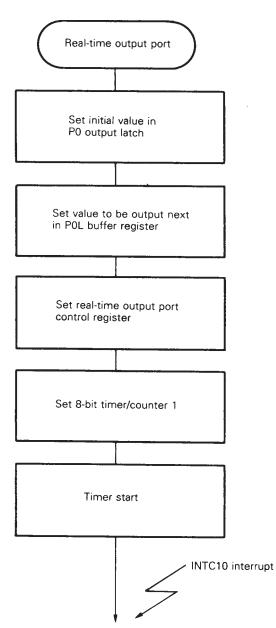

| 6-4      | Real-Time Output Port Operation Timing                              | 131  |

| 6-5      | Real-Time Output Port Operation Timing (2-ch independent control)   | 132  |

| 6-6      | Real-Time Output Port Operation Timing                              | 133  |

| 6-7      | Control Register Contents for Real-Time Output Function             | 134  |

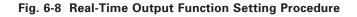

| 6-8      | Real-Time Output Function Setting Procedure                         |      |

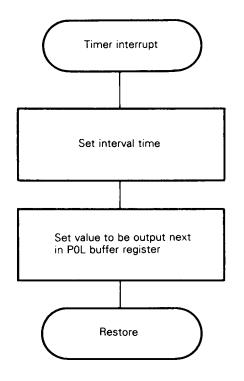

| 6-9      | Interrupt Request Processing When Real-Time Output Function Is Used | 135  |

# FIGURE (3/10)

| Fig. No. | Title                                                         | Page |

|----------|---------------------------------------------------------------|------|

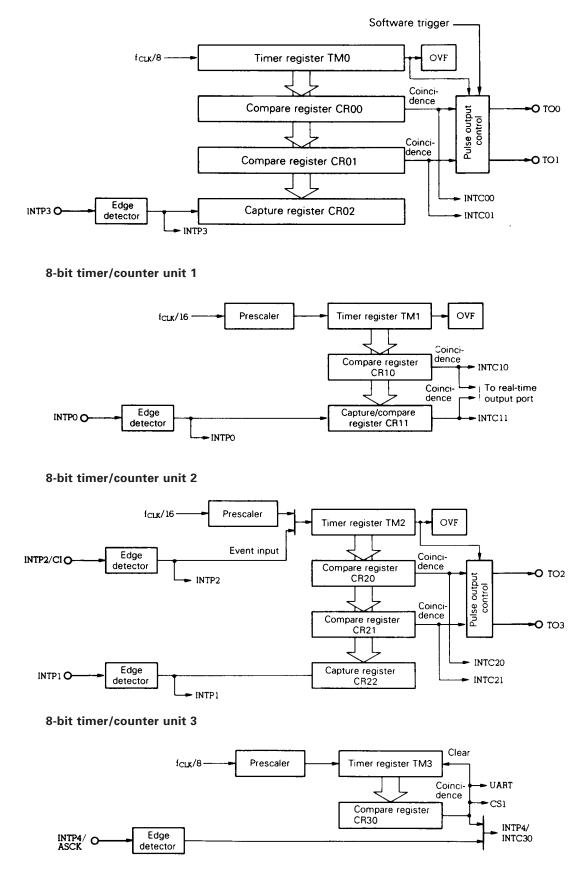

| 7-1      | Timer/Counter Units Configuration                             |      |

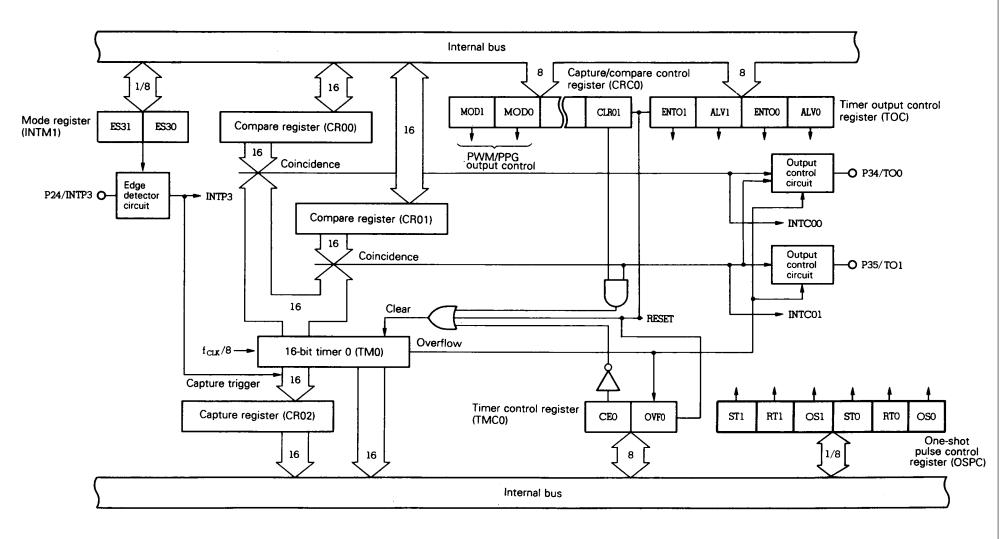

| 7-2      | Configuration of 16-bit Timer/Counter                         |      |

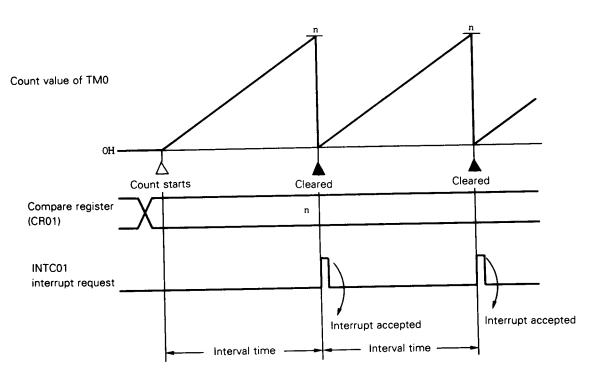

| 7-3      | Timer Control Register 0 (TMC0) Format                        |      |

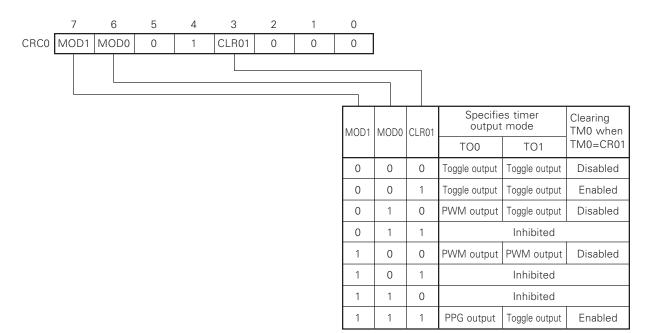

| 7-4      | Capture/Compare Control Register 0 (CRC0) Format              |      |

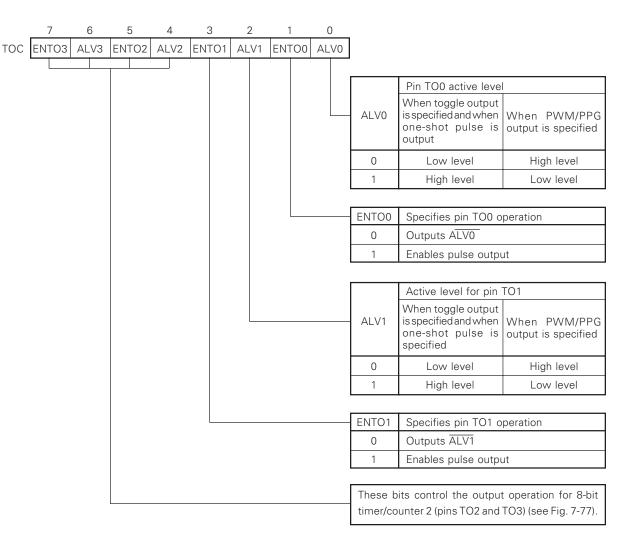

| 7-5      | Timer Output Control Register (TOC) Format                    |      |

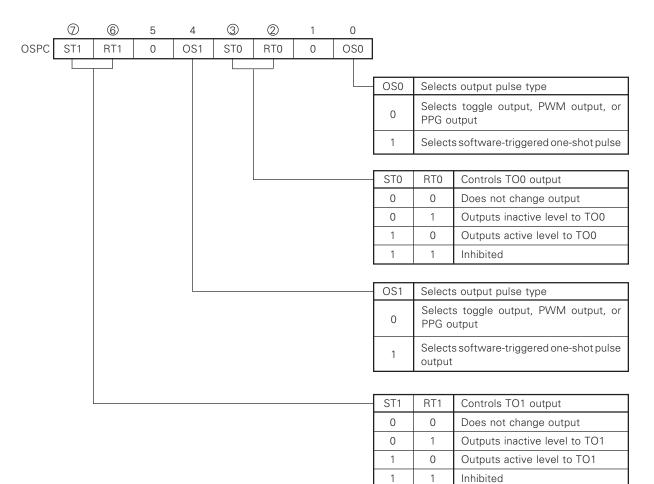

| 7-6      | One-Shot Pulse Output Control Register (OSPC) Format          |      |

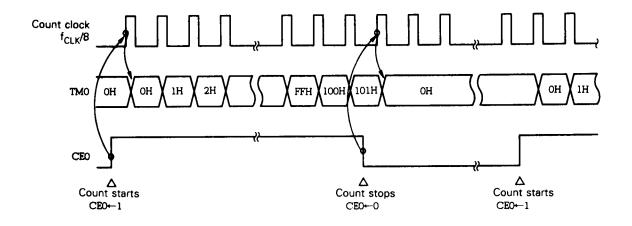

| 7-7      | 16-bit Timer 0 (TM0) Basic Operation                          |      |

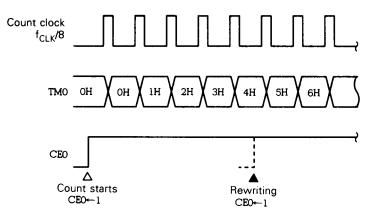

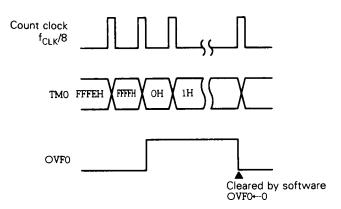

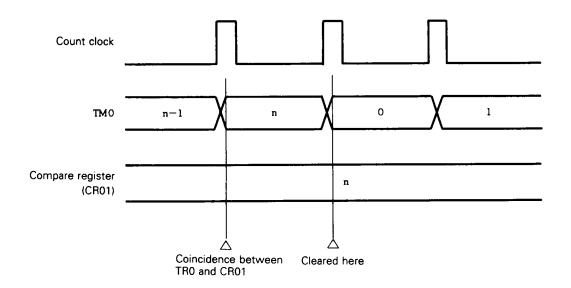

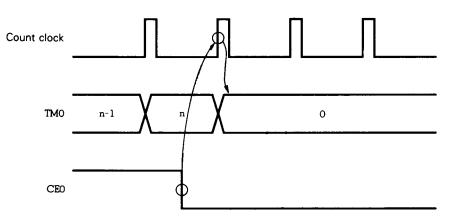

| 7-8      | Clearing TM0 by Coincidence with Compare Register             |      |

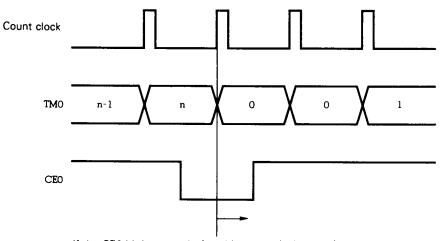

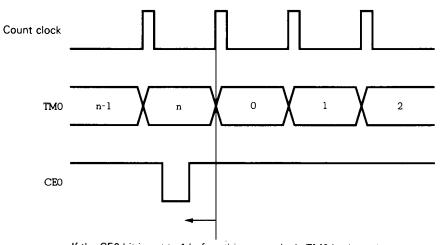

| 7-9      | Clear Operation When CE0 Bit Is Reset to 0                    |      |

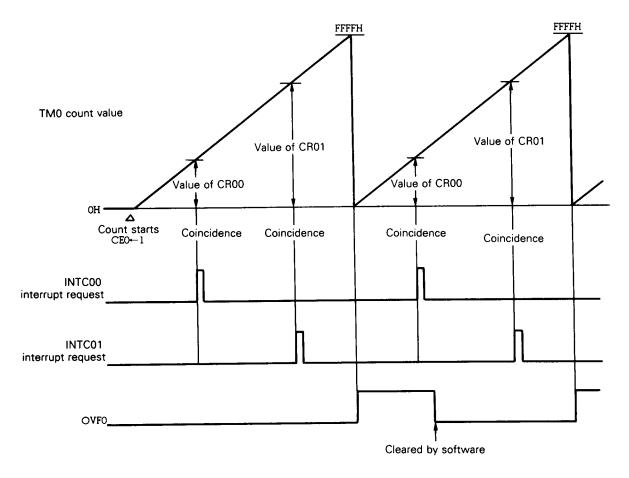

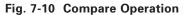

| 7-10     | Compare Operation                                             |      |

| 7-11     | Clearing TM0 after Coincidence Detection                      |      |

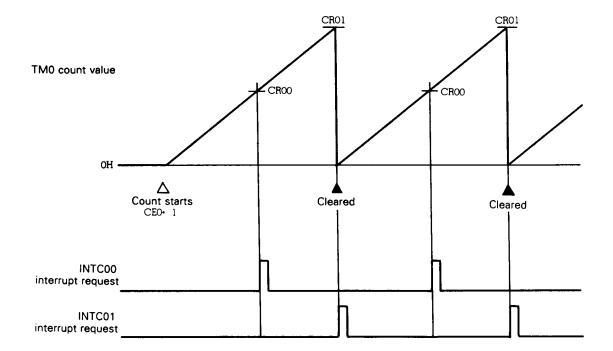

| 7-12     | Capture Operation                                             |      |

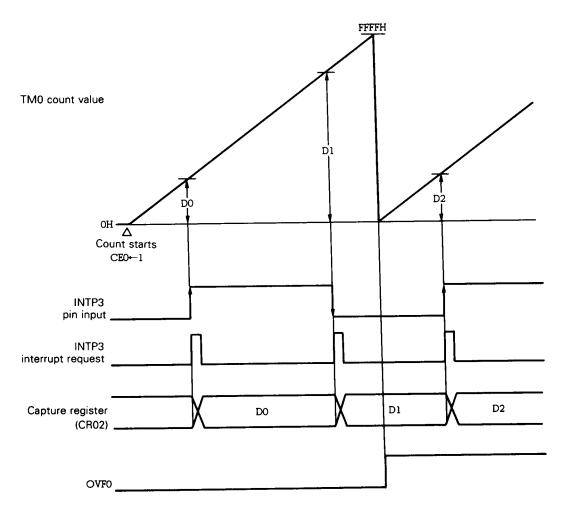

| 7-13     | Toggle Output Operation                                       |      |

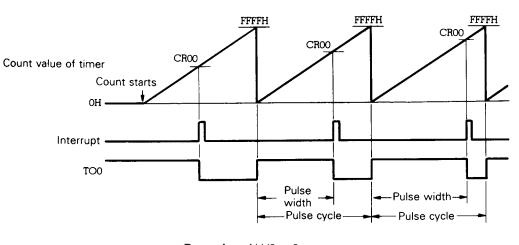

| 7-14     | PWM Pulse Output                                              |      |

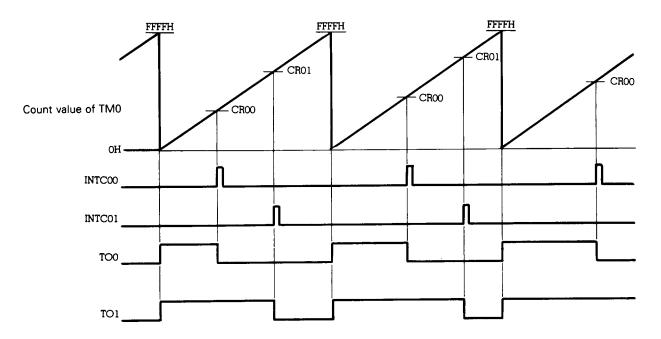

| 7-15     | PWM Output Example Using TM0                                  |      |

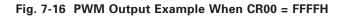

| 7-16     | PWM Output Example When CR00 = FFFFH                          |      |

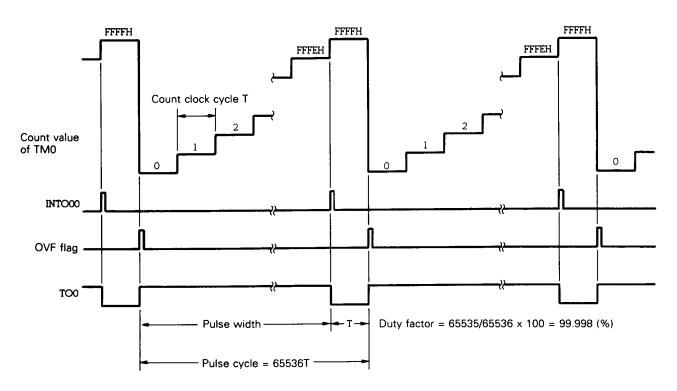

| 7-17     | Rewriting Compare Register Contents                           |      |

| 7-18     | PWM Output Example When Duty Factor Is 100%                   |      |

| 7-19     | When Stopping 16-bit Timer/Counter 0 during PWM Output        |      |

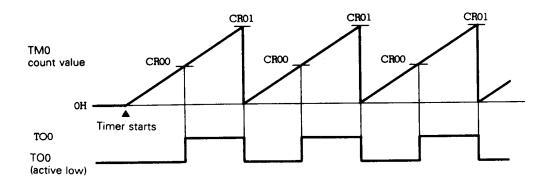

| 7-20     | PPG Output Example, Using TM0                                 |      |

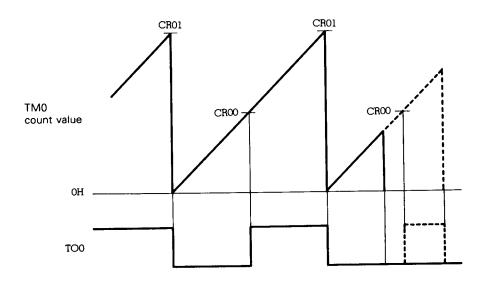

| 7-21     | PPG Output Example, When CR00 = CR01                          |      |

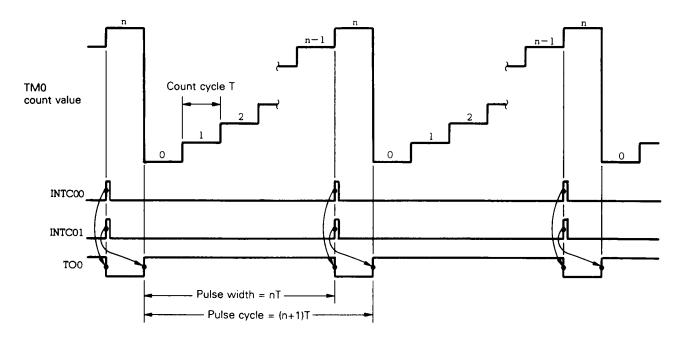

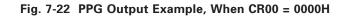

| 7-22     | PPG Output Example, When CR00 = 0000H                         |      |

| 7-23     | Rewriting Compare Register Example                            |      |

| 7-24     | PPG Output Example When Duty Factor Is 100%                   |      |

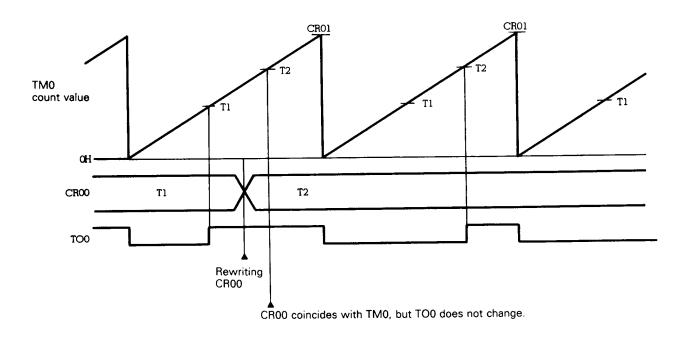

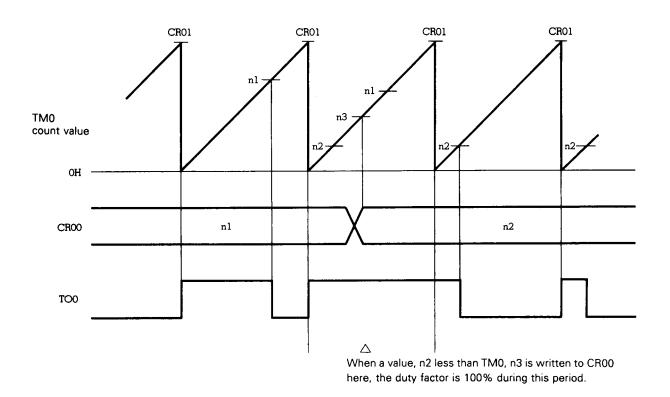

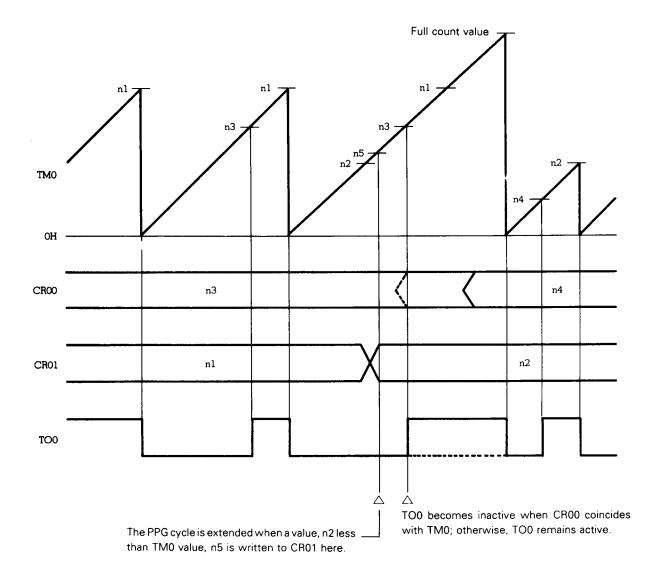

| 7-25     | PPG Output Example When Output Cycle Is Extended              |      |

| 7-26     | When Stopping 16-bit Timer/Counter 0 during PPG Output        |      |

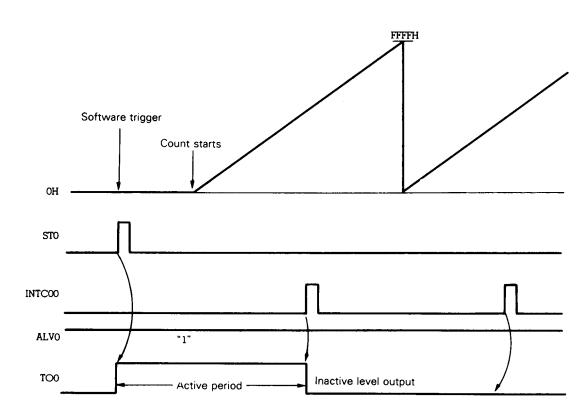

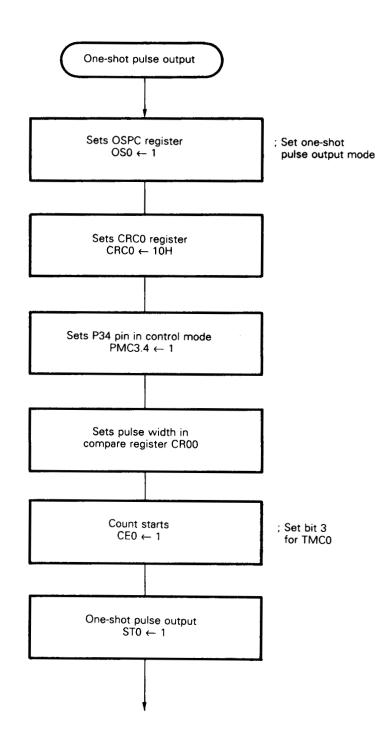

| 7-27     | Software-Triggered One-Shot Pulse Output Example              |      |

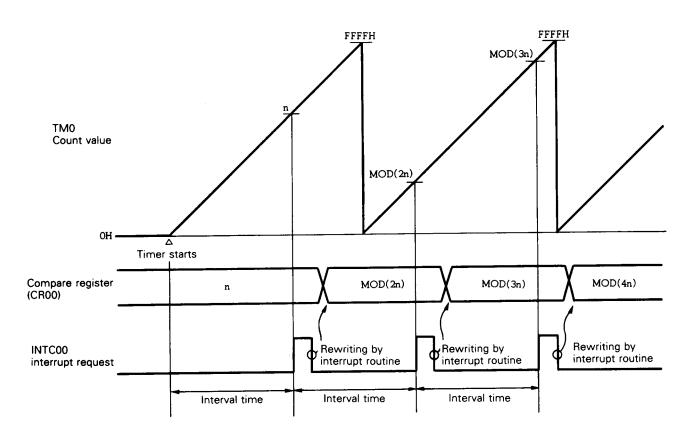

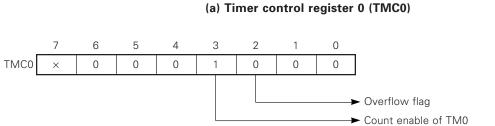

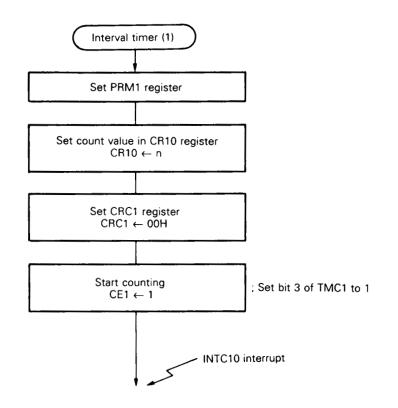

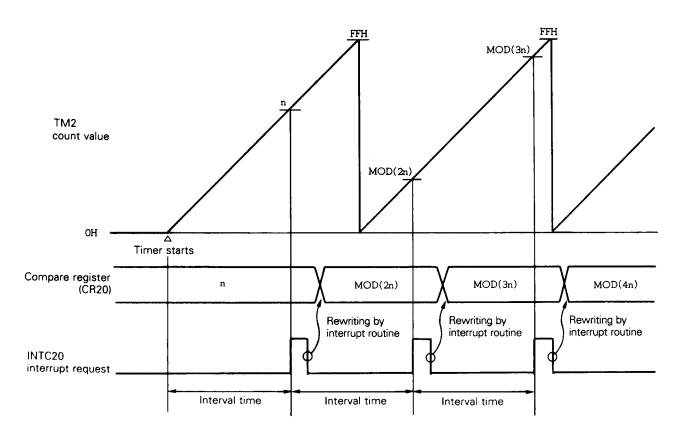

| 7-28     | Interval Timing Operation (1) Timing                          |      |

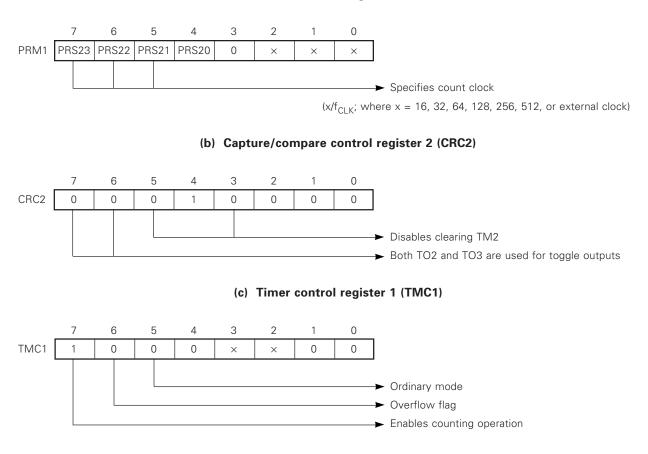

| 7-29     | Control Register Contents for Interval Timer Operation (1)    | 172  |

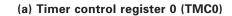

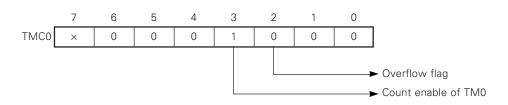

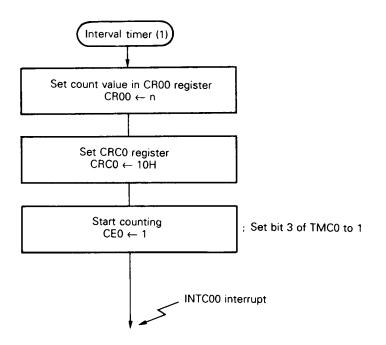

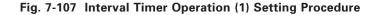

| 7-30     | Interval Timer Operation (1) Setting Procedure                | 172  |

| 7-31     | Interrupt Request Processing for Interval Timer Operation (1) |      |

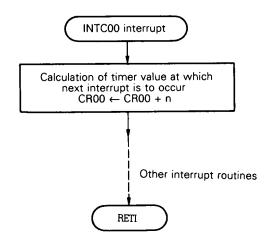

| 7-32     | Interval Timer Operation (2) Timing                           |      |

| 7-33     | Control Register Contents for Interval Timer Operation (2)    | 174  |

| 7-34     | Interval Timer Operation (2) Setting Procedure                | 174  |

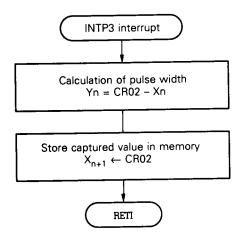

| 7-35     | Pulse Width Measurement Timing                                |      |

| 7-36     | Control Register Contents for Pulse Width Measurement         |      |

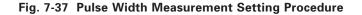

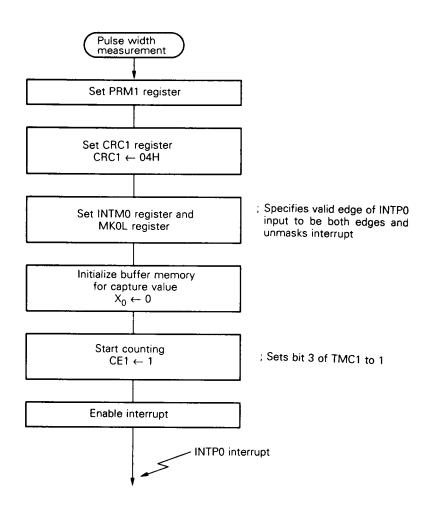

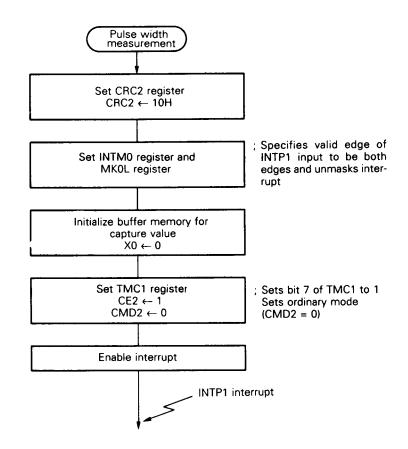

| 7-37     | Pulse Width measurement Setting Procedure                     | 177  |

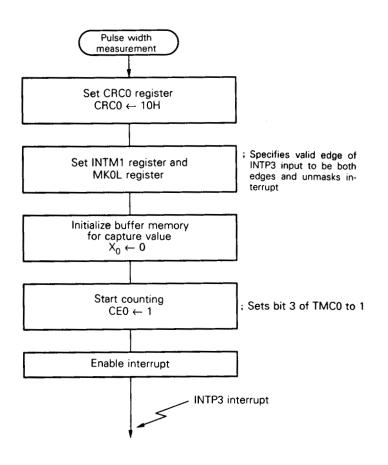

| 7-38     | Interrupt Request Processing to Calculate Pulse Width         | 177  |

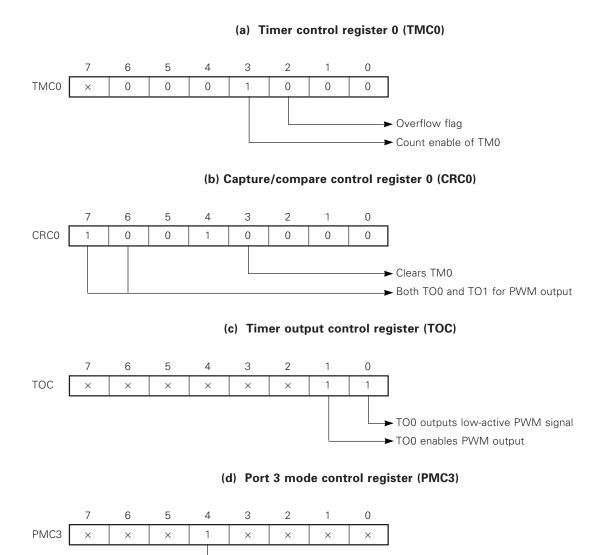

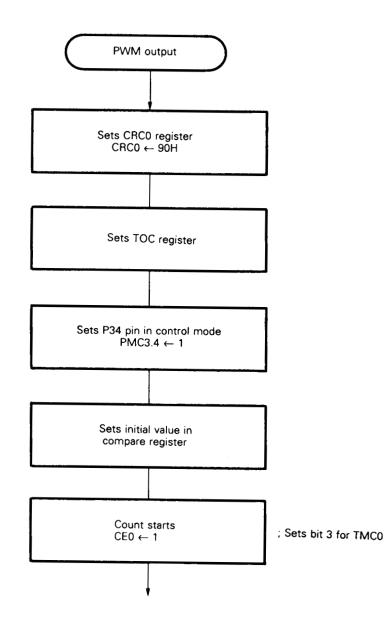

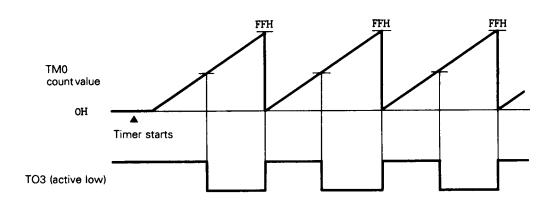

| 7-39     | PWM Signal Output Example by 16-bit Timer/Counter             |      |

| 7-40     | Control Register Contents Set for PWM Output Operation        |      |

| 7-41     | PWM Output Setting Procedure                                  |      |

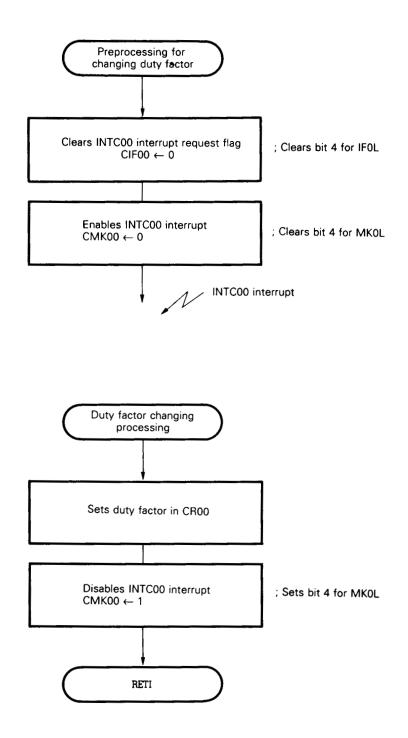

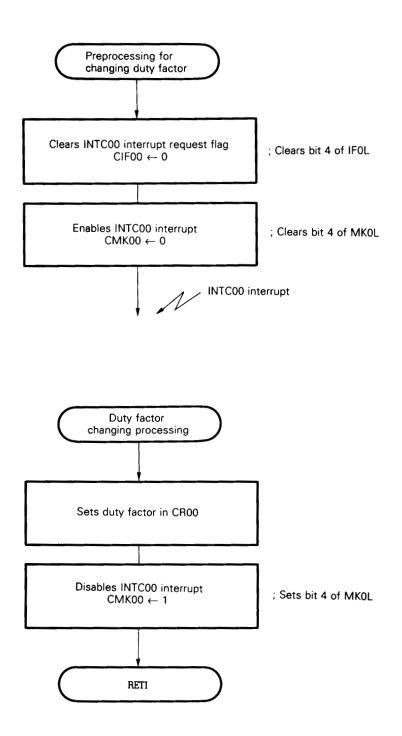

| 7-42     | Changing Duty Factor for PWM Output                           |      |

| 7-43     | 16-bit Timer/Counter PPG Signal Output Example                |      |

# FIGURE (4/10)

| Fig. No. | Title                                                                                              | Page  |

|----------|----------------------------------------------------------------------------------------------------|-------|

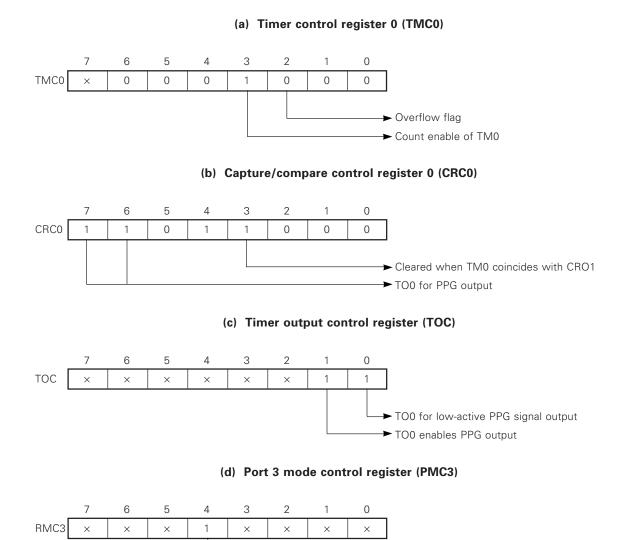

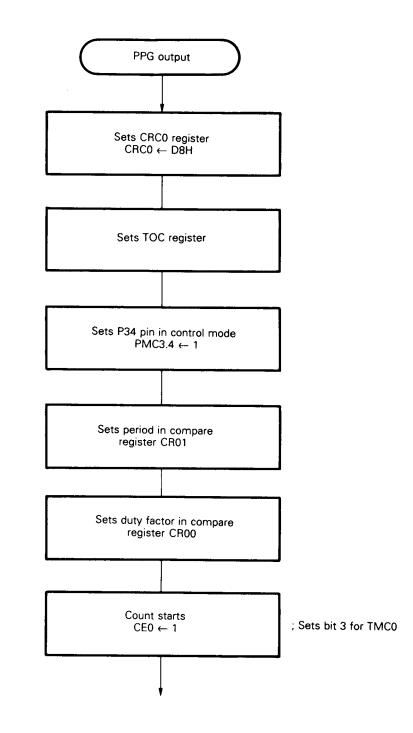

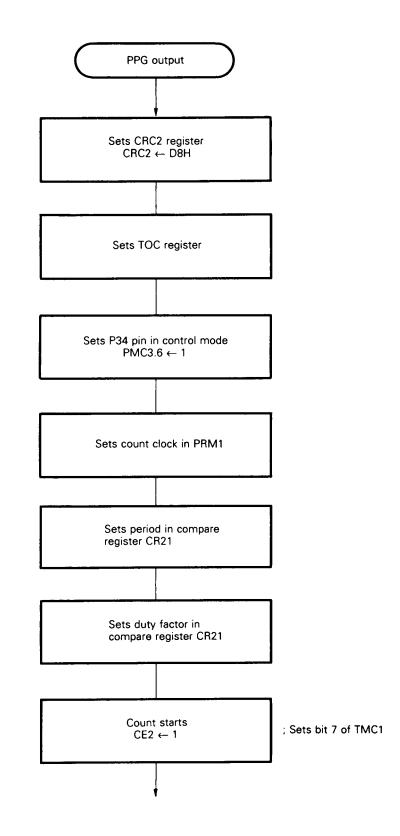

| 7-44     | Control Register Contents Set for PPG Output Operation                                             | . 183 |

| 7-45     | PPG Output Setting Procedure                                                                       | . 184 |

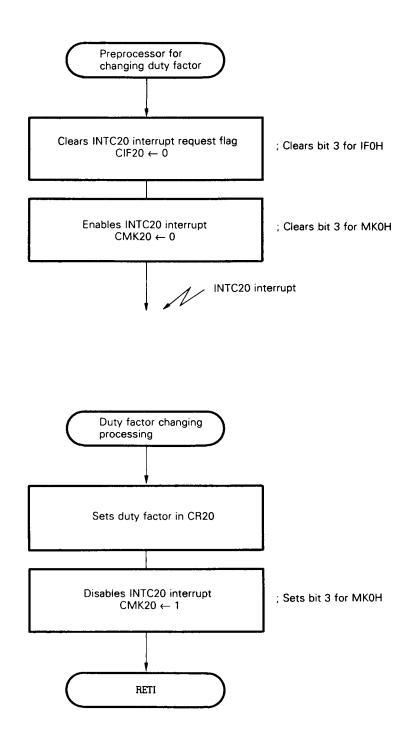

| 7-46     | Changing Duty Factor for PPG Output                                                                | . 185 |

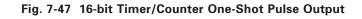

| 7-47     | 16-bit Timer/Counter One-Shot Pulse Output                                                         | . 186 |

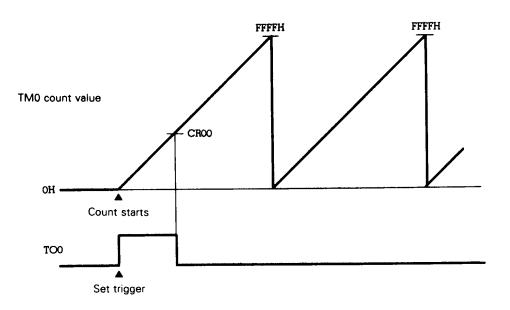

| 7-48     | Control Register Contents Set for One-Shot Pulse Output                                            | . 187 |

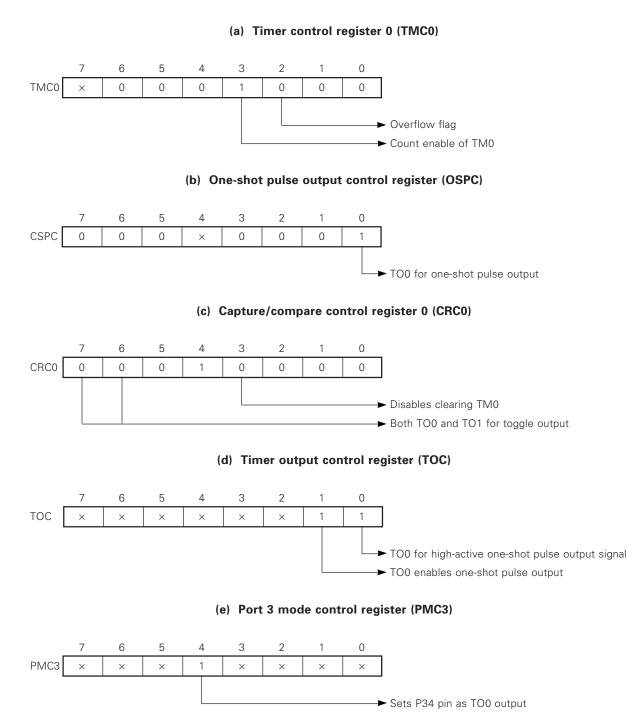

| 7-49     | One-Shot Pulse Output Setting Procedure                                                            | . 188 |

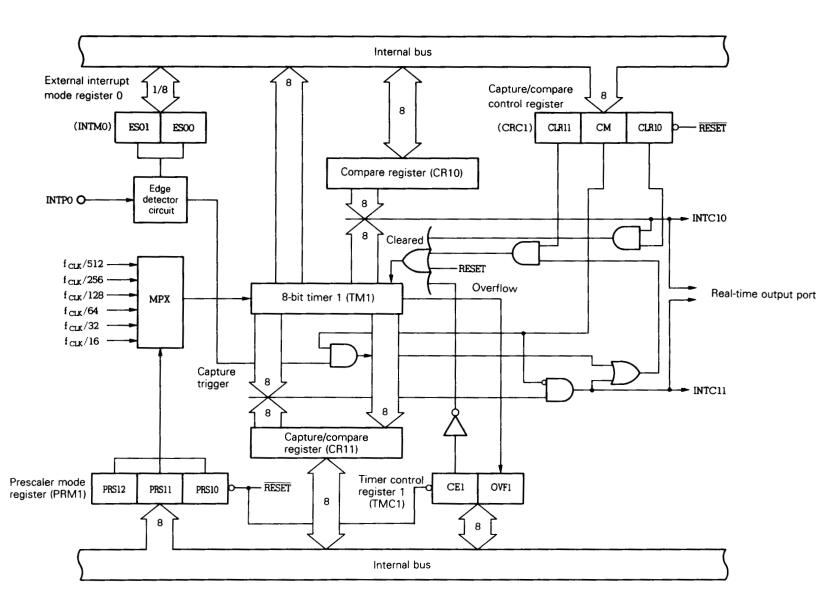

| 7-50     | Configuration of 8-bit Timer/Counter 1                                                             | . 191 |

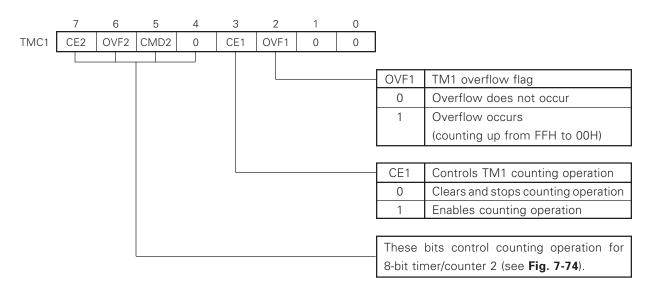

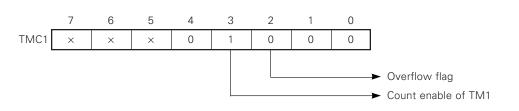

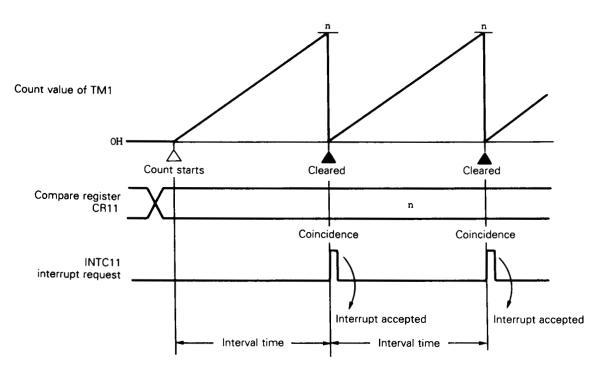

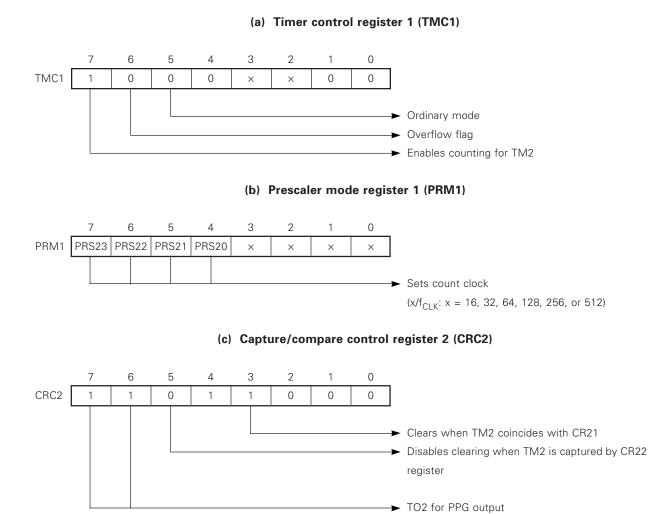

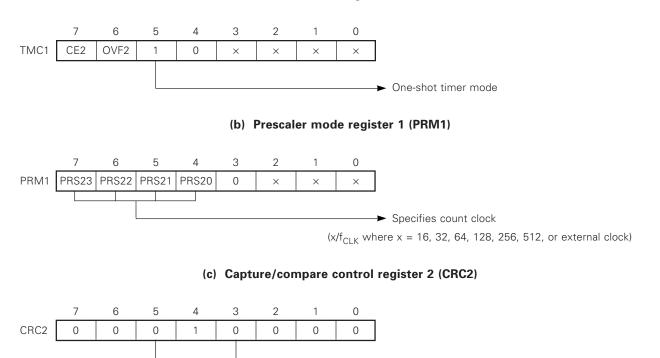

| 7-51     | Timer Control Register 1 (TMC1) Format                                                             | . 193 |

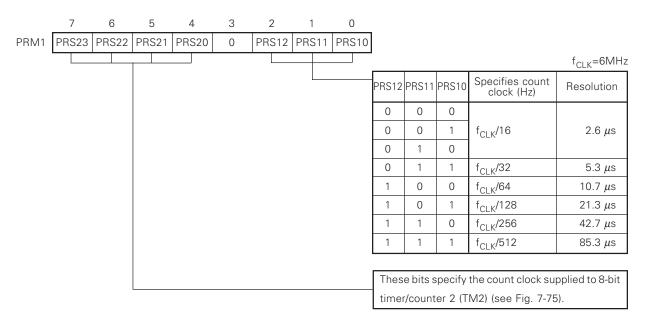

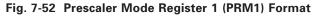

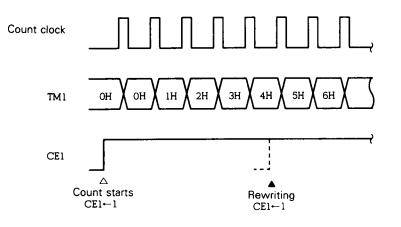

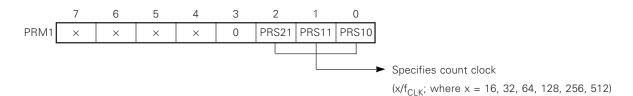

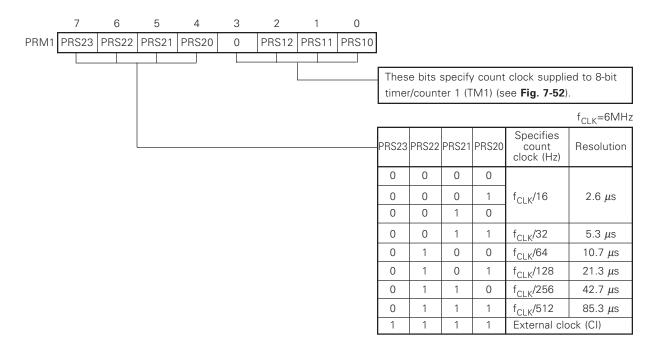

| 7-52     | Prescaler Mode Register 1 (PRM1) Format                                                            | . 194 |

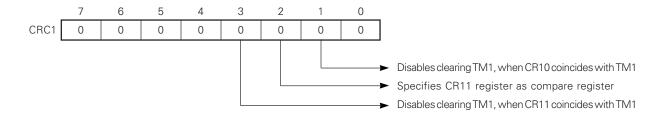

| 7-53     | Capture/Compare Control Register 1 (CRC1) Format                                                   | . 195 |

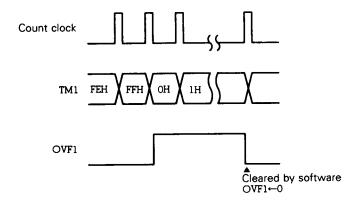

| 7-54     | Basic Operation for 8-bit Timer 1 (TM1)                                                            | . 197 |

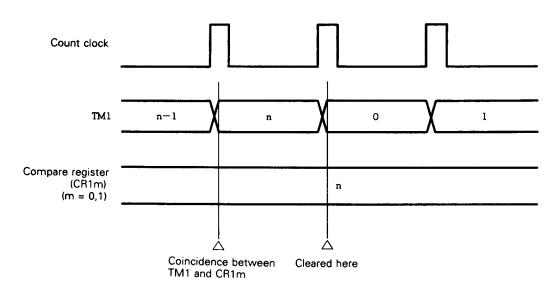

| 7-55     | Clearing TM1 by Coincidence with Compare Register (CR1m)                                           | . 198 |

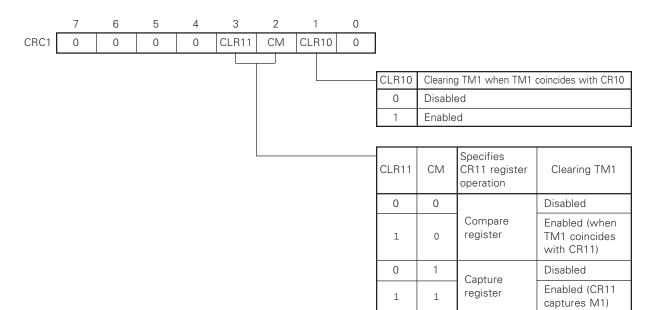

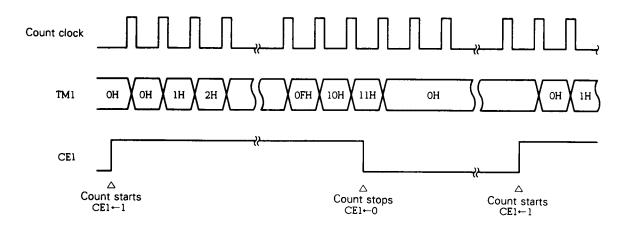

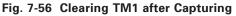

| 7-56     | Clearing TM1 after Capturing                                                                       | . 198 |

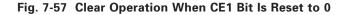

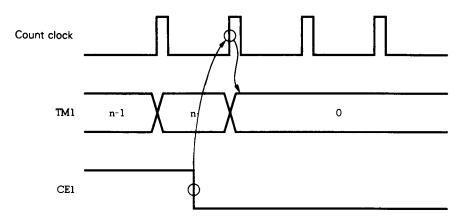

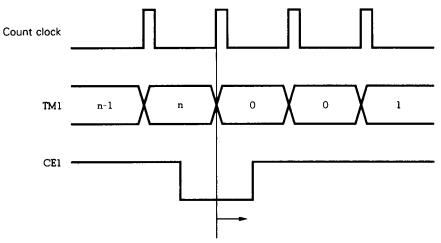

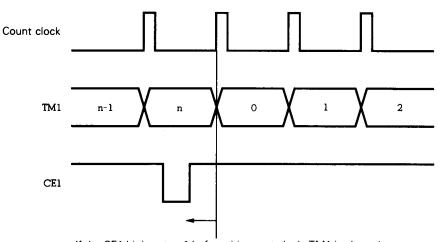

| 7-57     | Clear Operation When CE1 Bit Is Reset to 0                                                         | . 199 |

| 7-58     | Compare Operation                                                                                  | . 200 |

| 7-59     | Clearing TM1 after Coincidence Detection                                                           | . 201 |

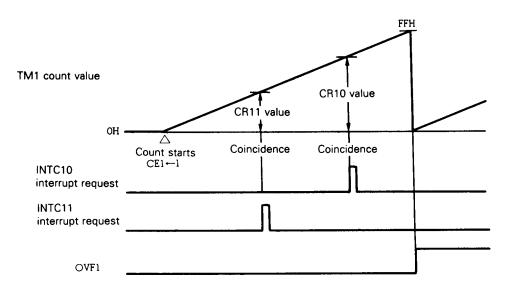

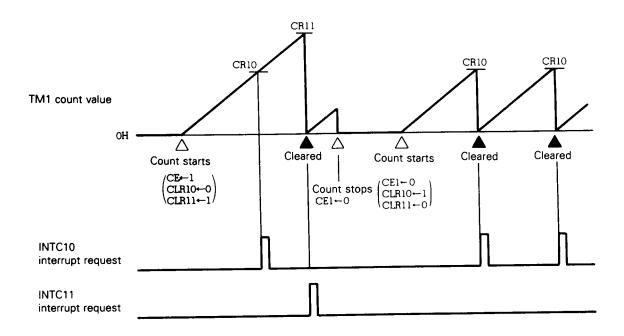

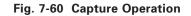

| 7-60     | Capture Operation                                                                                  | . 203 |

| 7-61     | Clearing TM1 after Its Value Has Been Captured                                                     | . 204 |

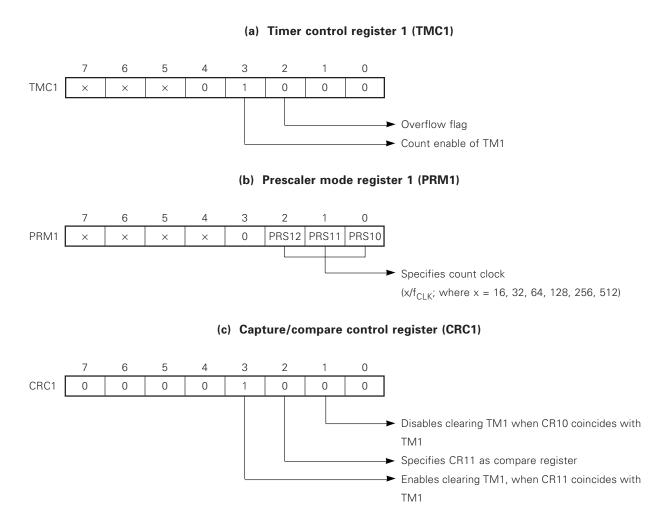

| 7-62     | Interval Timer Operation (1) Timing                                                                | . 205 |

| 7-63     | Control Register Contents for Interval Timer Operation (1)                                         | . 206 |

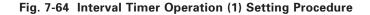

| 7-64     | Interval Timer Operation (1) Setting Procedure                                                     | . 207 |

| 7-65     | Interrupt Request Processing for Interval Timer Operation (1)                                      | . 207 |

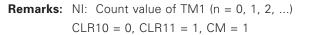

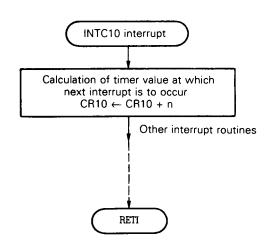

| 7-66     | Interval Timer Operation (2) Timing (when CR11 is used as the compare register)                    | . 208 |

| 7-67     | Control Register Contents for Interval Timer Operation (2)                                         | . 209 |

| 7-68     | Interval Timer Operation (2) Setting Procedure                                                     | . 210 |

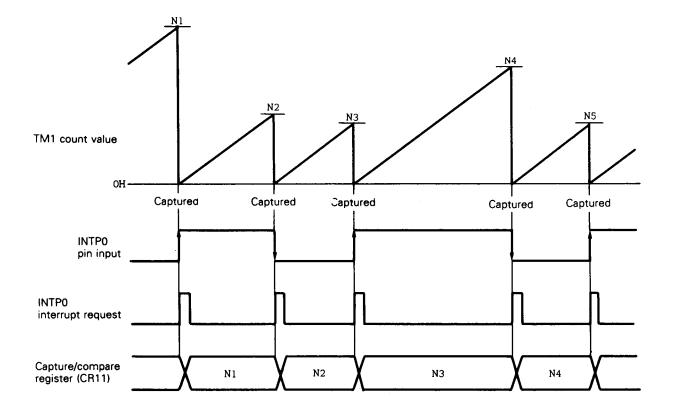

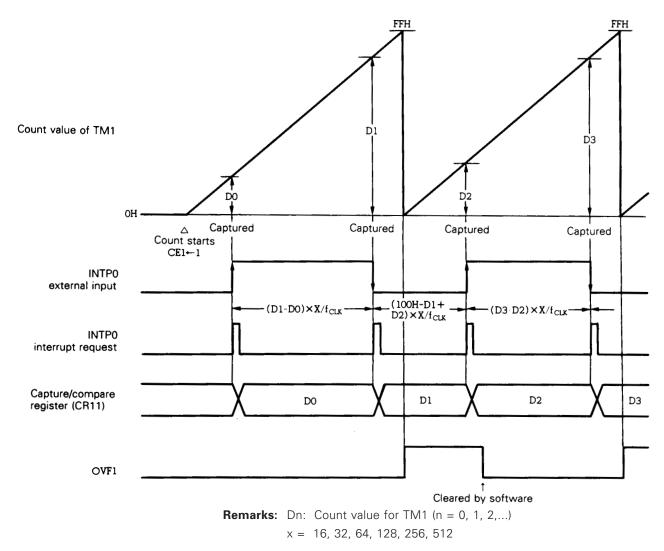

| 7-69     | Pulse Width Measurement Timing (when CR11 is used as the capture register)                         | . 211 |

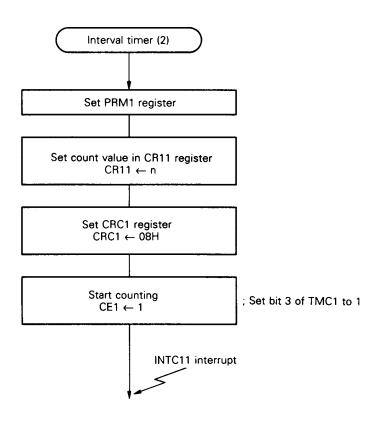

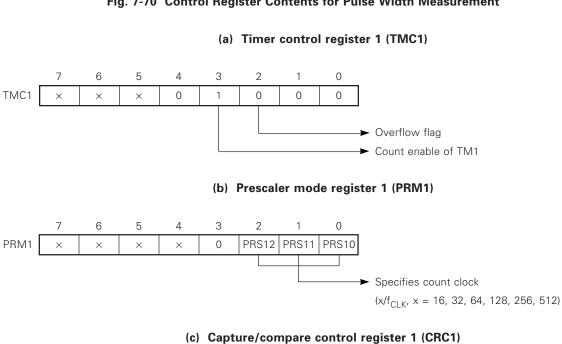

| 7-70     | Control Register Contents for Pulse Width Measurement                                              | . 212 |

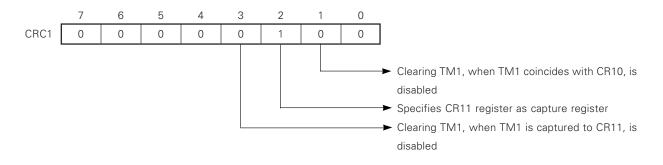

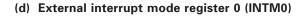

| 7-71     | Pulse Width Measurement Setting Procedure                                                          | . 213 |

| 7-72     | Interrupt Request Processing to Calculate Pulse Width                                              | . 213 |

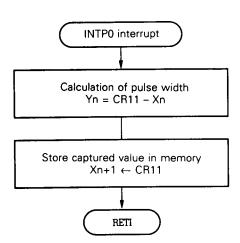

| 7-73     | Configuration of 8-bit Timer/Counter 2                                                             | . 217 |

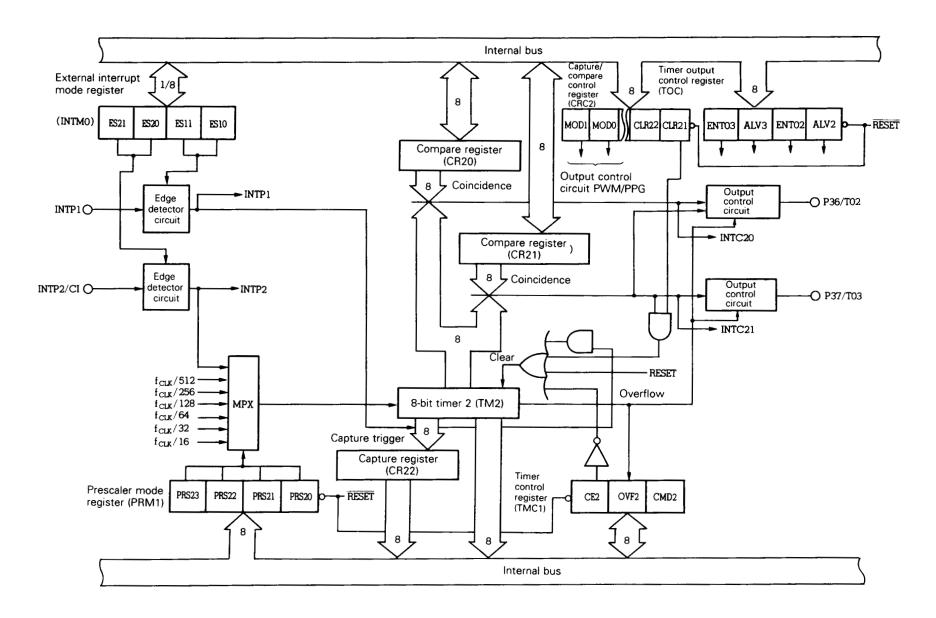

| 7-74     | Timer Control Register 1 (TMC1) Format                                                             | . 219 |

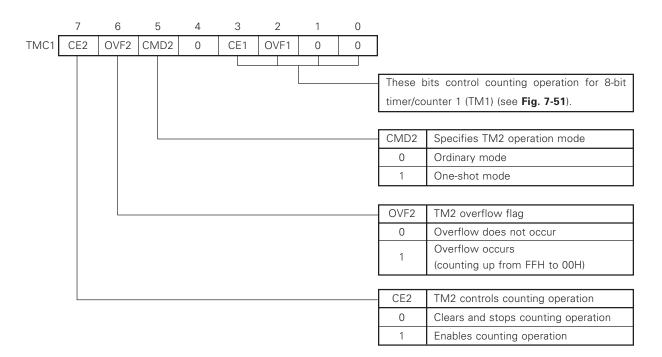

| 7-75     | Prescaler Mode Register 1 (PRM1) Format                                                            | . 220 |

| 7-76     | Capture/Compare Control Register 2 (CRC2) Format                                                   | . 221 |

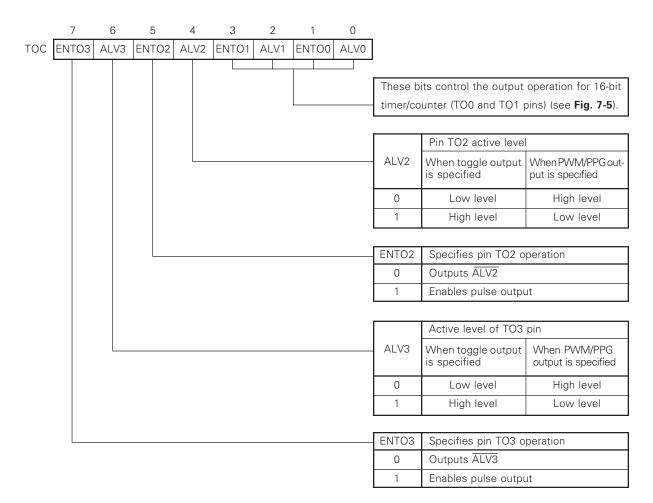

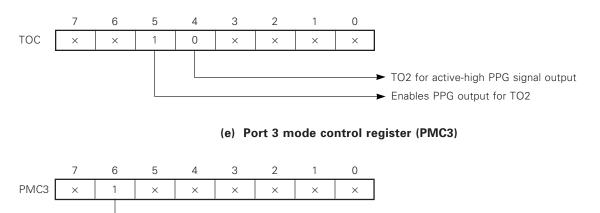

| 7-77     | Timer Output Control Register (TOC)Format                                                          | . 222 |

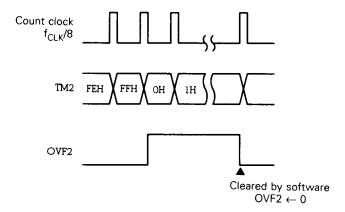

| 7-78     | Basic Operation for 8-bit Timer 2 (TM2)                                                            | . 224 |

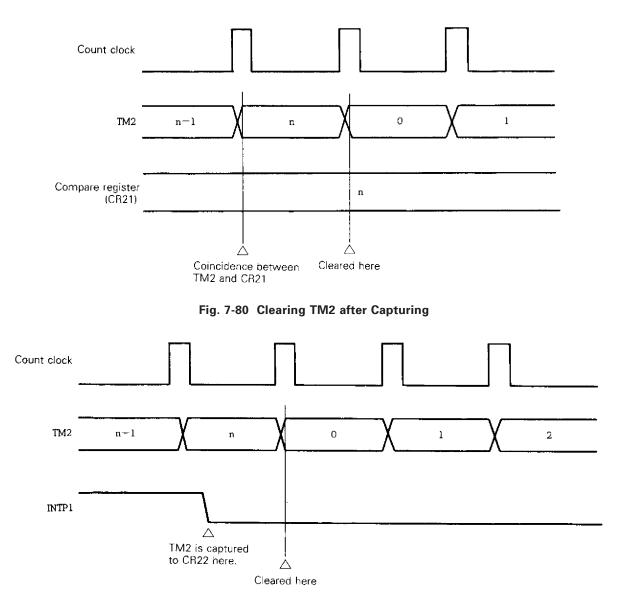

| 7-79     | Clearing TM2 by Coincidence with Compare Register (CR21)                                           | . 225 |

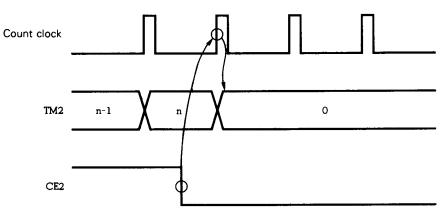

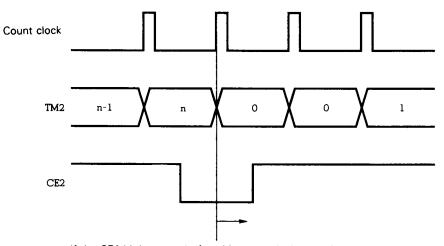

| 7-80     | Clearing TM2 after Capturing                                                                       | . 225 |

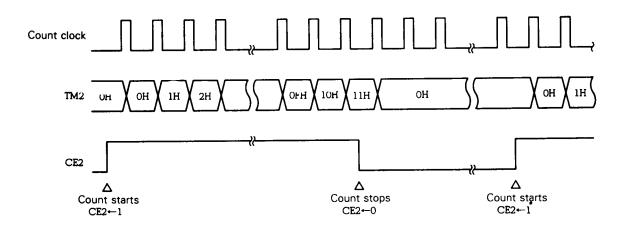

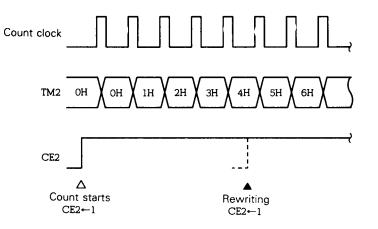

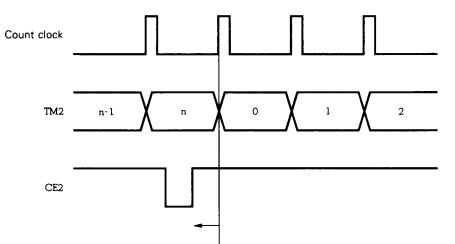

| 7-81     | Clear Operation When CE2 Bit Is Reset to 0                                                         | . 226 |

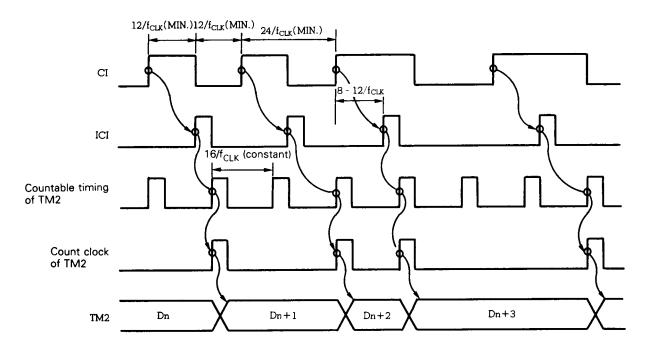

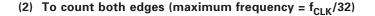

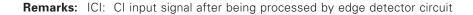

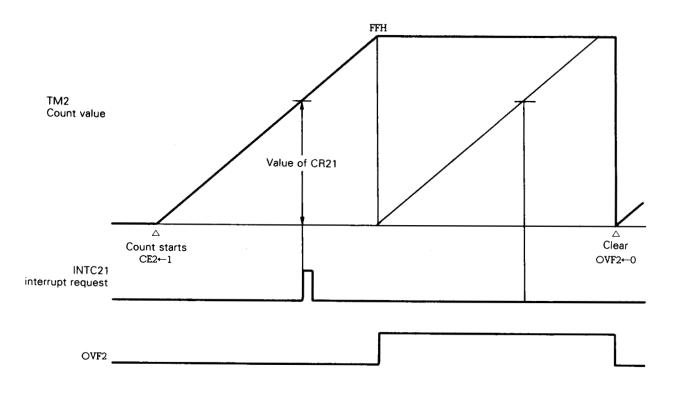

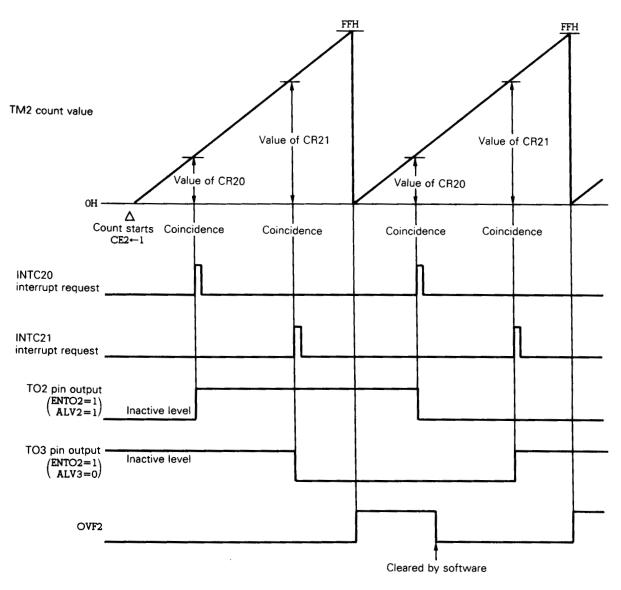

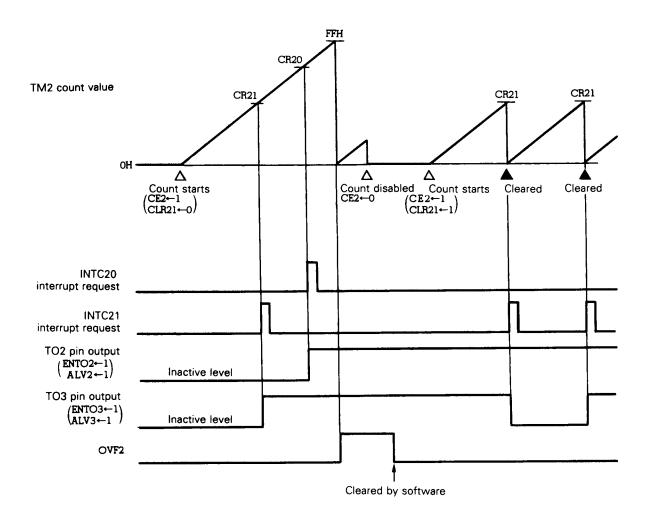

| 7-82     | External Event Count Timing for 8-bit Timer/Counter 2                                              | . 227 |

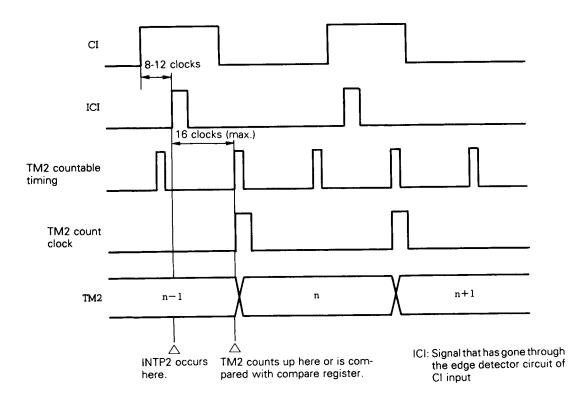

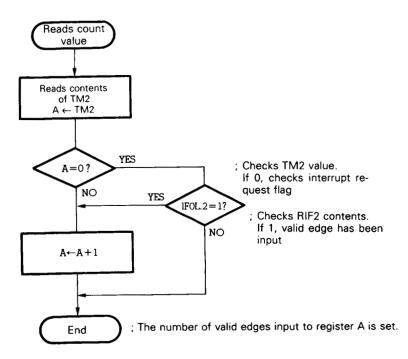

| 7-83     | Interrupt Request Generation by ExternalEvent Counter                                              |       |

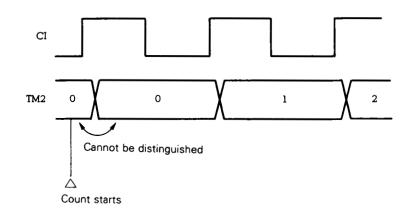

| 7-84     | If One Valid Edge Input Cannot Be Distinguished from No Valid Edge Input by External Event Counter |       |

| 7-85     | To Distinguish by External Counter                                                                 |       |

|          |                                                                                                    | 01    |

# FIGURE (5/10)

| Fig. No. | Title                                                         | Pag |

|----------|---------------------------------------------------------------|-----|

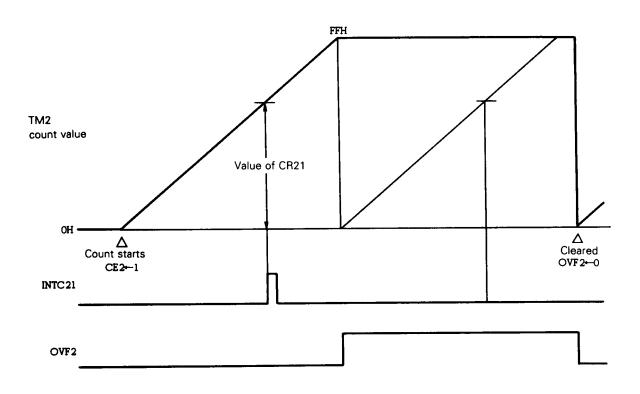

| 7-86     | One-Shot Timer Operation                                      | 232 |

| 7-87     | Compare Operation                                             |     |

| 7-88     | Clearing TM2 after Coincidence Detection                      |     |

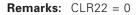

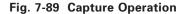

| 7-89     | Capture Operation                                             |     |

| 7-90     | Clearing TM2 after Its Value Has Been Captured                |     |

| 7-91     | Timer Output Operation                                        |     |

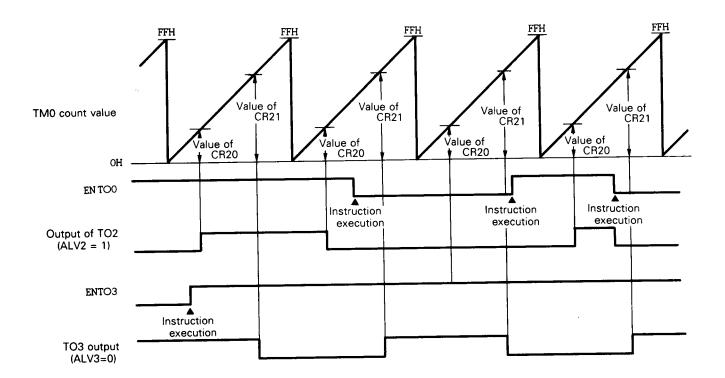

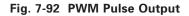

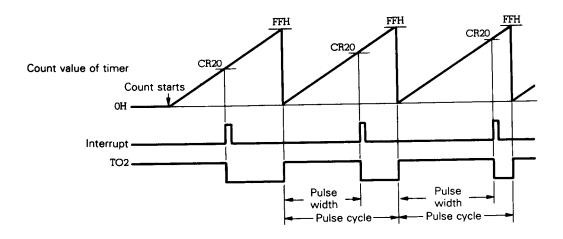

| 7-92     | PWM Pulse Output                                              |     |

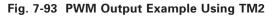

| 7-93     | PWM Output Example Using TM2                                  |     |

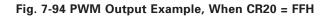

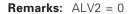

| 7-94     | PWM Output Example, When CR20 = FFH                           |     |

| 7-95     | Rewriting Contents for Compare Registers                      |     |

| 7-96     | PWM Output Example When Duty Factor Is 100%                   |     |

| 7-97     | When Stopping 8-bit Timer/Counter 2 during PWM Output         |     |

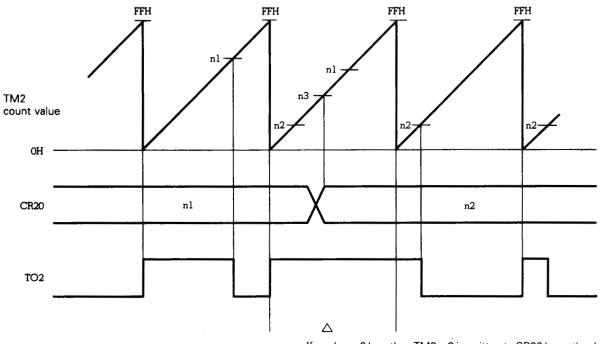

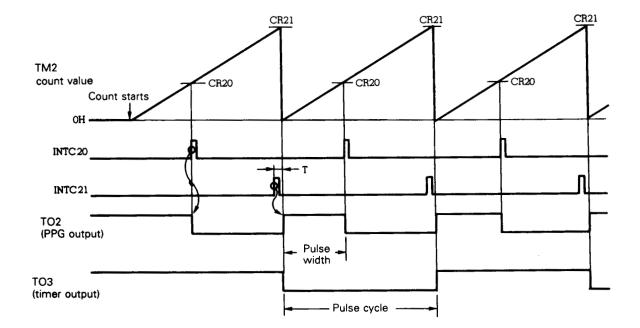

| 7-98     | PPG Output Example, Using TM2                                 |     |

| 7-99     | PPG Output Example, When CR20 = CR21                          |     |

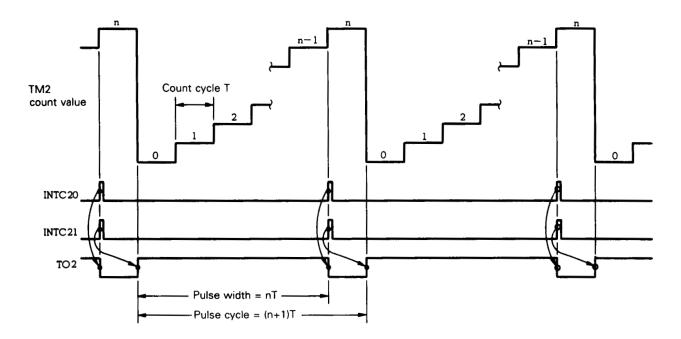

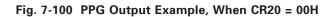

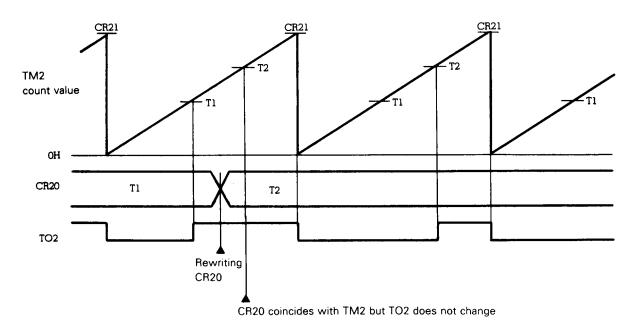

| 7-100    | PPG Output Example, When CR20 = 00H                           |     |

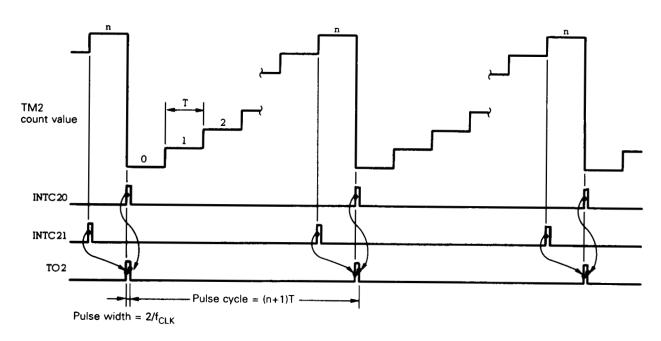

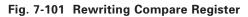

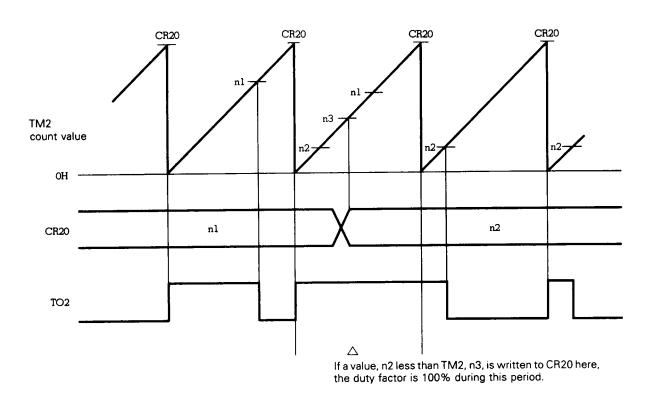

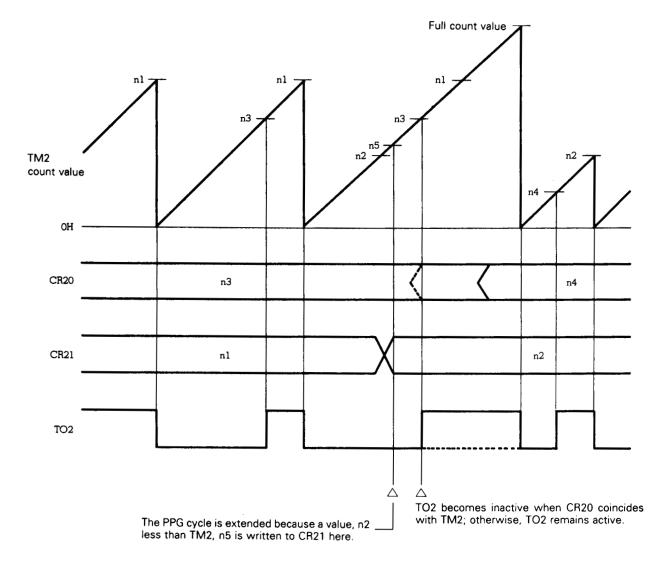

| 7-101    | Rewriting Compare Register                                    |     |

| 7-102    | PPG Output Example When Duty Factor Is 100%                   |     |

| 7-103    | PPG Output Example When Output Cycle Is Extended              |     |

| 7-104    | When Stopping 8-bit Timer/Counter 2 during PPG Output         |     |

| 7-105    | Interval Timer Operation (1) Timing                           |     |

| 7-106    | Control Register Contents for Interval Timer Operation (1)    |     |

| 7-107    | Interval Timer Operation (1) Setting Procedure                |     |

| 7-108    | Interrupt Request Processing for Interval Timer Operation (1) |     |

| 7-109    | Interval Timer Operation (2) Timing                           |     |

| 7-110    | Control Register Contents for Interval Timer Operation (2)    |     |

| 7-111    | Interval Timer Operation (2) Setting Procedure                |     |

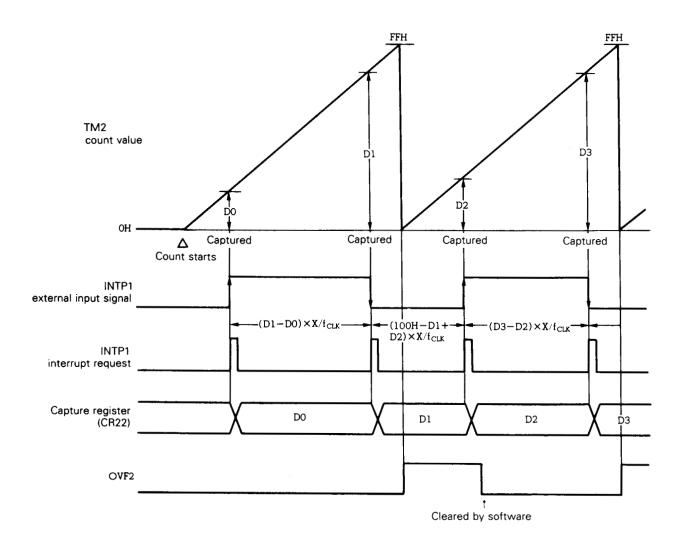

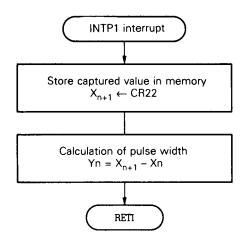

| 7-112    | Pulse Width Measurement Timing                                |     |

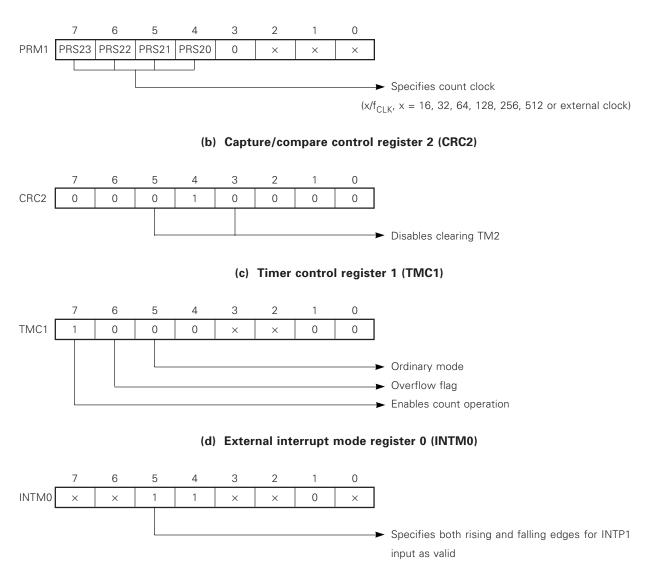

| 7-113    | Control Register Contents for Pulse Width Measurement         |     |

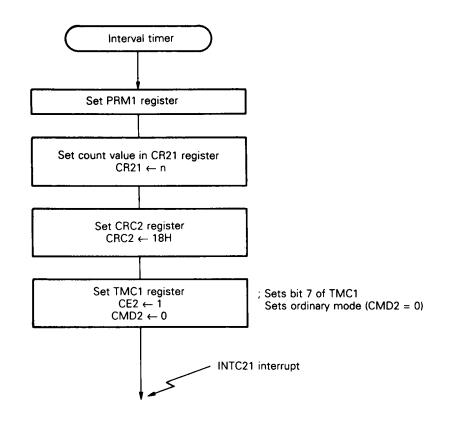

| 7-114    | Pulse Width Measurement Setting Procedure                     |     |

| 7-115    | Interrupt Request Processing to Calculate Pulse Width         |     |

| 7-116    | Example for PWM Signal Output by 8-bit Timer/Counter 2        |     |

| 7-117    | Control Register Contents Set for PWM Output Operation        |     |

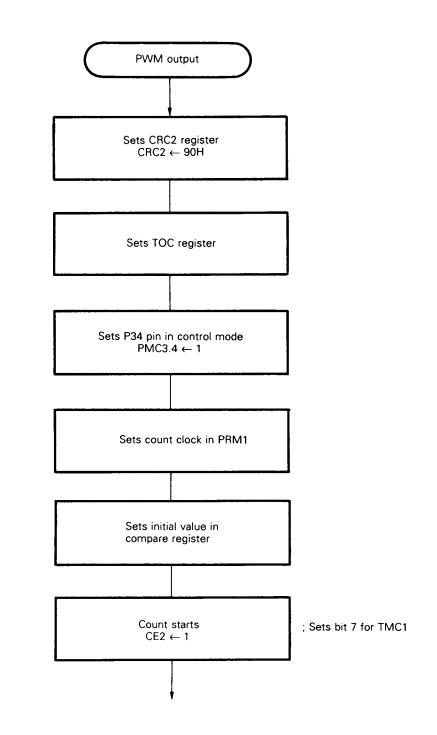

| 7-118    | PWM Output Setting Procedure                                  |     |

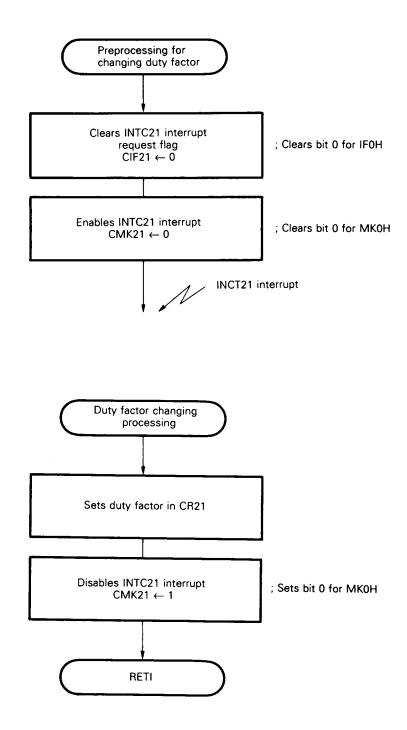

| 7-119    | Changing Duty Factor of PWM Output                            |     |

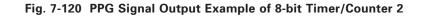

| 7-120    | PPG Signal output Example of 8-bit Timer/Counter 2            |     |

| 7-121    | Control Register Contents Set for PPG Output Operation        |     |

| 7-122    | PPG Output Setting Procedure                                  | 27  |

| 7-123    | Changing Duty Factor of PPG Output                            |     |

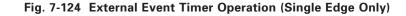

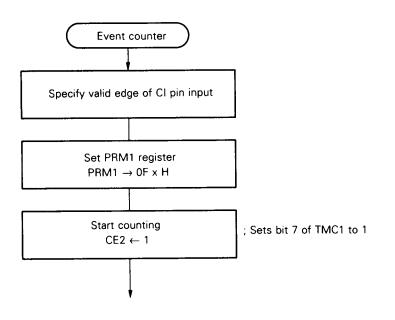

| 7-124    | External Event Timer Operation (Single Edge Only)             | 27  |

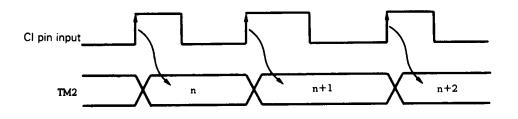

| 7-125    | Control Register Contents for External Event Counter          | 27  |

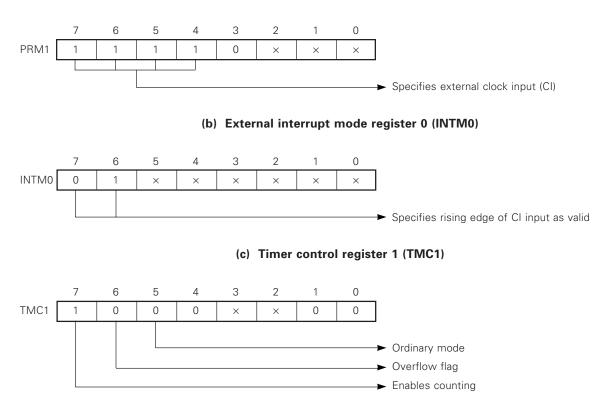

| 7-126    | External Event Counter Setting Procedure                      |     |

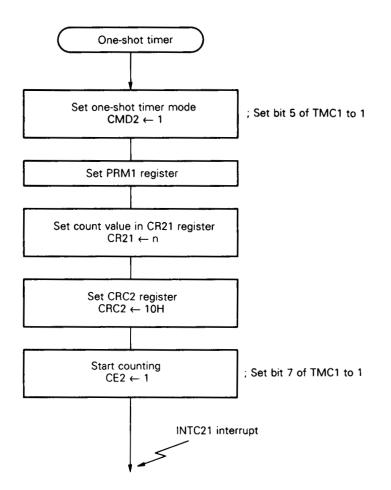

| 7-127    | One-Shot Timer Operation                                      |     |

| 7-128    | Control Register Contents for One-Shot Timer Operation        |     |

# FIGURE (6/10)

| ig. No. | Title                                                                                           | Page |

|---------|-------------------------------------------------------------------------------------------------|------|

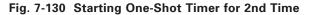

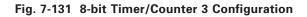

| 7-129   | Control Register Setting Procedure                                                              | 277  |

| 7-130   | Starting One-Shot Timer for 2nd Timer                                                           |      |

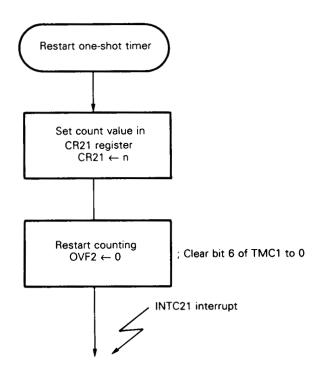

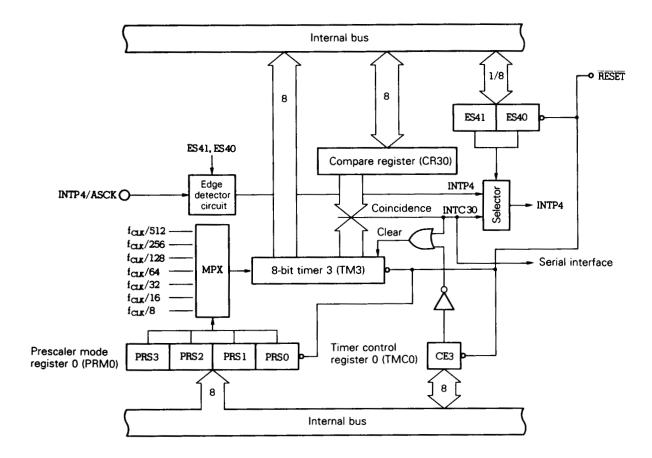

| 7-131   | 8-bit Timer/Counter 3 Configuration                                                             | 279  |

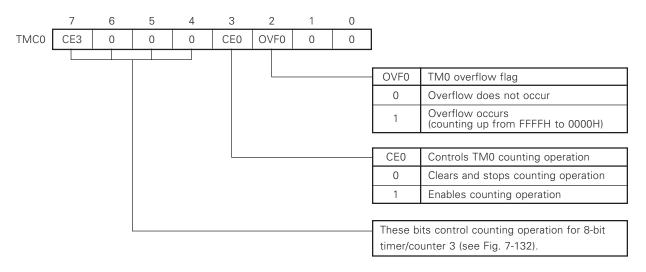

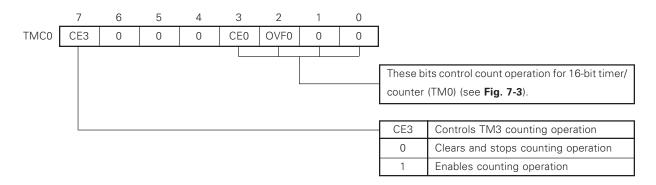

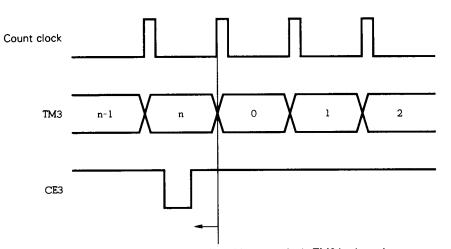

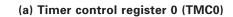

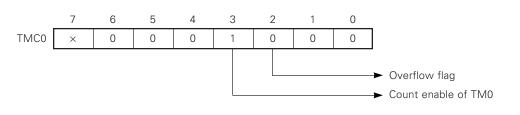

| 7-132   | Timer Control Register 0 (TMC0) Format                                                          | 281  |

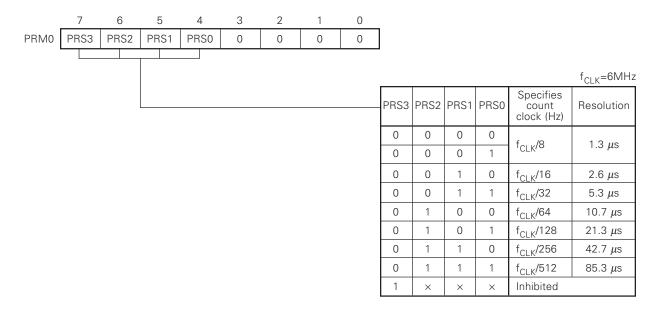

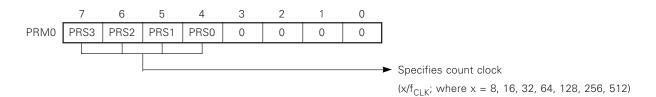

| 7-133   | Prescaler Mode Register 0 (PRM0) Format                                                         | 282  |

| 7-134   | Basic Operation for 8-bit Timer 3 (TM3)                                                         | 283  |

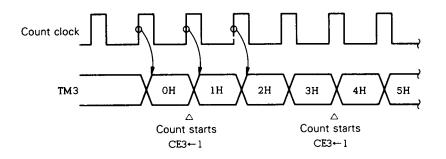

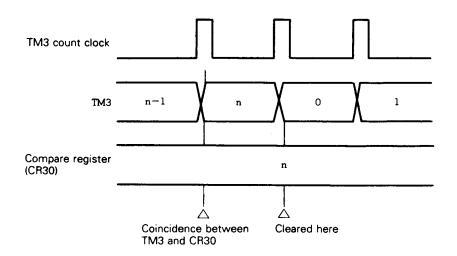

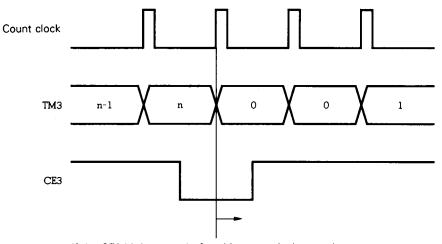

| 7-135   | Clearing TM3 by Coincidence with Compare Register                                               | 284  |

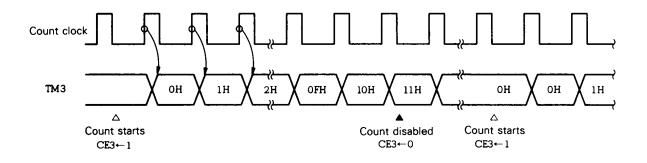

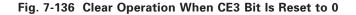

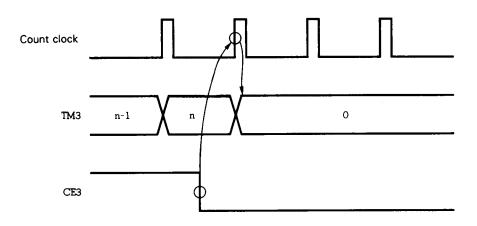

| 7-136   | Clear Operation When CE3 Bit Is Reset to 0                                                      | 285  |

| 7-137   | Compare Operation                                                                               | 286  |

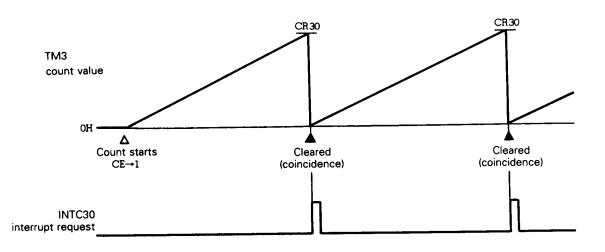

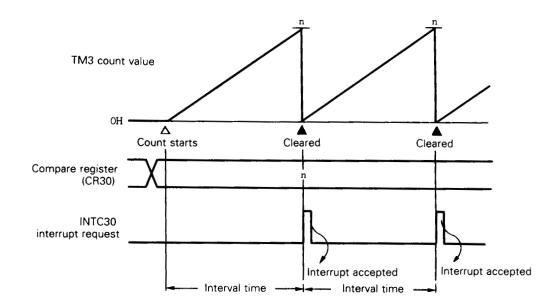

| 7-138   | Interval Timer Operation Timing                                                                 | 287  |

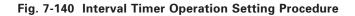

| 7-139   | Control Register Contents for Interval Timer Operation                                          | 288  |

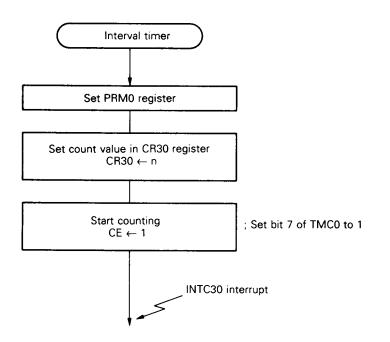

| 7-140   | Interval Timer Operation Setting Procedure                                                      | 288  |

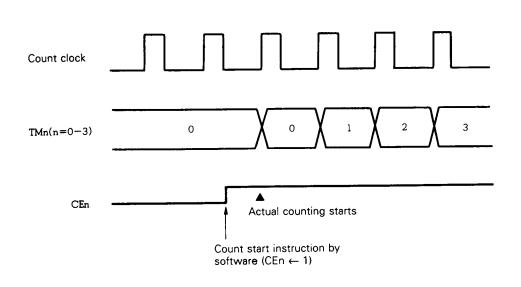

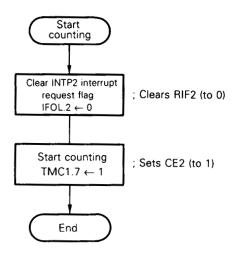

| 7-141   | Operation When Counting Is Started                                                              | 291  |

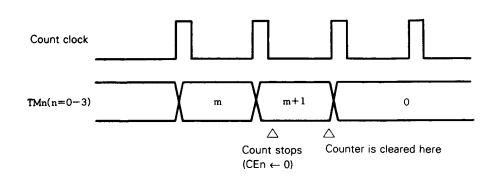

| 7-142   | Stopping Count Operation                                                                        | 292  |

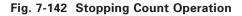

| 7-143   | Stopping and Starting Counting Operation                                                        | 292  |

| 7-144   | PWM Example When Duty Factor Is 100%                                                            | 294  |

| 7-145   | PPG Output Example When Duty Factor Is 100%                                                     | 295  |

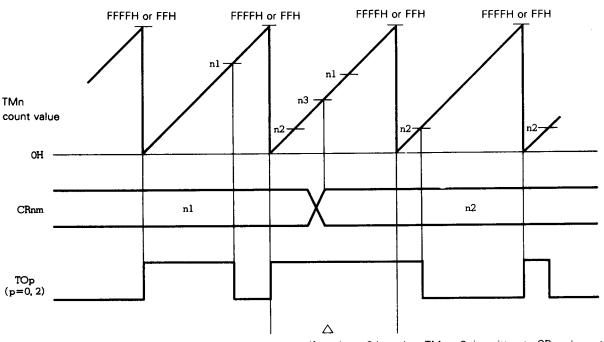

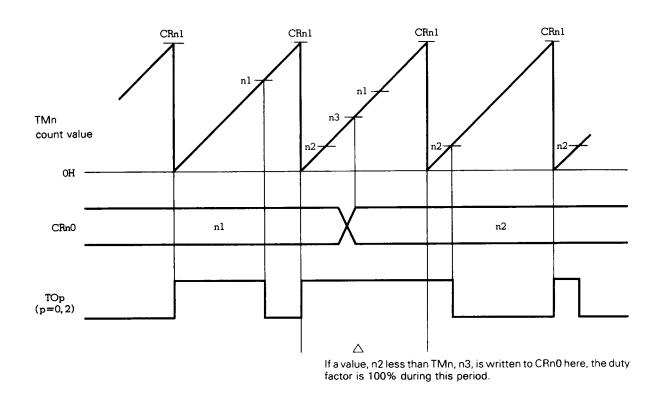

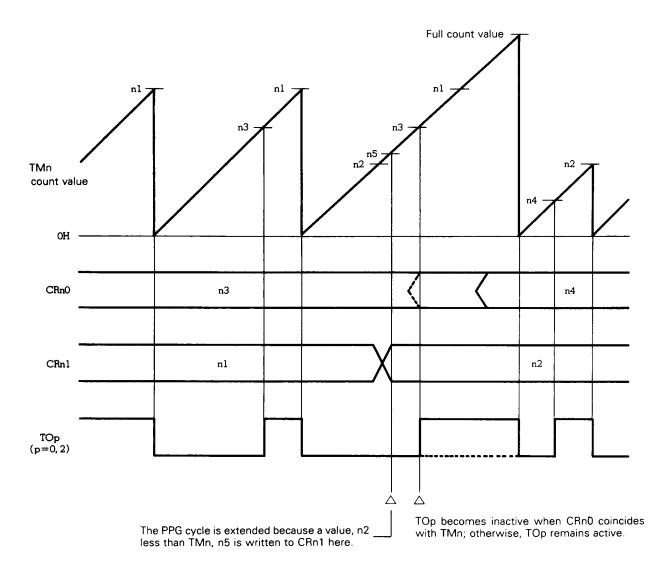

| 7-146   | PPG Output Example When Output Cycle Is Extended                                                | 296  |

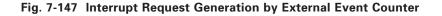

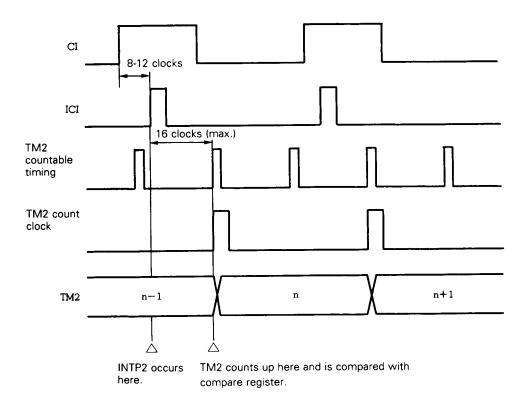

| 7-147   | Interrupt Request Generation by External Event Counter                                          | 299  |

| 7-148   | If One Valid Edge Input Cannot Be Distinguished from No Valid                                   |      |

|         | Edge Input by External Event Counter                                                            | 300  |

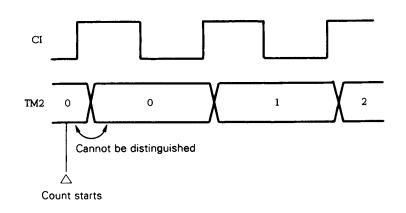

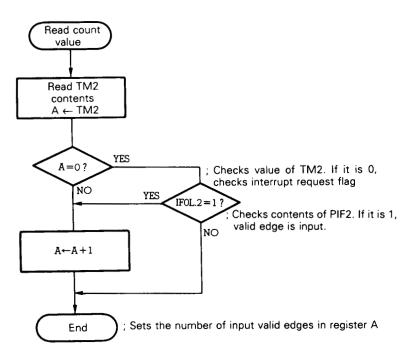

| 7-149   | To Detect Input of One Valid Edge by External Event Counter                                     | 301  |

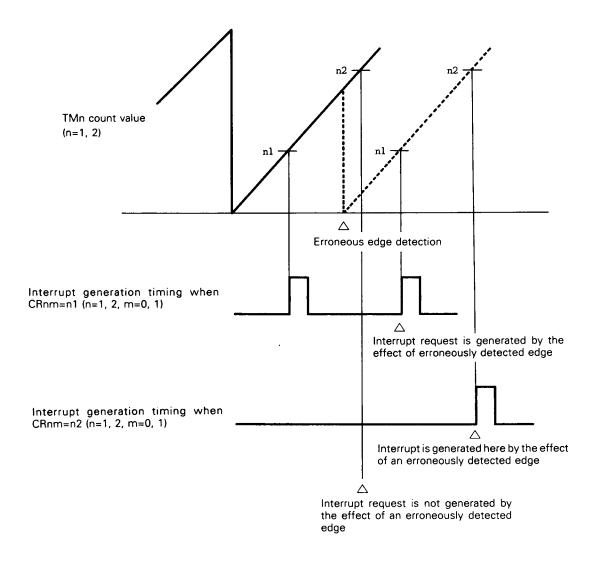

| 7-150   | Timing Change of Interrupt Genration by Erroneously Detected Edge                               | 304  |

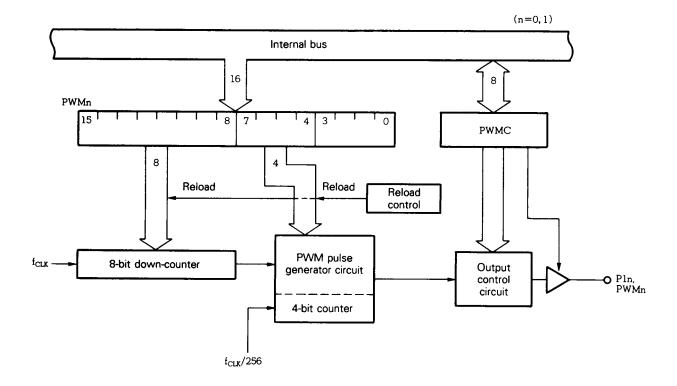

| 8-1     | PWM Output Unit Configuration                                                                   | 305  |

| 8-2     | PWM Control Register (PWMC) Format                                                              | 307  |

| 8-3     | Basic PWM Output Operation                                                                      | 309  |

| 8-4     | Setting Active Level for PWM Output                                                             | 310  |

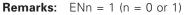

| 8-5     | PWM Output Timing Example 1 (PWM pulse width changing cycle: 2 <sup>12</sup> /f <sub>CLK)</sub> |      |

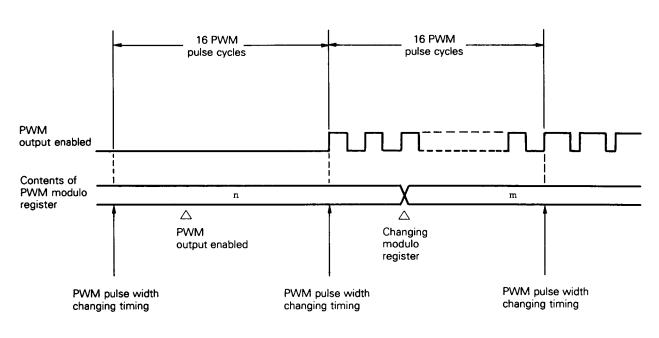

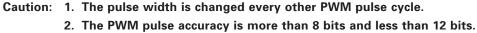

| 8-6     | PWM Output Timing Example 2 (PWM pulse width changing cycle: $2^{8}$ /f <sub>CLK</sub> )        | 312  |

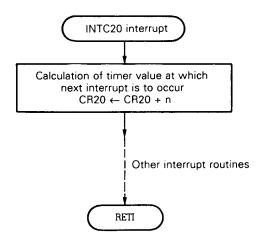

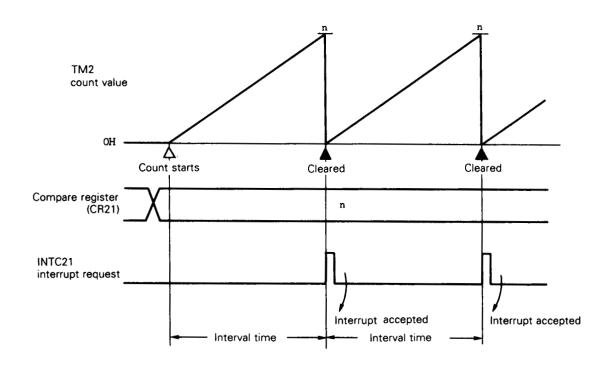

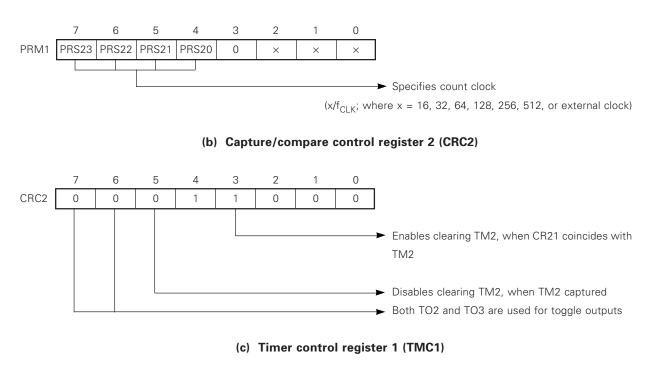

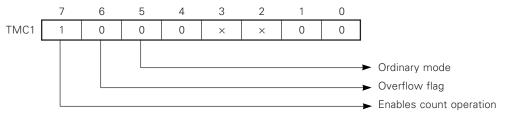

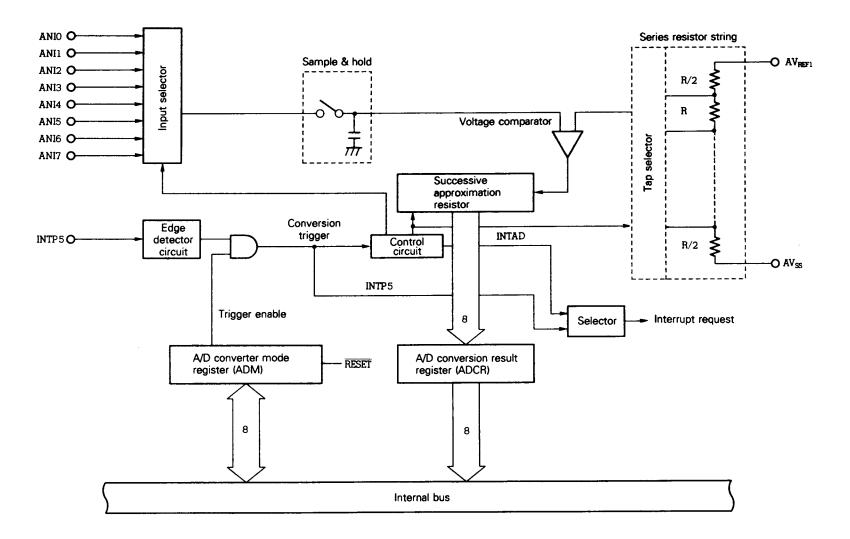

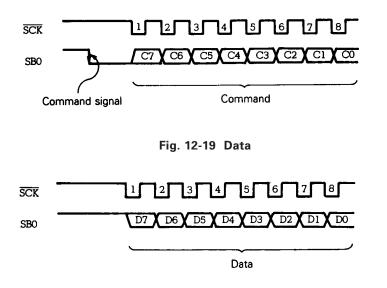

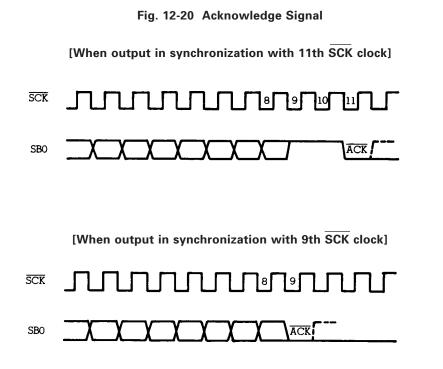

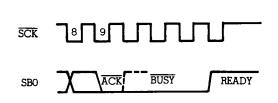

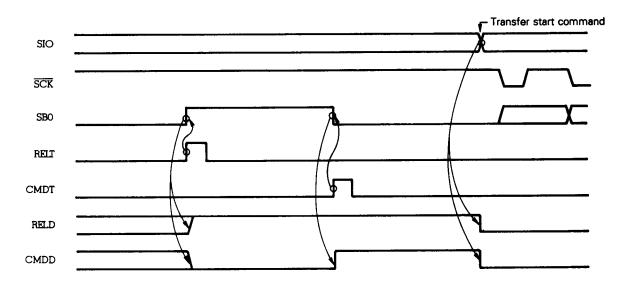

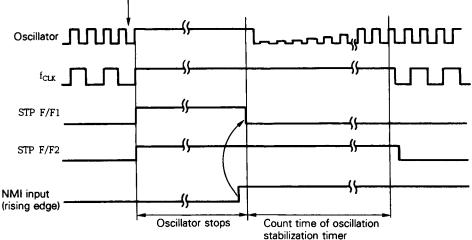

| 9-1     | A/D Converter Configuration                                                                     | 314  |