# User Manual GreenPAK DIP Development Platform UM-GP-007

## Abstract

This user manual provides basic guidelines for the developers to get familiar with the GreenPAK DIP Development Platform. It gives an overview of the hardware, as well as the functional description of this platform, and shows the example projects using SLG46534.

# Contents

| Ab  | stract |           |                                              | .1  |

|-----|--------|-----------|----------------------------------------------|-----|

| Co  | ntents | \$        |                                              | . 2 |

| Fig | jures. |           |                                              | . 3 |

| Та  | bles   |           |                                              | . 3 |

| 1   | Term   | s and De  | efinitions                                   | . 4 |

| 2   | Intro  | duction   |                                              | . 5 |

|     | 2.1    | GreenP    | AK Designer                                  | . 5 |

|     | 2.2    | Support   |                                              | . 5 |

| 3   | Getti  | ng Starte | ed                                           | . 6 |

|     | 3.1    | Introduc  | tion                                         | . 6 |

|     | 3.2    | Install S | oftware                                      | . 6 |

|     | 3.3    | Uninstal  | I Software                                   | . 6 |

| 4   | Hard   | ware      |                                              | . 7 |

|     | 4.1    | Overviev  | w                                            | . 7 |

|     | 4.2    | Functior  | nal Description                              | . 8 |

|     |        | 4.2.1     | Power Supply                                 | . 8 |

|     |        | 4.2.2     | USB Communication                            | . 8 |

|     |        | 4.2.3     | GND Connections                              | . 8 |

|     |        | 4.2.4     | DIP Adapter Connections                      | . 8 |

|     |        | 4.2.5     | Expansion Connector                          | . 9 |

|     |        | 4.2.6     | Pins Connectivity                            | 11  |

|     |        | 4.2.7     | Chip PIN versus Development Board Test Point | 13  |

| 5   | Exam   | ple Proj  | ects using SLG46534                          | 16  |

|     | 5.1    | Project:  | Counter with Clock Enable                    | 16  |

| 6   | Conc   | lusion    |                                              | 27  |

| Ар  | pendi  | x A Elect | rical Specification                          | 28  |

| Re  | vision | History   |                                              | 29  |

|     |        |           |                                              |     |

# **Figures**

| Figure 1: GreenPAK DIP Development Board, Top View                                 | 7  |

|------------------------------------------------------------------------------------|----|

| Figure 2: DIP Adapter Connector Pinout                                             |    |

| Figure 3: Breadboard with GreenPAK DIP Development Board                           | 9  |

| Figure 4: Expansion Connector Pinout                                               |    |

| Figure 5: Expansion Connector Control in GreenPAK Designer                         | 10 |

| Figure 6: Schematic Connection of the VDD Pin                                      |    |

| Figure 7: Schematic Connection of the Data Pin                                     |    |

| Figure 8: Pins and TPs Location                                                    | 14 |

| Figure 9: Pins and TPs Accordance (for SLG46534)                                   | 15 |

| Figure 10: GreenPAK Designer Components                                            | 16 |

| Figure 11: GreenPAK Designer Components List                                       |    |

| Figure 12: Pin 4, 5 Mode                                                           |    |

| Figure 13: Look Up Table Properties Configured as an AND Gate                      | 19 |

| Figure 14: Look Up Table Properties Configured as a NOR Gate                       | 20 |

| Figure 15: Counter Properties                                                      | 21 |

| Figure 16: Oscillator Properties                                                   | 22 |

| Figure 17: Ready Project in GreenPAK Designer                                      | 23 |

| Figure 18: GreenPAK Designer, Emulation Tool                                       |    |

| Figure 19: Generator Settings Window                                               |    |

| Figure 20: Waveform, Triggered on Button Pressed                                   | 25 |

| Figure 21: Waveform, no Triggered on Button Released                               | 26 |

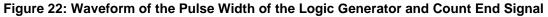

| Figure 22: Waveform of the Pulse Width of the Logic Generator and Count End Signal | 26 |

# **Tables**

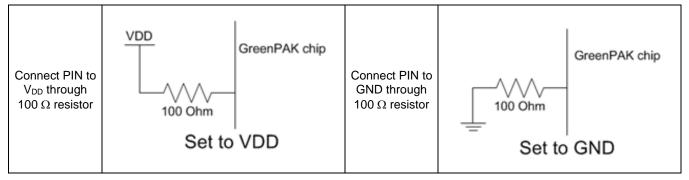

| Table 1: Data Pins Connections Schematics | 1 | 1 |

|-------------------------------------------|---|---|

| Table 2: GreenPAK Pin Configuration       | 1 | 8 |

RENESAS

# **1** Terms and Definitions

| DIP | Dual In-Line Package               |

|-----|------------------------------------|

| GND | Ground                             |

| GP  | General Purpose                    |

| IC  | Integrated Circuit                 |

| IDE | Integrated Development Environment |

| LED | Light Emitting Diode               |

| LUT | Look Up Table                      |

| MCU | Microcontroller Unit               |

| OTP | One-Time Programable               |

| NC  | Not Connected                      |

| RAM | Random-Access Memory               |

| ТР  | Test Point                         |

| USB | Universal Serial Bus               |

| Vdd | Power Supply                       |

|     |                                    |

4 of 30

RENESAS

# 2 Introduction

Thank you for choosing Renesas Electronics products. The GreenPAK DIP Development Platform allows you to develop your custom design using GreenPAK mixed signal ICs. You can design your own projects starting from a blank project, or by altering the sample projects provided at https://www.renesas.com/.

## 2.1 GreenPAK Designer

GreenPAK Designer is an easy-to-use full-featured integrated development environment (IDE) that allows you to specify exactly how you want the device to be configured. This provides you direct access to all GreenPAK device features and complete control over the routing and configuration of a PAK project with just one tool.

With GreenPAK Designer, you can:

- Design the configuration which corresponds to your project needs;

- Verify the project using software interface to GreenPAK DIP Development Platform hardware;

- With simple-to-use and intuitive software and hardware tools you can reduce your project development time and get to market faster.

To start working with GreenPAK Designer please take the following steps:

- Download and install GreenPAK Designer software;

- Configure modules that you will need for your project;

- Interconnect and configure modules;

- Specify the pin out;

- Test your design with the GreenPAK DIP Development Platform.

#### 2.2 Support

Free support for GreenPAK DIP Development Platform is available online at https://www.renesas.com/.

At facebook : https://www.facebook.com/RenesasElectronics/.

GreenPAK Designer will automatically notify you when a new version of software is available. For manual updates please go to https://www.renesas.com/software-tool/go-configure-software-hub.

These resources are also available under the **Help** menu of GreenPAK Designer.

## **3 Getting Started**

#### 3.1 Introduction

This chapter describes how to install and configure the GreenPAK DIP Development Platform. Section 4 provides the details of hardware operation. Section 5 provides an instructions on how to create a simple project example.

#### 3.2 Install Software

GreenPAK Designer software is available free of charge from the Renesas website at https://www.renesas.com/software-tool/go-configure-software-hub page.

## 3.3 Uninstall Software

The software can be uninstalled in the way typical for your operating system. Please refer to your operating system support documentation if you need the specific instructions or visit Section 2.2 of this document for additional support from Renesas.

# RENESAS

## **GreenPAK DIP Development Platform**

## 4 Hardware

#### 4.1 Overview

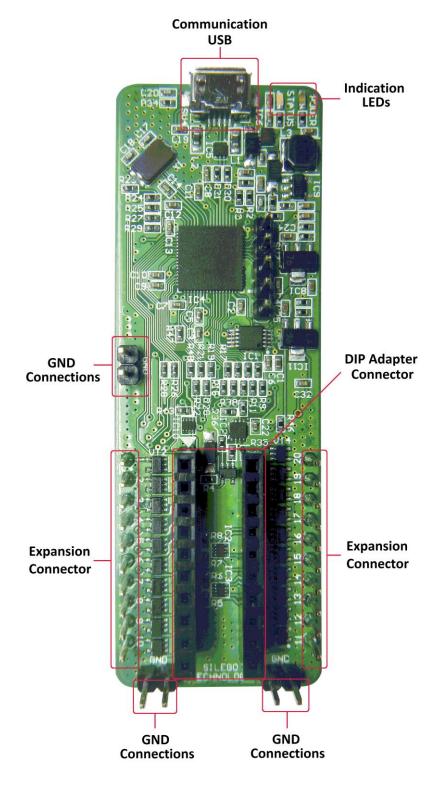

#### Figure 1: GreenPAK DIP Development Board, Top View

| User Manual |

|-------------|

|-------------|

## 4.2 Functional Description

#### 4.2.1 **Power Supply**

The main power source of the GreenPAK DIP Development Board is the USB power line. The Development Board can deliver power from 1.7 V to 5.5 V. To provide this power range the Development Board is equipped with a boost converter.

#### 4.2.2 USB Communication

The board has the USB communications interface that uses the USB mini-B connector. This interface provides communication with the software control tool and supplies power to the board, as described in Section 4.2.1.

#### 4.2.3 **GND Connections**

There are 4 GND pins on the left side, 2 pins on the right side. These can be used for test equipment (oscilloscope, multimeter, and others) ground reference connection or to connect external test circuitry ground.

#### 4.2.4 DIP Adapter Connections

The GreenPAK DIP Development Board should be used with a DIP Adapter board. Its main purpose is to connect the GreenPAK chip to the GreenPAK DIP Development Board. Information about DIP Adapters is available online at https://www.renesas.com/SLG4DVKDIP#documents.

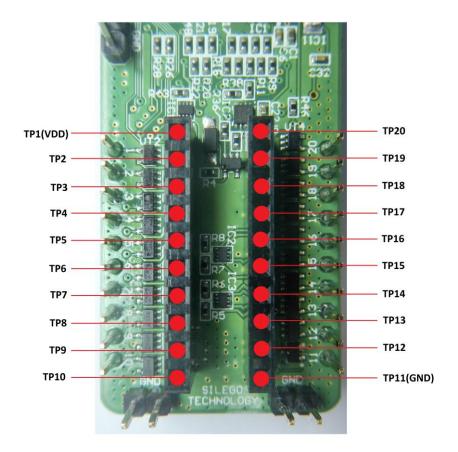

Figure 2: DIP Adapter Connector Pinout

| User Manual | Revision 1.1 | 23-Mar-2022                            |

|-------------|--------------|----------------------------------------|

| CFR0012     | 8 of 30      | © 2022 Renesas Electronics Corporation |

#### 4.2.5 Expansion Connector

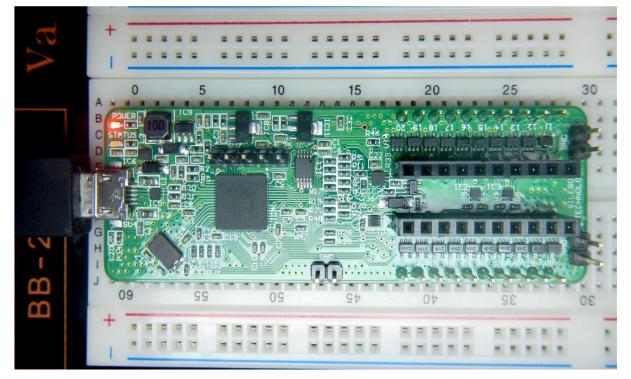

This 20-pins connector is in the right and left bottom part of the Development Board. The Expansion Connector is a standard 0.1" female connector compatible with breadboard, see Figure 3.

Figure 3: Breadboard with GreenPAK DIP Development Board

This port was designed to connect the GreenPAK DIP Development Board to external circuits and apply external power, signal sources, and loads. It can be used to apply the GreenPAK chip into your custom design with minimal additional tools.

**Figure 4: Expansion Connector Pinout**

Each pin, except GND and NC, is controlled through individual analog switch. GreenPAK Designer can enable or disable external pins, as it is shown on Figure 5. There is no individual control of each key: when one key is turned on, all others are also turned on.

Figure 5: Expansion Connector Control in GreenPAK Designer

The Expansion Connector is enabled only in Emulation mode or Test mode. To enter either of these two modes, the target GreenPAK device must be inside the socket the DIP Adapter Connector. When the Test mode button is pressed, the software will first read the chip to verify if it was inserted correctly, and then configure the GreenPAK DIP Development Board as it was set in Emulation mode. After the Emulation button is pressed, the software will automatically perform the following steps:

- Check chip presence;

- Open all expansion port switches (allowing external signals/loads to be left connected to Expansion Connector);

- Load target configuration into the target GreenPAK device using internal power;

- Configure Development Board as it was selected in Emulation Tool window.

Note that the GreenPAK device has internal OTP memory which is normally loaded into RAM registers at initialization time. "Emulation mode" will bypass this load and write the updated version of the project directly into the RAM register inside the GreenPAK chip many times, but after power loss all internal data will be lost. Also, when the GreenPAK chip is already programmed - user can use Emulation mode

| Iser Manual |  |

|-------------|--|

|             |  |

**Revision 1.1**

to load another project and test it on the emulation tool during the Emulation mode, in that case emulation data will be cleared. The "Emulation mode" is not necessary for checking programmed parts: in this case the "Test mode" will supply power to the device, which will perform the standard load of configuration data from OTP to RAM. The difference between the "Emulation" and the "Test mode" is that in the "Test mode" the process of loading configuration memory is skipped and after the chip power the OTP memory loads into RAM registers.

The Expansion Connector has the following type of connections:

- 1. V<sub>DD</sub>

- 2. GND

- 3. Data

The V<sub>DD</sub> connection allows the user to both use internal power supply to power the external circuit, and use external power source as the on-board chip power. This selection to use either internal or external power is made in the Emulator Controls window.

The GND connection is connected directly to the GreenPAK DIP Development Board ground and cannot be controlled or switched.

Data connections are the easiest way to connect external signals to the GreenPAK chip. They are software controlled switches that are controlled in the Emulator Controls window.

#### 4.2.6 Pins Connectivity

The Socket connector has the following type of connections:

- $1. \quad V_{\text{DD}}$

- 2. GND

- 3. Data

The GreenPAK DIP Development Board supports connecting five types of loads and signal sources. Each source has its own special purpose.

For V<sub>DD</sub> pins is only available a signal generator connection.

For the Data pins the following connections are available: V<sub>DD</sub>, GND, Pull-up, Pull-down, Configurable Button.

| Table 1: Data Pins | Connections Schematics |

|--------------------|------------------------|

|--------------------|------------------------|

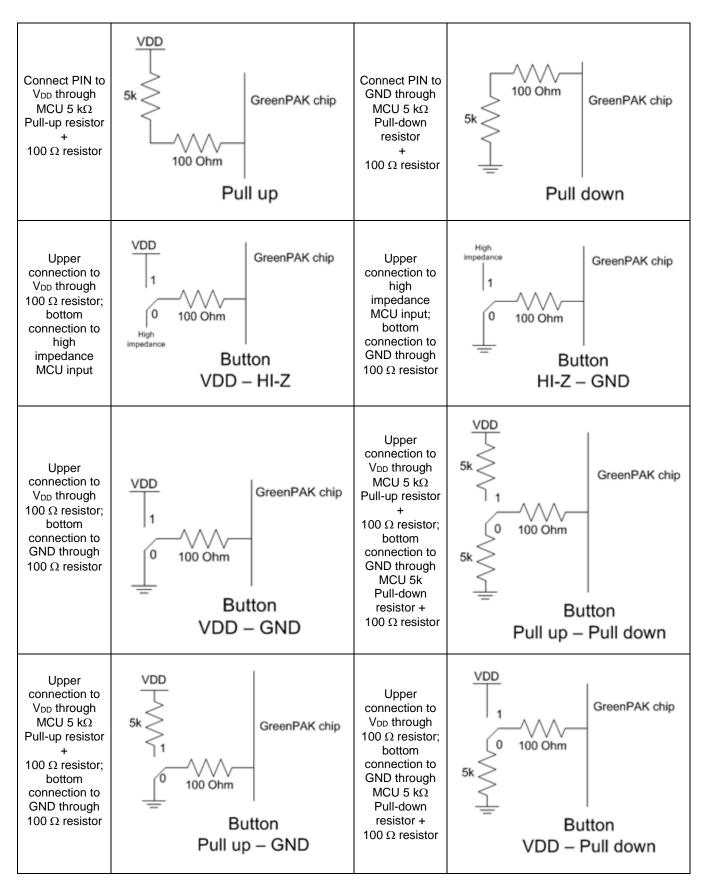

Figure 6 shows the schematic connection of the GP  $V_{DD}$  pins.

**User Manual**

#### Figure 6: Schematic Connection of the $V_{DD}$ Pin

Note 1 If chip has  $V_{DD2}$ . For more information see chip datasheet.

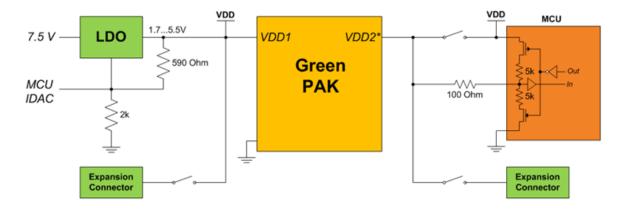

Figure 7 shows the schematic connection of the GP data pins.

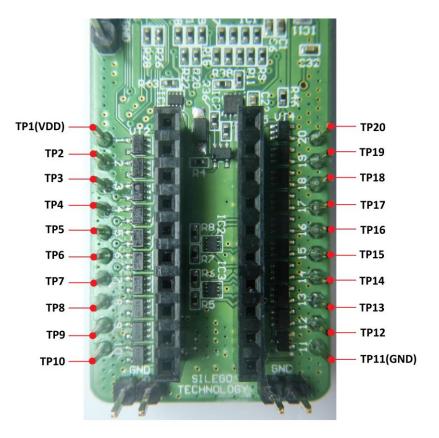

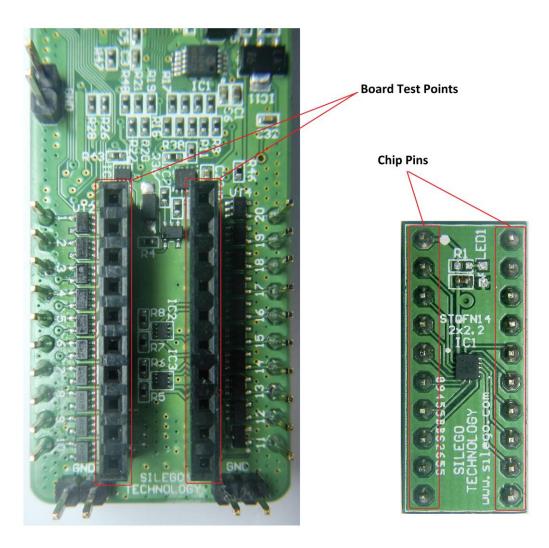

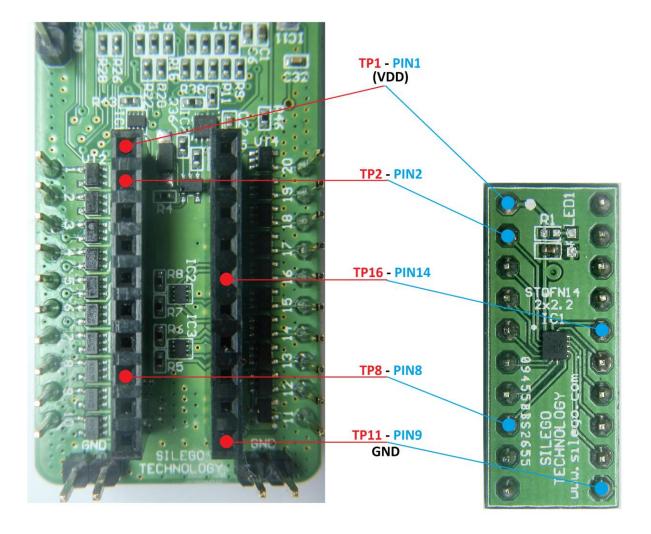

#### 4.2.7 Chip PIN versus Development Board Test Point

Before you start working with a chip you need to understand the difference between such concepts as PIN (chip pin) and TP (the Development Board test point). Figure 8 shows where PINs and TPs are.

| lleor | Manual |

|-------|--------|

| USCI  | Manual |

#### Figure 8: Pins and TPs Location

PINs refer to the physical pins that are on the chip package (their marking can be seen in the datasheet). TPs refer to the DIP Adapter and Expansion connector pins. TP and PIN numbers may not match since different PINs on the chip have different functions, see Figure 9.

Figure 9: Pins and TPs Accordance (for SLG46534)

# 5 Example Projects using SLG46534

## 5.1 **Project: Counter with Clock Enable**

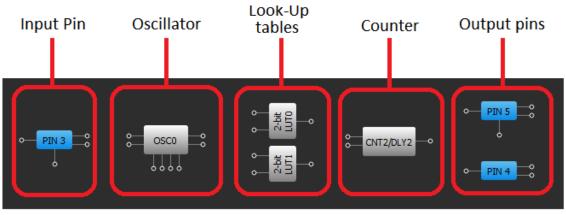

Blocks required:

- 1 digital input

- 2 digital outputs

- 2 Look Up Tables with two inputs

- 1 Counter

- 1 Oscillator

Figure 10: GreenPAK Designer Components

All these components can be found in Components List. If there are no components on the work area - make sure this component is enabled by checking appropriate boxes.

| Components List            |                                     |  |  |

|----------------------------|-------------------------------------|--|--|

| Components                 |                                     |  |  |

| ▼ I/O PADs                 |                                     |  |  |

| · 1/017                    | VDD (PIN 1)                         |  |  |

| ·                          | PIN 2                               |  |  |

| 1                          | PIN 3                               |  |  |

| · · ·                      | PIN 4                               |  |  |

| 1                          | PIN 5                               |  |  |

| 1                          | PIN 6                               |  |  |

| ✓                          | PIN 7                               |  |  |

|                            | PIN 8                               |  |  |

| ✓                          | GND (PIN 9)                         |  |  |

|                            | PIN 10                              |  |  |

|                            | PIN 11                              |  |  |

|                            | PIN 12                              |  |  |

|                            | PIN 13                              |  |  |

|                            | PIN 14                              |  |  |

| Analo                      | g Comparators                       |  |  |

|                            | A CMP0                              |  |  |

|                            | A CMP1                              |  |  |

|                            | A CMP2                              |  |  |

| <ul> <li>Specia</li> </ul> | al components                       |  |  |

|                            | P DLY                               |  |  |

| 1                          | POR<br>OSC0                         |  |  |

| v                          | OSC1                                |  |  |

| 1                          |                                     |  |  |

| Ľ.                         | Crystal OSC                         |  |  |

|                            | ASM                                 |  |  |

| ▼ Comb                     | ination Function components         |  |  |

|                            | FILTER0/EDGE DET0                   |  |  |

|                            | FILTER 1/EDGE DET 1                 |  |  |

| 1                          | 2-bit LUT0/DFF/LATCH0               |  |  |

| √                          | 2-bit LUT1/DFF/LATCH1               |  |  |

|                            | 2-bit LUT2/DFF/LATCH2               |  |  |

|                            | 2-bit LUT3/PGEN                     |  |  |

|                            | 3-bit LUT0/DFF/LATCH3               |  |  |

|                            | 3-bit LUT1/DFF/LATCH4               |  |  |

|                            | 3-bit LUT2/DFF/LATCH5               |  |  |

|                            | 3-bit LUT3/DFF/LATCH6               |  |  |

|                            | 3-bit LUT4/DFF/LATCH7               |  |  |

| ✓                          | 3-bit LUT5/8-bit CNT2/DLY2          |  |  |

|                            | 3-bit LUT6/8-bit CNT3/DLY3          |  |  |

|                            | 3-bit LUT7/8-bit CNT4/DLY4          |  |  |

|                            | 3-bit LUT8/8-bit CNT5/DLY5          |  |  |

|                            | 3-bit LUT9/8-bit CNT6/DLY6          |  |  |

|                            | 3-bit LUT10/Pipe Delay              |  |  |

|                            | 4-bit LUT0/WS Ctrl/16-bit CNT0/DLY0 |  |  |

|                            | 4-bit LUT1/16-bit CNT1/DLY1/FSM1    |  |  |

**Revision 1.1**

| Pin # | Pin Name          | Туре             | Pin Description |

|-------|-------------------|------------------|-----------------|

| 1     | Vdd               | PWR              | Supply Voltage  |

| 3     | Enable            | Digital Input    | Digital Input   |

| 4     | Counter Output    | Push-Pull Output | Digital Output  |

| 5     | Oscillator Output | Push-Pull Output | Digital Output  |

| 9     | GND               | GND              | Ground          |

#### Table 2: GreenPAK Pin Configuration

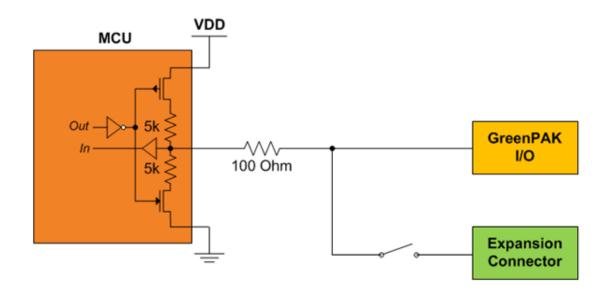

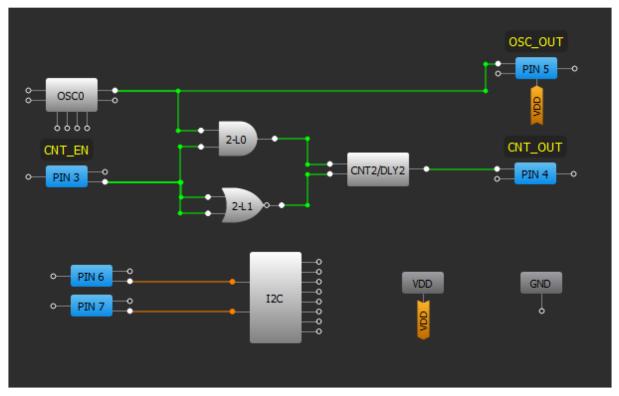

All components used in this project are shown on Figure 10. Next step is to configure selected blocks. Double click on PIN4 to open "Properties" panel. Select "Digital output" in **I/O Selection** field and then select "1x push pull" from the drop-down menu in **Output mode** field and hit "Apply" button. Make the same settings for PIN5.

| Properties          |                                                    |                    | ×                  | Properties    |                  |                  | ×                |

|---------------------|----------------------------------------------------|--------------------|--------------------|---------------|------------------|------------------|------------------|

| PIN 4               |                                                    |                    |                    | PI            | N 5              |                  |                  |

| I/0 select          | ion: C                                             | )igital output     | • •                | I/O selec     | tion: [          | Digital output   | t v              |

| Input mode: None    |                                                    | Input mo<br>OE = 0 | de:                | lone          | -                |                  |                  |

| Output mo<br>OE = 1 | Output mode:   1x push pull     OE = 1   Transform |                    | Output m<br>OE = 1 | iode:         | tx push pull     | •                |                  |

| Resistor:           | F                                                  | loating            | -                  | Resistor:     | F                | loating          | Ŧ                |

| Resistor v          | value: F                                           | loating            | •                  | Resistor      | value:           | loating          | -                |

|                     | Information Information                            |                    |                    |               |                  |                  |                  |

| Electrical Spe      | ecifications                                       |                    |                    | Electrical Sp | ecifications     |                  |                  |

|                     | 1.8 V<br>min/max                                   | 3.3 V<br>min/max   | 5.0 V<br>min/max   |               | 1.8 V<br>min/max | 3.3 V<br>min/max | 5.0 V<br>min/max |

| V_OH (V)            | 1.690/-                                            | 2.700/-            | 4.150/-            | V_OH (V)      | 1.690/-          | 2.700/-          | 4.150/-          |

| V_OL (V)            | -/0.013                                            | -/0.230            | -/0.240            | V_OL (V)      | -/0.013          | -/0.230          | -/0.240          |

| I_OH (mA)           | 1.070/-                                            | 6.050/-            | 22.080/-           | I_OH (mA)     | 1.070/-          | 6.050/-          | 22.080/-         |

| I_OL (mA)           | 0.920/-                                            | 4.880/-            | 7.220/-            | I_OL (mA)     | 0.920/-          | 4.880/-          | 7.220/-          |

| -                   | -/-                                                | -/-                | -/-                | -             | -/-              | -/-              | -/-              |

| -                   | -/-                                                | -/-                | -/-                | -             | -/-              | -/-              | -/-              |

| 0                   |                                                    |                    |                    |               |                  |                  |                  |

#### Figure 12: Pin 4, 5 Mode

The next component in this design is Look Up Table. First Look Up Table (LUT0) is used to generate logic "1" only when there are high logic levels on both inputs (AND gate). Select AND gate from "Standard gates" drop-down menu or set table manually. Second Look Up Table (LUT1) is configured as NOR gate. It is used to generate reset signal for counter on PIN3 falling edge.

| llcor | Manual |

|-------|--------|

| USCI  | manuai |

| Properties              | ;          |          |        | ×     |

|-------------------------|------------|----------|--------|-------|

|                         | 2-bit LU   | JTO/DFF/ | LATCHO |       |

| Type:                   |            | LUT      |        | •     |

| IN3                     | IN2        | IN1      | IN0    | OUT   |

| 0                       | 0          | 0        | 0      | 0     |

| 0                       | 0          | 0        | 1      | 0     |

| 0                       | 0          | 1        | 0      | 0     |

| 0                       | 0          | 1        | 1      | 1     |

| 0                       | 1          | 0        | 0      | 0     |

| 0                       | 1          | 0        | 1      | 0     |

| 0                       | 1          | 1        | 0      | 0     |

| 0                       | 1          | 1        | 1      | 0     |

| 1                       | 0          | 0        | 0      | 0     |

| 1                       | 0          | 0        | 1      | 0     |

| 1                       | 0          | 1        | 0      | 0     |

| 1                       | 0          | 1        | 1      | 0     |

| 1                       | 1          | 0        | 0      | 0     |

| 1                       | 1          | 0        | 1      | 0     |

| 1                       | 1          | 1        | 0      | 0     |

| 1                       | 1          | 1        | 1      | 0     |

| Standard gates All to 0 |            |          |        |       |

| AND  All to 1           |            |          |        |       |

| Re                      | gular shap | pe       | In     | ivert |

|                         | 5          | Ð        | Арр    | ly    |

Figure 13: Look Up Table Properties Configured as an AND Gate

| Properties           | ;                       |     |      | ×    |

|----------------------|-------------------------|-----|------|------|

|                      | 2-bit LUT1/DFF/LATCH1   |     |      |      |

| Туре:                |                         | LUT |      | •    |

| IN3                  | IN2                     | IN1 | IN0  | OUT  |

| 0                    | 0                       | 0   | 0    | 1    |

| 0                    | 0                       | 0   | 1    | 0    |

| 0                    | 0                       | 1   | 0    | 0    |

| 0                    | 0                       | 1   | 1    | 0    |

| 0                    | 1                       | 0   | 0    | 0    |

| 0                    | 1                       | 0   | 1    | 0    |

| 0                    | 1                       | 1   | 0    | 0    |

| 0                    | 1                       | 1   | 1    | 0    |

| 1                    | 0                       | 0   | 0    | 0    |

| 1                    | 0                       | 0   | 1    | 0    |

| 1                    | 0                       | 1   | 0    | 0    |

| 1                    | 0                       | 1   | 1    | 0    |

| 1                    | 1                       | 0   | 0    | 0    |

| 1                    | 1                       | 0   | 1    | 0    |

| 1                    | 1                       | 1   | 0    | 0    |

| 1                    | 1                       | 1   | 1    | 0    |

| Standard             | Standard gates All to 0 |     |      |      |

| NOR                  | NOR  All to 1           |     |      | to 1 |

| Regular shape Invert |                         |     | vert |      |

|                      | 5                       | Ð   | App  | ly   |

Figure 14: Look Up Table Properties Configured as a NOR Gate

Figure 15 shows counter properties.

| Properties                  | ×                     |

|-----------------------------|-----------------------|

| 3-bit LUT5                  | /8-bit CNT2/DLY2      |

| Туре:                       | CNT/DLY -             |

| Mode:                       | Counter 💌             |

| Counter data:               | 4                     |

| Output period<br>(typical): | N/D Formula           |

| Edge select:                | Rising -              |

| Output polarity:            | Non-inverted (OUT) 🔻  |

| Q mode:                     | None 💌                |

| Stop and restart:           | None 💌                |

| Cor                         | nnections             |

| Clock:                      | Ext. Clk. (From mat 💌 |

| Clock source:               | Ext. Clk. (matrix)    |

| Clock<br>frequency:         | <u>N/D</u>            |

|                             | D Apply               |

**Figure 15: Counter Properties**

Figure 16 shows oscillator properties.

| Properties 🗵                 |                     |  |

|------------------------------|---------------------|--|

| OSC0                         |                     |  |

| Control pin<br>mode:         | Power down 💌        |  |

| 05C Power<br>Mode:           | Force Power On 🔹    |  |

| Clock selector:              | OSC 💌               |  |

| Fast start-up:               | Disable 💌           |  |

| RC 05C<br>Frequency:         | 25 kHz 💌            |  |

| 'CLK' predivider<br>by:      | 8 •                 |  |

| 'OUTO' second<br>divider by: | 64 💌                |  |

| 'OUT1' second<br>divider by: | 1 •                 |  |

| Information                  |                     |  |

| Frequency                    |                     |  |

| Clock output conf            | iguration:          |  |

| RC OSC Output                | Value               |  |

| CLK /4                       | RC OSC Freq. /8 /4  |  |

| CLK /12                      | RC OSC Freq. /8 /12 |  |

| CLK /24                      | RC OSC Freq. /8 /24 |  |

| CLK /64                      | RC OSC Freq. /8 /64 |  |

| OUTO                         | RC OSC Freq. /8 /64 |  |

| OUT1                         | RC OSC Freq. /8     |  |

| 0 >                          | Apply               |  |

**Figure 16: Oscillator Properties**

The Final step is to connect each of the selected components. Use Wire tool to perform this action. To

connect two pins select "Set Wire" and then click on the first and the second pins of the module or modules that you want to connect. The trace will be automatically routed.

Figure 17 displays ready project with configured blocks and wire connections.

#### Figure 17: Ready Project in GreenPAK Designer

Use the GreenPAK DIP Development Board to test this project. Connect USB cable to GreenPAK DIP Development Board, if everything is correct, you will see two blinks of green LED, and then LED becomes red. Then press "Emulation" button. This will open emulation tool. Using it you can load code of your project to the chip.

In emulation tool from drop down menu in the right down corner select "GreenPAK DIP Development Board", see Figure 18.

| Debugging controls      |                            | 0 ×               |

|-------------------------|----------------------------|-------------------|

|                         | Debugging Controls         |                   |

| GreenPAK DI<br>Platform | P Development              | Change platform   |

| Device: Onboard         | •                          | I2C Reset         |

|                         |                            | Read              |

| Emulation 💌             | Test Mode                  | Program           |

|                         |                            | Project Data      |

| Start All               | Pause All                  | Stop All          |

| 2 4 6 8 10 12           | 14 16 18 20 Vb             | 22 24 26 28 30 32 |

| Va 3 5 7 9 G            | 13 15 17 19                | 21 23 25 27 29 31 |

| Int. VDD Ext. VDD       | ON OFF<br>LEDs ON LEDs OFF | TP Map            |

Figure 18: GreenPAK Designer, Emulation Tool

To test this project, we will use the following tools:

- Signal generator. Signal generator is applied to V<sub>DD</sub> pin to power GreenPAK chip;

- Button is a software simulation of the real button. It switches PIN between V<sub>DD</sub> and GND signal levels.

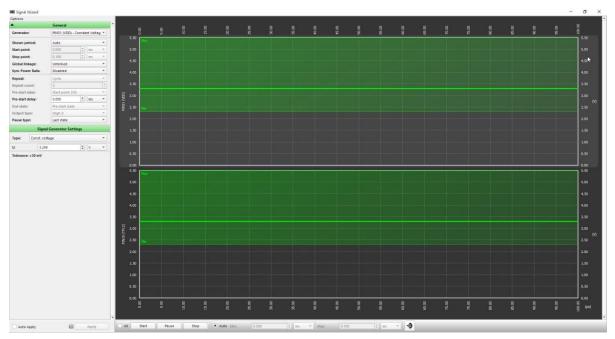

The Signal generator is presented as power source for the GreenPAK chip (at  $V_{DD}$  pin). By default, it's configured to output source constant 3.3 V. To see signal generators settings click on the "Edit" button near the  $V_{DD}$  pin, see Figure 19.

| User Manual |

|-------------|

|-------------|

Figure 19: Generator Settings Window

It is necessary to connect virtual button to the PIN3. To do so click on "Button" item in TP3 context menu.

After all settings have done, click button "Emulation" from Emulation Tool window to start emulation process.

#### Functionality Waveform

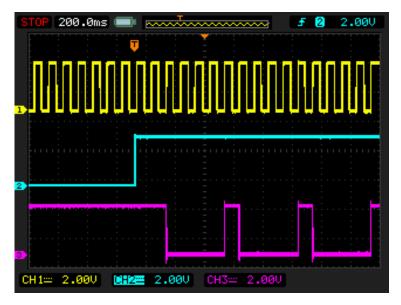

Channel 1 (yellow/top) – Oscillator Output Channel 2 (light blue/2nd line) – Button, 1 - enable Counter; 0 - disable Counter Channel 3 (magenta/3rd line) – Counter output

Figure 20: Waveform, Triggered on Button Pressed

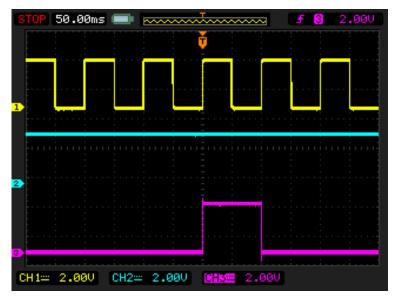

Channel 1 (yellow/top) – Oscillator Output

Channel 2 (light blue/2nd line) – Button, 1 - enable Counter; 0 - disable Counter Channel 3 (magenta/3rd line) – Counter output

| lleor | Manual |

|-------|--------|

| USCI  | Manual |

Figure 21: Waveform, no Triggered on Button Released

Channel 1 (yellow/top) – Oscillator Output

Channel 2 (light blue/2nd line) – Button, 1 - enable Counter; 0 - disable Counter Channel 3 (magenta/3rd line) – Counter output

As it is shown in Figure 21 and Figure 22 Counter works only when the button is pressed.

| User | Manual |  |

|------|--------|--|

|      |        |  |

# 6 Conclusion

This Development Platform is a truly versatile tool. It allows the designer to create a custom project within minutes.

For more information please visit our website https://www.renesas.com/.

27 of 30

RENESAS

# **Appendix A Electrical Specification**

| Mode                                                         | Parameter                                               | Min | Тур             | Мах  | Units |

|--------------------------------------------------------------|---------------------------------------------------------|-----|-----------------|------|-------|

| General                                                      | Test Point Capacitance                                  | 20  |                 |      | pF    |

|                                                              | Input Leakage Current                                   |     |                 | 1    | nA    |

|                                                              | Max Current through Protection Diode to $V_{\text{DD}}$ |     |                 | 0.1  | mA    |

|                                                              | Voltage Range                                           | 1.7 |                 | 5.5  | V     |

| Power Supply                                                 | V <sub>DD</sub> Max Current                             |     |                 | 100  | mA    |

|                                                              | Voltage Output Total Error                              |     |                 | ±30  | mV    |

| Virtual Button, V <sub>DD</sub> /GND,<br>Pull-Up/Down Driver | Output Level High                                       |     | V <sub>DD</sub> |      |       |

|                                                              | Output Level Low                                        |     | GND             |      |       |

|                                                              | Strong Drive (V <sub>DD</sub> /GND) Resistance          |     | 100             |      | Ω     |

|                                                              | Pull-Up/Down Resistance                                 | 3.5 | 5.6             | 8.5  | kΩ    |

| Expansion Connector<br>Switch                                | Max Voltage                                             |     |                 | 5.5  | V     |

|                                                              | Continuous Current through Any<br>Terminal              |     |                 | ±400 | mA    |

|                                                              | Switch On-Resistance                                    |     | 1.2             |      | Ω     |

|                                                              | External VDD Switch On-Resistance                       |     | 1.2             |      | Ω     |

|                                                              | On Leakage Current                                      | -1  |                 | 1    | uA    |

|                                                              | Off Leakage Current                                     | -1  |                 | 1    | uA    |

# **Revision History**

| Revision | Date        | Description                                     |  |  |

|----------|-------------|-------------------------------------------------|--|--|

| 1.1      | 23-Mar-2022 | Renesas rebranding                              |  |  |

| 1.0      | 15-Sep-2021 | Updated according to Dialog's Writing Guideline |  |  |

**User Manual**

#### **Status Definitions**

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### **RoHS Compliance**

Renesas Electronics Corporation's suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

**User Manual**

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.