# SSP v2.6.1

## **Release Note**

Renesas Synergy™ Platform Synergy Software Synergy Software Package

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Renesas Electronics

Rev.1.12 Jul 2024

## Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### www.renesas.com

## Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

## **Contact information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="http://www.renesas.com/contact/">www.renesas.com/contact/</a>.

Renesas Synergy™ Platform

## SSP v2.6.1 Release Note

## Contents

| 1.        | Introduction                                                                | 3   |

|-----------|-----------------------------------------------------------------------------|-----|

| 2.        | Release Information                                                         | 3   |

| 3.        | Synergy MCU Groups Supported                                                | 3   |

| 4.<br>4.1 | Software Tools and Hardware Kits Supported with this SSP Release            |     |

| 5.        | SSP Release Package and Installation Information with e <sup>2</sup> studio | 7   |

| 6.        | SSP Release Package and Installation Information with SSC                   | . 9 |

| 7.        | Issues Fixed in SSP v2.6.1                                                  | 9   |

| 8.        | Known Issues and Limitations in SSP v2.6.1                                  | 9   |

| 8.1       | BSP for SSP Supported Platforms                                             | 9   |

| 8.2       | Creation of Pin Mapper Input xml Files                                      | 9   |

| 8.3       | Crypto/r_sce                                                                | .10 |

| 8.4       | FileX Development                                                           | .10 |

| 8.5       | File System                                                                 | .10 |

| 8.6       | ISDE User Experience                                                        | .10 |

| 8.7       | NetX and NetX Duo                                                           | .11 |

| 8.8       | r_agt_input_capture                                                         | .11 |

| 8.9       | r_rspi                                                                      | .12 |

| 8.10      | r_sci_spi                                                                   | .12 |

| 8.11      | sf_ble                                                                      | .12 |

| 8.12      | sf_cellular                                                                 | .13 |

| 8.13      | sf_el_fx records                                                            | .13 |

| 8.14      | sf_el_gx                                                                    | .13 |

| 8.15      | sf_el_nx                                                                    | .13 |

| 8.16      | sf_el_tx                                                                    | .14 |

| 8.17      | sf_el_ux                                                                    | .14 |

| 8.18      | sf_Wifi                                                                     | .15 |

| 8.19      | sf_wifi_qca4010                                                             | .15 |

| 8.20      | SSP IAR Support                                                             | .15 |

| 8.21      | SSP XMLs for ISDEs                                                          | .16 |

| 8.22      | TES                                                                         | .16 |

| 8.23      | USBX                                                                        | .17 |

| 8.24 Known Issues in Synergy Development Tools                     | 17 |

|--------------------------------------------------------------------|----|

| 8.24.1 Pin Mapping Issues                                          | 17 |

| 8.24.2 Synergy Tools                                               | 19 |

| 9. Complete List of Modules Supported in this Release              |    |

| 9.1 BSP and Driver Modules Available in this Release               | 21 |

| 9.2 Framework Modules Supported in this Release                    | 23 |

| 9.3 Third-Party Modules Supported in this Release                  | 24 |

| 9.4 Cryptographic Functions for Each MCU Supported in this Release | 27 |

| 9.5 Experimental Modules Supported in this Release                 | 28 |

| 10. Additional Technical Notes                                     |    |

| Revision History                                                   |    |

## 1. Introduction

This document describes the release notes for Synergy Software Package (SSP) version 2.6.1.

## 2. Release Information

| SSP Release Version | v2.6.1       |

|---------------------|--------------|

| Release Date        | Jul 22, 2024 |

The intended audience for this release note is Renesas Synergy<sup>™</sup> customers, prospective customers, partners, and support staff. This release note describes the enhancements, fixed issues, and known issues in SSP v2.6.1.

Note: All SSP v2.0.0 and later releases no longer require a Synergy license key.

## 3. Synergy MCU Groups Supported

MCU Groups: S7G2, S5D9, S5D5, S5D3, S3A7, S3A6, S3A3, S3A1, S128, S124, and S1JA.

## 4. Software Tools and Hardware Kits Supported with this SSP Release

| Tool                                                                 | Version              | Description                                                                            | Remarks                                                                                                                                                                                                 |

|----------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| e <sup>2</sup> studio                                                | 2024-01.1            | Software development and debugging tool.                                               | e <sup>2</sup> studio for Synergy standalone<br>installer is no longer provided on<br>the website. If needed, please<br>use <u>Renesas Knowledge Base</u><br>and enter a ticket request.                |

| IAR<br>Embedded<br>Workbench <sup>®</sup><br>for Renesas<br>Synergy™ | 8.23.3               | Software development<br>environment and debugging<br>tool.                             | Renesas no longer distributes<br>IAR tool chain, contact IAR:<br><u>https://www.iar.com/products/ar</u><br><u>chitectures/renesas/iar-</u><br><u>embedded-workbench-for-</u><br><u>renesas-synergy/</u> |

| SSC                                                                  | 2024-01.1            | Synergy Standalone<br>Configurator.<br>Used in combination with IAR<br>EW for Synergy. | Available here for downloading:<br>https://www.renesas.com/in/en/s<br>oftware-tool/renesas-synergy-<br>standalone-configurator-ssc                                                                      |

| GNU Arm<br>Compiler                                                  | GCC 10.3-<br>2021.10 | GNU compiler is an open-<br>source compiler provided by<br>Arm <sup>®</sup>            | https://developer.arm.com/tools-<br>and-software/open-source-<br>software/developer-tools/gnu-<br>toolchain/gnu-rm/downloads                                                                            |

| IAR<br>Compiler                                                      | 8.23.3               | IAR Arm <sup>®</sup> compiler toolchain                                                | Renesas no longer distributes<br>IAR tool chain, contact IAR:<br><u>https://www.iar.com/products/ar</u><br><u>chitectures/renesas/iar-</u><br><u>embedded-workbench-for-</u><br><u>renesas-synergy/</u> |

| QE for<br>Capacitive<br>Touch                                        | v3.5                 | Development Assistance Tool<br>for Capacitive Touch Sensors                            | https://www.renesas.com/us/en/<br>software-tool/qe-capacitive-<br>touch-development-assistance-<br>tool-capacitive-touch-sensors                                                                        |

| RYZ014A<br>Pmod                                                      | v01                  | Expansion board for RYZ014A module                                                     | RTKYZ014A0B00000BE -<br>PMOD Expansion Board for<br>RYZ014A   Renesas                                                                                                                                   |

| ΤοοΙ                                                        | Version | Description                                                                                           | Remarks                                                                                                                                                           |

|-------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                             |         |                                                                                                       | Note: RYZ014A Pmod Not<br>Recommended for New<br>Designs                                                                                                          |

| PE-HMI1                                                     | 2.0     | Product Example (PE) for<br>Human Machine Interface to<br>evaluate Renesas Synergy™<br>S7G2 MCU Group | https://www.renesas.com/us/en/<br>products/microcontrollers-<br>microprocessors/renesas-<br>synergy-platform-<br>mcus/yspehmi1s20ws2j-pe-<br>hmi1-product-example |

| DK-S7G2                                                     | 4.1     | Development Kit for Renesas<br>Synergy™ S7G2 MCU Group                                                | https://www.renesas.com/us/en/<br>products/microcontrollers-<br>microprocessors/renesas-<br>synergy-platform-<br>mcus/ysdks7g2e40-dk-s7g2-<br>development-kit     |

| SK-S7G2                                                     | 3.3     | Starter Kit for Renesas<br>Synergy™ S7G2 MCU Group                                                    | https://www.renesas.com/us/en/<br>products/microcontrollers-<br>microprocessors/renesas-<br>synergy-platform-<br>mcus/yssks7g2e30-sk-s7g2-<br>starter-kit         |

| PK-S5D9                                                     | 1.0     | Promotion Kit for Renesas<br>Synergy™ S5D9 MCU Group                                                  | https://www.renesas.com/us/en/<br>products/microcontrollers-<br>microprocessors/renesas-<br>synergy-platform-<br>mcus/yspks5d9e10-pk-s5d9-<br>promotion-kit       |

| TB-S5D5                                                     | 1.2     | Target Board Kit for Renesas<br>Synergy™ S5D5 MCU Group                                               | https://www.renesas.com/us/en/<br>products/microcontrollers-<br>microprocessors/renesas-<br>synergy-platform-<br>mcus/ystbs5d5e10-tb-s5d5-<br>target-board-kit    |

| TB-S5D3                                                     | 1.2     | Target Board Kit for Renesas<br>Synergy™ S5D3 MCU Group                                               | https://www.renesas.com/us/en/<br>products/microcontrollers-<br>microprocessors/renesas-<br>synergy-platform-<br>mcus/ystbs5d3e10-tb-s5d3-<br>target-board-kit    |

| DK-S3A7<br>(Obsolete –<br>do not use<br>for new<br>designs) | 2.0     | Development Kit for Renesas<br>Synergy™ S3A7 MCU Group                                                | https://www.renesas.com/us/en/<br>products/microcontrollers-<br>microprocessors/renesas-<br>synergy-platform-<br>mcus/ysdks3a7e20-dk-s3a7-<br>development-kit     |

| TB-S3A6                                                     | 1.2     | Target Board Kit for Renesas<br>Synergy™ S3A6 MCU Group                                               | https://www.renesas.com/us/en/<br>products/microcontrollers-<br>microprocessors/renesas-<br>synergy-platform-<br>mcus/ystbs3a6e10-tb-s3a6-<br>target-board-kit    |

| Tool               | Version | Description                                                                                                               | Remarks                                                                                                                                                        |

|--------------------|---------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TB-S3A3            | 1.2     | Target Board Kit for Renesas<br>Synergy™ S3A3 MCU Group                                                                   | https://www.renesas.com/us/en/<br>products/microcontrollers-<br>microprocessors/renesas-<br>synergy-platform-<br>mcus/ystbs3a3e10-tb-s3a3-<br>target-board-kit |

| TB-S3A1            | 1.1     | Target Board Kit for Renesas<br>Synergy™ S3A1 MCU Group                                                                   | https://www.renesas.com/us/en/<br>products/microcontrollers-<br>microprocessors/renesas-<br>synergy-platform-<br>mcus/ystbs3a1e10-tb-s3a1-<br>target-board-kit |

| DK-S128            | 2.0     | Development Kit for Renesas<br>Synergy™ S128 MCU Group                                                                    | https://www.renesas.com/us/en/<br>products/microcontrollers-<br>microprocessors/renesas-<br>synergy-platform-<br>mcus/ysdks128e10-dk-s128-<br>development-kit  |

| DK-S124            | 3.1     | Development Kit for Renesas<br>Synergy™ S124 MCU Group                                                                    | https://www.renesas.com/us/en/<br>products/microcontrollers-<br>microprocessors/renesas-<br>synergy-platform-<br>mcus/ysdks124s20-dk-s124-<br>development-kit  |

| TB-S1JA            | 1.3     | Target Board Kit for Renesas<br>Synergy™ S1JA MCU Group                                                                   | https://www.renesas.com/us/en/<br>products/microcontrollers-<br>microprocessors/renesas-<br>synergy-platform-<br>mcus/ystbs1jae10-tb-s1ja-<br>target-board-kit |

| J-Link<br>Software | 7.84d   | SEGGER J-Link <sup>®</sup> debug probe<br>is the quasi standard for Arm <sup>®</sup><br>Cortex <sup>®</sup> -M based MCUs | Jlink 7.84d is integrated as part<br>of e <sup>2</sup> studio 2024-01.1 and SSP<br>v2.6.1 Platform Installer.                                                  |

## 4.1 Version Information for Third-Party Modules

| Component                                 | Version in SSP v2.6.1 | Links for Azure RTOS<br>documents and download links<br>for GUIX Studio and TraceX |

|-------------------------------------------|-----------------------|------------------------------------------------------------------------------------|

| Azure RTOS ThreadX <sup>®</sup>           | 6.4.0                 | https://docs.microsoft.com/en-<br>us/azure/rtos/threadx/                           |

| Azure RTOS NetX™                          | 6.2.1                 | https://docs.microsoft.com/en-<br>us/azure/rtos/netx/                              |

| Azure RTOS NetX Duo™                      | 6.2.1                 | https://docs.microsoft.com/en-<br>us/azure/rtos/netx-duo/                          |

| Azure RTOS NetX Application bundle        | 6.2.1                 | https://docs.microsoft.com/en-<br>us/azure/rtos/netx/                              |

| Azure RTOS NetX Duo<br>Application bundle | 6.2.1                 | https://docs.microsoft.com/en-<br>us/azure/rtos/netx-duo/                          |

| Component                           | Version in SSP v2.6.1                                                         | Links for Azure RTOS<br>documents and download links<br>for GUIX Studio and TraceX                                                                                                                                                             |

|-------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Azure RTOS USBX™                    | 6.2.1                                                                         | https://docs.microsoft.com/en-<br>us/azure/rtos/usbx/                                                                                                                                                                                          |

| Azure RTOS FileX <sup>®</sup>       | 6.2.1                                                                         | https://docs.microsoft.com/en-<br>us/azure/rtos/filex/                                                                                                                                                                                         |

| Azure RTOS GUIX™                    | 6.2.1                                                                         | https://docs.microsoft.com/en-<br>us/azure/rtos/guix/                                                                                                                                                                                          |

| Azure RTOS LevelX                   | 6.2.1                                                                         | https://docs.microsoft.com/en-<br>us/azure/rtos/levelx/                                                                                                                                                                                        |

| Azure RTOS TraceX <sup>1</sup>      | 6.2.1 or later                                                                | https://docs.microsoft.com/en-<br>us/azure/rtos/tracex/<br>Downloadable from Microsoft App<br>Store <sup>1</sup> :<br>https://apps.microsoft.com/store/d<br>etail/azure-rtos-<br>tracex/9NF1LFD5XXG3?hl=en-<br>us≷=US                          |

| Azure RTOS GUIX Studio <sup>1</sup> | 6.2.1 or later                                                                | https://docs.microsoft.com/en-<br>us/azure/rtos/guix/overview-guix<br>Downloadable from Microsoft App<br>Store <sup>1</sup> :<br>https://www.microsoft.com/en-<br>us/p/azure-rtos-guix-<br>studio/9pbm1k1r7q0f?activetab=pi<br>vot:overviewtab |

| TES D/AVE 2D                        | 3.4.0                                                                         | https://www.tes-<br>dst.com/technology-<br>products/gpus/d/ave-2d/                                                                                                                                                                             |

| CMSIS component versions            | CMSIS Base v5.8.0<br>CMSIS Core v5.5.0<br>CMSIS DSP v1.9.0<br>CMSIS NN v3.0.0 | Release CMSIS 5.8.0 ARM-<br>software/CMSIS 5 GitHub                                                                                                                                                                                            |

<sup>&</sup>lt;sup>1</sup> Minimum system requirement is a Windows<sup>®</sup> 10 version to build 14393. Your company's IT policy may limit the installation of software from the Microsoft App Store. In such a case, contact your company's IT department.

## 5. SSP Release Package and Installation Information with e<sup>2</sup> studio

For installation of SSP with e<sup>2</sup> studio, please use the platform installer link provided on the SSP download page (<u>Renesas Synergy™ Software Package (SSP)</u>):

- 1. Click the Platform Installer button.

- 2. Select e<sup>2</sup> studio on the Select a Development Environment pop-up.

- 3. Read and accept the SSP Evaluation License Agreement.

- 4. A \*.zip file will then be downloaded. Once complete, extract and run the \*.exe file.

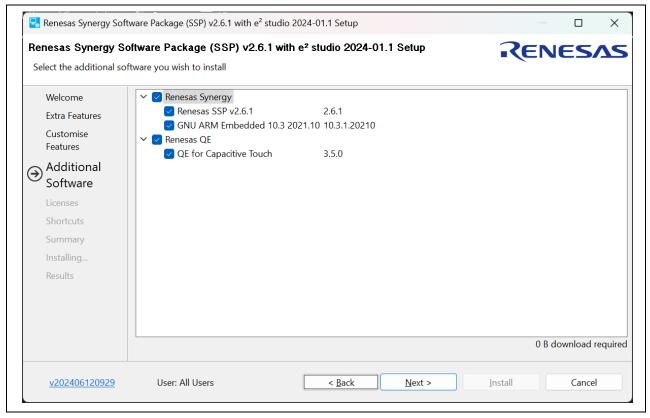

- 5. Choose either the Quick Install or Custom Install options:

- A. Quick Install will install e<sup>2</sup> studio v2024-01.1, SSP v2.6.1, and GCC 10.3-2021.10 and additional components as needed.

- B. Custom Install will allow you to select the options you want to install and during the process, will allow you to deselect the GNU ARM compiler as shown in the screenshot below.

- Note: The only version of the GCC compiler supported by SSP v2.6.1 is GCC 10.3-2021.10. If you must use earlier versions of the GCC compiler, please use with the recommended version of SSP and do not install SSP v2.6.1.

- 6. Accept the Software Agreement terms.

- 7. Accept the Shortcut or create your own as needed.

- 8. Click Install and the installation will be completed.

#### Important Notes:

## 1. The default installation folder for the SSP is C:\Renesas\Synergy.

SSP documentation is available for download from the Renesas Synergy<sup>™</sup> Software Package (SSP) page at <u>Renesas Synergy<sup>™</sup> Software Package (SSP)</u>. Sign in to the MyRenesas account using your existing MyRenesas or Synergy Gallery credentials, or by creating a new MyRenesas account.

- 2. All SSP v2.6.1. software source code is provided without encryption, except FMI and r\_sce modules which are shared as pre-built libraries.

- 3. e<sup>2</sup> studio does not need a License key for generating SSP v2.6.1 Projects.

## 6. SSP Release Package and Installation Information with SSC

**Important:** Only Renesas Synergy<sup>™</sup> users who would like to use the IAR Embedded Workbench for Renesas Synergy<sup>™</sup> as their development environment need to download and install the SSC.

To install SSC v2024-01.1, download the individual SSC v2024-01.1 installer (.zip) from <u>www.renesas.com/synergy/ssc</u>. Unzip it, then double-click the installer and follow the directions on the screen.

To use the SSC and the SSP together with IAR Embedded Workbench for Synergy, follow these steps:

- 1. Download SSC v2024-01.1 from <u>www.renesas.com/synergy/ssc</u>, unzip it, and double-click the executable file. The default installation directory is C:\Renesas\Synergy\sc\_v2024-01.1 ssp v2.6.1.

- 2. IAR Embedded Workbench for Synergy v8.23.3 is available from IAR at <u>www.renesas.com/synergy/iar-embedded-workbench</u>.

- 3. Backup the existing SSP projects before migrating to SSC v2024-01.1.

Note: With SSC platform installer both SSC and SSP 2.6.1 will be installed , user need not install SSP separately

## 7. Issues Fixed in SSP v2.6.1

#### Issue ID: 17608

An attacker can cause arbitrary read and write due to vulnerability in parameter checking mechanism in Azure RTOS ThreadX, which may lead to privilege escalation. The affected components include RTOS ThreadX v6.2.1 and below. The fixes have been included in ThreadX release 6.4.0. Users are advised to use SSP v2.6.1 and above to avoid this vulnerability.

Applies to: All MCUs

## 8. Known Issues and Limitations in SSP v2.6.1

## 8.1 BSP for SSP Supported Platforms

## **Issue ID**: 10664

If a user is using the trace buffer for debugging and has data stored in the RAM at addresses above 0x2000 4000, that data will be overwritten by the trace buffer when debugging.

#### Applies to: S128 and S1JA MCU Groups

**Workaround**: The S128 linker script currently allocates 1K for the trace buffer at 0x2000 0000. This allocation could be removed, freeing up the 1K mistakenly reserved for the trace buffer. Using the e<sup>2</sup> studio trace buffer function will store 1K of the trace buffer data beginning at 0x2000 4000, so that 1K of RAM must not be used by the application if the trace buffer is to be used for debugging.

## 8.2 Creation of Pin Mapper Input xml Files

#### **Issue ID**: 17574

When creating a new project or changing the BSPs of an existing project, pin configurations for some peripherals may show unresolved conflicts. These conflicts do not cause any functional issue; the user can proceed to build the project.

#### Applies to: All MCUs

**Workaround**: Disable the operation mode for the peripheral and enable it again.

## 8.3 Crypto/r\_sce

Issue ID: 15261

At times, some noticeable delay is seen during RSA 2048-bit key generation.

Applies to: S7 and S5 MCU Series

Workaround: None

## 8.4 FileX Development

## Issue ID: 17076

When files are created in a media device using FileX and if they are operated in the Windows platform, the short file name (SFN) associated with the files will get changed. If more files are created using FileX in the same media device, FileX may end up assigning SFN which collides with the SFNs of existing files.

Applies to: S3, S5, and S7 MCU Series

Workaround: None

## 8.5 File System

#### Issue ID: 16181

If the block media is partially exFAT formatted (FileX configuration option "total\_sectors" is less than the total sectors in block media, and the "File system on block media" id changed to "False"), the SD card media opens correctly in the board, file operation on the board also works correctly, but the media open fails in a PC Windows<sup>®</sup> environment.

#### Applies to: All MCUs

**Workaround**: The user has to exFAT format the complete block media to use it in a PC Windows<sup>®</sup> environment.

## 8.6 ISDE User Experience

## **Issue ID**: 7665

When using the Synergy Software Configurator in e<sup>2</sup> studio/SSC, if you rename a thread on the Threads tab and generate code, a new thread\_entry.c file is created with template content, and the old thread\_entry.c file remains in the project. If you have edited the thread\_entry.c file, your changes are not moved to the new file. The old file remains in the project. It will not be called; it causes a build error if not removed from the project manually.

#### Applies to: All MCUs

**Workaround**: Manually move any edits (if made) from the old thread\_entry.c file to the new thread entry.c file, then manually delete the old thread entry.c file from your project.

#### **Issue ID**: 12826

If Synergy Configuration window is maximized in e<sup>2</sup> studio, the property window will not be updated.

#### Applies to: All MCUs

**Workaround**: Do not maximize the Synergy Configuration window before clicking on elements when editing the properties.

#### Issue ID: 12908

A multiple symbol definition error may occur during linkage if an Azure RTOS library component and the corresponding source component such as ux and ux\_src are included. If this occurs, remove the library such as libux.a from the list of libraries used by the linker.

For GCC, this in the **Cross ARM C Linker > Libraries section of the C/C++ Build > Settings** in the project **Properties**.

For IAR, this in the IAR Linker for ARM > Library section of the C/C++ Build > Settings in the project **Properties**.

Module Names: ux (USBX), tx (ThreadX), nx (NetX), nxd (NetX Duo), fx (FileX), gx (GUIX), ux\_host\_class\_XXX (USBX Host Classes), ux\_device\_class\_XXX (USBX Device Classes).

Applies to: All supported MCU Groups

#### **Issue ID**: 13854

When debugging a project with a large number of threads (for example, 150 threads) with the RTOS Resource View open, e<sup>2</sup> studio might hang and become unresponsive.

#### Applies to: All MCUs

**Workaround**: Make the RTOS Resource View small and expand it once the Debug Tree View has finished updating.

## 8.7 NetX and NetX Duo

#### **Issue ID**: 7745

The NetX/NetX Duo FTP Client requires FileX in stack configuration. Due to dependencies, FileX cannot be removed from the configurator while using FTP\_Client application.

Applies to: S7G2, S5D9, and S5D5 MCU Groups

#### Workaround: None

#### **Issue ID**: 14293

Build warnings will be observed on compiling NetX Duo BSD application with GCC v7.x compiler.

Applies to: CM4 MCUs (S7, S5, and S3 MCU Series)

#### Workaround: None

## Issue ID: 16888

New features introduced in SSP released are enabled by default. This may cause existing applications to exceed the maximum available memory space of the selected MCU causing memory overflow errors.

#### Applies to: All MCUs

**Workaround**: Use the configurator to disable any unused options and rebuild the application. For example, in SSP v2.1.0, support for ECC P-224 and P-384 ciphers is added and these are enabled by default. If an application using r\_sce that built successfully prior to SSP v2.1.0 now fails to build with SSP v2.1.0 due to memory overflow, this may be due to the newly added ECC cipher support. This can be fixed by choosing the SCE Common driver on r\_sce in the e<sup>2</sup> studio Threads Configuration view and disabling all cipher types and key lengths that are not used by the application.

## 8.8 r\_agt\_input\_capture

#### **Issue ID**: 15070

While capturing pulse width with AGT input capture, after a measurement completion, the counter and overflow value returned from callback are fine, but the same values read simultaneously with <code>lastCaptureGet API</code> are incorrect.

## Applies to: All MCUs

Workaround: None

## 8.9 r\_rspi

## Issue ID: 16700

The RSPI SPI module uses the DTC as the low level transfer driver. If the DMAC and the DTC are contending for the DMA bus the DMAC always uses a high priority. Thus a DTC based SPI transfer from RSPI module will not get access to the DMA bus since the DMAC is already using it. This will cause the SPI to go into the IDLE mode and trigger a TEND interrupt event. Since at this point the TEND interrupt is disabled, the interrupt remains in the pending state. When the DTC transfer finishes, the CPU will receive the TX interrupt to finish the transfer and then will enable the TEND interrupt. The pending TEND interrupt causes the SPU transfer to be ended early.

## Applies to: All MCUs

**Workaround**: This is a limitation of the RSPI module and the issue can be avoided by not using the DMAC while the DTC is being used by the RSPI module.

## 8.10 r\_sci\_spi

## **Issue ID**: 15574

In an application, if using DTC for data transfer, SCI SPI can experience overrun error if the same application makes heavy use of DMAC and/or another DTC instance. This is because DMAC has a high priority over DTC in arbitration for the mastership of the DMA bus. Also, arbitration between different triggers/transfers in DTC is done based on interrupt/trigger priority. So, if the DMAC or DTC triggered by high priority interrupt/task is accessing the DMA bus and SCI SPI receiving the data at the same time, DTC used by SCI SPI will not be able to access the bus to transfer the received data into the memory, causing SCI SPI to return overrun error.

## Applies to: All MCUs

Workaround: Overrun error can be averted with one of the following options:

1. If SCI SPI uses DTC for data transfer, avoid the use of DMAC or another DTC instance in an application.

2. If DMAC/DTC is a must for other data transfers, avoid the use of DTC with SCI SPI.

3. Use the RSPI instead of SCI SPI. The RSPI hardware can handle overrun conditions.

## 8.11 sf\_ble

## Issue ID: 9225

HID profile client mode is not supported by RL78G1D. As a result, the BLE framework implementation of the HID profile will also not support the HID profile client mode. Applications using a BLE framework for RL78G1D will not be able to use the HID profile in client mode.

## Applies to: All MCUs

## Workaround: None

## Issue ID: 9256

The projects using RL78G1D framework will see compilation warnings. All the warnings are in the RL78G1D driver code and will not have impact on the user applications. The RL78G1D framework files do not have any warnings.

Applies to: RL78G1D on all Synergy MCUs

## Workaround: None

## 8.12 sf\_cellular

sf\_cellular\_ryz014catm1 and sf\_cellular\_ryz014catm1\_socket frameworks are deprecated and will be excluded from future SSP releases.

#### **Issue ID**: 14565

PAP/CHAP authentication fails on the network where authentication is enabled. PAP callback is not working when PAP authentication is enabled in the configurator.

Applies to: S7, S5, S3 MCU Series

Workaround: None

#### **Issue ID**: 14566

Automatic time zone update disable functionality does not work. Even when the user disables automatic time zone update, the current updated time is received.

Applies to: Quectel BG96 modules

Workaround: None

## 8.13 sf\_el\_fx records

Issue ID: 17016

When creating more than 26 files using fx\_file\_unicode\_create() API, the service returns FX\_ALREADY\_CREATED error code from the  $27^{th}$  time.

Applies to: S3, S5, and S7 MCU Series

Workaround: None

## 8.14 sf\_el\_gx

**Issue ID**: 15783

Build warnings are being observed when compiling GUIX Source with GCC 7.2.1.

Applies to: S7G2 and S5D9 MCU Groups

Workaround: None

## 8.15 sf\_el\_nx

**Issue ID** :7513

Current sf\_el\_nx NetX Port driver is hard-coded to use RMMI interface which is for a Micrel Ethernet PHY chip mounted on Renesas kits but does not support the other PHY chips or MMI interface. Customer need to define their own Ethernet PHY chip driver if they use a different PHY chip from the one mounted on Renesas kits, or use a PHY chip with MII interface.

#### Applies to: All MCUs

## Workaround:

Currently there is no plan to provide support for other Ethernet PHY chip drivers in SSP, users should create their custom PHY chip driver using the reference driver provided in SSP. To do that, you can utilize sf\_el\_nx (NetX Port) module under /ssp/src/framework/sf\_el\_nx/ as a template and modify it for your Ethernet PHY chip. Also include an interface file sf\_el\_nx.h located at

/ssp/inc/framework/instances/ in the created new PHY chip driver. Source files under sf\_el\_nx are plain text so you can copy the file to other directories, such as /src/ directory and exclude original sf\_el\_nx module from building to avoid 'multiple definition' compile-error.

Here is the brief guideline to work around the issue:

• Copy the directory /ssp/src/framework/sf\_el\_nx/ including all the files under the directory to /src/.

- Exclude original SF\_EL\_NX module in SSP from your build. Right click on the directory /ssp/src/framework/sf\_el\_nx/ and select 'Exclude from build...'. Then click 'Select All' button.

- Modify /src/sf\_el\_nx/nx\_hw\_init.c.nx\_synergy\_ethernet\_init() needs modification below to select MII interface. Change IOPORT\_ETHERNET\_MODE\_RMII to IOPORT\_ETHERNET\_MODE\_MII.g\_ioport\_on\_ioport.pinEthernetModeCfg(IOPORT\_ETHERNET\_CHA NNEL n, IOPORT\_ETHERNET\_MODE\_RMII);

- Modify /src/sf\_el\_nx/phy/ether\_phy.c and ether\_phy.h. These files need modification to match to your Ethernet PHY chip.

- Make sure selecting MII pins under Pins tab in Synergy Configurator. Check pin configuration setting; Peripherals > Connectivity:ETHERC.

Notes:

- Source files under /ssp/src/framework/sf\_el\_nx/ will be overwritten by tool when building a project so you should copy the files before Source files under /ssp/src/framework/sf\_el\_nx/ will be overwritten by tool when building a project so you should copy the files before your editing.

- To exclude files from building, right-click on the files and select 'Exclude from build..' (this is the case for e<sup>2</sup> studio).

Module Name: SF\_EL\_NX (NetX Port)

## 8.16 sf\_el\_tx

Issue ID: 13678

SF\_CONTEXT\_SAVE and SF\_CONTEXT\_RESTORE (in <code>bsp\_common.h</code>) should only be defined if TX\_ENABLE\_EXECUTION\_CHANGE\_NOTIFY or TX\_ENABLE\_EVENT\_TRACE is defined.

Applies to: All MCUs

Workaround: None

## 8.17 sf\_el\_ux

**Issue ID**: 8574

The current sf\_el\_ux HCD driver does not enable the double buffer feature for bulk out PIPEs, which is supported by USB hardware. Because of that, USB data throughput for data write through a bulk out PIPE will be less than the value for double buffer-enabled. This issue is only for data write (bulk OUT). Double buffering is supported for data read (bulk IN).

Applies to: S7, S5, and S3 MCU Series

Workaround: None

**Issue ID**: 13481

The USB host sends out a PING packet after receiving NAK or NYET handshake from the device. However, it also sends out a PING packet for ACK handshake, which is not expected behavior according to the USB 2.0 specification.

Applies to: All MCUs supporting USBX Host

#### Workaround: None

Issue ID: 16572

In sf\_el\_ux device class driver, there is a redundant semaphore for 'device transfer request' that needs to be removed. Common semaphore can be used for the device transfer request for both S1 MCU Series and S3, S5, S7 MCU Series instead of using two semaphores - one for S1 MCU series and another for S3, S5 and S7 MCU Series separately.

Applies to: All MCUs

Workaround: None

## 8.18 sf\_Wifi

## Issue ID: 8394

The projects using GT202 framework will see compilation warnings. All the warnings are in the 3<sup>rd</sup> party GT202 driver code. The GT202 framework files do not have any warnings. The warnings should not impact the user applications.

Applies to: WiFi Framework for GT202 on S7G2, S3A7, S5D9, S5D5, S3A6 (only socket), S3A3 MCU Groups

## Workaround: None

Issue ID: 12742

GT202 module supported by WiFi Framework is affected by WPA2 KRACK issue.

**Applies to**: GT202 module supported by WiFi Framework

#### Workaround: None

Issue ID: 14126

WiFi WPS functionality does not work with WPA security.

Applies to: WiFi Framework using GT202

Workaround: None

## 8.19 sf\_wifi\_qca4010

Issue ID: 16558

SF\_WIFI\_QCA4010 framework does not support WPS method of provisioning.

Applies to: S3, S5, S7 MCU Series

Workaround: None

## 8.20 SSP IAR Support

Issue ID: 13900

In some cases, the build fails with the error "Secure builder required" after migrating to a newer SSP version in EWSYN.

#### Applies to: All MCUs

**Workaround**: Select **Project** > **Make** (F7) after the issue occurs. The project should then build without errors.

#### **Issue ID**: 14485

Library projects which use many/long include paths cause the compiler command line to exceed system limit and fails to build the library.

**Applies to:** Projects created with IAR compiler in e<sup>2</sup> studio.

#### Workaround: None

Issue ID: 16723

If using the IAR compiler from IAR EWSYN product, but invoked from e<sup>2</sup> studio IDE, installing the IAR Embedded Workbench plugins into e<sup>2</sup> studio may result in the following message:

"Warning: Installing unsigned software for which the authenticity or validity cannot be established. Continue with installation?"

#### Applies to: All MCUs

**Workaround**: This warning can be ignored – click on the "Install anyway" option to continue with the installation.

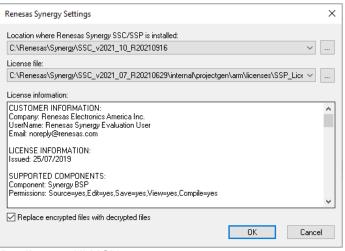

#### Issue ID: 16988

Synergy License file information is no longer required for SSP v2.x. The Renesas Synergy™ settings dialog in IAR Embedded Workbench for Synergy shows the License information section to support any imported SSP v1.x projects.

SSP Evaluation License is located in the following directory: <SSC base dir>\internal\projectgen\arm\Licenses\.

## Applies to: All MCUs

## Workaround: None

## 8.21 SSP XMLs for ISDEs

#### Issue ID: 10695

Configurator does not warn about the limitation on RSPI bit rate if it is less than or equal to 30 MHz.

#### Applies to: All MCUs

**Workaround**: RSPI bit rate must be a positive integer less than or equal to 30 MHz or PCLK/2, whichever is minimum.

#### Issue ID: 12857

Creating a project with a custom board pack might not reflect the customized values set for the properties in that custom board pack.

#### Applies to: All MCUs

Workaround: None

## 8.22 TES

Issue ID: 14095

The rendering of concave polygons is not supported when D/AVE 2D drawing engine is enabled.

Applies to: S7G2 and S5D9 MCU Groups

Workaround: Disable D/AVE 2D drawing engine to render concave polygons.

#### **Issue ID**: 15762

An application using pixelmaps to fill the shapes does not render pixelmaps properly inside the shapes if the pixelmaps width and height are not the power of 2.

Applies to: S7G2 and S5D9 MCU Groups

**Workaround**: The pixelmaps are properly drawn inside the shapes if pixelmap width and height are the power of 2.

## 8.23 USBX

## Issue ID: 8647

The USB throughput for file read/write operation with USBX Device Class Mass Storage is not consistent and may vary for every measurement.

#### Applies to: All MCUs

## Workaround: None

## Issue ID: 17096

The sf\_el\_ux\_comms\_v2 Write API sends a ZLP packet after it sends the requested bytes, for all requested lengths, instead of sending ZLP only when the requested length is a Multiple of wMaxPacketSize. There is no functionality impact because of this, but this is an undesired behavior.

## Applies to: All MCUs

Workaround: None

## 8.24 Known Issues in Synergy Development Tools

## 8.24.1 Pin Mapping Issues

Issue ID: 12261

DAC8 output pin is not configured when it is configured through ISDE as the pin configuration does not support setting ASEL and PSEL bit fields for the same pin.

Applies to: S1JA, S128, and S3A3 MCU Groups

Workaround: Configure DAC8 output pin manually.

Update g\_ioport\_on\_ioport.pinCfg setting on the pin configured for DAC by adding the following:

| IOPORT\_CFG\_PERIPHERAL\_PIN | IOPORT\_PERIPHERAL\_CAC\_AD

## **Issue ID**: 14088

When setting the IRQ on the GPIO pin, there is no conflict shown if the IRQ is already assigned to another pin.

## Applies to: All MCUs

**Workaround**: Manually check the ICU peripheral to see if the IRQ is already assigned to a pin before setting it to a GPIO pin.

#### Issue ID: 16561

The VREFH pin for the S1JA device cannot be configured but the VREFL pin is configurable without errors through the pin configurator. When generating the project content, pin\_data.c file does not have the data for the pin configured. The user needs to manually add the data.

#### Applies to: S1JA MCU Group, and S3 MCU Series

**Workaround**: The user will have to manually configure the VREF pins for S1JA MCUs through the IO port API in their application, for example, g\_ioport.p\_api -> pincfg(OPPORT\_PORT\_00\_PIN\_10, IOPORT\_CFG\_ANALOG\_ENABLE);

## Issue ID: 16592

Migrating a SSP v1.x project that has the comparator functions configured, to SSP v2.x does not work properly.

One of the following issues will be noticed:

- 1. Pin editor does not open and complains about the invalid pinmapping.xml file.

- 2. Shows messages about conflicts found.

- 3. Migrates with error in pin configuration.

#### Applies to: All MCUs

Workarounds (corresponding to items 1,2, and 3 in the issue description above, respectively):

- Option 1: Manually recreate the configuration in SSP v2.x.

Option 2: Remove the configuration for CMP function and then migrate to SSP v2.x.

- Click Continue and OK on the messages shown below to continue to migrate the project. The project migrates with an error. Manually fix the error in the ACMP function (for example, by selecting the pin for VCOUT on ACMP0).

- 3. Manually fix the error in the ACMP function (for example, setting the operation mode).

| 🕲 Vers | ion has changed                                                                                                                                                                                          |                                                                                         |                                                        | -      |                                | ×  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------|--------|--------------------------------|----|

| ?      | The version of the pin mapping<br>from version 2.04 to version 2.0<br>Due to these incompatibilities<br>R7FS7G27G2A01CBD.pincfg in<br>Press Continue to start an imp<br>Press Cancel to quit, the pincfg | 05 and these versio<br>it is not possible to<br>the pin editor.<br>ort operation, in or | ns appear to be<br>open the file:<br>der to resolve tl | incor  | npatible.                      |    |

|        |                                                                                                                                                                                                          |                                                                                         | Cancel                                                 |        | Continu                        | JE |

| 📴 Con  | flicts found                                                                                                                                                                                             |                                                                                         |                                                        | _      |                                | ×  |

|        | Conflicts were found while up<br>Select one of the following opt<br>Press Cancel to cancel updatin<br>Press OK to continue updating<br>imported.                                                         | tions:<br>g to the new version                                                          | n.                                                     | ings w | vill not be<br><< <u>D</u> eta |    |

|        | xt settings have conflicts:<br>wn configuration id found: acmj                                                                                                                                           | p.vcout                                                                                 |                                                        |        |                                |    |

|        |                                                                                                                                                                                                          |                                                                                         |                                                        |        |                                |    |

4. Manually fix the error in the ACMP function (for example, by setting the operation mode).

## 8.24.2 Synergy Tools

## Issue ID: 11556

Synergy builder is excluded from the tool command pattern when changing the toolchain from IAR 7.x to IAR 8.x, which leads to a build error that the secure builder is required when trying to build the project after migrating.

## Applies to: All MCUs

## Workaround:

The following workaround can be used to migrate projects with IAR 7.x to IAR 8.x:

- 1. Add environment variable SECURE\_BUILD\_COMMAND: \${renesas.support.targetLoc:synergybuild} /isdebuild

- 2. Update command line pattern IAR C/C++ Compiler for ARM setting if the following command is missing: \${SECURE\_BUILD\_COMMAND}

- 3. Update command line pattern IAR C/C++ Assembler for ARM if the following command is missing: \${SECURE\_BUILD\_COMMAND}

## **Issue ID**: 12584

An error occurs when setting the watchpoint at certain addresses. Debug sessions cannot be started when these watchpoints with errors are still present.

## Applies to: S5D9 MCU Group

Workaround: Remove the watchpoints from the breakpoints view and start the debug session.

## **Issue ID**: 12925

When exporting the project, selecting the option for .tar format does not export the project in tar format, but exports it in zip format.

## Applies to: Tools

**Workaround**: Edit the archive file name field by replacing the .zip with .tar, and the project will be exported in .tar format.

## Issue ID: 14436

Some of the old projects with customized stacks might fail after migrating to  $e^2$  studio v7.3 or later versions because the default modules get repopulated in the stack.

## Applies to: All MCUs

Workaround: The user explicitly needs to delete the modules that are repopulated after migration.

#### Issue ID: 15339

Default property value of the IP address does not get picked up for existing projects after changes to the pack. Opening existing projects shows the previously saved value instead of the default value from the pack.

Applies to: Projects which use the packs with the change for IP address

#### Workaround: None

Issue ID: 17055

Developer Assistance for API reference for r\_ctsuv2 module is not available.

Applies to: All MCUs

Workaround: None

## Issue ID: 17237

SSC does not provide a Save button to save changes to the Synergy project configuration.

## Applies to: All MCUs

**Workaround**: Click **Ctrl-S** to save the Synergy Configuration or close the SSC and click **Yes** in the Save Resource dialog to save your changes.

## 9. Complete List of Modules Supported in this Release

These modules are available on the respective MCUs based on the following criteria:

- If the core functionality of the module has been tested and works on an MCU, even if it has known issues, then the module is supported on the MCU.

- If the core functionality is broken or not tested on an MCU, then that module is not supported on the MCU.

- If a module is independent of the underlying MCU hardware or HAL drivers, and has been tested on a particular Synergy MCU, the following table indicates that this module is supported on all the Synergy MCUs that the underlying driver/framework/stack depend on have been tested.

| Module Name         | SSP Feature                                     | Supported Synergy MCU Groups                                        |

|---------------------|-------------------------------------------------|---------------------------------------------------------------------|

| BSP                 | Board Support Package                           | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_acmphs            | Analog Comparator High Speed                    | S1JA, S3A7, S5D9, S5D5, S5D3, S7G2                                  |

| r_acmplp            | Analog Comparator Low Power                     | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7                            |

| r_adc               | A/D Converter                                   | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_agt               | Asynchronous General Purpose<br>Timer           | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_agt_input_capture | AGT Input Capture                               | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_analog_connect    | Analog Connect                                  | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_cac               | Clock Frequency Accuracy<br>Measurement Circuit | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_can               | Controller Area Network                         | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_cgc               | Clock Generation Circuit                        | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_crc               | Cyclic Redundancy Check<br>Calculator           | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_ctsuv2            | Capacitive Touch Sensing Unit<br>Version 2      | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_dac               | Digital to Analog Converter                     | S124, S3A1, S3A3, S3A6, S3A7, S5D3, S5D5, S5D9, S7G2                |

| r_dac8              | 8-bit Digital to Analog Converter               | S128, S1JA, S3A1, S3A3, S3A6                                        |

| r_dmac              | Direct Memory Access Controller                 | S3A1, S3A3, S3A6, S3A7, S5D3, S5D5, S5D9,<br>S7G2                   |

| r_doc               | Data Operation Circuit                          | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_dtc               | Data Transfer Controller                        | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_elc               | Event Link Controller                           | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_flash_hp          | Flash Memory, High<br>Performance               | S5D3, S5D5, S5D9, S7G2                                              |

| r_flash_lp          | Flash Memory, Low Power                         | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7                            |

| r_fmi               | Factory Microcontroller<br>Information          | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_glcd              | Graphics LCD Controller                         | S5D9, S7G2                                                          |

## 9.1 BSP and Driver Modules Available in this Release

| Module Name         | SSP Feature                      | Supported Synergy MCU Groups                                        |

|---------------------|----------------------------------|---------------------------------------------------------------------|

| r_gpt               | General Purpose Timer            | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,                           |

|                     |                                  | S5D3, S5D5, S5D9, S7G2                                              |

| r_gpt_input_capture | General Input Capture            | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,                           |

|                     |                                  | S5D3, S5D5, S5D9, S7G2                                              |

| r_icu               | Interrupt Controller Unit        | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,                           |

|                     |                                  | S5D3, S5D5, S5D9, S7G2                                              |

| r_ioport            | General Purpose I/O Ports        | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,                           |

|                     |                                  | S5D3, S5D5, S5D9, S7G2                                              |

| r_iwdt              | Independent Watchdog Timer       | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_jpeg_common       | JPEG Common                      | S5D9, S7G2                                                          |

| r_jpeg_decode       | JPEG Decode                      | S5D9, S7G2                                                          |

| r_jpeg_encode       | JPEG Encode                      | S5D9, S7G2                                                          |

| r_kint              | Keyboard Interrupt Interface     | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,                           |

|                     |                                  | S5D3, S5D5, S5D9, S7G2                                              |

| r_lpmv2_s1ja        | Low Power Mode V2 for S1JA       | S1JA                                                                |

| r_lpmv2_s124        | Low Power Mode V2 for S124       | S124                                                                |

| r_lpmv2_s128        | Low Power Mode V2 for S128       | S128                                                                |

| r_lpmv2_s3a1        | Low Power Mode V2 for S3A1       | S3A1                                                                |

| r_lpmv2_s3a3        | Low Power Mode V2 for S3A3       | S3A3                                                                |

| r_lpmv2_s3a6        | Low Power Mode V2 for S3A6       | S3A6                                                                |

| r_lpmv2_s3a7        | Low Power Mode V2 for S3A7       | S3A7                                                                |

| r_lpmv2_s5d3        | Low Power Mode V2 for S5D3       | S5D3                                                                |

| r_lpmv2_s5d5        | Low Power Mode V2 for S5D5       | S5D5                                                                |

| r_lpmv2_s5d9        | Low Power Mode V2 for S5D9       | S5D9                                                                |

| r_lpmv2_s7g2        | Low Power Mode V2 for S7G2       | \$7G2                                                               |

| r_lvd               | Low Voltage Detection Driver     | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,                           |

| r onomn             | Operational Amplifier            | S5D3, S5D5, S5D9, S7G2                                              |

| r_opamp<br>r_pdc    | Parallel Data Capture Unit       | S128, S1JA, S3A1, S3A3, S3A6, S3A7<br>S5D5, S7G2                    |

| r_ptp               | Precision Time Protocol          | S5D9, S7G2                                                          |

| r_qspi              | Quad Serial Peripheral Interface | S3A1, S3A3, S3A7, S5D3, S5D5, S5D9, S7G2                            |

| r_riic              | IIC                              | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,                           |

| 1_110               |                                  | S5D3, S5D5, S5D9, S7G2                                              |

| r_riic_slave        | IIC Slave                        | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,                           |

|                     |                                  | S5D3, S5D5, S5D9, S7G2                                              |

| r_rspi              | Serial Peripheral Interface      | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,                           |

|                     |                                  | S5D3, S5D5, S5D9, S7G2                                              |

| r_rtc               | Real-time Clock                  | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,                           |

|                     | Conial Communication Interface   | S5D3, S5D5, S5D9, S7G2                                              |

| r_sci_i2c           | Serial Communication Interface   | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_sci_spi           | Serial Communication Interface   | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,                           |

| <u></u>             | SPI                              | S5D3, S5D5, S5D9, S7G2                                              |

| r_sci_uart          | Serial Communication Interface   | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,                           |

|                     | UART                             | S5D3, S5D5, S5D9, S7G2                                              |

| r_sdadc             | Sigma Delta ADC                  | S1JA                                                                |

| r_sdmmc             | SDHI Driver for SDIO and         | S3A1, S3A3, S3A7, S5D3, S5D5, S5D9, S7G2                            |

|                     | SD/MMC Memory Devices            |                                                                     |

| r_slcdc             | Segment LCD Controller           | S3A1, S3A3, S3A6, S3A7                                              |

| Module Name        | SSP Feature                                                          | Supported Synergy MCU Groups                                        |

|--------------------|----------------------------------------------------------------------|---------------------------------------------------------------------|

| r_ssi              | (Inter-IC Sound) Interface [old:<br>Serial Sound Interface] or r_i2s | S3A1, S3A3, S3A6, S3A7, S5D3, S5D5, S5D9, S7G2                      |

| r_wdt              | Watchdog Timer                                                       | S124, S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2 |

| r_sce <sup>1</sup> | Cryptographic Library (HAL interfaces)                               | See table note on Cryptographic Functions                           |

<sup>1</sup>Cryptographic Functions: Section 9.4 lists cryptographic functions available for each MCU in this release; these functions are accessible as part of r\_sce/cryptographic library.

## 9.2 Framework Modules Supported in this Release

| Module Name                    | SSP Feature                                      | Supported Synergy MCU Groups                                        |

|--------------------------------|--------------------------------------------------|---------------------------------------------------------------------|

| sf_adc_periodic                | Periodic Sampling ADC                            | S124, S128, S3A3, S3A6, S3A7, S5D3,<br>S5D5, S5D9, S7G2             |

| sf_audio_playback              | Audio Playback                                   | S124, S128, S1JA, S3A1, S3A3, S3A6,<br>S3A7, S5D3, S5D5, S5D9, S7G2 |

| sf_audio_playback_hw_dac       | Audio Playback HW DAC                            | S124, S128, S1JA, S3A1, S3A3, S3A6,<br>S3A7, S5D3, S5D5, S5D9, S7G2 |

| sf_audio_playback_hw_i2s       | Audio Playback HW I2S                            | S3A1, S3A3, S3A6, S3A7, S5D3, S5D5,<br>S5D9, S7G2                   |

| sf_audio_record_adc            | Audio Record ADC                                 | S124, S128, S3A3, S3A6, S3A7, S5D3,<br>S5D5, S5D9, S7G2             |

| sf_audio_record_i2s            | Audio Record I2S                                 | S3A1, S3A3, S3A6, S3A7, S5D3, S5D5,<br>S5D9, S7G2                   |

| sf_ble_rl78g1d                 | BLE Framework                                    | S124, S128, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2       |

| sf_ble_rl78g1d_onboard_profile | BLE Framework Onboard<br>Profiles                | S124, S128, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2       |

| sf_block_media_lx_nor          | Block Media Interface for<br>LevelX NOR          | S3A1, S3A3, S3A7, S5D3, S5D5, S5D9,<br>S7G2                         |

| sf_block_media_qspi            | Block Media Interface for QSPI                   | S3A1, S3A3, S3A7, S5D3, S5D5, S5D9,<br>S7G2                         |

| sf_block_media_ram             | Block Media Interface for RAM                    | S128, S1JA, S3A1, S3A3, S3A6, S3A7,<br>S5D3, S5D5, S5D9, S7G2       |

| sf_block_media_sdmmc           | Block Media Interface for<br>SD Multi Media Card | S3A1, S3A3, S3A7, S5D3, S5D5, S5D9,<br>S7G2                         |

| sf_comms_telnet                | Telnet Communications                            | S5D3, S5D5, S5D9, S7G2                                              |

| sf_console                     | Console                                          | S124, S128, S1JA, S3A1, S3A3, S3A6,<br>S3A7, S5D3, S5D5, S5D9, S7G2 |

| sf_el_fx                       | Synergy FileX interface                          | S3A1, S3A3, S3A6, S3A7, S5D3, S5D5,<br>S5D9, S7G2                   |

| sf_el_gx                       | Synergy GUIX Interface                           | S5D9, S7G2                                                          |

| sf_el_lx_nor                   | Synergy LevelX NOR<br>Interface                  | S3A1, S3A3, S3A7, S5D3, S5D5, S5D9,<br>S7G2                         |

| sf_el_nx                       | Synergy NetX Interface                           | S5D5, S5D9, S7G2                                                    |

| sf_el_ux                       | Synergy USBX Interface                           | S124, S128, S1JA, S3A1, S3A3, S3A6,<br>S3A7, S5D3, S5D5, S5D9, S7G2 |

| sf_el_ux_comms_v2              | Synergy USBX<br>Communication Interface<br>V2    | S124, S128, S1JA, S3A1, S3A3, S3A6,<br>S3A7, S5D3, S5D5, S5D9, S7G2 |

| sf_external_irq                | External Interrupt                               | S124, S128, S1JA, S3A1, S3A3, S3A6,<br>S3A7, S5D3, S5D5, S5D9, S7G2 |

| SSP Feature                                        | Supported Synergy MCU Groups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I2C Framework                                      | S124, S128, S1JA, S3A1, S3A3, S3A6,<br>S3A7, S5D3, S5D5, S5D9, S7G2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| JPEG Decode                                        | S5D9, S7G2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Memory QSPI NOR                                    | S3A1, S3A3, S3A7, S5D3, S5D5, S5D9,<br>S7G2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |