Overview

Description

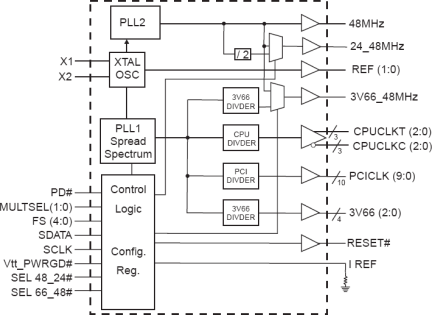

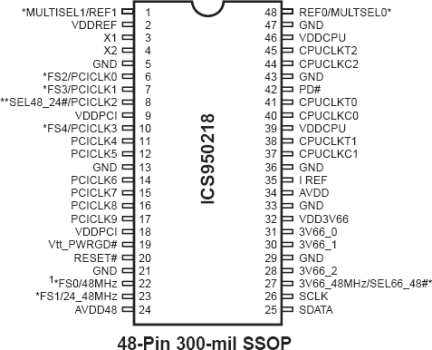

The 950218 is a single chip clock solution for desktop designs using the Intel Brookdale chipset with PC133 or DDR memory. It provides all necessary clock signals for such a system. The 950218 is part of a whole new line of ICS clock generators and buffers called TCH™ (Timing Control Hub). ICS is the first to introduce a whole product line which offers full programmability and flexibility on a single clock device. This part incorporates ICS's newest clock technology which offers more robust features and functionality. Employing the use of a serially programmable I2C interface, this device can adjust the output clocks by configuring the frequency setting, the output divider ratios, selecting the ideal spread percentage, the output skew, the output strength, and enabling/disabling each individual output clock. TCH also incorporates ICS's Watchdog Timer technology and a reset feature to provide a safe setting under unstable system conditions. M/N control can configure output frequency with resolution up to 0.1MHz increment. With all these programmable features ICS's, TCH makes mother board testing, tuning and improvement very simple.

Features

- 3 - Pairs of differential CPU clocks (differential current mode)

- 3 - 3V66 @ 3.3V

- 10 - PCI @ 3.3V

- 1 - 48MHz @ 3.3V fixed

- 2 - REF @ 3.3V, 14.318MHz

- 1 - 48_66MHz selectable @ 3.3V fixed

- 1 - 24_48MHz selectable @ 3.3V

- Programmable output frequency.

- Programmable output divider ratios.

- Programmable output rise/fall time.

- Programmable output skew.

- Programmable spread percentage for EMI control.

- Watchdog timer technology to reset system if system malfunctions.

- Programmable watch dog safe frequency.

- Support I2C Index read/write and block read/write operations.

- Uses external 14.318MHz crystal.

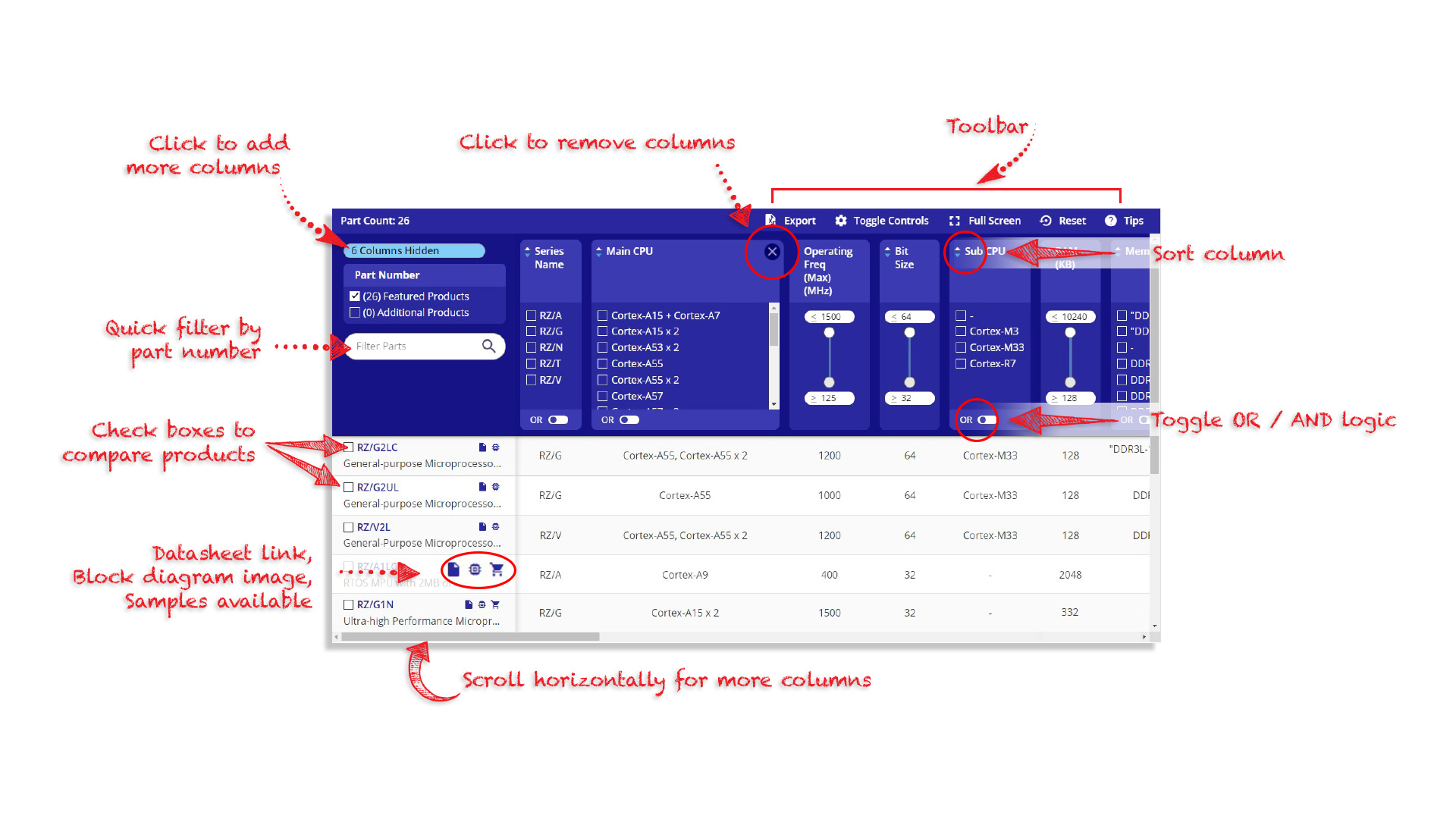

Comparison

Applications

Documentation

= Featured Documentation

Log in required to subscribe

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Datasheet | PDF 224 KB | |

| End Of Life Notice | PDF 125 KB | |

| Product Change Notice | PDF 361 KB | |

| End Of Life Notice | PDF 125 KB | |

| End Of Life Notice | PDF 122 KB | |

5 items

|

||

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.