概要

説明

The 5V9351 is a high performance, zero delay, low skew, phase-lock loop (PLL) clock driver. It has four banks of configurable outputs. The 5V9351 uses a differential PECL reference input and an external feedback input. These features allow the 5V9351 to be used as a zero delay, low skew fan-out buffer. REF_SEL allows selection between PECL input or TCLK, a CMOS clock driver input. If PLL_EN is set to low and REF_SEL to high, it will bypass the PLL. By doing so, the 5V9351 will be in clock buffer mode. Any clock applied to TCLK will be divided down to four output banks. When PLL_EN is set high, PLL is enabled. Any clock applied to TCLK will be clocked in both phase and frequency to FBIN. PECL clock is activated by setting REF_SEL to low.

特長

- Fully integrated PLL

- Output frequency up to 200MHz

- 2.5V and 3.3V Compatible

- Compatible with PowerPC™, Intel, and high performance RISC

- microprocessors

- Output frequency configurable

- Cycle-to-cycle jitter max. 22ps RMS

- Compatible with MPC9351

製品比較

アプリケーション

設計・開発

モデル

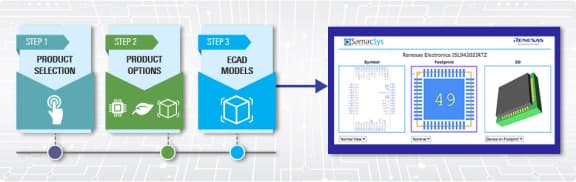

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。