概要

説明

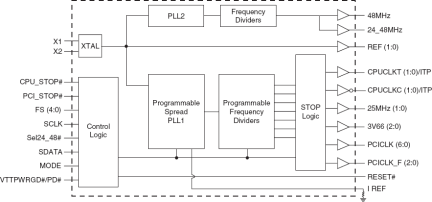

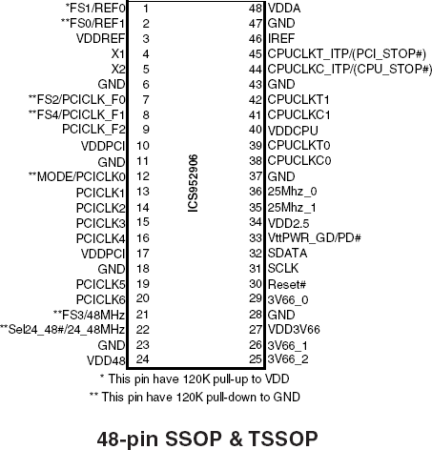

Programmable Timing Control Hub™ for Next Gen P4™ processor

特長

- 3 - 0.7V current-mode differential CPU pairs

- 10 - PCI, 3 free running, 33MHz

- 2 - REF, 14.318MHz

- 3 - 3V66, 66.66MHz

- 1 - 48MHz

- 1 - 24/48MHz

- 2 - 25MHz @ 2.5V

- CPU/SRC outputs cycle-cycle jitter < 125ps

- 3V66 outputs cycle-cycle jitter < 250ps

- PCI outputs cycle-cycle jitter < 250ps

- CPU - AGP skew < +/- 350ps

- AGP-PCI skew between 1~3.5ns

- Programmable output frequency.

- Programmable asynchronous 3V66&PCI frequency.

- Programmable output divider ratios.

- Programmable output skew.

- Programmable spread percentage for EMI control.

- Watchdog timer technology to reset system if system malfunctions.

- Programmable watch dog safe frequency.

- Support I2C Index read/write and block read/write operations.

- Uses external 14.318MHz reference input.

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。