概要

説明

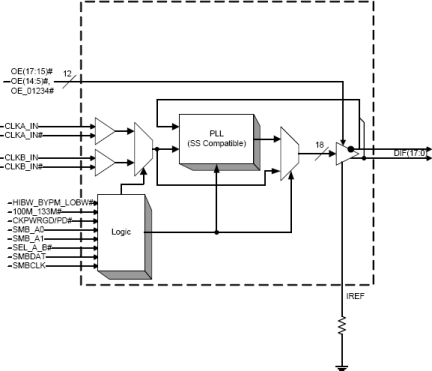

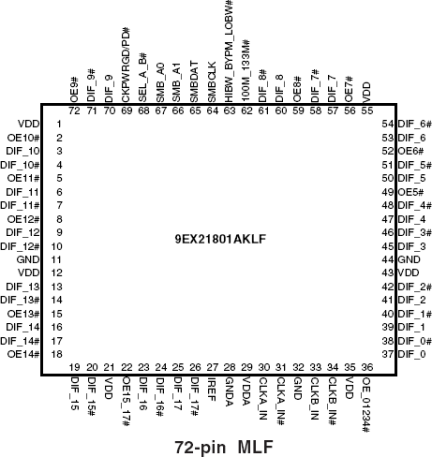

The 9EX21801 provides 18 output clocks for PCIe Gen2 (100MHz) or QPI (133MHz) applications. The 9EX21801 has 4 selectable SMBus addresses, and dedicated CKPWRGD/PD# and VDDA pins for easy board design. A differential CPU clock from a CK410B+ main clock generator, such as the 932S421, drives the 9EX21801. In fanout mode, the 9EX21801 provides outputs up to 400MHz.

特長

- DIF output cycle-to-cycle jitter < 50ps

- DIF output-to-output skew < 150 ps

- PCIe Gen2 compliant phase noise

- QPI 133MHz compliant phase noise

- Supports output clock frequencies up to 400 MHz

- 4 Selectable SMBus addresses

- SMBus address is independent of PLL operating mode

- Dedicated CKPWRGD/PD# and VDDA pins ease board design

- Available in industrial temperature range (-40°C to +85°C)

製品比較

アプリケーション

設計・開発

モデル

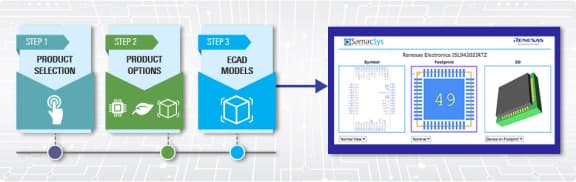

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

ビデオ&トレーニング

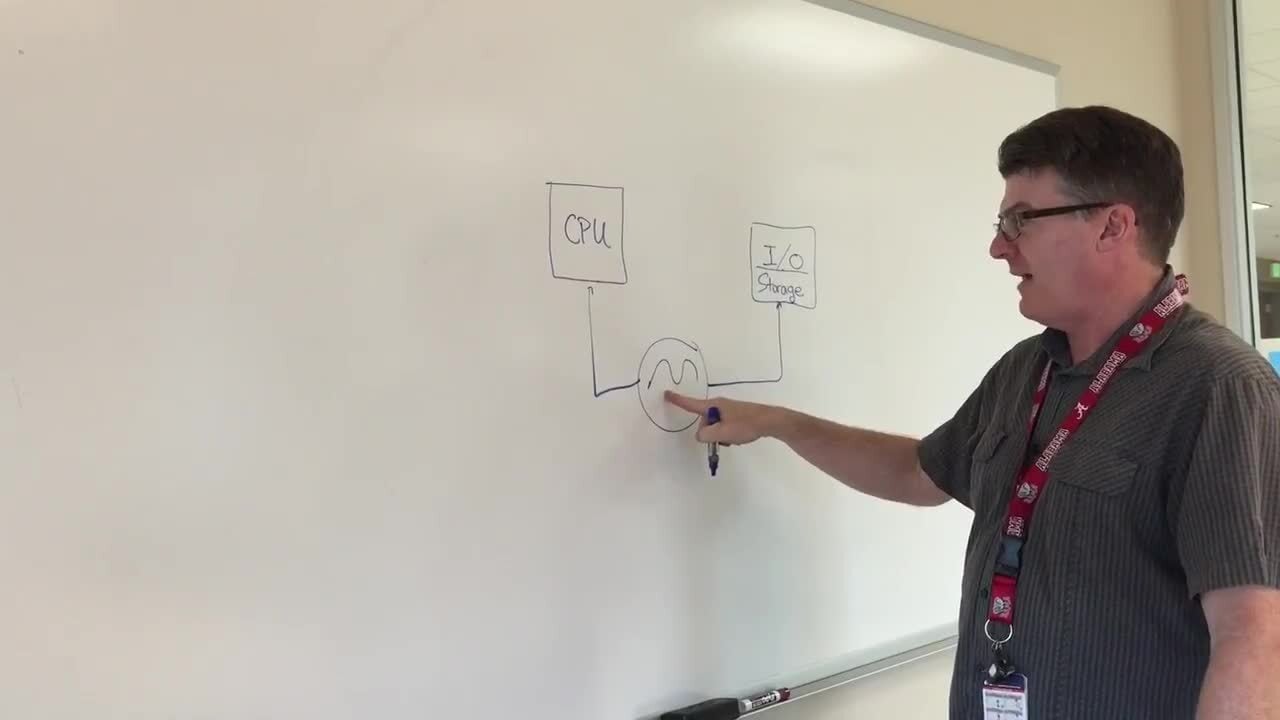

This is the first video in our PCIe series. In this video, we define PCIe architectures, focusing on common and separate clock architectures. Watch the rest of the video series below where Ron will cover the impact of different timing architectures.

Watch the Video Series Below