Overview

Description

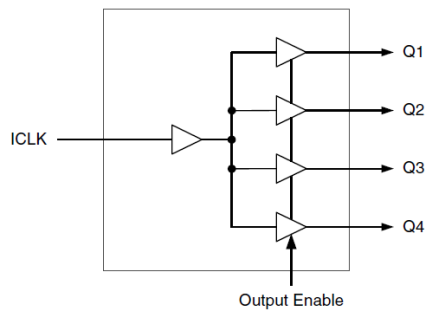

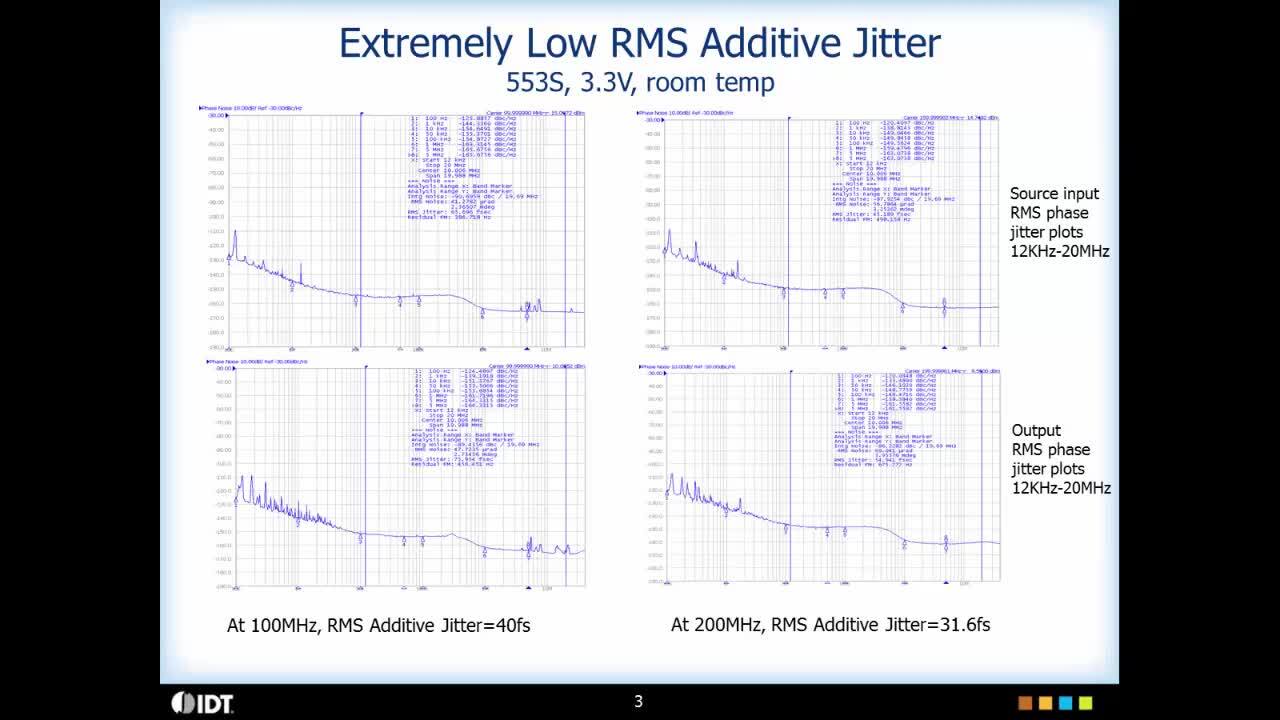

The 651S is a low cost, high-speed single input to four output LVCMOS clock buffer. The 651S has best in class Additive Phase Jitter of sub 50 fsec.

Features

- Low additive phase jitter RMS: 50 fs

- Extremely low skew outputs (50 ps)

- Low cost clock buffer

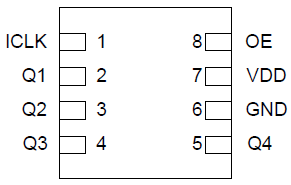

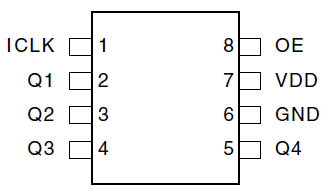

- Packaged in 8-pin SOIC and 8-pin DFN, Pb-free

- Input / Output clock frequency up to 200 MHz

- Non-inverting output clock

- Ideal for networking clocks

- Operating Voltages: 1.8 V to 3.3 V

- Output Enable mode tri-states outputs

- Advanced, low power CMOS process

- Extended temperature range (-40°C to +105°C)

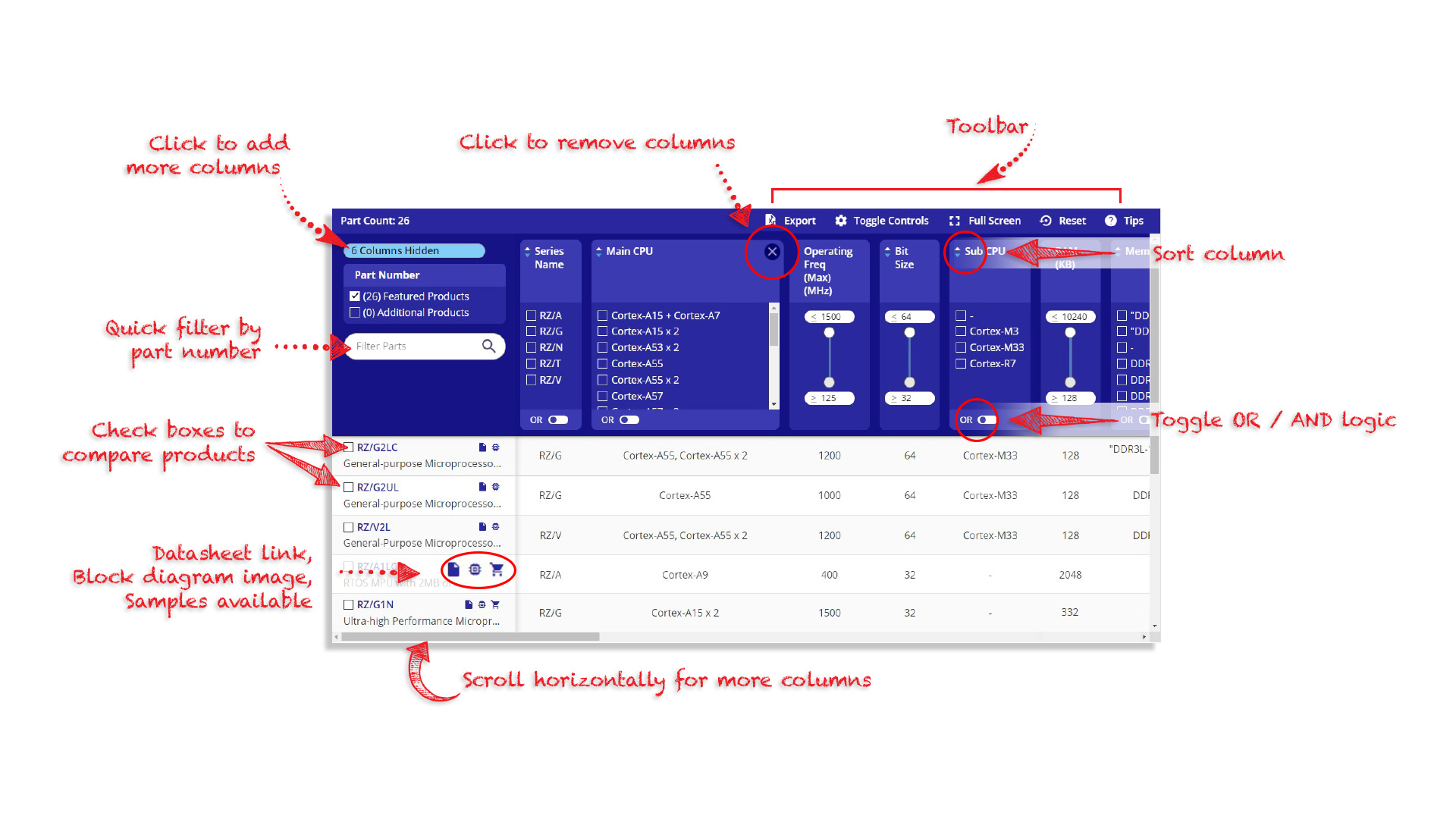

Comparison

Applications

Documentation

= Featured Documentation

Log in required to subscribe

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Datasheet | PDF 305 KB | |

| Application Note | PDF 187 KB | |

| Overview | PDF 217 KB | |

| Product Change Notice | PDF 268 KB | |

| Product Change Notice | PDF 611 KB | |

| Product Change Notice | PDF 611 KB | |

| Application Note | PDF 495 KB | |

| Application Note | PDF 442 KB | |

| Application Note | PDF 565 KB | |

9 items

|

||

Design & Development

Models

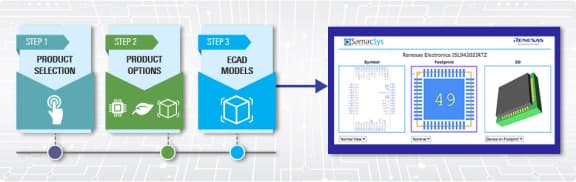

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Videos & Training

Low-jitter LVCMOS Fanout Clock Buffers by IDT

This video overviews the LVCMOS Fanout Buffers, showcasing their best-in-class performance with extremely low phase jitter, minimal output skew, and low power consumption, along with other competitive features.

Video List