Human Machine Interface (HMI) in building automation products needs 3D graphics, video processing, and a variety of high-speed interfaces. All these features are available in the Renesas’ Verified Linux Package (VLP) incorporating an industrial-grade Linux Civil Infrastructure Platform (CIP) super long-term support (SLTS) kernel in the RZ/G series’ Board Support Package (BSP). Achieving this full-fledged BSP is a journey full of joy that I would like to share with you here.

Reduced Development Time

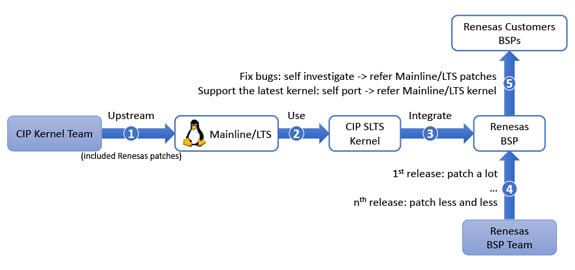

Taking advantage of the CIP reference hardware platforms, the RZ/G BSP development starts with upstreaming to Mainline/LTS, then using in CIP kernel, and finally integrating into the BSP. It is a tedious process among the CIP kernel team, members, and non-members of kernel development community, and Renesas cannot wait.

Figure 1. Process for Renesas and Customers to Reduced Time to Develop, Maintain and Update BSPs

To deliver on time to customers, the BSP team must start development and patch a lot in the first release before the CIP kernel is mature, and incorporate the CIP kernel into BSP. From the second release onwards, the more Renesas patches are accepted in the CIP kernel will result in lesser patches needed by the BSP team. At the saturation point, the BSP team has almost no kernel patching work, except for proprietary modules.

Additionally, both Renesas and our customers gain benefits in kernel bug fixing and updating. Before CIP, to fix a bug, we had to investigate the reason, find possible solutions, decide the best solution, apply the solution, regression test, and review carefully to make sure the fixing does not cause a negative impact on the kernel. It takes a lot of effort and sometimes out of our local capabilities. To support the latest kernel, we had similar concerns. After CIP is implemented, we refer to Mainline/LTS to fix bugs or support the latest kernel features reducing the development time greatly.

Improved Engineering Capabilities

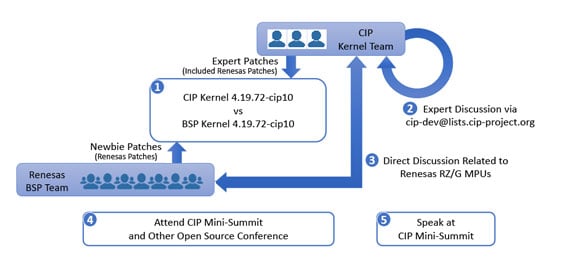

In developing engineering capabilities, CIP also brings us many chances to learn from and work with the experts.

Firstly, comparing our newbie patches to expert patches created by the kernel team teaches us what is right and what is wrong. Based on the golden model, we are able to create patches in the same way to reach that level. Every time our patch is similar, we succeed. Every time our patch is different, we fail. Regardless of the challenges faced, we continue to improve and get ready for more challenges.

Figure 2. Engineers Improve Capabilities via Daily Work and International Events

Besides comparing the two results, we also follow closely on the discussion via [email protected]. It helps us to understand the background and different viewpoints of kernel development, especially in direct discussions relating to the RZ/G series. We can improve not only coding skills but also communication skills.

Lastly, as CIP members, we join international events. At CIP Mini-Summit and other Open Source conferences, we catch up with the latest technology trend, meet people from all over the world, touch and feel amazing exhibition booths, and get inspired by the presentations.

With a stronger engineering capability in Renesas, we are able to release BSPs with higher quality in a shorter time. We even add new features to the current BSPs and develop new BSPs. We provide what customers need - an industrial-grade Linux maintained for 10+ years in a Verified Linux package to reduce maintenance man-hours and gain customer satisfaction! And, we are continuously working to develop better and more fully-fledged BSPs.

Learn more about RZ/G Verified Linux Package.