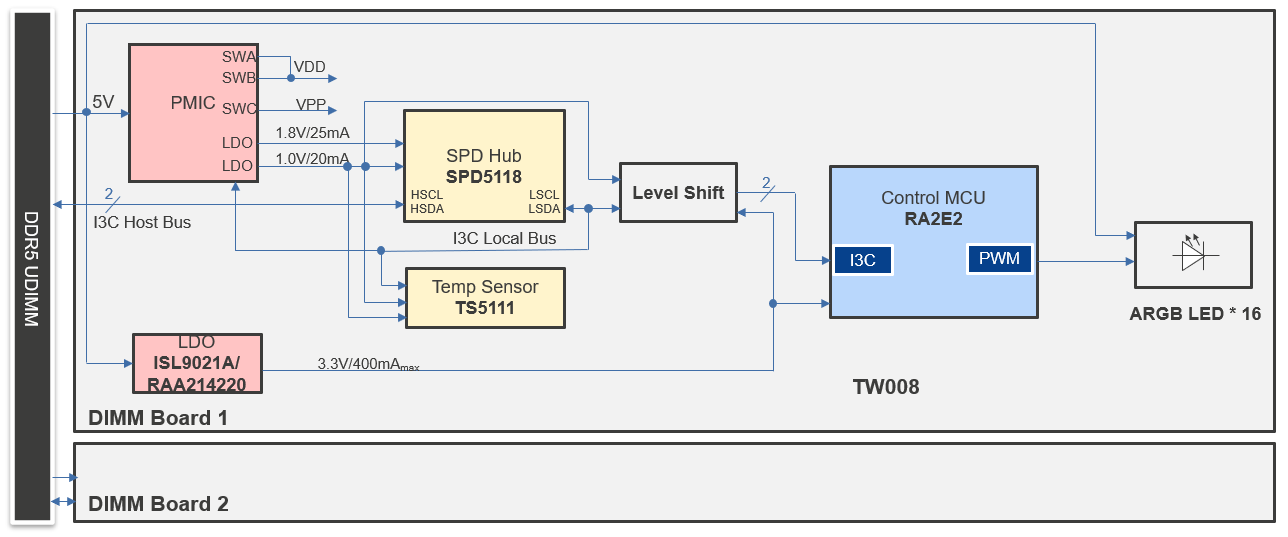

A new Sideband Bus, officially known as JESD403-1 JEDEC Module Sideband Bus, is introduced by the DDR5 system management. The DDR5 standard development is in cooperation between JEDEC and MIPI Alliance.

In the context of this new application engagement, the SPD Hub, PMIC and Microcontroller used in this application are required to be highly integrated based on the protocol compliance. Therefore, Renesas has developed a solution in the combination of Renesas SPD5 Hub SPD5118, Renesas PMIC, Temperature Sensor and a new Renesas RA RA2E2 Group to realize the Sideband Bus operation fitting the JEDEC JESD403 and MIPI I3C BasicSM requirement. On the other hand, those key Renesas devices are fully certified by MIPI I3C BasicSM, and the system also provides backward compatibility for legacy JEDEC I2C implementations.

A brief architecture of DDR5 DIMM Sideband Bus and Host Bus

The Renesas DDR5 solution comes with a prototyping kit that follows the above architecture for the bus and power layout, and a level-shifting circuit is adopted in the front of RA I3C bus to satisfy the specified Bus voltage by JESD403-1. Customers can leverage this fully integrated kit with their SDRAM module to speed up the product launch plan.

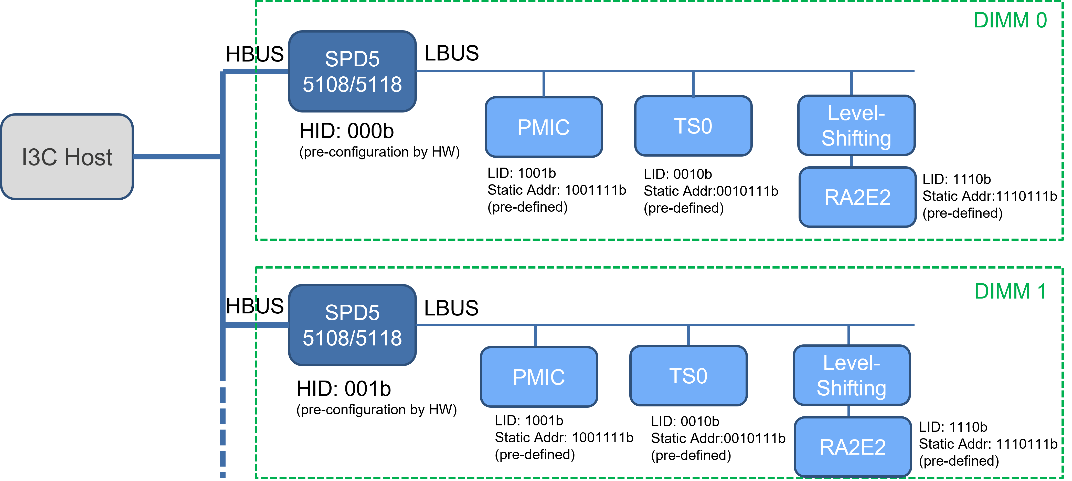

Management Bus Protocol

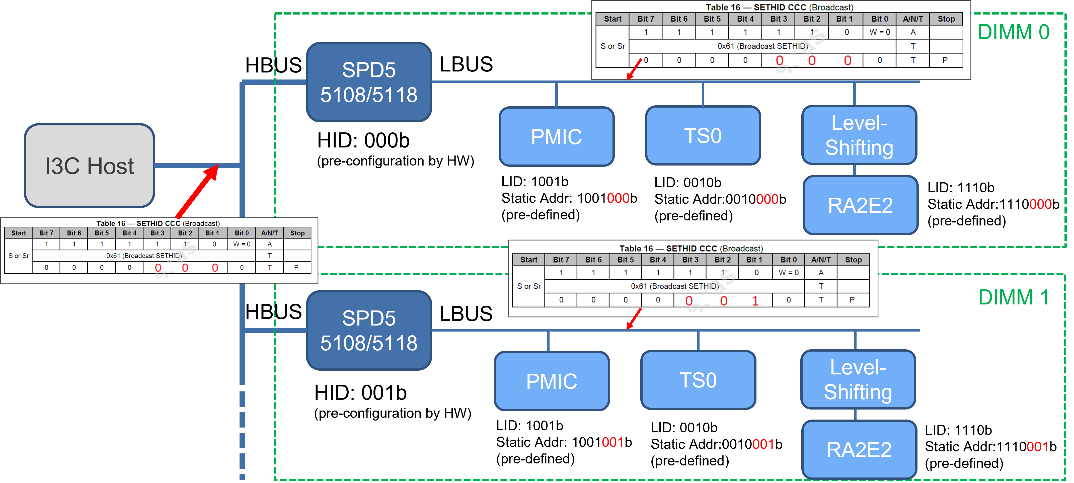

Sideband Bus uses a specific and structured addressing scheme as briefly demonstrated below to identify DIMMs and devices on the DIMMs. Hence, I3C basic’s ENTDAA and PID-based address enumeration scheme is not mandated. Based on this condition, the SPD Hub handles the address enumeration and HID assignment through two modes, and the devices on the DIMMs, which can operate in I3C basic mode, should support the JEDEC SETHID CCC and SETAASA CCC.

In the JEDEC I2C mode, which is the power on default, transactions, where the devices on the DIMMs are the targeted slave devices, begin with the Host issuing a START condition followed by a 7-bit slave address then a read or write bit. During the transaction, the SPD Hub as the first receiver replaces the LSB 3bits (HID) of the slave address for the addressed DIMM and forwarding to the local bus, except the broadcast address of 0x7E. The SPD-Hub detects the HID/DIMM_ID using the precision resistor and assists in the assignment of HID.

In the JEDEC I3C mode, which is in effect until a JEDEC SETHID CCC is received by SPD-Hub as the first receiver on the Sideband Bus. Once the hub detects a JEDEC SEHID CCC, the hub stops to do the HID bit flipping and transparently passes the incoming 7-bit slave address as is to the local bus. Following this operation, all the I3C devices on the DIMMs receiving the SETHID CCC from SPD-Hub should update its static address assignment and wait for the SETAASA CCC for the completion of address assignment to enter the I3C basic operation.

The images below summarize the above operation description for two different modes.

Power on default in I2C mode before JEDEC SETHID CCC is received.

Entering I3C mode while JEDEC SETHID CCC is received.

The RA2E2 group contains I3C interface that is fully certified by MIPI I3C BasicSM and has backward compatibility for legacy JEDEC I2C implementations, a designer able to simplify the hardware design and easy to migrate from legacy I2C platform to I3C platform smoothly.

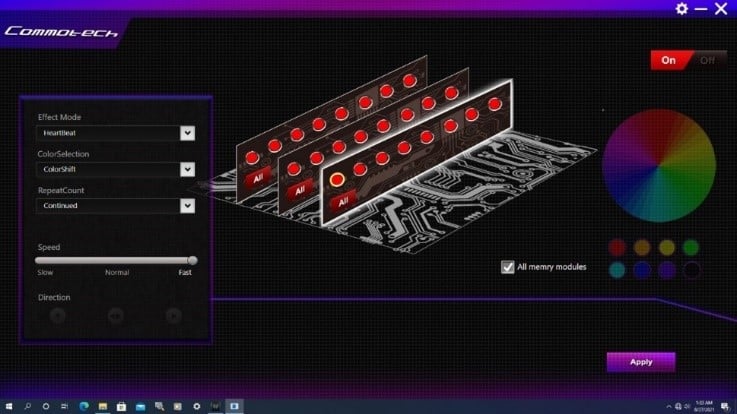

DDR5 ARGB LED Control Implementation

The RA2E2 group offers 6 channels General PWM Timers within a 24-pin HW Quad Flat No-leads (HWQFN) Package that measures only 4.00 x 4.00mm. With the hardware support, the options of lighting effect can be extended by maximizing the amount of controllable ARGB LED array.

Demonstration and Verification

As a MIPI alliance member and earlier adoption of MIPI I3C Basic SM and JEDEC JESD 403-1, Sideband Bus operation and protocol compliance verification on Renesas solution have been completed through Prodigy I3C Protocol Analyzer and Exerciser, which is able to support MIPI I3C Basic V1.0, V1.1 specification. Also, Renesas' solution can be backward compatible to SM Bus to meeting Intel's current DDR4 and DDR5 structure requirement on LED lighting control, and turnkey solution including H/W, F/W and S/W also provided by Renesas cooperation 3rd party to enhance the overall development environment.