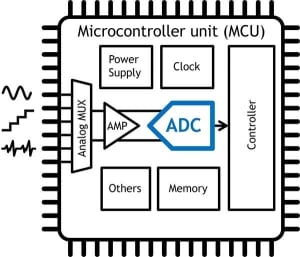

Today’s topic is "Renesas Presented an Ultra-Low Power Discrete-Time Delta-Sigma ADC at VLSI 2023!" Embedded systems around us are becoming increasingly intelligent, with microcontrollers (MCUs) constantly sensing the environment and controlling devices based on pre-installed programs. The AD converter in the MCU plays a vital role in converting the environmental sensing results (analog data) into digital data that the computer can process. Therefore, ADCs are required to have both high-speed conversion and low power consumption.

Discrete-time (DT) delta-sigma (DS) ADCs are highly accurate and suitable for integration into MCUs in terms of their process, voltage and temperature (PVT) robustness, jitter sensitivity, and frequency scalability. Still, their high-speed conversion and low-power operation have been challenging.

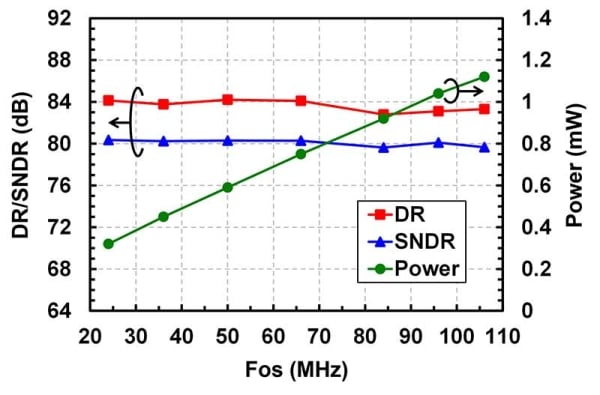

The new technology presented here is a dynamic circuit-based, ultra-low power DT DS ADC that solves this challenge. It offers a solution to reducing power consumption while maintaining accuracy in conversion. With an oversampling ratio of 24, it achieves a bandwidth of 2MHz, a dynamic range (DR) of 83dB, a signal-to-noise and distortion ratio (SNDR) of 80dB, and higher efficiency compared to conventional delta-sigma modulators (DT-DSM). This innovative technology will enable MCUs to be utilized in broader IoT applications.

Renesas presented this achievement at the 2023 Symposium on VLSI Technology and Circuits (VLSI 2023), which took place June 11 - 16, 2023 in Kyoto, Japan.

Learn more about the VLSI Symposium.