Hello, I have been working on developing CPU architecture for a long time and today's topic is "Time flies in a flash of light! The Renesas RXv2 Core has exceeded a CoreMark® of 5.0. How does it achieve this? Please stay with me until the end. In recent years, more complicated processing such as AI is performed using microcontrollers. Performance has become a key requirement.

You may want to know "What is the performance of RX (32-bit CISC)?" and we are going to introduce its CoreMark benchmark. It is not so old and has been used since 2009, which marked its 10th-anniversary last year together with RX.

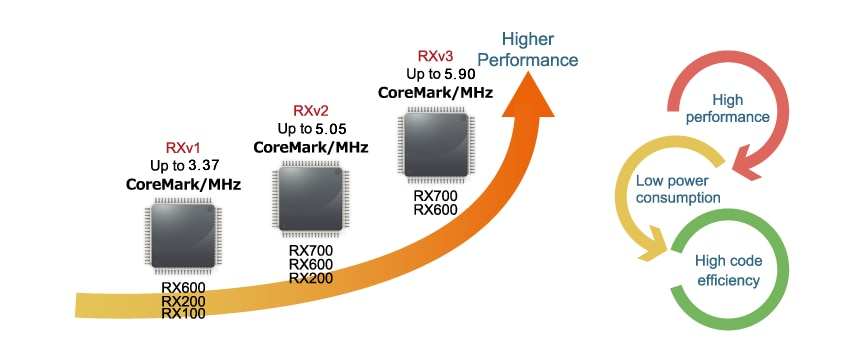

You will come to know the high performance of RX by CoreMark score. To bring out the abilities of CPU hardware, the high-efficient compiler is indispensable. We have been improving the performance of RX with both CPU architecture and compiler.

RXv2 (2nd-generation core launched in 2014) is the first CPU core for a microcontroller in the world to exceed 4.0 CoreMark/MHz. It has been seven years since then, and finally, it has achieved 5.05 CoreMark/MHz with Renesas' high-performance compiler! RXv2 Core is a dual issue pipeline architecture, based on RX's unique architecture like DSP function instructions and complex instructions by microcode. With Renesas professional engineers who know this architecture well, they were able to improve the compiler over the last 7 years to achieve these good performance results. RX has surpassed the Arm RISC microcomputer. By the way, the flagship model of RXv3 has achieved 5.90 CoreMark/MHz. Are you surprised?

The high performance of RX is the result of the good collaboration between the compiler and CPU. Looking back on the RX development for the last 10 years, "Time flies in a flash of light". Now, what processor will we develop in the next 10 years?

More information about the RX CPU

More about EMMBC CoreMark®