Overview

Description

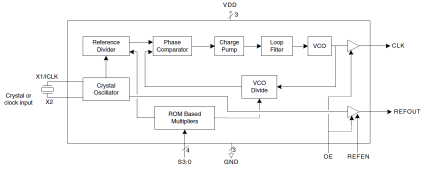

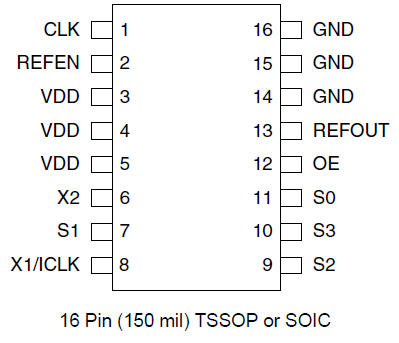

The ICS601-01 is a low-cost, low phase noise, high-performance clock synthesizer for applications which require low phase noise and low jitter. It is Renesas’ lowest phase noise multiplier, and also the lowest CMOS part in the industry. Using Renesas’ patented analog and digital Phase-Locked Loop (PLL) techniques, the chip accepts a 10 - 27 MHz crystal or clock input, and produces output clocks up to 156 MHz at 3.3 V. This product is intended for clock generation. It has low output jitter (variation in the output period), but input to output skew and jitter are not defined nor guaranteed. For applications which require defined input to output timing, use the ICS670-01.

Features

- Packaged in 16-pin SOIC or TSSOP

- Pb (lead) free package

- Uses fundamental 10 - 27 MHz crystal or clock

- Patented PLL with the lowest phase noise

- Output clocks up to 156 MHz at 3.3 V

- Low phase noise: -132 dBc/Hz at 10 kHz

- Low jitter - 18 ps one sigma typ.

- Full swing CMOS outputs with 25 mA drive capability at TTL levels

- Advanced, low power, sub-micron CMOS process

- Industrial temperature range available

- Operating voltage of 3.3V or 5V

Comparison

Applications

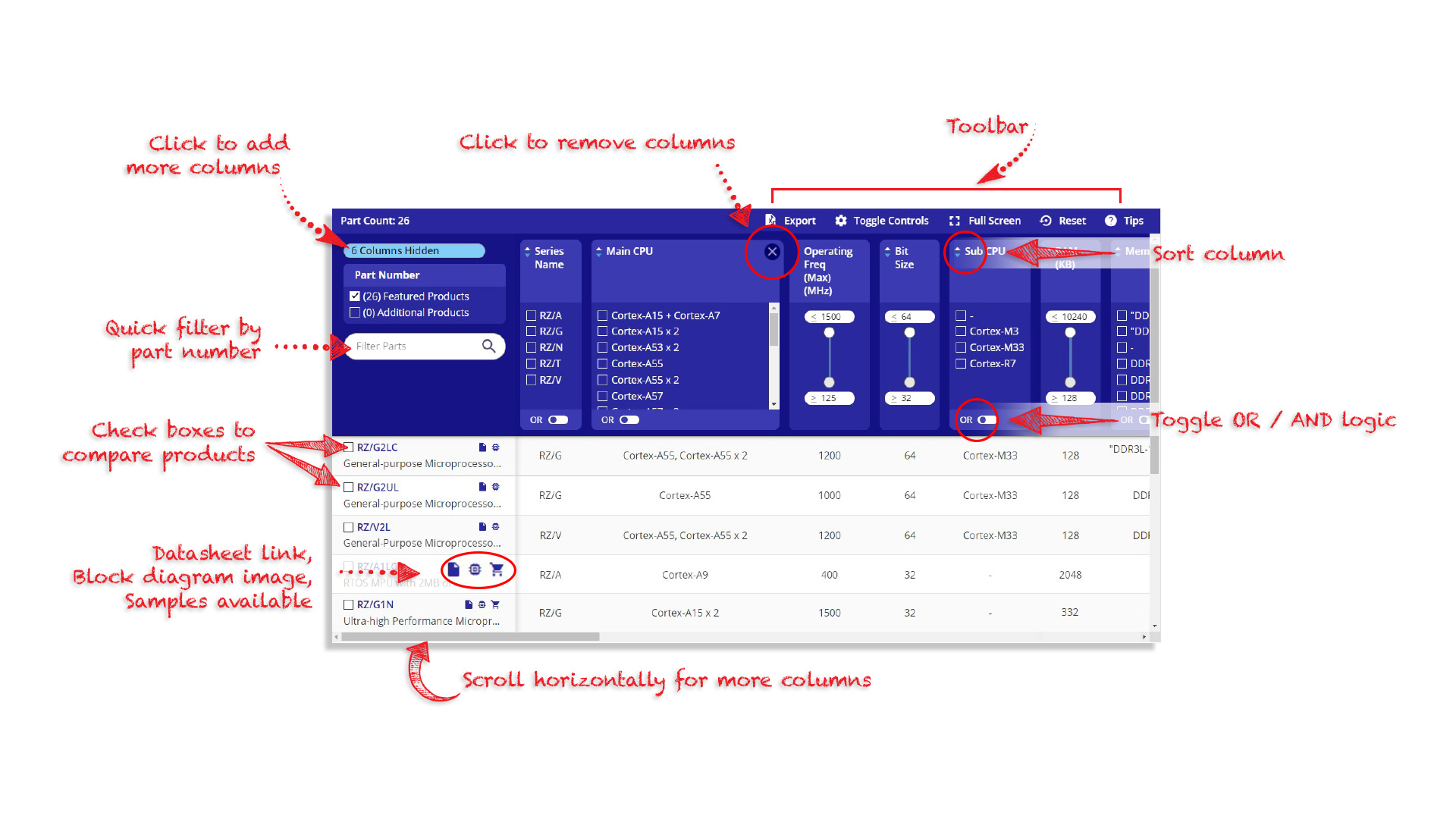

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.