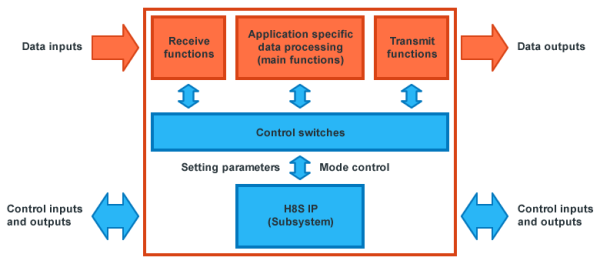

Processor IP implementation in application specific LSIs produces small size and good results by microcontroller or software control.

It is easy to control LSI modes by monitoring system, to tune parameters for each device or equipment and to control mechanics by using internal timers.

H8S CPU subsystem (H8S C200) IP is small and handy, which uses plane RTL. It is suitable for the implementation and minimization additional work-load to use processor IP.

Design features

- Full RTL/full synthesizable

Without tri-state logic or clock control - Easy interface/easy product design to implement operating mode, power down state and pin functions for the application specific LSIs.

For an example, it is possible to stop CPU (set sleep mode) under clock running. - Scan test etc. is available after implementation in LSIs.

- 3-type bus interfaces are available to design synchronous and asynchronous interface.

- The IP has many product results in various processes inside and outside Renesas. Users select the most suitable process for the LSIs.

Specification features

- Small and handy subsystem for application specific LSIs.

- 3-type bus interfaces for user functions and other IPs.

Compiled memory interface

External bus interface

Peripheral bus interface - 4-type timers for system control and mechanical control

16-bit free-running timer (FRT)

8-bit timer (TMR)

14-bit PWM timer

Watchdog timer (WDT) - Serial communication interface

- E10A-USB supported (option)

Good results by microcontroller or software control which H8S IP performs

- Easy mode control by monitoring system

- Easily tuning parameters for each device or equipment

- Easy development and easily changing functions by implementing new functions in software

- Easy mechanical control by internal timers