About This Video

In this episode, Ron Wade from IDT (acquired by Renesas) explains PCIe common clocking and its impact on timing solutions. Learn about using a single clock source, fan-out buffers, and the considerations for spread spectrum and non-spread spectrum clocking in PCIe systems.

Transcript

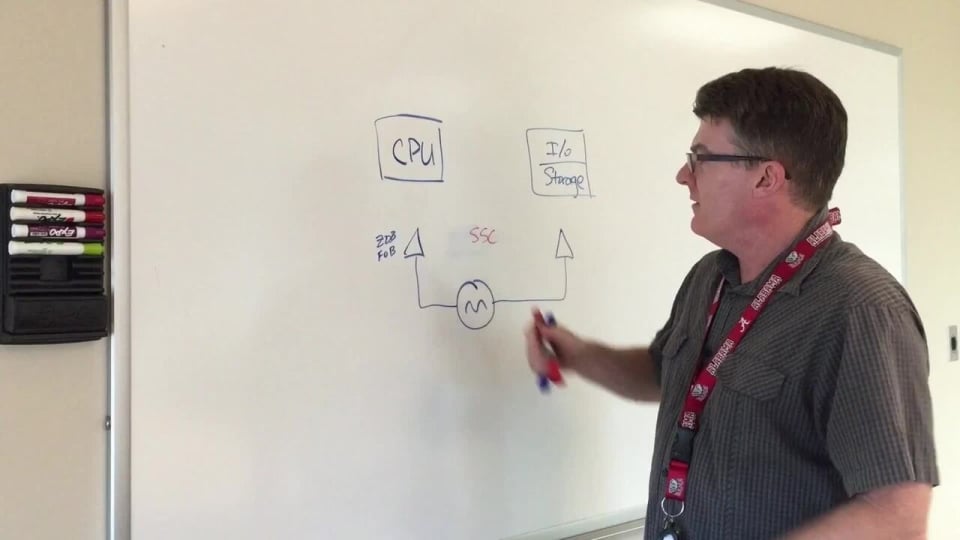

Hi, this is Ron Wade again with IDT. Today in this little episode we're gonna talk about PCI Express common clocking and its impact on the timing solutions that you would use in the system. So, as the name implies, common clocking says that all of the clocks come from one source. In this case it's a PLL. It may be spreading, it may not, but very seldom do you get all of your clocks from one device, so you'll need some sort of fan out buffers to distribute extra copies of the PCI Express clocks.

And while it's still a common clock, now we have to take into account whether we're using spread spectrum or whether we're using non-spread spectrum. If we are not using SFC, then we can fan out to these buffers here, and this could be a ZDB with a PLL inside, or it could be a fan out buffer, or it could be a part where you select between the two. Without spread spectrum, I can put this buffer in PLL mode or ZDB mode, it doesn't really matter and I don't violate the common clock requirement from the PCI Express sig. Same with this guy, it could be a fan out buffer or a PLL, ZDB, it doesn't really matter.

Things get really interesting though when spread spectrum is in use. When spread spectrum is in use then I have to have...this is my common clock. With spread spectrum in use, these have to be in fan out buffer mode. They cannot be used in PLL mode. And there's a couple of reasons for that, the simplest reason is that if this were a PLL, ZDB and it is tracking the spread, there will always be some tracking error, which means that as the input clock goes like this, the output clock is gonna overshoot it and go down like that. That's just the nature of having a PLL with finite bandwidth. So, you have tracking error here, and the tracking error will cause this to fall out of the PCI Express PPM limitations of +5,300 to -5,300 when you're using a half percent down-spread clock. So with SFC, you have your spread spectrum clock generator but any fan out buffer, any buffering at all has to be a fan out buffer without a PLL. That's a limitation on the architecture.

So the other point I'd like to make is as far as the jitter is concerned, because we're using a common clock here, to assume that the jitter on both sides for the clock is the same and all we have to do is take the difference function...that's a minus sign...the difference between the CPU and the CPU transmitter, say in the I/O storage receiver to calculate our jitter. That'll be more important when we get to the separate clocking in a future video.