The rapidly evolving automotive landscape is shifting from the traditional distributed architecture to centralized compute architecture coupled with domain integration. There is also mass deployment of advanced driver-assistance systems (ADAS) - the drive towards more autonomy. These transformations in turn are fueling the change from a hardware-central model to a software-defined vehicle (SDV) model. All these changes are driving an increase in the demand for SoCs to support higher computing needs. Along with the SoCs, a reliable open development environment is also necessary to build future vehicles and continue to evolve.

Renesas is expanding its scalable SoC portfolio with its fifth generation (Gen 5) R-Car SoCs to deliver new solutions integrating the latest cutting-edge chiplet and process node technologies for automotive in Renesas' open access SDV environment. The Renesas R-Car Gen 5 SoCs are designed specifically for centralized compute and cross-domain architectures, for software-defined vehicle applications, and for high autonomy. The scalable portfolio offers solutions to all levels of vehicles ranging from entry mass market to premium, while the SDV environment enables software reuse and portability across devices and generations with a common architecture creating a sustainable and efficient development approach for the evolving automotive industry. The key value propositions of R-Car Gen 5 SoCs are their high scalability, flexibility, power efficiency, and mixed-criticality support.

Scalable High-Performance Platform for Centralized Architecture

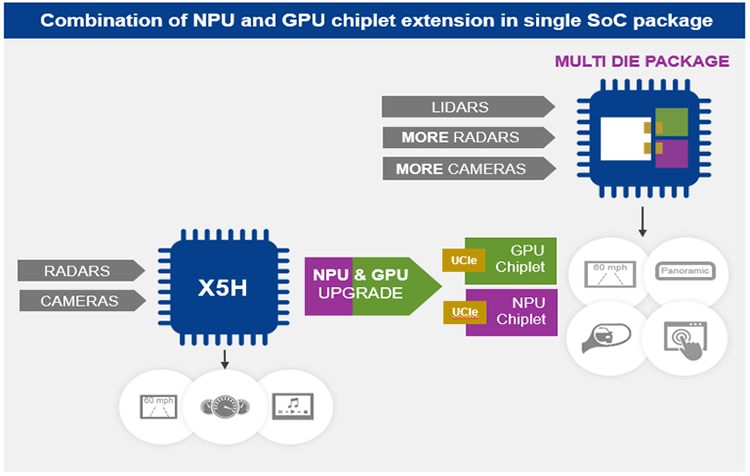

The R-Car X5H, the industry's first 3nm automotive cross-domain SoC, is a high-performance compute platform that is open, innovative, and automotive-focused. The high performance of the monolithic design can be scaled further with AI and a graphics chiplet extension using the latest compute and interconnect technology.

Key features of R-Car X5H:

- 32x Arm® Cortex®-A720AE cores achieving upwards of 1000kDMIPS to cover high compute applications.

- 6x Arm Cortex-R52 dual lockstep CPU cores for RT processing, delivering over 60K DMIPS with ASIL D support.

- AI processing of up to 400 TOPS1 with optimized NPU and DSP implementation for higher efficiency.

- Graphics performance of up to 4 TFLOPS equivalent2 with support for hardware virtualization on the GPU.

- Multi-4k media, multi-megapixel camera, and multi-display support for video and vision processing for premium ADAS/IVI.

Flexible and Modular Architecture to Meet OEM Processing Needs

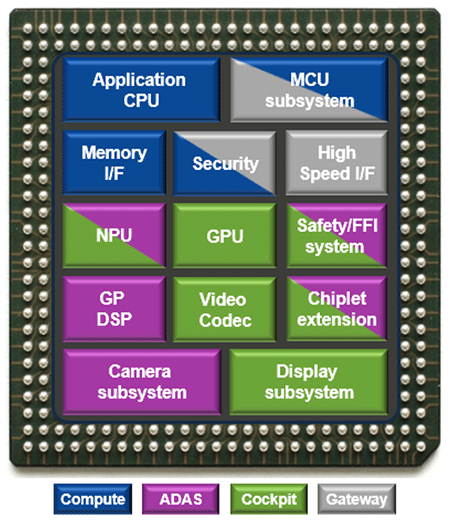

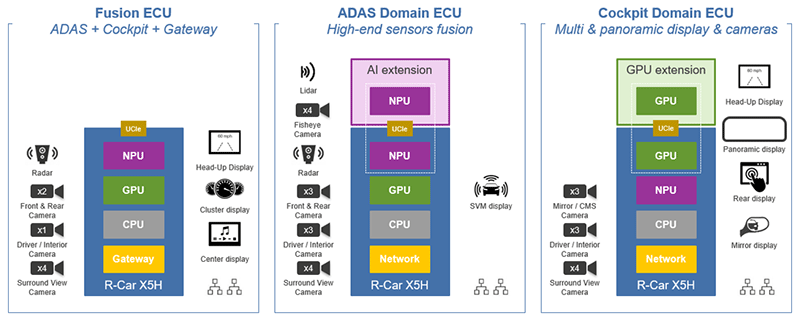

In a centralized architecture, domain integration is seen at varying levels. At the entry segment, we see a full fusion of ADAS + IVI + gateway on a single SoC to reduce cost, while at the mid and higher segments, a combination with some domain specificity is more common. Be it full-fusion or domain-specific compute, the R-Car X5H is designed to address all application configurations. Using standardized die-to-die interconnects, the AI and graphics performance can be further extended with chiplet extensions depending on the application needs. The chiplet approach enables higher performance scaling heterogeneously. The fusion application using R-Car X5H is also supported by the R-Car Open Access (RoX) SDV platform with ADAS, cockpit, and gateway solution stacks (both commercial and OSS) pre-integrated and ready to use.

At the very high-end or premium car segments, multiple domain-specific car computer architecture is adopted especially for ADAS due to the very high compute needs. Using die-to-die interconnects, the core AI capability of R-Car X5H can scale up heterogeneously via AI chiplet extension in multi-die packaging. Combined with Renesas' AI Gigafactory concept to develop AI solutions – AI toolchain, network/model support, and cloud native support – customers have an end-to-end platform for all their autonomy needs.

R-Car X5H's standardized die-to-die interconnects using the latest Universal Chiplet Interconnect Express (UCIe) interface facilitate interoperability in a multi-die system and the flexibility to mix and match depending on OEM needs as well as the ability to integrate custom accelerators. The chiplet approach is adopted to enable such open architecture while scaling for higher performance with less overhead. All these extensions are compliant with the latest automotive safety and security requirements.

Best-in-Class Power Efficiency with Leading Edge Technology

One of the challenges with integrating multiple domain functionalities into a single module is thermal or power management. R-Car X5H is built with the latest and very power-efficient 3nm process technology. The latest technology node is chosen especially for the performance to power efficiency – a 30% to 35% improvement for specific workloads compared to the next higher 5nm process. This enables the R-Car X5H to support high compute performance (e.g. AI processing for 360˚ perception) with best-in-class performance to power (TOPS/watt) efficiency and to achieve lower overall power consumption. The R-Car X5H also integrates a system control processor (SCP) supporting different low-power modes for applications such as parking, sentry mode, etc.

Secure Isolation for Multi-Domain Integration

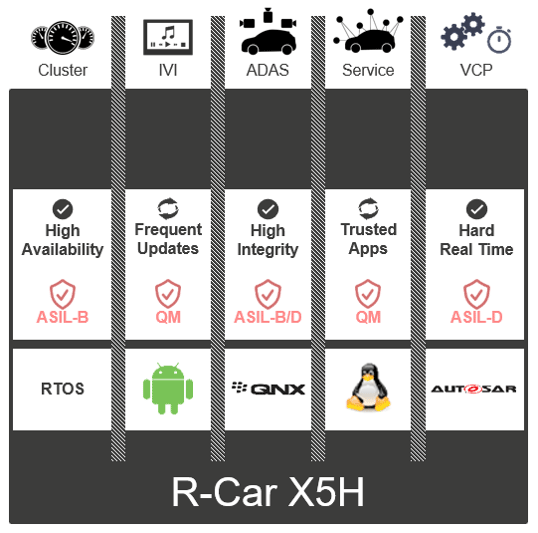

Functional safety (FuSa) is extremely important for multi-domain SDV architecture. When integrating mixed-criticality applications on a single SoC, FuSa requires stringent domain isolation or freedom from interference (FFI) to prevent cascading failures. Most of the current solutions in the market achieve this via software solutions such as hypervisors, safety islands with safety OS, etc. The software-based approaches are not as robust as the hardware-based approach inherent in distributed architecture. A hardware-based FFI solution enables strict isolation for multi-domain integration on a single chip. With a long history of delivering safety-compliant devices, safety and security are part of Renesas' DNA. The R-Car Gen 5 SoCs use Renesas' unique and industry-proven hardware-based FFI solution to achieve the best isolation for mixed-criticality multi-domain integration on a single chip compared to other solutions in the market. This solution implements isolation at multiple levels such as the peripheral level, memory level, and bandwidth using features like Region ID, memory protection, and advanced QoS.

Renesas Open Access (RoX) Development Platform

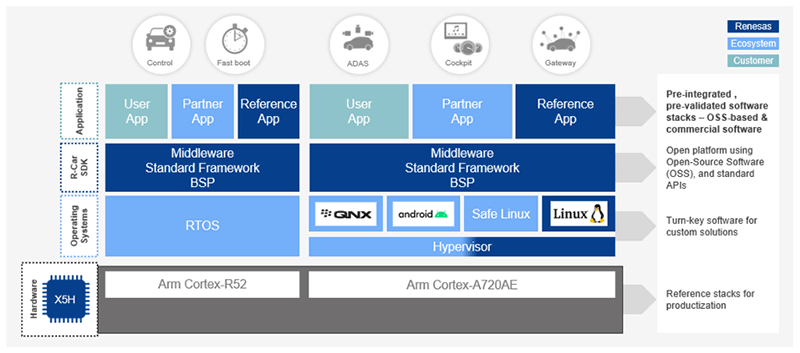

R-Car X5H and all future R-Car Gen 5 SoCs are designed to enable and accelerate SDV development. R-Car Gen 5 is supported by the R-Car Open Access (RoX) SDV platform. The RoX platform integrates all essential hardware, software (OS, MW, and Apps), and tools needed for automotive developers to rapidly develop next-generation vehicles with secure and continuous software updates. RoX provides OEMs and Tier 1 suppliers with the flexibility to develop and deploy a broad range of scalable compute solutions for ADAS, IVI, gateway, and fusion systems using a virtual platform or on the hardware and deploy seamlessly with integrated cloud support.

With the R-Car Gen 5 SoC family, Renesas is transforming customer experience and driving the future of SDV architecture. From the native high performance of the chips to further scalability with chiplets and by unifying MCU and SoC architectures on Arm®, Renesas offers scalability like no other solution available in the market. Covering all applications including but not limited to ADAS, IVI, gateway, and control combined with support for cross-domain central/zonal architecture, R-Car Gen 5 SoCs cover the breadth and depth of customer platform needs. With the latest 3nm automotive process technology, chiplet architecture, and hardware-based FFI solution, R-Car Gen 5 SoCs are positioned at the leading edge of innovation delivering a cost-effective solution that has a fast time to market and best-in-class power efficiency; all with a robust functional safety backbone that is part of Renesas’ automotive DNA.

1Sparse TOPS

2Equivalent TFLOPS based on data from Manhattan 3.1 benchmarking