Earlier this month at electronica 2024 in Munich, Germany, I had the pleasure of speaking to a group of international journalists to introduce our fifth-generation (Gen 5) R-Car system-on-chip (SoC) for software-defined vehicle (SDV) design.

SDV platforms are reinventing the automotive value chain by incentivizing designers to overturn the industry's conservative heritage of methodical technology advances. New electric/electronic (E/E) innovations are rewriting old rules with the advent of electrification, autonomous driving, advanced safety systems, and a vast mobile network, making the average car safer, smarter, and more accessible than ever before.

The SDV sea change signals a permanent shift from discrete, distributed automotive electronic control units (ECUs) to a centralized control architecture. By replacing a dispersed web of sensors, actuators, and processors, these highly integrated zonal ECU clusters are emerging to serve multiple automotive domains such as Advanced Driver Assistance Systems (ADAS), in-vehicle infotainment, and gateway applications that enable data transfers between disparate bus interconnects.

Renesas has pioneered SDV design principles for more than a decade, applying various levels of SoC integration across our MCU, sensor, analog, power management, software, and system solutions. We believe our broad and comprehensive portfolio positions Renesas to outperform the automotive semiconductor sector and exceed average ADAS market growth between 2023 and 2030.

Renesas R-Car Gen 5 Future-Proofs Multi-Domain Automotive Compute Solutions

Having recently augmented our industry-leading R-Car lineup with the R-Car Open Access (RoX) accelerated hardware/software development platform, Renesas is addressing these industry changes by expanding our purpose-built SDV automotive SoC portfolio.

The first device in the Renesas R-Car Gen 5 family, the R-Car X5H SoC delivers the industry's highest level of integration and performance and is the first multi-domain automotive SoC built on TSMC's 3nm process technology. The advanced manufacturing node reduces power by up to 35 percent compared to devices designed for 5nm processes, simplifying cooling requirements and extending vehicle driving range.

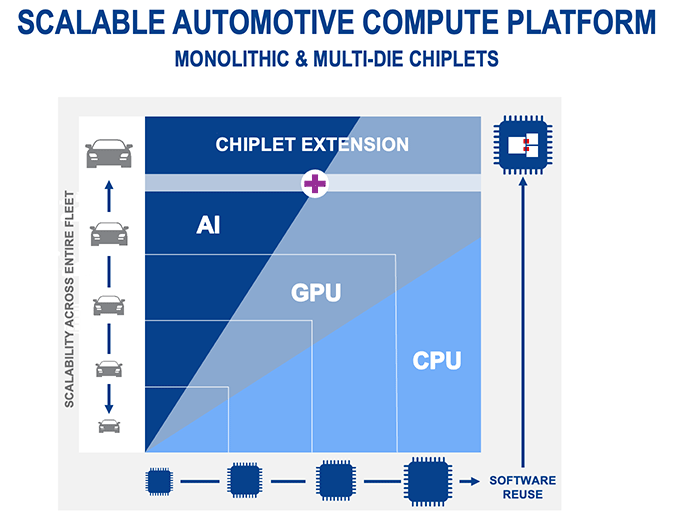

Until the fourth generation, Renesas R-Car SoCs were designed for specific SDV use cases that required leading-edge AI and graphics performance or dedicated data gateways. The R-Car X5H is a highly scalable monolithic SoC series which also integrates multi-die chiplet technology creating a flexible platform that can be customized – and software upgraded – to meet the requirements of any use case ranging from specific domain integration for ADAS or cockpit and infotainment ECUs to cross-domain compute (a.k.a. fusion). By enabling software reuse and portability with a common architecture, the R-Car X5H is the first SoC of its kind to enable OEMs and Tier 1 customers to centralize ECU layout, streamline vehicle development, and future-proof designs across multiple vehicle classes.

The open development platform allows the combination of open-source software with customer/partner IP, allowing users to continuously update software and improve the vehicle's ability to detect and respond to its environment. This adaptability is crucial as the auto industry moves to fully autonomous vehicles that require constant enhancements and real-time information processing.

What's Under the Hood?

The R-Car X5H SoC is a marvel of chip design. With native neural processors for ADAS applications, GPU and display engines processing cockpit and infotainment data, customers can easily scale up performance through heterogeneous chiplet extensions. An external NPU extension, for example, allows designers to increase AI processing performance by a factor of three to four times using their own IP and an in-package UCIe die-to-die interconnect. By using external GPU chiplets, graphics performance can be tripled, allowing next-gen infotainment experiences such as pillar-to-pillar displays and premium gaming.

As the flagship product in our new SoC family, the R-Car X5H delivers automotive designers high-performance compute with over 1000k DMIPS, the industry's fastest AI acceleration with up to 400 TOPS performance and GPU processing as high as 4 TFLOPS equivalent. The R-Car X5H incorporates 32 Arm® Cortex®-A720AE CPU cores for application processing and another six Dual Core Lock Step (DCLS) Arm Cortex-R52 CPUs to support ASIL D-level certification – the industry's highest automotive ISO-recognized safety integrity classification. And, while other SoCs rely solely on software to isolate safety-critical functions such as brake-by-wire, the R-Car X5H includes hardware-based Freedom from Interference (FFI) technology. FFI designates separate, redundant safety domains with a dedicated CPU core, memory, and interfaces, which prevents catastrophic cascading vehicle failures in the event of a hardware or software fault from a different domain.

Additionally, our reference designs, based on open-source software, promote rapid evaluation and development, while our pre-integrated, pre-validated software stacks use commercial software to enable faster prototyping and time-to-market.

Our Automotive DNA Is Baked into the R-Car X5H SoC

The trend toward SDVs designed with a centralized, zonal architecture is driven by demand for advanced safety, autonomous driving, connected vehicles, immersive UX, and the move to EVs. But across automotive fleets, one size does not fit all.

Renesas is well-positioned with an extensive, scalable portfolio that encompasses everything from basic controls to real-time applications and high-performance compute. And with the new R-Car X5H SoC series, we are uniquely situated within the SDV ecosystem.

Building on our MCU legacy, Renesas is leveraging leading-edge chiplet technology, a familiar toolchain, and deep-sub-micron manufacturing to increase vehicle design efficiency and reduce development cost and time to revenue for our customers. For more performance details, I recommend reading this companion blog: "Advance the Development of Centralized Car Compute and SDV Architectures with R-Car Gen 5 SoC".