I would like to introduce the RH850 Model-Based Development Environment, Embedded Target for RH850 Virtual Platform, and its functions. For reference, please refer to the RH850 Model-Based Environment [Embedded Target for RH850 Virtual Platform] product page, where a demo video has been uploaded.

About Embedded Target

Renesas is advancing the concept of a unified development environment (Corporate strategy page.17) as a next-generation vehicle development environment and, as part of that, is offering Embedded Target to support design through different levels of abstraction. Embedded Target is a tool that converts a model at several levels of abstraction. Embedded Target for RH850 converts the abstraction from MILS to PILS, and Embedded Target for RH850 Virtual Platform converts the abstraction from MILS to vHILS (described later). This blog introduces Embedded Target for RH850 Virtual Platform.

MILS: Model In the Loop Simulation. MILS is verification by using a model in Model-Based Development

PILS: Processer In the Loop Simulation. PILS is verification by using a model and processor in Model-Based Development

About Embedded Target for RH850 Virtual Platform

Embedded Target for RH850 Virtual Platform (hereafter ET-VPF) is a model-based development tool offered by Renesas. Conventionally, HILS, which verifies the whole system, was conducted at a later phase of development. However, by using Virtual Platform (hereafter VPF), it is possible to verify the equivalent to HILS in an early phase. Renesas calls HILS using VPF “vHILS” (Fig. 1).

HILS: Hardware In the Loop Simulation. HILS is verification by using a real device in Model-Based Development

vHILS: virtual Hardware In the Loop Simulation. vHILS is verification by using a device model instead of a real device in Model-Based Development

vHILS Using VPF

ET-VPF performs simulation by using RH850 VPF (Introduction of the RH850 Virtual Platform (VPF) to Improve the Quality of Automotive Software). RH850 VPF is a platform that enables the simulation of an RH850 device, including peripherals such as port and ADC.

For example, an input port receives an external signal from a controlled object block (1), the ADC converts analog data to digital data (2), the CPU executes data processing by application code (3), an output port outputs the calculation result as a control signal (4), and the control signal controls the controlled object block (5). In this way, it is possible to simulate vHILS equivalent to HILS.

vHILS Execution Flow by ET-VPF

First, the user prepares a MILS model which models the whole system (Fig. 3 upper left), and adds peripheral IP blocks to the controller block in order to control the controlled object block by device.

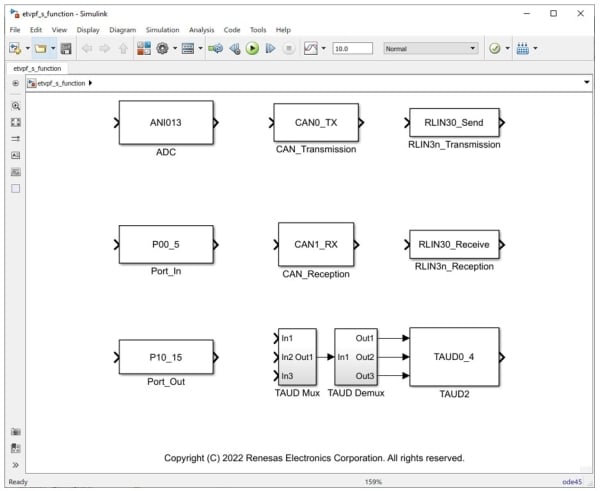

ET-VPF prepares peripheral IP such as port, ADC, and so on as a Simulink block (Fig. 4).

For added peripheral IP blocks, it is possible to configure their basic settings (Fig. 3 lower left). It is possible to configure detailed settings on Smart Configurator, which works together with ET-VPF.

After setting, ET-VPF automatically conducts the process until vHILS execution.

A device driver program that controls peripheral IP is generated. Application code is generated from the user algorithm block in the controller block. They are included into the build environment, and then the load module is generated by the build tools automatically (Fig. 5).

The generated load module is downloaded to VPF. The controller block is replaced with the bridge block, which connects Simulink and VPF, and then vHILS simulation is executed by using Simulink and VPF (Fig. 3 lower right). With this vHILS, it is possible to verify the whole system in the early phase of development.

ET-VPF can display a graph of execution time in every cycle (control cycle) after simulation (Fig. 3 upper right). The user can easily verify the performance of the whole system by referring to the graph.

Looking Forward

In this way, by using ET-VPF it is possible to verify the equivalent to HILS of a whole system that is designed by MILS. As of Nov. 1, 2022, ET-VPF supports RH850/F1KM-S1 and S4.

Going forward, we will add more target devices and continue to develop a unified development environment that supports several levels of abstraction.