Generating sampling clocks for ADCs is one of the most demanding applications for clean (low-jitter) clock generation. Using a noisy clock directly impacts the ability of the data converter to accurately translate the signal it is receiving. Signal-to-Noise Ratio (SNR) is an important specification for an Analog-to-Digital converter which quantifies how accurately an ADC does its job. Here is the equation which relates SNR to jitter:

SNR = -20*log(2π*FIN*tJ); where tJ is the RMS time jitter and FIN is the analog BW. tJ (RMS) is obtained by integrating the phase noise over the encode bandwidth.

I am not revisiting the derivation of the formula because it can be found elsewhere on the web.

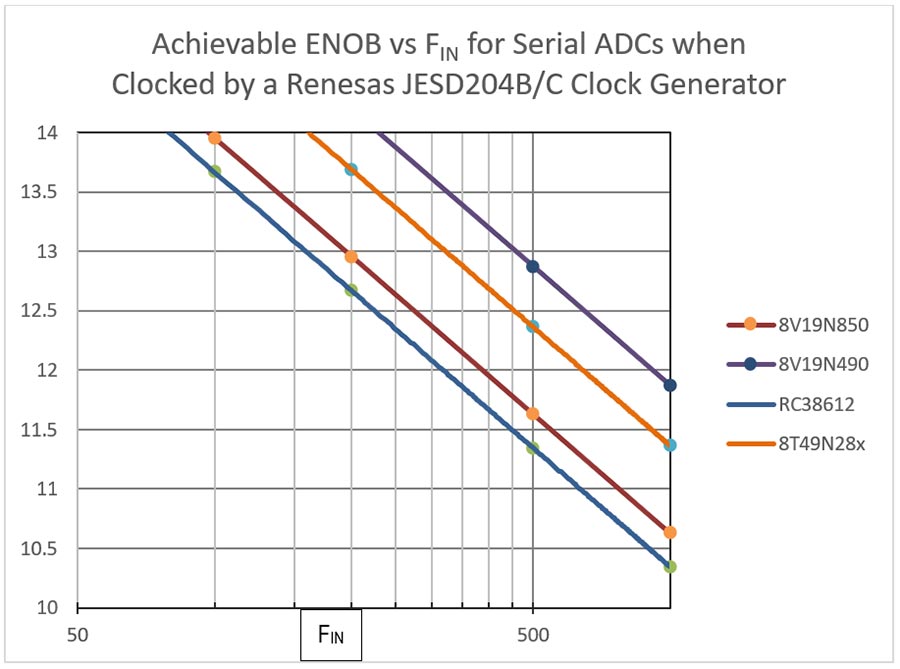

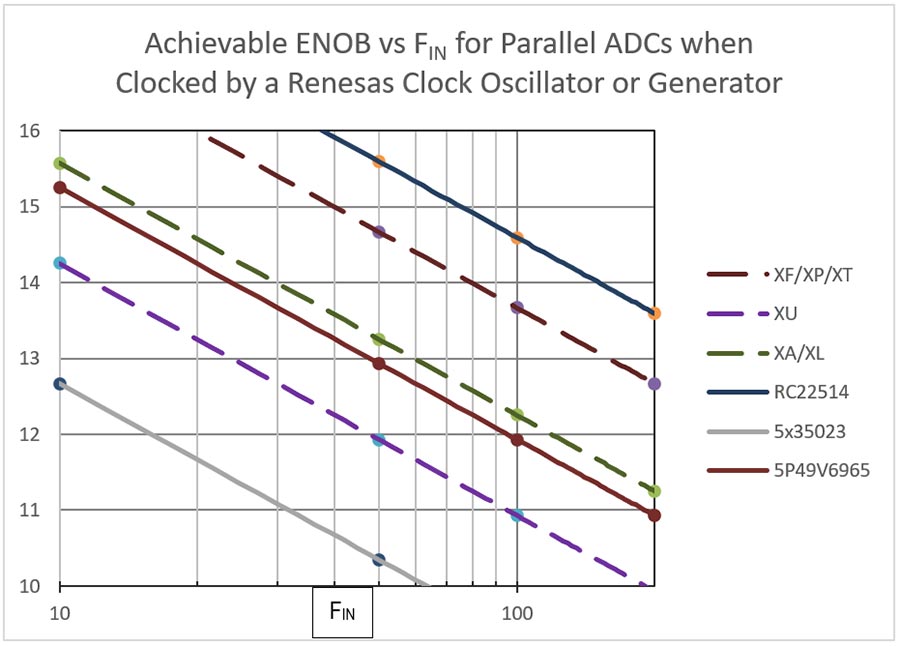

The Renesas timing portfolio is the largest in the industry. To help you navigate to the best part for your needs, Renesas provides the charts below. Here is how to use the charts to identify the right part for your needs: Find the spot on the XY grid that corresponds to your use case, second, move right and/or up to the next solid diagonal on the graph. The first solid line you encounter indicates which device Renesas recommends you consider first. Separate plots are provided for parallel and serial-output ADCs. Modern serial-output ADCs typically need to have JESD204x synchronization capability, so for that chart, only clock devices that provide support for JESD204B/C have been populated (Figure 1).

To explore alternatives to the device recommended here, use the equation previously provided [tJ = (10^(SNR/-20))/ (2π*FIN), but solving for tJ] to establish the jitter performance you need. Plug tJ (as max jitter) into the parametric search table for either our Clock Generator portfolio or our JESD204B/C Clock Jitter Attenuator portfolio.

If you have only a single converter in your system which needs clocking, you may be best served by selecting an oscillator (see dashed lines) from the chart below (Figure 2), but if you need multiple clocks for additional converters (or other components), you may be better served by selecting a clock generator (solid lines).

For more information on Renesas’s clocking portfolio visit reneas.com/clocks.