Overview

Description

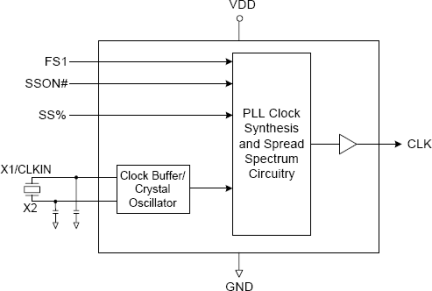

The 180-52 generates a low EMI output clock from a clock or crystal input. The device uses IDT's proprietary mix of analog and digital Phase-Locked Loop (PLL) technology to spread the frequency spectrum of the output, thereby reducing the frequency amplitude peaks by several dB. The 180-52 offers center spread selection of +/-0.625% and +/-1.875%. Refer to the MK1714-01/02 for the widest selection of input frequencies and multipliers. IDT offers a complete line of EMI reducing clock generators. Consult us when you need to remove crystals and oscillators from your board.

Features

- Pin and function compatible to Cypress W180-52

- Packaged in 8-pin SOIC

- Provides a spread spectrum output clock

- Accepts a clock input and provides same frequency dithered output

- Input frequency of 8 to 15 MHz

- Peak reduction by 7dB - 14dB typical on 3rd - 19th odd harmonics

- Spread percentage selection for +/-0.625% and +/-1.875%

- Operating voltage of 3.3 V and 5 V

- Advanced, low-power CMOS process

Comparison

Applications

Documentation

Featured Documentation

Log in required to subscribe

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Datasheet | PDF 208 KB | |

| End Of Life Notice | PDF 161 KB | |

| Product Change Notice | PDF 439 KB | |

| End Of Life Notice | PDF 161 KB | |

| End Of Life Notice | PDF 159 KB | |

| Product Change Notice | PDF 361 KB | |

| Product Change Notice | PDF 223 KB | |

7 items

|

||

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Applied Filters: