Overview

Description

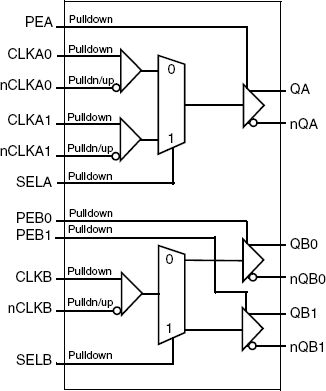

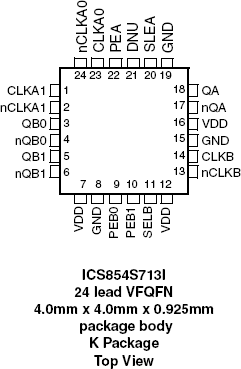

The 854S713I is a differential, high-speed 2:1 data/clock multiplexer and 1:2 clock/data demultiplexer in one device. The outputs support pre-emphasis in order to drive backplanes and long transmission lines while reducing inter-symbol interference effects. The pre-emphasis level is individually configurable to optimize for low bit error rate or power consumption. Pre-emphasis utilizes an increased output voltage swing for transition bits. The device is optimized for data rates up to 4.5Gbps (NRZ) and for deterministic jitter in data applications and low additive jitter in clock applications. The outputs are LVDS-compliant while the differential input is compatible with a variety of signal levels such as LVDS, LVPECL and CML. A small package (4.0mm x 4.0mm 24-lead VFQFN) supports space-efficient board designs. The 854S713I operates from a 3.3V power supply and supports the industrial temperature range of -40 to +85 deg C.

Features

- 2:1 differential data/clock multiplexer and 1:2 data/clock demultiplexer with a two-output fanout

- 4.5 Gbps max. data rate (NRZ)

- Differential LVDS outputs

- Differential inputs supporting LVDS, LVPECL and CML levels

- Configurable output pre-emphasis

- Low-skew output: 25ps (maximum)

- Low data deterministic jitter: 3ps (maximum)

- LVCMOS interface levels for the control inputs

- Additive phase jitter, RMS: 0.09ps (typical)

- Full 3.3V supply voltage

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Applied Filters: