Overview

Description

In an integrated cockpit, the converged system integrates and analyzes multiple streams of information and reports the results to the driver in an optimized format, which is increasingly delivered through interoperation with smartphones. This convergence is driving demand for higher-level functionality and greater added value for entry-level applications.

Display audio systems are one growth area that is well suited for smartphone interoperation. This interoperability makes it possible to provide functionality that has been difficult to implement in the vehicle information system itself, and the range of functions is expected to continue expanding. This requires a broad scope of support, including support for interfaces enabling connections with multiple smartphones and to support the broad range of applications accessed via these connections. As a result, software development has become more challenging, and the resulting slowdown in development speed and sudden increase in development costs are becoming key issues.

As the integrated cockpit becomes mainstream, it is generating a wide variety of implementations. OEMs and Tier-1s are looking for automotive suppliers to provide a broad product lineup that is flexible enough to support these many variations, and the ability to reuse software across the entire product lineup – key requirements that must be met to enable the realization of integrated cockpit systems.

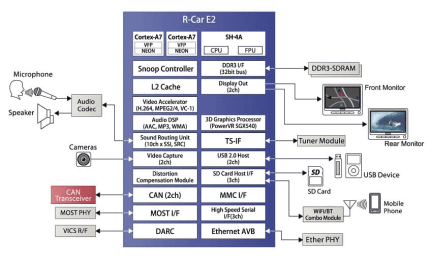

To meet these requirements, Renesas developed the R-Car E2 solution to deliver optimized infotainment and display audio for entry-level integrated cockpit systems. In combination with other second-generation Renesas R-Car Series devices (R-Car H2, M2, E2, and V2H), this helps achieve the scalability required to bridge the full range of integrated cockpit systems from entry-level to high-end models.

Features

- Performance and functions optimized for display audio and entry-level integrated cockpit systems

- Scalability to support a wide variety of requirements

- Highly accessible development environment for ease of design

Specifications

- Product No.: R-Car E2 (R8A7794)

- Power supply voltage: 3.3/1.8 V (IO), 1.5/1.35 V (DDR3), 1.0 V (Core)

- CPU core:

- Arm® Cortex®-A7 Dual Core

- SH-4A core

- Cache memory

- Arm® Cortex®-A7 Dual Core

- L1 Instruction cache: 32 KB

- L1 Data cache: 32 KB

- L2 Cache: 512 KB

- SH-4A core

- L1 Instruction cache: 32 KB

- L1 Data cache: 32 KB

- Arm® Cortex®-A7 Dual Core

- External memory:

- DDR3-SDRAM

- Data bus width: 32 bits

- Expansion bus

- Flash ROM and SRAM

- Data bus width: 8 or 16 bits

- Graphics: PowerVR SGX540 (3D)

- Video

- Display Out × 2 ch (RGB888)

- Video Input × 2 ch

- Video codec module VCP3 (H.264/AVC, MPEG-2/4, VC-1)

- IP conversion module

- TS Interface × 1 ch

- Video image processing (color conversion, image expansion, reduction, filter processing)

- Distortion compensation module (image renderer) × 1 ch

- Audio

- Audio DSP

- Sampling rate converter × 6 ch

- Serial sound interface × 10 ch

- MOST DTCP

- Storage interfaces

- USB 2.0 Host interface × 2 port (wPHY)

- SD Host interface × 3 ch (SDXC, UHS-I)

- Multimedia card interface × 1 ch

- In car network and automotive peripherals

- Media local bus (MLB) Interface × 1 ch

- Controller Area Network (CAN) Interface × 2 ch

- IEBus TM Interface

- Security

- Crypto engine (AES, DES, Hash, RSA)

- SecureRAM

- Other peripherals

- DMA controller

- LBSC DMAC: 3 ch / SYS-DMAC: 30 ch / Audio-DMAC: 13 ch / Audio(peripheral)-DMAC: 29 ch

- 32-bit timer × 12 ch

- PWM timer × 7 ch

- I2C bus interface × 8 ch

- Serial communication interface (SCIF) × 18 ch

- Quad serial peripheral interface (QSPI) × 1 ch (for boot)

- Clock-synchronized serial interface (MSIOF) × 3 ch (SPI/IIS)

- Ethernet AVB controller (IEEE802.1BA/802.1AS/802.1Qav/IEEE1722, GMII/MII, without PHY)

- Ethernet controller (IEEE802.3u, RMII, without PHY)

- Interrupt controller (INTC)

- Clock generator (CPG) with built-in PLL\

- On-chip debugger interface

- Package: 501-pin Flip Chip BGA (21 mm × 21 mm)

Arm® and Cortex® are registered trademarks of Arm Limited.

PowerVR® is a trademark of Imagination Technologies Limited.

All names of other products or services mentioned are trademarks or registered trademarks of their respective owners.

Comparison

Applications

- Integrated cockpit

- Automotive infotainment

Documentation

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Manual - Hardware | PDF 1.10 MB | |

1 item

|

||