Overview

Description

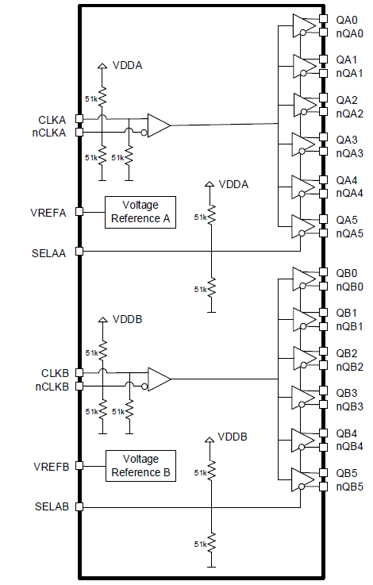

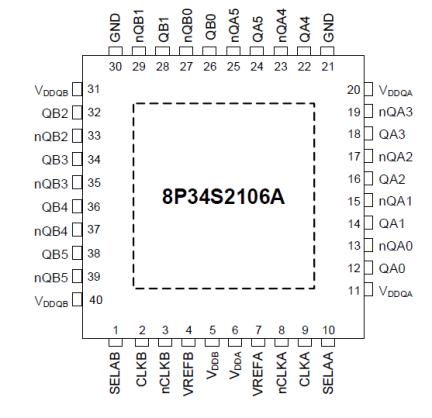

The 8P34S2106A is a high-performance, low-power, differential dual 1:6 LVDS output 1.8V/2.5V fanout buffer. The device is designed for the fanout of high-frequency, very-low additive phase noise clock and data signals. Two independent buffer channels are available, each channel has six low-skew outputs. High isolation between channels minimizes noise coupling. AC characteristics such as propagation delay are matched between channels. Guaranteed output-to-output and part-to-part skew characteristics make the 8P34S2106A ideal for clock distribution applications demanding well-defined performance and repeatability. The device is characterized to operate from a 1.8V/2.5V power supply. The integrated bias voltage references enable easy interfacing of AC-coupled signals to the device inputs. The device supports fail-safe operation, it can handle DC levels up to 2.5V on its input pins while the device is powered down with very low leakage currents and doesn’t impact long-term reliability.

Features

- Dual 1:6 low skew, low additive jitter LVDS fanout buffers

- Matched AC characteristics across both channels

- High isolation between channels

- Low power consumption

- Both differential CLKA, nCLKA and CLKB, nCLKB inputs accept LVDS, LVPECL, and single-ended LVCMOS levels

- Maximum input clock frequency: 2GHz

- Output amplitudes: 350mV, 500mV (selectable)

- Output bank skew: 10ps typical

- Output skew: 20ps typical

- Low additive phase jitter, RMS: < 30fs typical, (fREF = 156.25MHz, 12kHz to 20MHz)

- Full 1.8V and 2.5V supply voltage mode

- Lead-free (RoHS 6), 40-lead VFQFN packaging

- -40 °C to 85 °C (Tc ≤ 105 °C) operating temperature range

- Supports fail-safe operation

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Applied Filters: