Overview

Description

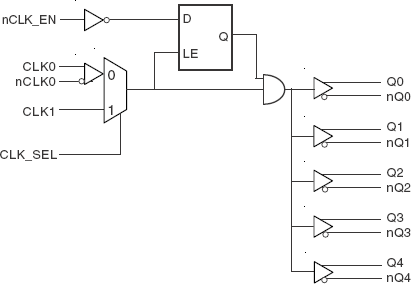

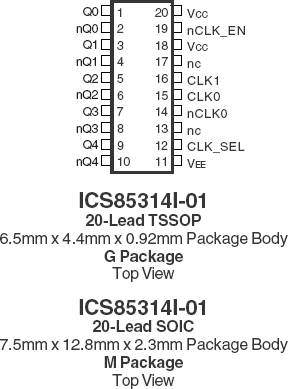

The 85314I-01 is a low skew, high performance 1-to-5 Differential-to-2.5V/3.3V LVPECL Fanout Buffer.The 85314I-01 has two selectable clock inputs. The CLK0, nCLK0 pair can accept most standarddifferential input levels. The single-ended CLK1 can accept LVCMOS or LVTTL input levels. The clock enable is internally synchronized to eliminate runt clock pulses on the outputs during asynchronous assertion/deassertion of the clockenable pin. Guaranteed output and part-to-part skew characteristics make the 85314I-01 ideal for those applications demanding well defined performance and repeatability.

Features

- 5 differential 2.5V/3.3V LVPECL outputs

- Selectable differential CLK0, nCLK0 or LVCMOS inputs

- CLK0, nCLK0 pair can accept the following differential input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

- CLK1 can accept the following input levels: LVCMOS or LVTTL

- Maximum output frequency: 700MHz

- Translates any single-ended input signal to 3.3V LVPECL levels with resistor bias on nCLK input

- Output skew: 30ps (maximum), TSSOP package 50ps (maximum), SOIC package

- Part-to-part skew: 350ps (maximum)

- Propagation delay: 1.8ns (maximum)

- RMS phase jitter @ 155.52MHz (12kHz - 20MHz): 0.05ps (typical)

- LVPECL mode operating voltage supply range: VCC = 2.375V to 3.8V, VEE = 0V

- -40°C to 85°C ambient operating temperature

- Available in lead-free RoHS-compliant package

Comparison

Applications

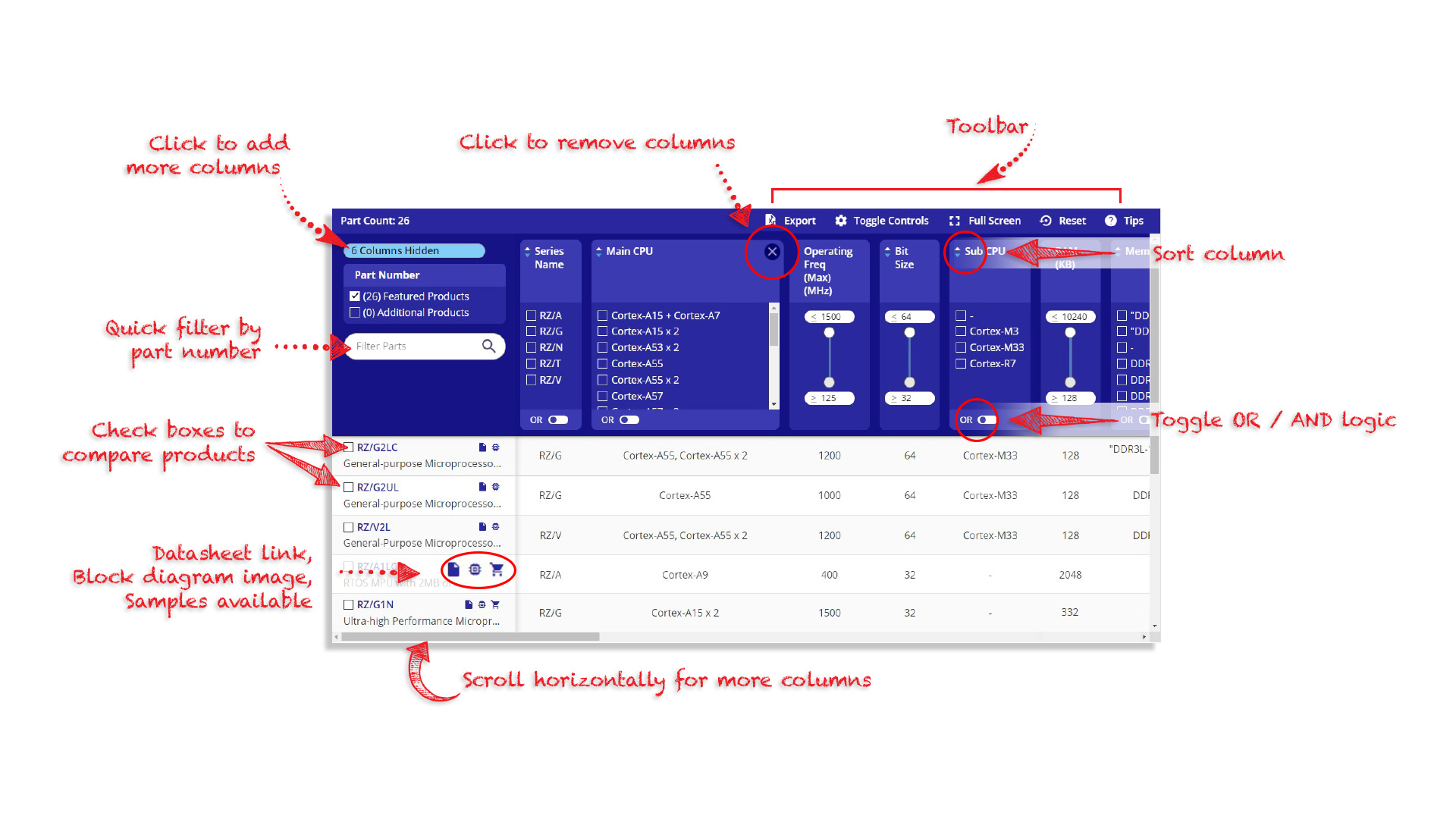

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.