Overview

Description

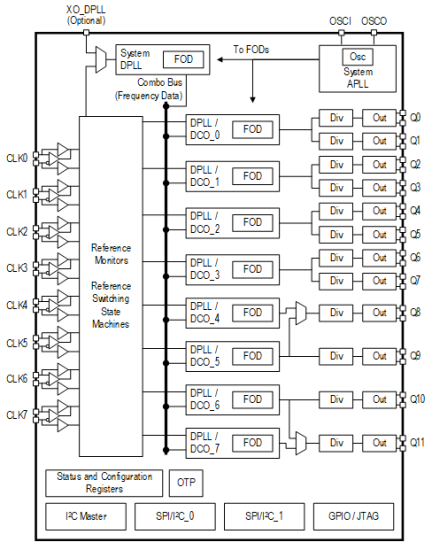

The 8A34041 multi-channel Digital PLL/Digitally Controlled Oscillator (DPLL/DCO) provides tools to manage timing references, clock conversion, and timing paths for common communications protocols such as Synchronous Ethernet (SyncE), Optical Transport Network (OTN), and Common Public Radio Interface (CPRI). The device can be used to synchronize communication ports on line cards or daughter cards that are connected with synchronization sources across backplanes or other media. Digitally Controlled Oscillators (DCOs) are available to be controlled by OTN clock recovery servo software running on an external processor. Digital PLLs (DPLLs) support filtering of gapped clocks for OTN; and hitless reference switching between references from redundant timing sources. The device supports multiple independent timing channels for clock generation; jitter attenuation and universal frequency translation. Input-to-input, input-to-output and output-to-output phase skew can all be precisely managed. The device outputs ultra-low-jitter clocks that can directly synchronize SerDes running at up to 28Gbps; as well as CPRI/OBSAI, SONET/SDH and PDH interfaces.

To see other devices in this product family, visit the ClockMatrix Timing Solutions page.

Features

- Eight independent timing channels

- Jitter output below 150fs RMS (typical)

- Digital PLLs (DPLLs) lock to any frequency from 1kHz to 1GHz

- DPLLs/Digitally Controlled Oscillators (DCOs) generate any frequency from 0.5Hz to 1GHz

- DCO outputs can be aligned in phase and frequency with the outputs of any DPLL or DCO

- Supports up to 8 differential; or 16 single-ended reference clock inputs

- Supports up to 12 differential outputs; or 24 LVCMOS outputs

- Reference monitors qualify/disqualify references depending on LOS, activity, frequency monitoring, and/or LOS input pins

- Automatic reference selection state machines select the active reference for each DPLL based on the reference monitors, priority tables, revertive/non-revertive and other programmable settings

- Device requires a crystal oscillator or fundamental-mode crystal: 25MHz to 54MHz

- Optional XO_DPLL input allows a wider range for XO, TCXO, or OCXO frequencies from 1MHz to 150MHz for applications that require a local oscillator with high stability

- Serial processor ports support 1MHz I²C or 50MHz SPI

- The device can configure itself automatically after reset via:

- Internal Customer-programmable One-Time Programmable memory

- Standard external I²C EPROM via separate I²C Master Port

Comparison

Applications

Design & Development

Software & Tools

Software & Tools

| Software title

|

Software type

|

Company

|

|---|---|---|

| Timing Commander Timing Commander™ is an innovative Windows™-based software platform enabling system design engineers to configure, program, and monitor sophisticated timing devices with an intuitive and flexible graphical user interface (GUI).

|

Code Generator | Renesas |

1 item

|

||

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Applied Filters:

Videos & Training

The ClockMatrix family of devices offers high-performance, precision timing solutions for applications with up to 100 Gbps interface speeds. They are versatile in their usage, supporting functions such as clock generation, frequency translation, jitter attenuation, and phase alignment across a range of densities. The 8A3404x Multichannel Digital PLL/DCO family manages timing references and clock conversion for protocols like SyncE, OTN, and CPRI. It features multiple independent timing channels for clock generation, jitter attenuation, and universal frequency translation, outputting ultra-low-jitter clocks for high-speed interfaces like SERDES, CPRI/OBSAI, SONET/SDH, and PDH.

Related Resources