Overview

Description

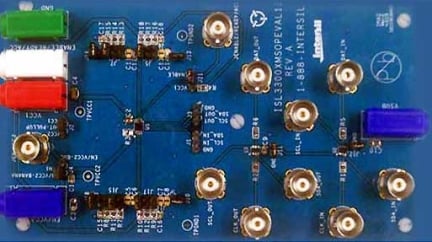

The ISL33002MSOPEVAL1Z evaluation board is designed to provide a quick and easy method for evaluating the ISL33002 two-channel bus buffer with rise time accelerators and hot-swap capability.

Discrete NMOS transistors are used to produce the pull-down functions of a wired-AND bus. Each SDA/SCL pin on the buffer is connected to an external open-drain NMOS transistor. The evaluation board also contains connections for the bus pull-up resistor and load capacitance. The logic input pins on the ISL33002 IC can be held logic High by a pull-up resistor or driven dynamically with an external logic source.

The ISL33002 two-channel bus buffer provides the buffering necessary to extend the bus capacitance beyond the 400pF maximum specified by the I2C specification. In addition, the ISL33002 features rise time accelerator circuitry to reduce power consumption from passive bus pull-up resistors and improve data-rate performance. The device also includes hot-swap circuitry to prevent corruption of the data and clock lines when I2C devices are plugged into a live backplane, and the ISL33002 adds level translation for mixed supply voltage applications.

Features

- Evaluation board for the ISL33002IUZ in the MSOP package

- +2.3V to +5.5V supply operation

- Configured to operate in an I2C environment

- Two-channel supply for level shifting applications

- On-board discrete NMOS open-drain transistors connected to SDA/SCL pins

- 3V logic for NMOS transistor gate

- On-board discrete bus pull-up resistors and load capacitance on SDA/SCL pins

- Convenient test points on SDA/SCL pins

Applications

- I2C bus extender and capacitance buffering

- Server racks for telecom, datacom and computer servers

- Desktop computers

- Hot-swap board insertion and bus isolation

Documentation

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Manual - Development Tools | PDF 418 KB | |

| Datasheet | PDF 1.17 MB | |

2 items

|

||

Design & Development

Product Options

Applied Filters: