Overview

Description

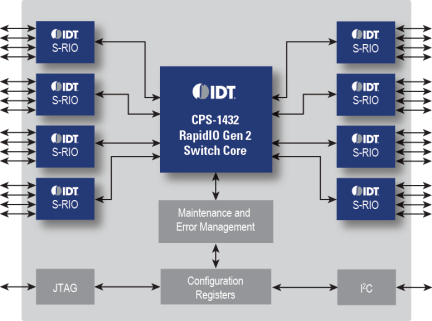

The IDT CPS-1432 is an 8x4/14x2/14x1 RapidIO Gen2 switch ideal for boards that require up to eight high bandwidth connections of up to 20 Gbps per port (8x4). The CPS-1432 can also be used in space constrained applications such as AMC or 6U/3U VPX where a large number of x4 links are used and small footprint is required. The CPS-1432 features a full, non-blocking bandwidth of 160 Gbps for up to 14 ports. It can also be used to drive backplanes or can be used as a backplane switch for small systems. The CPS-1432 device utilizes a 5th generation switch fabric, building upon RapidIO Gen1 CPS and Tsi switching architectures. This new switch uses patent pending features to minimize latency, ensure scheduling fairness, and provide superior multicast throughput.

Learn more: IDT RapidIO Development Systems

Features

- Designed to S-RIO 2.1 specification

- 32 lanes, with up to 8x4, 14x2, 14x1 port configurations

- 1.25, 2.5, 3.125, 5.0, or 6.25 Gbaud

- Full-duplex 160Gbps non-blocking bandwidth

- Long reach 100-cm 2 connector

- Enhanced quads configurable as 1x4, 2x2, 2x1

- 25x25 FCBGA

- Standard quads configurable as 1x4, 1x2, 1x1

- Up to 40% power savings -vs- RapidIO 1.3 switches per 10 Gigabit of data

Comparison

Applications

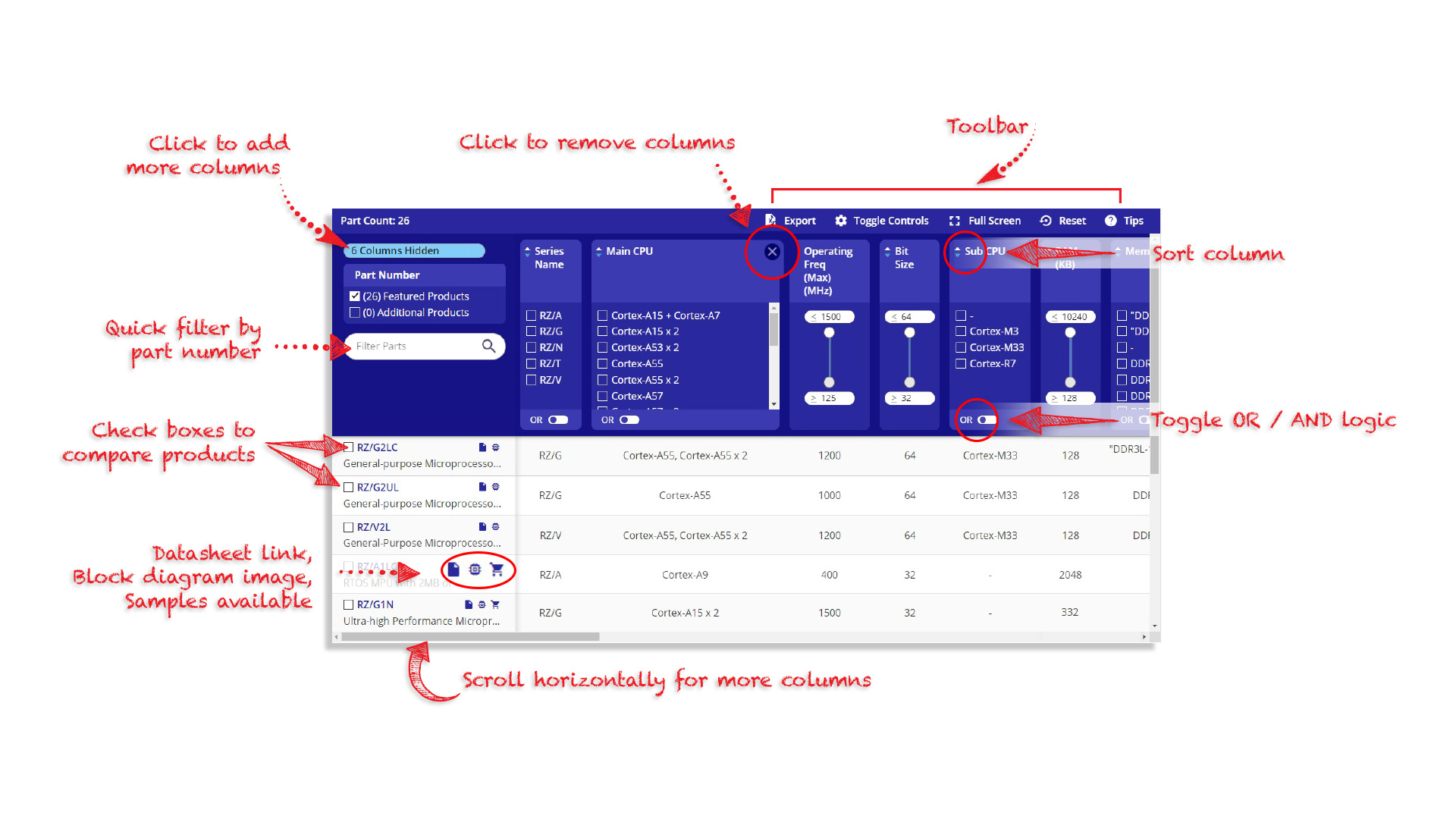

Design & Development

Software & Tools

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Videos & Training

Description

Transcript