Overview

Description

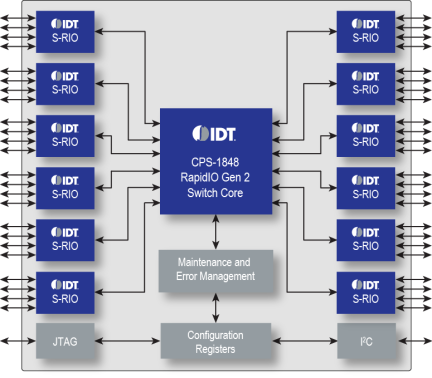

The IDT CPS-1848 provides a full, non-blocking bandwidth of 240 Gbps for up to 18 logical ports. The CPS-1848 device utilizes a 5th generation switch fabric, building upon Gen1 CPS and Tsi switching architectures. This new switch uses patent pending features to minimize latency, ensure scheduling fairness, and provide superior multicast throughput. The CPS-1848's 6.25 Gbaud SerDes is ideal for backplanes, yet can run even lower power for local connectivity.This performance is realized over twice the transmission channel distance and three orders of magnitude improvement in bit error rate (BER) compared to the very capable Gen1 standard.

Learn more: IDT RapidIO Development Systems

Features

- Designed to Serial RapidIO 2.1 Specification

- 48 lanes, with up to 12x4, 18x2, 18x1 port configurations

- 6 Enhanced quads configurable as 1x4, 2x2, 4x1

- 6 quads configurable as 1x4, 1x2, 1x1

- Full-duplex 240 Gbps non-blocking bandwidth

- 1.25, 2.5, 3.125, 5.0, or 6.25 Gbaud

- 29x29 FCBGA

- Long reach 100-cm 2 connector

- As low as 300mW per 10 Gbps data rate is up to 40% more power efficient vs. RapidIO 1.3 switches

Comparison

Applications

Design & Development

Software & Tools

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Videos & Training

Description

Transcript