Overview

Description

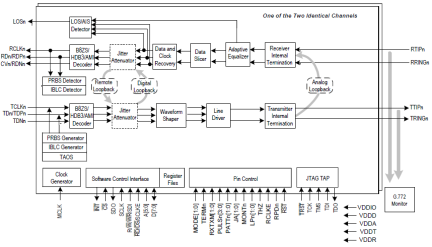

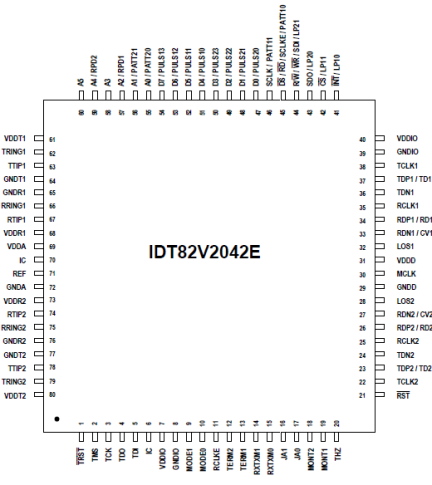

The 82V2042E can be configured as a dual-channel T1, E1, or J1 Line Interface Unit (LIU). The 82V2042E performs clock/data recovery, AMI/B8ZS/HDB3 line decoding, and detects and reports the Loss of Signal (LOS) conditions. An integrated adaptive equalizer is available to increase the receive sensitivity and enable the programming of LOS levels. In the transmit path, there is an AMI/B8ZS/HDB3 encoder and waveform shaper. There is one jitter attenuator, which can be placed in either the receive path or the transmit path. The jitter attenuator can also be disabled. The 82V2042E supports both single-rail and dual-rail system interfaces. To facilitate network maintenance, a PRBS/QRSS generation/detection circuit is integrated into the chip and different types of loopbacks can be set according to the applications. Four different kinds of line terminating impedances, 75Ω, 100Ω, 110Ω, and 120Ω are selectable on a per channel basis. The chip also provides driver short circuit protection and an internal protection diode and supports JTAG boundary scanning. The chip can be controlled by either software or hardware. The 82V2042E can be used in LAN, WAN, routers, wireless base stations, IADs, IMAs, IMAPs, gateways, frame relay access devices, CSU/DSU equipment, etc.

Features

- Dual channel T1/E1/J1 short haul line interfaces

- Supports Hitless Protection Switching (HPS) for 1+1 protection without external relays

- Programmable T1/E1/J1 switchability allowing one bill of material for any line condition

- Single 3.3V power supply with 5V tolerance on digital interfaces

- Meets or exceeds specifications in

- ANSI T1.102, T1.403, and T1.408

- ITU I.431, G.703, G.736, G.775, and G.823

- ETSI 300-166, 300-233, and TBR12/13

- AT&T Pub 62411

- Adaptive receive sensitivity up to -20dB (Host mode only)

- Non-intrusive monitoring per ITU G.772 specification

- Short circuit protection and internal protection diode for line drivers

- Loss of Signal (LOS) detection with programmable LOS level (Host mode only)

- Alarm Indication Signal (AIS) detection

- JTAG interface

- Supports serial control interface, Motorola and Intel non-multiplexed

- Interfaces and hardware control mode

- Software programmable or hardware selectable on:

- Wave-shaping templates

- Line terminating impedance (T1: 100Ω, J1: 110Ω, E1: 75Ω/120Ω)

- Adjustment of arbitrary pulse shape

- Jitter attenuator (JA) position (receive path or transmit path)

- Single-rail/dual-rail system interfaces

- B8ZS/HDB3/AMI line encoding/decoding

- Active edge of transmit clock (TCLK) and receive clock (RCLK)

- Active level of transmit data (TDATA) and receive data (RDATA)

- Receiver or transmitter power down

- High impedance setting for line drivers

- Pseudo Random Bit Sequence (PRBS) generation and detection with 215-1 PRBS polynomials for E1

- Quasi Random Sequence Signals (QRSS) generation and detection with 220-1 QRSS polynomials for T1/J1

- 16-bit Bipolar Pulse Violation (BPV)/Excess Zero/PRBS or QRSS error counter

- Analog loopback, digital loopback, remote loopback, and inband loopback

Comparison

Applications

- LAN

- WAN

- Routers

- Wireless base stations

- IADs

- IMAs

- IMAPs

- Gateways

- Frame relay access devices

- CSU/DSU equipment

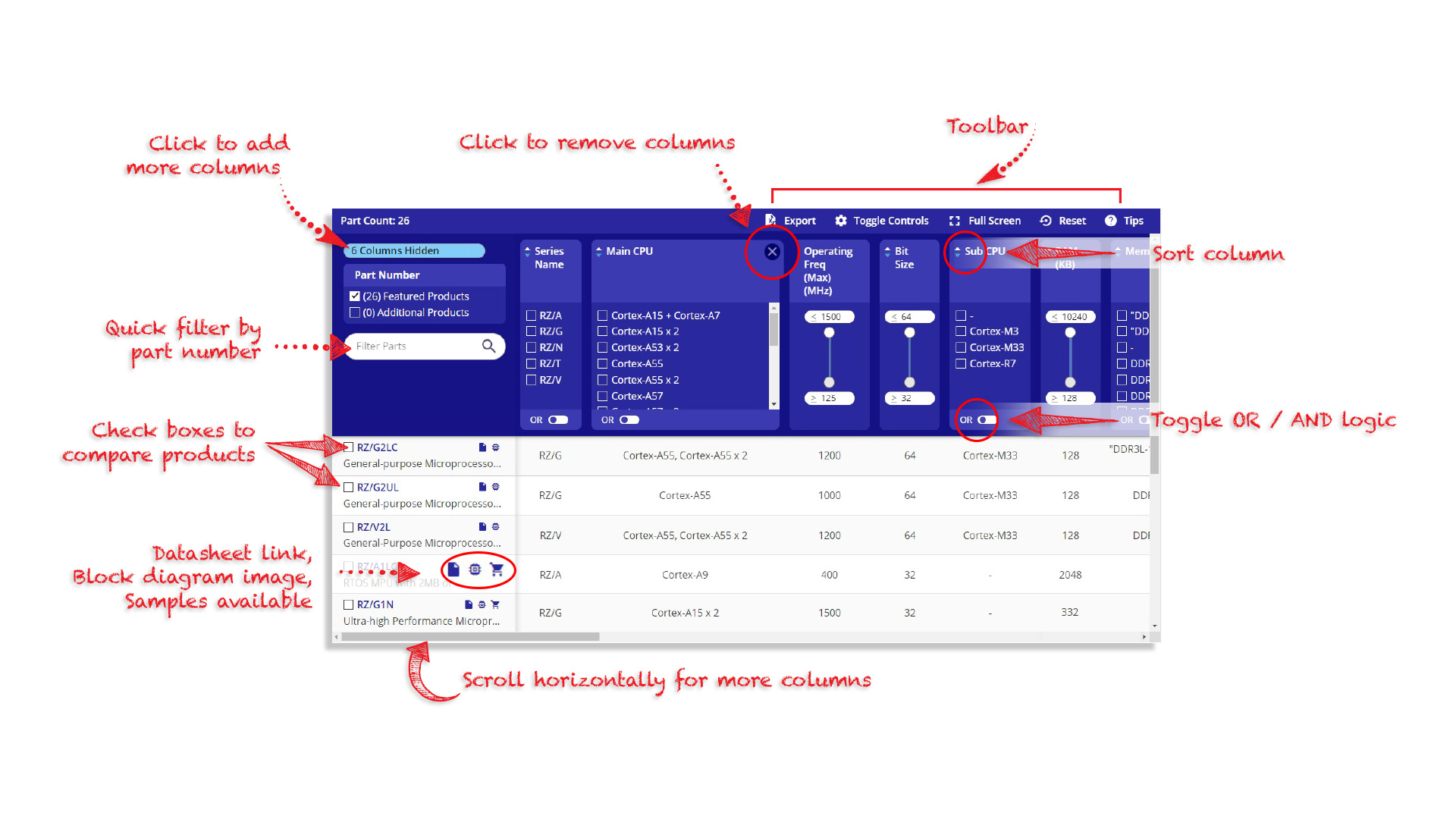

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.