Overview

Description

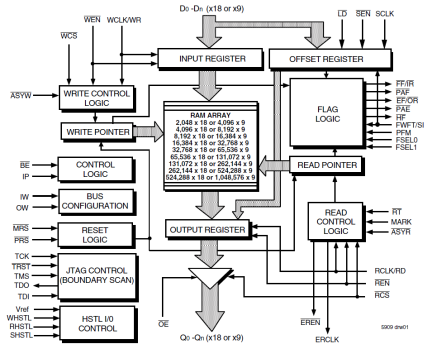

The 72T18125 is a 512K x 18 / 1M x 9 TeraSync 2.5V FIFO memory with clocked read and write controls and a flexible Bus-Matching x18/x9 data flow. Bus-Matching TeraSync FIFOs are particularly appropriate for network, video, telecommunications, data communications and other applications that need to buffer large amounts of data and match busses of unequal sizes. There are two possible timing modes of operation with these devices: IDT Standard mode and First Word Fall Through mode.

Features

- User selectable HSTL/LVTTL Input and/or Output

- 2.5V LVTTL or 1.8V, 1.5V HSTL Port Selectable Input/Output voltage

- 3.3V Input tolerant

- Program programmable flags by either serial or parallel means

- Big-Endian/Little-Endian user selectable byte representation

- Auto power down minimizes standby power consumption

- Master Reset clears entire FIFO

- Partial Reset clears data, but retains programmable settings

- Empty, Full and Half-Full flags signal FIFO status

- Output enable puts data outputs into high impedance state

- JTAG port, provided for Boundary Scan function

- Available in 240-pin PBGA package

- Easily expandable in depth and width

- Independent Read and Write Clocks (permit reading and writing simultaneously)

- Industrial temperature range (–40C to +85C) is available

Comparison

Applications

Design & Development

Models

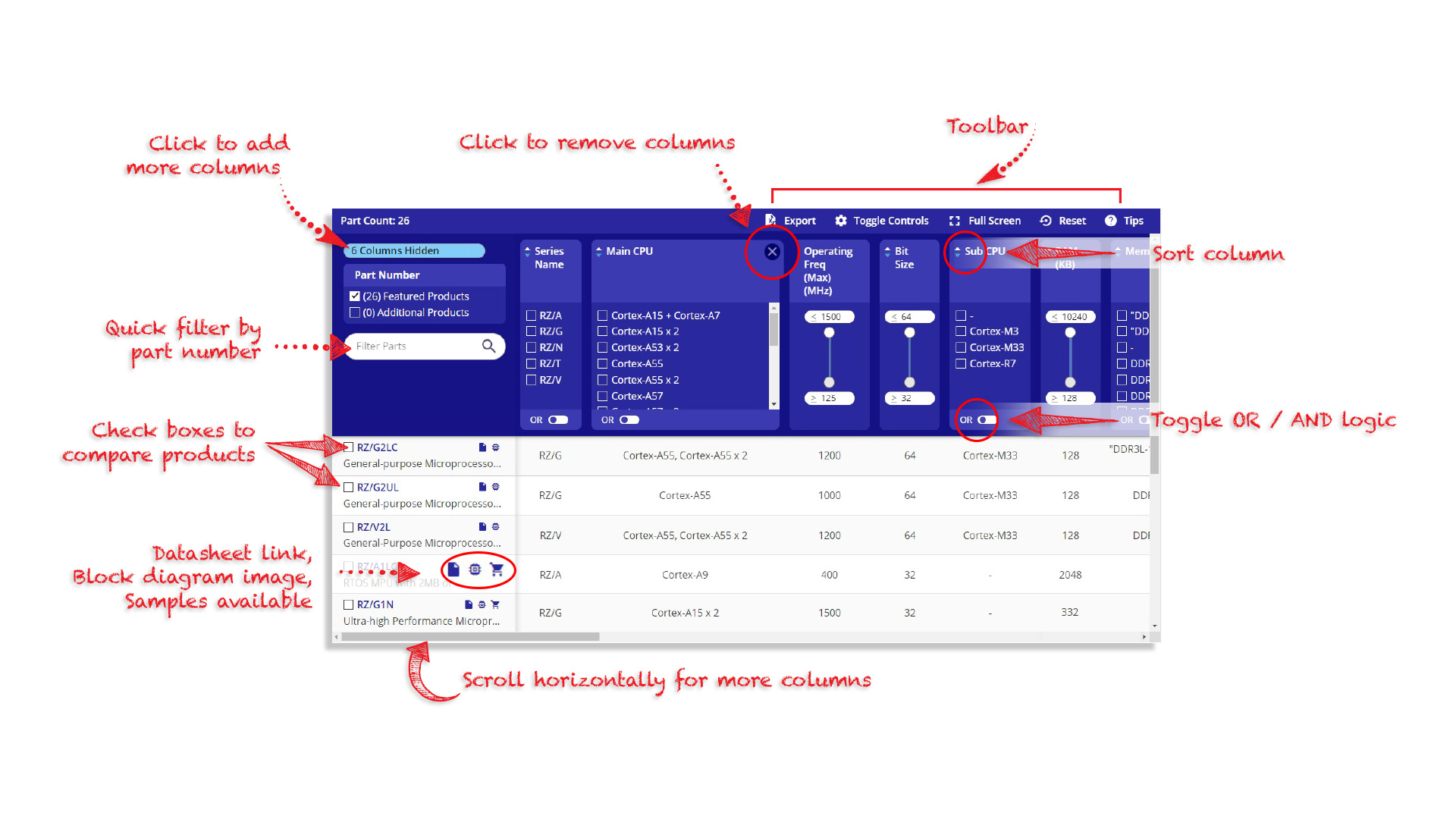

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.